DDR3基础技术培训_V0.9

DDR走线知识

SDRAM, DDR, DDR2, DDR3是RAM技术发展的不同阶段, 对于嵌入式系统来说, SDRAM常用在低端, 对速率要求不高的场合, 而在DDR/DDR2/DDR3中,目前基本上已经以DDR2为主导,相信不久DDR3将全面取代DDR2, 关于DDR, DDR2, DDR3, 其原理这里不多介绍, 其典型差别就是在内部逻辑的"预存取"技术有所差别, 但是从外部接口之间的速率来看, 他们基本类似, 就是clock,strobe,data,address, control, command等,无论是DDR/DDR2/DDR3,他们的clock与data 的理论频率是一致的, 及clock=266MHz, 则对应的data=266MHzMHz(这里可能有人反对, 觉得data应该等于533MHz, 其实它我们常说的533MHz的Bit Rate, 这里要注意一个周期是由'0'与'1'组成的, 我们在SI仿真时要注意了。

)DDR/DDR2/DDR3的Layout Guidelines通常具有下面的格式(只显示一部分,并且里面的参数参数参考)本文结合Micron与Freescale的DesignGuidelines,详细介绍DDR2的layout方面需要注意的问题,从总体来看,就可以归纳为上面那张图所表现的形式。

本文中关于lql-xxx为个人文章编号,无实际意义。

另外,读者可以参阅本站的另外一篇文章DDR2 design checklist。

1. Micro建议VSS为数字地,VSSQ为信号地,若无特别说明,两者是等效的。

VDD为器件内核供电,VDDDQ为器件的DQ和I/O供电,若无特别说明,两者是等效的。

本文内容可以和lql-003-DDR Designer Check list.doc 配合使用,作为DDR设计原则指导资料。

对于DDR来说,定义信号组如下:l 数字信号组DQ,DQS,DM,其中每个字节又是内部的一个信道Lane 组,如DQ0~DQ7,DQS0, DM0为一个信号组。

产品技术知识培训课件 DIY篇之2 内存 讲师王丹丹

内存类型

DDR4 虽然DDR3至今仍是少数高端用户和发烧友的专利,但内存厂商已经开始在规划下 一代DDR4了,初步预计四年后登场,届时会再次带来更低的电压和更高的频率。 根据奇梦达的一份路线图,最近两年的主要方向是将DDR3的标准电压从1.5V降 低到1.35V,首先是引入服务器市场,然后向桌面拓展;同时还要逐步提高主流频率, 从1066MHz到1333MHz再到1600。到2011年,1.35V的DDR3-1600将会大面积普及开来。 而在2012年,DDR4时代开启,起步频率降至1.2V,而频率提升至2133MHz,次年进一步将电 压降至1.0V,频率则实现2667MHz。当然这还只是早期规划,尤其是核心电压问题尚未达成一致标 准,但降低是肯定无疑的。 由于AMD和Intel都已将内存控制器整合在处理器内,因此预计四五年后又都会推出新的Socket/L GA接口。

PC100 从性能的角度来说,PC100的内存在主板设置在100MHZ外频,且在主板的BIOS选项中CL设置为2,此内存可以 稳定的工作。 PC133 其中的133指的是该内存工作频率可达133MHz。PC133 SDRAM的数据传输速率可以达到1.06GB/s。 严格地说,PC133和PC100内存在制造工艺上没有什么太大的不同,区别只是在制造PC133内存时多了一道"筛选“ 工序,把内存颗粒中外频超过133 MHz的挑选出来,焊接成高档一些的内存。

不同针脚DIMM接口对比 产品技术培训课件

颗粒封装 颗粒封装其实就是内存芯片所采用的封装技术类型,封装就是将内存芯片包裹起来, 以避免芯片与外界接触,防止外界对芯片的损害。 空气中的杂质和不良气体,乃至水蒸气都会腐蚀芯片上的精密电路,进而造成电学性 能下降。不同的封装技术在制造工序和工艺方面差异很大,封装后对内存芯片自身性 能的发挥也起到至关重要的作用。 DIP封装 芯片封装基本都采用DIP(Dual ln-line Package,双列直插式封装)封装,此封装形式在当时具有 适合PCB(印刷电路板)穿孔安装,布线和操作较为方便等特点。DIP封装的结构形式多种多样, 包括多层陶瓷双列直插式DIP,单层陶瓷双列直插式DIP,引线框架式DIP等。但DIP封装形式封装 效率是很低的,其芯片面积和封装面积之比为1:1.86,这样封装产品的面积较大,内存条PCB板的 面积是固定的,封装面积越大在内存上安装芯片的数量就越少,内存条容量也就越小。同时较大的 封装面积对内存频率、传输速率、电器性能的提升都有影响。 TSOP封装 到了上个世纪80年代,内存第二代的封装技术TSOP出现,得到了业界广泛的认可,时至今日仍旧 是内存封装的主流技术。TSOP是“Thin Small Outline Package”的缩写,意思是薄型小尺寸封 装。TSOP内存是在芯片的周围做出引脚,采用SMT技术(表面安装技术)直接附着在PCB板的表 面。TSOP封装外形尺寸时,寄生参数(电流大幅度变化时,引起输出电压扰动) 减小,适合高频应用, 操作比较方便,可靠性也比较高。同时TSOP封装具有成品率高,价格便宜等优点,因此得到了极 为广泛的应用。 TSOP封装内存 TSOP封装方式中,内存芯片是通过芯片引脚焊接在PCB板上的,焊点和PCB板的接触面积较小,使 得芯片向PCB办传热就相对困难。而且TSOP封装方式的内存在超过150MHz后,会产品较大的信号 干扰和电磁干扰。 产品技术培训课件

电脑短训班培训教案

电脑短训班培训教案一、前言1. 教学目标:本课程旨在让学员掌握基本的电脑操作技能,包括Windows操作系统的使用、常用办公软件的应用、互联网的基本使用等。

通过短期的培训,使学员能够独立完成日常的电脑操作,提高工作效率。

2. 教学对象:无电脑操作经验的学员,或有基础但需要进一步提高的学员。

3. 教学方式:理论讲解与实践操作相结合,以实践操作为主。

4. 教学环境:每人一台电脑,安装有Windows操作系统和常用办公软件。

二、教学内容1. 第一章:Windows操作系统的基本操作1.1 认识电脑硬件与软件1.2 启动与关闭电脑1.3 桌面与任务栏的基本操作1.4 窗口的基本操作1.5 文件与文件夹的基本操作2. 第二章:常用办公软件的应用2.1 认识常用的办公软件2.2 Word文档的基本操作2.3 Excel表格的基本操作2.4 PowerPoint演示文稿的基本操作3. 第三章:互联网的基本使用3.1 认识互联网3.2 浏览器的使用3.3 搜索引擎的使用3.4 与文件3.5 电子邮件的基本操作4. 第四章:网络交流与安全4.1 腾讯QQ的基本操作4.2 的基本操作4.3 网络安全与防护5. 第五章:常用快捷键与操作技巧5.1 认识快捷键5.2 常用快捷键的使用5.3 操作技巧分享三、教学安排1. 每章内容安排2个课时,共10个课时。

2. 每个课时45分钟,其中包括讲解与实践操作时间。

四、教学评价1. 课后作业:每章布置相应的实践作业,巩固所学内容。

2. 课程结束后进行综合测试,检验学员掌握程度。

五、教学资源1. 教材:电脑短训班培训教材。

2. 课件:每章内容配套的PPT课件。

3. 实践案例:提供实际操作案例,帮助学员更好地理解与运用所学知识。

六、教学建议1. 注重学员的实践操作,鼓励学员在课堂上积极动手实践。

2. 针对不同学员的基础,给予个别辅导与指导。

3. 定期进行课程回顾与总结,帮助学员巩固所学内容。

《内存条知识培训》课件

04

内存颗粒的品质和性能 对整个内存条的性能有 很大影响。

电路板

01

02

03

04

电路板是内存条的基板,负责 连接和固定各个部件。

电路板上的布线要尽可能地短 、直,以减小信号延迟和干扰

。

电路板上通常会有一些电容和 电感等元件,用于滤波和稳压

。

电路板的品质和工艺也会影响 内存条的性能和稳定性。

金手指

更低功耗

更广泛的应用领域

随着云计算、物联网等技术的普及, 未来内存条的应用领域将更加广泛。

未来内存条将更加注重节能环保,降 低功耗,减少能源消耗。

THANKS

感谢观看

稳定性

总结词

稳定性是衡量内存条可靠性的重要指 标,稳定性越高,内存条越不容易出 错。

详细描述

稳定性通常通过长时间运行测试和压 力测试来评估,稳定性高的内存条可 以保证计算机长时间稳定运行。

04

内存条的选购与使用

选购注意事项

01

02

03

04

品牌信誉

选择知名品牌,确保产品质量 和售后服务的可靠性。

避免频繁插拔

尽量避免频繁插拔内存条,以免造成接触不 良或损坏。

检查内存容量与速度

定期检查内存容量与速度是否正常,如有异 常及时处理。

05

内存条常见问题与解决方案

兼容性问题

总结词

内存条与主板或其他硬件不匹配导致的问题

详细描述

当内存条与主板或其他硬件不兼容时,可能会出现电脑无法启动、运行缓慢、蓝屏等问题。解决方案 包括检查内存条规格与主板要求是否匹配,确保购买的内存条与原有内存条品牌、型号、容量相同。

金手指是内存条与主板连接的部分, 用于传输数据和控制信号。

DDR3_desigin guide_V1.3

龙芯CPU DDR3布线设计指导及软件调试说明产品型号:龙芯3A2013年1月龙芯中科技术有限公司阅读指南本手册是龙芯3A、3B及2G芯片的内存软硬件设计指导,分为两部分,第一部分为硬件设计的指导及布线约束文件,第二部分为软件调试说明,适用于针对龙芯3A、3B及2G处理器的主板设计。

修订历史目录第一部分DDR3硬件设计指导 (5)1. 说明 (5)2. 电源设计要求 (5)3、PCB布局及走线要求 (5)3.1 信号分组(DDR3 signal groups) (6)3.2 叠层和布线层使用 (6)3.3 参考平面 (8)3.4 时钟信号组布线要求 (8)3.5 控制信号 (9)3.6 命令信号 (10)3.7 数据信号 (12)3.8 数据选通信号 (13)第二部分DDR3软件调试说明 (15)4. 内存基础知识 (15)5. 龙芯芯片的访存流程 (16)6. Pmon内存初始化代码介绍(3A/B、2G/H) (16)7. 内存故障诊断 (18)第一部分 DDR3硬件设计指导1. 说明本文档为基于龙芯3A、3B及2G芯片的主板设计提供内存设计及layout指导,根据我们针对现有的开发系统的信号测试结果及龙芯CPU的特点,给出了目前我们认为比较合理的内存设计方案。

本方案针对采用DDR3 DIMM插槽的主板设计方案,其它情况我们后续会补充完善,现阶段请跟我们技术人员联系。

2. 电源设计要求Vref信号,该信号电流较小,但是该信号的不稳定会导致时序误差、产生比较大的jitter 等问题,所以需要保证Vref电压值稳定,波动范围小于+-2%。

对于Vref的走线要求:1)走线宽度30mils,推荐走在表层2)距离其它信号走线距离大于20mil,距其它干扰源(power switch,晶振等)250mil 以上3)Vref通过1%的电阻对DIMM_VDD分压产生,在DIMM插槽的每一个Vref引脚和CPU 的每个Vref引脚附近至少放置0.01uF和0.1uF电容各一个,在分压电阻附近放置1个0.1uF 电容。

DDR3基础技术培训_V0.9

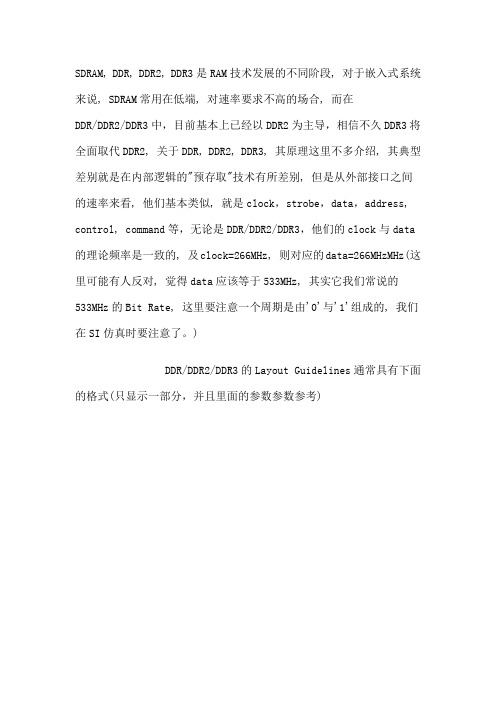

1.DDR的发展:2003年秋季Intel公布了DDR2内存的发展计划。

而随着当时CPU 前端总线带宽的提高和高速局部总线的出现,内存带宽成为系统越来越大的瓶颈。

处于主流DDR技术已经发展到极至,因此DDR2脱颖而出。

DDR2的实际工作频率是DDR的两倍。

这得益于DDR2内存拥有两倍于标准DDR内存的4bit预读取能力。

下图为DDR和DDR2预读取能力的对比。

DDR2内存技术最大的突破点其实不在于用户们所认为的两倍于DDR的传输能力,而是在采用更低发热量、更低功耗的情况下(由2.5V降为1.8V),DDR2 可以获得更快的频率提升,突破标准DDR的400MHZ限制。

DDR内存通常采用TSOP芯片封装形式,这种封装形式可以很好的工作在200MHz上,当频率更高时,它过长的管脚就会产生很高的阻抗和寄生电容,这会影响它的稳定性和频率提升的难度。

这也就是 DDR的核心频率很难突破275MHZ的原因。

而DDR2内存均采用FBGA封装形式。

不同于目前广泛应用的 TSOP 封装形式,FBGA封装提供了更好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的发展提供了良好的保障。

2007年中Intel表示支持DDR3的发展,随后DDR3慢慢走上了历史的舞台,根据由JEDEC协会所制定的规格来看,由技术面来切入DDR3与DDR2的异同点,DDR3拥有高频率低电压的优点,DDR3可以比DDR2运作时省下约30%的电力,速度方面DDR3从800Mbps起跳最高可以至1600Mbps,几乎是DDR2的二倍速度,正因为高传输率的关系,DDR3可以在一个时序(Clock)之中传出8bit的数据,比起DDR2的4bit也是二倍的数据传输量,低电压更是DDR3的优势之一,1.5V 的电压比DDR2的1.8V降低了17%。

下面的图表总结了DDR,DDR2,以及DDR3的一些重要的区别:2、认识内存相关工作流程与参数首先,我们先了解一下内存的大体结构工作流程,这样会比较容量理解这些参数在其中所起到的作用。

电脑硬件培训资料(幻灯片)

电脑硬件培训资料 第一节 认识计算机的各大硬件组成

机箱的整体外观

电脑硬件培训资料 第一节 认识计算机的各大硬件组成

主板

• 主板和CPU都是电脑中最 关键的部件。 • 所有的板卡必须通过主 板发挥作用,主板性能 和质量的好坏直接影响 到整个系统。 • 电脑主板按不同的架构 标准和各种不同的主要 部件、接口组合而成。

电脑硬件培训资料 第二节 计算机的各大硬件详细介绍

IDE接口: • IDE接口用来连接硬盘 和光驱等IDE存储设备。 通常蓝色的IDE接口为 IDE1,白色的IDE接口 为IDE2。靠近IDE接口, 颜色为黑色的接口为软 驱接口。

电脑硬件培训资料 第二节 计算机的各大硬件详细介绍

SCSI接口

• 一般的,它连接的是并口 硬盘的数据接口。 • SCSI接口多用于服务器和 高端工作站上,目前主流 的SCSI接口规范为SCSI 80和SCSI 160,传输速度 分别为80 MB/s和160 MB/s

希 捷 硬 盘

电脑硬件培训资料 第一节 认识计算机的各大硬件组成

光驱

• 功能: 听歌,看牒,装软 件,用游戏光牒打游戏, 等等。有了它,电脑处处 充满生机和活力。

电脑硬件培训资料 第二节 计算机的各大硬件详细介绍

二、计算机各大硬件的详细介绍

电脑硬件培训资料 第二节 计算机的各大硬件详细介绍

主板电源插座:

硬盘

• 功能:硬盘是我们熟知的 电脑配件之一,简单的说 就是一个大容量存储器, 与主机通讯速度很快,成 为现代电脑不可缺少的配 件。 • 作用:由于计算机在工作 时CPU,输人输出设备与存 储器这间要大量地交换数 据,因此存储器的存处速 度和容量,也是影响计算 机运行速度的主要因素之 一。

ddr3 学习分享

读/写

激活命令(active)

每次开始读写任务之前,Bank中的目标行必须进行激活命令,进入激活状态。 最多4个Bank可同时进入激活状态。 同一个Bank中不同行激活命令之前都需要进行Precharge命令。

读/写

当Bank中目标行激活后,就可以发出读/写命令。

过程:

首先确定行(包括片选及L-bank的确定),行有效命令,并使其处于激活状态; 然后确定列,列寻址信息与读/写命令同时发出。

时钟频率,即核心频率:DDR3的clk频率。(上升沿)

I/0频率,总线频率,工作频率:数据线上传输频率。(上升沿)

等效频率:等效数据传输频率。(上升沿,下降沿) 带宽: 内存总线所能提供的数据传输能力。

带宽=内存核心频率×倍增系数×(内存总线位数/8) Eg:DDR3-1600 200 *8*64/8=12800MB/S=1.28GB/S

附录:典型时间参数

1.RAS-CAS Delay tRCD

行有效命令到列读取命令的间隔。 后改进,可让CAS紧接着RAS发出。可提高CA利用率,时序参数上添加一个AL (附加延迟)

2.CL CAS Latency 读取潜伏期

读命令到数据出现在I/O总线上的时间

3.写入/校正时间 tWR

写操作完成,会留出一定的时间以保证数据完成有效的写入芯片。

容量计算验证

2^15 * 2^11 * 2^3 * 16bit* ¾=6Gb

32GB eMMC+24Gb LPDDR3

6Gb*4 64bit

8GB Emmc+8Gb LPDDR3

4Gb*2 64bit

DDR3 学习总结

DDR2_DDR3_SDRAM命令和协议汇总

/memory 1检验DDR, DDR2和DDR3 SDRAM 命令和协议跟上更加复杂、更短设计周期的步伐不只计算机存储器系统一直需要更大、更快、功率更低、物理尺寸更小的存储器,嵌入式系统应用也有类似的要求。

本应用指南介绍了逻辑分析仪在检验DDR, DDR2和DDR3 SDRAM 命令和协议中的能力。

应用指南 电子发烧友 电子技术论坛2 /memory检验DDR, DDR2和DDR3 SDRAM 命令和协议应用指南表1. SDRAM 标准引言DRAM的异步操作特性在连接同步处理器时导致了许多设计挑战。

SDRAM (同步DRAM)采用专门设计,以实现DRAM 与计算机系统其余部分同步操作,而不需定义基于序列模式的存储器操作。

SDRAM 的技术演进,如DDR SDRAM,已经迅速提高了存储器的数据速率性能。

DDR, DDR2和DDR3 SDRAM 都通过从存储控制器主机向存储器发送的存储器命令进行控制。

DDR, DDR2和DDR3 SDRAM一直都有这样的需求,就是存储器要容量更大、速度更快、功耗更低以及物理尺寸更小。

这些需求推动着DRAM 技术的进步。

近几年中,主流DRAM 技术有很多主要提升,如SDRAM(同步DRAM),DDR(双数据率)SDRAM,DDR2(双数据率2)SDRAM,DDR3(双数据率3)SDRAM。

DDR(双数据率)SDRAM 通过提升时钟速率、猝发式数据以及在一个时钟内传输两个数据位,提升了内存的数据率性能。

DDR2(双数据率2)SDRAM在DDR的基础有一些进步。

DDR2 SDRAM 时钟速率更高,这样就增加了内存的数据速率。

但在时钟速率增长的情况下,可靠的内存处理对信号完整性的要求更为苛刻。

随着时钟速率增长,电路板上的信号路径变成了传输线,这样正确的布线和信号走线末端端接变得至关重要。

DDR3 SDRAM 是革命性的技术提升,它将SDRAM 速度推到了800Mb/s以上。

电信行业G技术培训普及手册

3G技术培训普及手册目录一.3G标准篇 (1)1.什么是第三代移动通信系统 12.IMT-2000标准组织简要介绍 13.3GPP协议版本的发展路线 14.3GPP各个版本的主要特点是什么 25.3GPP R99和R4版本的主要区别 26.3GPP R4版本为什么使用BICC协议而不是SIP-T? 37.在R4中使用的扩展的H.248与H.248有什么不同? 48.3GPP R99和R4核心网电路域差异 49.承载与控制分离的结构有什么好处?710.3GPP R4相对于R99的优势811.R4版本基本体系结构1112.3GPP R5版本为什么要引入IMS域1213.国际上3G专利的形势和进展1414.中国IMT-2000频谱分配1515.3G频段Operating Band有哪些?1516.CDMA2000标准演进1617.IS-95A/B演进到CDMA20001x有什么变化?1618.如何从CDMA2000 1X到CDMA2000 1x EV的平滑演进1719.IS-95的技术特点是什么?1820.CDMA20001X有什么技术特点?1821.CDMA2000 1x EV-DO有什么技术特点?1922.CDMA20001x EV-DO如何进行网络部署?2023.CDMA2000 1X EV-DV有什么特点?20 二.3G原理篇 (22)24.什么是CDMA技术2225.CDMA技术的起源2326.CDMA的软容量是指什么2327.CDMA短码和长码2428.为什么功率控制在CDMA系统中非常重要2429.为什么CDMA手机能保持低的发射功率2530.什么是CDMA软切换?它与硬切换有什么分别2531.什么是CDMA的"更软切换"2632.CDMA系统的UIM卡介绍2633.IMSI(MIN)介绍2734.MDN号码的介绍2835.TLDN号码的介绍2936.CDMA为什么要加密和鉴权2937.什么是机卡一体,机卡分离2938.为什么EIR在国内没有开通3039.CDMA系统如何保护A_key安全性3040.天线增益、水平/垂直波束宽度、单/双极化的概念?3141.接收机底噪、接收机增益、接收灵敏度、移动台的热噪声功率3242.GOS、RSSI、Eb/No、Eb/Io的概念3343.db、dBi、dBm分别是什么单位,有何区别?3344.基站侧信号处理,比如交织、复用后同原来相比什么区别3345.I、Q信号是如何产生的,I、Q信号复用的作用3446.3G系统采用了什么语音编码技术?3547.3G系统采用了什么信道编码技术?3548.什么是HARQ技术3549.CPCH是否能够提高上行速率容量,该信道相关功能3650.WCDMA承载分组数据的传输信道有哪些3651.WCDMA系统中物理信道的功率分配方式3752.AAL2/AAL5等ATM连接的区别3853.单模光纤和多模光纤简要介绍3854.什么是无线资源管理,主要的技术有哪些?3955.WCDMA终端是如何实现与系统的同步的?4056.WCDMA系统是如何完成寻呼过程的?4157.WCDMA系统在切换时需要测量哪些参数?4258.什么是TD-SCDMA系统中的接力切换技术?4259.WCDMA无线接入网络都有哪些接口?4360.WCDMA终端有哪些工作模式?4361.为什么CDMA需要对整个网络同步4462.WCDMA的同步方式,以及与cdma2000在同步上的区别4563.相对与同步切换,异步切换会对切换掉话率有多少影响4664.3G中都采用了哪些分集技术?4665.基站发射分集的实现方式以及带来的增益、投资成本4766.什么是高速下行分组接入技术(HSDPA)?4967.智能天线波束宽度是多大? 多径条件下如何跟踪用户?4968.GGSN和SGSN是否和GPRS中的设备相同?4969.3G电路域和分组域网络鉴权和认证基本要求5070.2G系统和3G系统中对用户的鉴权有哪些区别?5071.相对2G系统,3G在信息安全措施上有哪些改进?5072.七号信令传输如何变为MPLS,也就是如何用IP承载?5173.R4如何和PSTN网络互通?5174.路由器支持哪些安全协议,启用后对路由器的性能影响?5175.移动网络中信令寻址方式有哪些?各有什么优缺点?5376.什么是APN?5377.什么是SIGTRAN?5378.什么是TFO、TrFO,各有什么优点?5479.R4的承载方式有哪些及其各自优缺点?5480.3G用户是如何访问外部数据网的?5581.MIP技术简单介绍,及技术实现方案5582.频间硬切换实现的机制,以及对RNC性能的影响5683.RNC IuCS和IuPS能否通过同一物理链路到MSC再到SGSN5784.分组域设备IP地址如何规划5785.Ga接口和GTP’协议是什么?5786.QoS保证58 三.业务市场篇 (59)87.3G业务概述5988.什么是3G业务网络?它主要包含哪些网元?6089.WCDMA业务平台(或者说业务网关)具有哪些功能6090.介绍一下3G业务平台的界面规范?6191.业务管理平台对用户门户有哪些功能要求?6292.会议电视和可视电话的区别?可视电话的工作过程?6393.MultiCALL与多方通话关系如何?6394.综合预付费业务的主要功能和实现方式?6495.预付费漫游怎样实现机制如何?6496.移动智能网和固网智能网的主要区别?6597.主要的3G智能网协议有那些?6598.3G智能网相比2G智能网而言,新增了什么业务能力?6699.CAMEL在R4和R5阶段有何区别?67100.移动定位业务(LCS业务)采用哪三种移动定位技术?68 101.初期定位业务主要有哪些?这些业务对定位精度有什么要求?69 102.通过Cell-ID方式的定位过程中HLR如何找到了MS70 103.针对3G的商用定位业务是否与2G有不同?70 104.运营商开展定位业务的盈利模式是什么?71 105.移动流媒体业务有哪些类型的应用?71 106.影响移动流媒体应用的因素有哪些?72 107.移动流媒体业务有哪几种传输方式?72 108.移动流媒体业务使用哪些特有的应用和控制协议?73 109.电路域视频业务的业务流程。

维修部培训教程(1)

Bios的设置选项意义

维修部培训教程(1)

Bios的设置选项意义

维修部培训教程(1)

微型系统PE

微型系统有什么用?如何在U盘上安装win PE系统?

维修部培训教程(1)

XP直装和XP GHOST

பைடு நூலகம்

XP原版直装 XP GHOST

PE系统下装系统

维修部培训教程(1)

电脑故障检测常见方法

• 直接观察法检测故障 • 清洁法 • 擦拔法 • 最小系统法 • 逐步添加去除法 • 替换法 • 听声音判断电脑故障 • 电脑故障处理步骤 • 电脑故障排除前的准备工作

再见,see you again

2020/12/13

维修部培训教程(1)

维修部培训教程(1)

2020/12/13

维修部培训教程(1)

主板上的原件

维修部培训教程(1)

主板上的原件

维修部培训教程(1)

内存的类型

SD 同步动态内存 DDR3

DDR

DDR2

SD

DDR

DDR2

维修部培训教程(1)

DDE3

显卡接口类型

PCI

VGA

PCIE

PCI-X

维修部培训教程(1)

CPU的类型

3G手机操作系统培训共16页

2、利用官方OVI商店下载-在手机安装OVI商店客户端

用手机登录官方OVI商店,点击<下载客户端>后,将自动进行OVI 商店的下载和安装。在OVI商店中选择您喜欢的应用程序。点击< 购买>,输入密码后点击<确定>,确认购买页面点击<确认>。

塞班操作系统培训

培训师:刘辰 2019.08

目录

1 塞班系统简介 2 塞班系统软件安装方法 3 热门应用推荐

4

2

1 塞班系统简介

塞班是什么?

塞班一词是英文“Symbian”的谐音, Symbian 操作系统是Symbian公司为手机而设计 的操作系统,它包含联合的数据库、使用者界面 架构和公共工具的参考实现 。Symbian的优势在 于它得到了占据市场份额大多数的手持通讯设备 厂商的支持,在NOKIA的大力倡导下,已经成为 一个开放的、易用的、专业的开发平台 。wap和web浏览器多页浏览器, 集成常用网址,在线书签。

是一款输入快捷、操作简便、功能 强大的新一代智能手机平台输入法。

Google Maps 谷歌地图,支持导 航,查询地址,个性化星标、卫星 视图和实时交通情况。 可以随时随地免费发布浏览赶集网 海量生活信息。无论是找房,找工 作,还是本地服务又快又轻松!

3. 利用诺基亚PC套件或者诺基亚OVI套件,双击需要 安装的应用软件,将手机连接到电脑,确认<安装 >。

8

24 塞班系统软件安装方法

2024年度服务器硬件技术培训文档

存储服务器

专门用于数据存储和管理,提 供大容量、高可靠性的存储解

决方案。

9

定制化配置方案设计

内存配置

根据应用需求和预算,选择合 适的内存容量和速度。

网络设备

选择高性能网卡和交换机,确 保数据传输速度和稳定性。

处理器选择

根据业务需求选择适合的处理 器型号和核心数量。

2024/3/24

存储方案

根据数据类型和访问频率,选 择合适的存储介质(如SSD、 HDD)和存储容量。

服务器具有高速CPU运算能力、长时间 可靠运行、强大I/O外部数据吞吐能力 以及强大网络通信能力.

服务器分类:按应用层次划分(入门级 服务器、工作组级服务器、部门级服务 器、企业级服务器)、按处理器架构划 分(CISC架构服务器、RISC架构服务 器、VLIW架构服务器)、按处理器运 算方式划分(单路服务器、双路服务器、 多路服务器)、按机箱结构划分(台式 服务器、机架式服务器、刀片式服务器、 机柜式服务器)

2024/3/24

03

熟悉常用的故障排除工 具和技术,如替换法、 最小系统法、逐步添加 法等。

17

04

学会如何与厂商或技术 支持团队沟通和协作, 以便及时获取帮助和解 决方案。

性能优化策略探讨

了解服务器性能评估标准和指标,如 处理器性能、内存带宽、磁盘I/O等。

熟悉常用的性能监控和分析工具,如 系统自带的性能监视器、第三方性能 分析工具等。

可扩展性考虑

在满足性能要求的前提 下,选择性价比较高的

产品。

8

选择支持升级和扩展的 硬件,以适应未来业务

增长。

常见配置方案分析

01

02

03

04

塔式服务器

计算机应用培训

06

其他硬件组件

介绍其他重要硬件组件,如电源、主板、声卡 等

计算机软件基础

操作系统

介绍常见的操作系统(如 Windows,macOS,Linux), 以及它们的特点和适用场景

总结词

了解计算机软件的分类和应用

办公软件

介绍常用的办公软件(如 Microsoft Office系列),以及 这些软件的基本功能和使用方法

计算机应用实践与案例分析

企业办公自动化实践

总结词

掌握企业办公自动化系统的使用 ,提高工作效率。

详细描述

介绍企业办公自动化系统的基本 功能和特点,包括文档管理、邮 件系统、日程安排等,并演示如 何使用这些工具提高工作效率。

网站建设与维护实践

总结词

学会网站的设计、开发和维护,提升 个人或企业形象。

详细描述

详细描述

了解演示文稿的创建、幻灯片的添加和删除等基本操作;掌 握幻灯片的主题、背景、切换效果等设计技巧;学会插入文 字、图片、形状等元素,并进行格式化;能够添加动画效果 ,使演示文稿更加生动有趣。

邮件系统操作

总结词

掌握如何使用邮件系统发送和接收邮件,以及如何管理邮件。

详细描述

了解如何注册和使用邮件系统;掌握如何编写和发送邮件,包括添加附件、抄送、密送等;学会如何 接收和查看邮件,包括标记为已读、删除、移动到文件夹等;能够使用过滤器对邮件进行分类和管理 。

介绍网站建设的基本流程,包括需求 分析、设计、开发、测试和上线等阶 段,同时讲解如何进行网站维护和更 新,保持网站内容的新鲜度和吸引力 。

电子商务应用实践

总结词

掌握电子商务平台的运营和管理,拓 展业务渠道。

详细描述

介绍电子商务平台的运营模式和管理 方法,包括商品管理、订单处理、物 流配送等环节,并分享成功和失败的 案例,总结经验教训。

DDRII、DDRIII设计分析技术培训班

DDRII/DDRIII设计分析技术培训班招生对象---------------------------------硬件设计工程师,硬件测试工程师,PCB设计工程师,EMC工程师,PI工程师,SI工程师,项目经理,技术支持工程师,研发主管,研发总监,研发经理,测试经理,系统测试工程师等等【主办单位】中国电子标准协会【咨询热线】0 7 5 5 – 2 6 5 0 6 7 5 7 1 3 7 9 8 4 7 2 9 3 6 李生【报名邮箱】martin# (请将#换成@)课程内容---------------------------------【参加对象】硬件设计工程师,硬件测试工程师,PCB设计工程师,EMC工程师,PI 工程师,SI工程师,项目经理,技术支持工程师,研发主管,研发总监,研发经理,测试经理,系统测试工程师等等培训课程大纲:一、DDRII 技术特点1.DDR /DDRII 特性比较;2.Banking结构;3.ODT 技术;4.OCD技术;5.DDR/DDRII功耗比较;二、DDRII PCB 设计技术1.拓扑结构设计;2.PCB叠层结构设计;3.阻抗设计;4.走线设计;5.线长匹配三、性能测试与分析技术1.DDRII 规范;2.电源测试与分析方法;3.信号质量测试与分析方法;4.时序分析方法;5.Margin分析方法;四、功能测试技术1.兼容性测试;2.稳定性测试;3.可靠性测试;五、芯片选择技术1.主要技术参数;2.参数对性能影响;3.工艺及封装;六、案例分析1.电源设计问题分析案例;2.串扰问题分析案例;3.叠层结构问题分析案例七、DDRIII设计技术1.信号分布;2.叠层结构;3.拓扑结构;4.阻抗设计;5.线宽间距;6.线长匹配;7.布线规则;讲师介绍---------------------------------资深老师**************************************************【温馨提示】:本公司竭诚为企业提供灵活定制化的内部培训和顾问服务,培训内容可根据客户的需要灵活设计,企业内部培训人数不受限制,培训时间由企业灵活制定。

DDR3的ODT详解

DDR3的ODT详解话说有三个人将被依次执行死刑,分别是牧师、律师、工程师。

牧师第一个被推向绞刑架。

侩子手拉动控制杆以抽出活板,但它失灵了。

牧师宣称这是上帝的旨意,要求得到释放,于是他获得了自由。

接着,律师走向了绞刑架。

侩子手再一次拉动了控制杆,但它仍然失灵,律师同样要求获得释放,因为他不能因为同一罪状被判两次死刑,于是他也获得了自由。

最后,轮到工程师了。

他上去对脚手架仔细检查了一遍,在侩子手还没动手之前,他抬起头大声说,“啊哈,是这里出了故障!”看到这里,大家应该知道结果了吧,真是好奇害死猫,有时工程师的强迫症来了真的会差点累及无辜。

这不,最近就遇到了一件很揪心的DDR3设计。

该DDR3主控为国外知名公司的芯片,功能强大而且比较成熟了,该设计为32位系统,一个主控芯片拖了4片DDR3颗粒,采用6层板,空间比较紧张。

这种常规设计对于我们的设计人员来说应该没有太大的问题,好歹我们一年也有好几千款的DDRx设计,在这个上面的技术积累还是很多的。

但是,这个设计的硬件工程师出于后期调试和EMI 的考虑在所有的数据信号线上加了串阻,这就使得原本就很紧张的布线空间捉襟见肘了,为此我们的设计人员叫苦不迭,这么紧张的空间怎么去绕等长呢?就算累到没朋友恐怕也很难保证很好的完成设计吧!无解了,只能请高速先生出招!首先查看了下主控芯片的数据手册,什么ODT、Write leveling 该有的功能都有,好家伙,这下有救了。

为什么呢?因为我们有任性的ODT功能。

ODT是On Die Termination的缩写,又叫片内端接,顾名思义,就是将端接电阻放在了芯片内部,这个功能只有在DDR2以上的数据信号才有,其他信号无此宠幸!有了这个功能,原本需要在PCB板上加串阻的数据信号就不用再额外添加端接了,因为芯片内部可以打开这个ODT端接功能,而且端接还可调,哈哈,确实有点任性。

下面是ODT 的端接示意图。

图一ODT端接示意图当数据读操作的时候,主控(FPGA或CPU)读取Memory颗粒的数据,此时主控为接收端,可以根据需要选择是否打开ODT;当数据写操作的时候,主控(FPGA或CPU)将数据写入到Memory颗粒,此时颗粒为接收端,也可以根据需要选择是否打开ODT,这种操作可以在寄存器内部实现控制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.DDR的发展:2003年秋季Intel公布了DDR2内存的发展计划。

而随着当时CPU 前端总线带宽的提高和高速局部总线的出现,内存带宽成为系统越来越大的瓶颈。

处于主流DDR技术已经发展到极至,因此DDR2脱颖而出。

DDR2的实际工作频率是DDR的两倍。

这得益于DDR2内存拥有两倍于标准DDR内存的4bit预读取能力。

下图为DDR和DDR2预读取能力的对比。

DDR2内存技术最大的突破点其实不在于用户们所认为的两倍于DDR的传输能力,而是在采用更低发热量、更低功耗的情况下(由2.5V降为1.8V),DDR2 可以获得更快的频率提升,突破标准DDR的400MHZ限制。

DDR内存通常采用TSOP芯片封装形式,这种封装形式可以很好的工作在200MHz上,当频率更高时,它过长的管脚就会产生很高的阻抗和寄生电容,这会影响它的稳定性和频率提升的难度。

这也就是 DDR的核心频率很难突破275MHZ的原因。

而DDR2内存均采用FBGA封装形式。

不同于目前广泛应用的 TSOP 封装形式,FBGA封装提供了更好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的发展提供了良好的保障。

2007年中Intel表示支持DDR3的发展,随后DDR3慢慢走上了历史的舞台,根据由JEDEC协会所制定的规格来看,由技术面来切入DDR3与DDR2的异同点,DDR3拥有高频率低电压的优点,DDR3可以比DDR2运作时省下约30%的电力,速度方面DDR3从800Mbps起跳最高可以至1600Mbps,几乎是DDR2的二倍速度,正因为高传输率的关系,DDR3可以在一个时序(Clock)之中传出8bit的数据,比起DDR2的4bit也是二倍的数据传输量,低电压更是DDR3的优势之一,1.5V 的电压比DDR2的1.8V降低了17%。

下面的图表总结了DDR,DDR2,以及DDR3的一些重要的区别:2、认识内存相关工作流程与参数首先,我们先了解一下内存的大体结构工作流程,这样会比较容量理解这些参数在其中所起到的作用。

这部分的讲述运用DDR3的简化时序图。

DDR3的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格。

和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。

对于内存,这个单元格可称为存储单元,那么这个表格(存储阵列)就是逻辑Bank (Logical Bank,下面简称Bank)。

DDR3内部Bank示意图,这是一个NXN的阵列,B代表Bank地址编号,C代表列地址编号,R代表行地址编号。

如果寻址命令是B1、R2、C6,就能确定地址是图中红格的位置目前DDR3内存芯片基本上都是8个Bank设计,也就是说一共有8个这样的“表格”。

寻址的流程也就是先指定Bank地址,再指定行地址,然后指列地址最终的确寻址单元。

目前DDR3系统而言,还存在物理Bank的概念,这是对内存子系统的一个相关术语,并不针对内存芯片。

内存为了保证CPU正常工作,必须一次传输完CPU 在一个传输周期内所需要的数据。

而CPU在一个传输周期能接受的数据容量就是CPU数据总线的位宽,单位是bit(位)。

控制内存与CPU之间数据交换的北桥芯片也因此将内存总线的数据位宽等同于CPU数据总线的位宽,这个位宽就称为物理Bank(Physical Bank,有的资料称之为Rank)的位宽。

目前这个位宽基本为64bit。

在实际工作中,Bank地址与相应的行地址是同时发出的,此时这个命令称之为“行激活”(Row Active)。

在此之后,将发送列地址寻址命令与具体的操作命令(是读还是写),这两个命令也是同时发出的,所以一般都会以“读/写命令”来表示列寻址。

根据相关的标准,从行有效到读/写命令发出之间的间隔被定义为tRCD,即RAS to CAS Delay(RAS至CAS延迟,RAS就是行地址选通脉冲,CAS就是列地址选通脉冲),我们可以理解为行选通周期。

tRCD是DDR的一个重要时序参数,广义的tRCD以时钟周期(tCK,Clock Time)数为单位,比如tRCD=3,就代表延迟周期为两个时钟周期,具体到确切的时间,则要根据时钟频率而定,DDR3-800,tRCD=3,代表30ns的延迟。

图中显示的是tRCD=3接下来,相关的列地址被选中之后,将会触发数据传输,但从存储单元中输出到真正出现在内存芯片的 I/O 接口之间还需要一定的时间(数据触发本身就有延迟,而且还需要进行信号放大),这段时间就是非常著名的 CL(CASLatency,列地址脉冲选通潜伏期)。

CL 的数值与 tRCD 一样,以时钟周期数表示。

如 DDR3-800,时钟频率为 100MHz,时钟周期为 10ns,如果 CL=2 就意味着 20ns 的潜伏期。

不过CL只是针对读取操作。

由于芯片体积的原因,存储单元中的电容容量很小,所以信号要经过放大来保证其有效的识别性,这个放大/驱动工作由S-AMP负责,一个存储体对应一个S-AMP通道。

但它要有一个准备时间才能保证信号的发送强度(事前还要进行电压比较以进行逻辑电平的判断),因此从数据I/O总线上有数据输出之前的一个时钟上升沿开始,数据即已传向S-AMP,也就是说此时数据已经被触发,经过一定的驱动时间最终传向数据I/O总线进行输出,这段时间我们称之为tAC(Access Time from CLK,时钟触发后的访问时间)。

图中标准CL=2,tAC=1目前内存的读写基本都是连续的,因为与CPU交换的数据量以一个Cache Line(即CPU内Cache的存储单位)的容量为准,一般为64字节。

而现有的Rank 位宽为8字节(64bit),那么就要一次连续传输8次,这就涉及到我们也经常能遇到的突发传输的概念。

突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输的周期数就是突发长度(Burst Lengths,简称BL)。

在进行突发传输时,只要指定起始列地址与突发长度,内存就会依次地自动对后面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址。

这样,除了第一笔数据的传输需要若干个周期(主要是之前的延迟,一般的是tRCD+CL)外,其后每个数据只需一个周期的即可获得。

突发连续读取模式:只要指定起始列地址与突发长度,后续的寻址与数据的读取自动进行,而只要控制好两段突发读取命令的间隔周期(与BL相同)即可做到连续的突发传输。

谈到了突发长度时。

如果BL=4,那么也就是说一次就传送4×64bit的数据。

但是,如果其中的第二笔数据是不需要的,怎么办?还都传输吗?为了屏蔽不需要的数据,人们采用了数据掩码(Data I/O Mask,简称DQM)技术。

通过DQM,内存可以控制I/O端口取消哪些输出或输入的数据。

这里需要强调的是,在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。

DQM 由北桥控制,为了精确屏蔽一个P-Bank位宽中的每个字节,每个DIMM有8个DQM信号线,每个信号针对一个字节。

这样,对于4bit位宽芯片,两个芯片共用一个DQM信号线,对于8bit位宽芯片,一个芯片占用一个DQM信号,而对于16bit位宽芯片,则需要两个DQM引脚。

在数据读取完之后,为了腾出读出放大器以供同一Bank内其他行的寻址并传输数据,内存芯片将进行预充电的操作来关闭当前工作行。

还是以上面那个Bank示意图为例。

当前寻址的存储单元是B1、R2、C6。

如果接下来的寻址命令是B1、R2、C4,则不用预充电,因为读出放大器正在为这一行服务。

但如果地址命令是B1、R4、C4,由于是同一Bank的不同行,那么就必须要先把R2关闭,才能对R4寻址。

从开始关闭现有的工作行,到可以打开新的工作行之间的间隔就是tRP(Row Precharge command Period,行预充电有效周期),单位也是时钟周期数。

在不同Bank间读写也是这样,先把原来数据写回,再激活新的Bank/Row。

数据选取脉冲(DQS)DQS是DDR中的重要功能,它的功能主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。

每一颗芯片都有一个DQS信号线,它是双向的,在写入时它用来传送由北桥发来的DQS信号,读取时,则由芯片生成DQS向北桥发送。

完全可以说,它就是数据的同步信号。

在读取时,DQS与数据信号同时生成(也是在CK与CK#的交叉点)。

而DDR 内存中的CL也就是从CAS发出到DQS生成的间隔,DQS生成时,芯片内部的预取已经完毕了,由于预取的原因,实际的数据传出可能会提前于DQS发生(数据提前于DQS传出)。

由于是并行传输,DDR内存对tAC也有一定的要求,对于DDR266,tAC的允许范围是±0.75ns,对于DDR333,则是±0.7ns,有关它们的时序图示见前文,其中CL里包含了一段DQS的导入期。

DQS在读取时与数据同步传输,那么接收时也是以DQS的上下沿为准吗?不,如果以DQS的上下沿区分数据周期的危险很大。

由于芯片有预取的操作,所以输出时的同步很难控制,只能限制在一定的时间范围内,数据在各I/O端口的出现时间可能有快有慢,会与DQS有一定的间隔,这也就是为什么要有一个tAC规定的原因。

而在接收方,一切必须保证同步接收,不能有tAC之类的偏差。

这样在写入时,芯片不再自己生成DQS,而以发送方传来的DQS为基准,并相应延后一定的时间,在DQS的中部为数据周期的选取分割点(在读取时分割点就是上下沿),从这里分隔开两个传输周期。

这样做的好处是,由于各数据信号都会有一个逻辑电平保持周期,即使发送时不同步,在DQS上下沿时都处于保持周期中,此时数据接收触发的准确性无疑是最高的。

在写入时,以DQS的高/低电平期中部为数据周期分割点,而不是上/下沿,但数据的接收触发仍为DQS的上/下沿3.容量的计算上图为X8data的单颗DDR3架构图,行(Row)地址线复用14根,列(Column)地址线复用10根,Bank数量为8个,IO Buffer 通过8组数位线(DQ0-DQ7)来完成对外的通信,故此单颗DDR3芯片的容量为2的14次方乘2的10次方乘8乘8,结果为1Gbit,因为1B包含8bit,1GB/8=128MB。

如果我们要做成容量为1GB的内存条则需要8颗这样的DDR3内存芯片,每颗芯片含8根数位线(DQ0-DQ7)则总数宽为64bit,这样正好用了一个Rank。

假果还用128MB的DDR3芯片去做2GB内存条,结果就会有所不同。

我们最好选用4根数位线(DQ0-DQ3),数量是16颗,这样也是用了一个Rank。