verilog中generate的使用(for循环的使用)

verilog genvr用法

verilog genvr用法genvar是Verilog中的一个特殊变量类型,它用于循环生成不同的信号或实例。

genvar通常与generate语句结合使用。

下面是genvar的一般用法:1. 声明genvar变量```genvar i;```2. 在generate语句中使用genvargenvar通常与for循环结合使用,用于生成多个信号或实例。

```generatefor (i = 0; i < N; i = i + 1) begin// 生成代码endendgenerate```在循环中,可以使用genvar变量i来生成不同的信号或实例。

可以通过改变循环的起始值、结束条件和步长来生成不同的序列。

3. 生成信号或实例在循环中可以使用genvar来生成不同的信号或实例。

生成信号:```generatefor (i = 0; i < N; i = i + 1) beginreg [7:0] data_i;// 生成不同的信号assign data_i = i;endendgenerate```生成实例:```generatefor (i = 0; i < N; i = i + 1) begin// 生成不同的实例full_adder my_adder(.a(in1[i]), .b(in2[i]), .cin(carry_in), .sum(sum[i+1]), .cout(carry_o ut[i+1]));endendgenerate```在上面的示例中,使用genvar i来生成了不同的信号data_i和实例my_adder。

总结:genvar用于循环生成不同的信号或实例,可以与generate语句结合使用。

通过改变循环的起始值、结束条件和步长,可以生成不同的序列。

在循环中使用genvar可以生成不同的信号或实例。

verilog中for循环的用法

verilog中for循环的用法

verilog是一种高级的硬件描述语言,它可以描述电路的

行为和功能。

verilog中的for循环是一种重要的控制结构,它可以实现多次重复执行某个操作,有效地完成复杂的电路设计。

首先,让我们来看一下verilog中for循环的基本语法结构:for(初始化表达式;循环条件;更新表达式){循环体},其

中for是关键字,初始化表达式是初始化循环变量的表达式,

循环条件是控制循环执行次数的表达式,更新表达式是更新循环变量的表达式,循环体是需要重复执行的操作。

以下是一个典型的verilog for循环的例子:for(i=0;i<4;i=i+1) begin a[i] <= b[i] + c[i]; end这个例子中,我们

将循环变量i初始化为

0,然后每次循环i都会增加

1,直到i的值变成

4,循环终止。

在每次循环的循环体中,我们将数组a的

某个元素等于数组b和数组c的相同位置的元素之和。

从上面的例子可以看出,for循环在verilog中极其重要,

它可以帮助我们有效地实现复杂的电路设计。

通过for循环,

我们可以实现多次重复执行某个操作,从而极大地减少程序的长度,提高程序的可读性,可维护性和可扩展性。

此外,verilog中的for循环还可以用于实现复杂的电路设计,例如,可以用for循环来实现多路复用器,可以用for循环实现多路分配器,可以用for循环实现循环变量的累加和累乘等等。

总之,verilog中的for循环是一种非常重要的控制结构,可以有效地实现复杂的电路设计,它的使用可以极大地提高程序的可读性,可维护性和可扩展性。

verilog generate写法

文章标题:深入探讨Verilog Generate写法在数字电路设计中,Verilog语言是一种常用的硬件描述语言,而Verilog中的generate语句则是一种非常强大的语法结构,可以实现代码的重复、参数化和灵活性。

本文将深入探讨Verilog中generate 语句的写法,帮助读者更好地理解和运用这一语法结构。

1. 了解Verilog Generate让我们了解一下Verilog Generate的基本概念。

Generate语句允许在编译时生成多个代码实例,这些实例的数量和结构可以根据参数进行控制。

这种特性使得Verilog代码在处理重复性结构时更加灵活和高效。

在实际的数字电路设计中,我们经常会遇到需要重复性构建模块的情况,而generate语句正是为了解决这一需求而设计的。

2. 基本的Generate写法在Verilog中,generate语句通常和for循环结合使用,以实现对模块的重复实例化。

我们可以使用generate语句来生成多个相同模块的实例,每个实例的参数可以根据循环变量进行设置。

以下是一个简单的Verilog Generate写法示例:```veriloggenvar i;generatefor (i = 0; i < N; i = i + 1) begin// 实例化模块,并设置参数module_name #(parameter_value) instance_name(.input(input_signal), .output(output_signal));endendgenerate```在这个示例中,我们使用generate语句结合for循环,实现了对模块的N次重复实例化。

通过设置不同的参数值,我们可以生成具有不同配置的模块实例,从而提高了代码的重用性和灵活性。

3. Generate的高级应用除了基本的循环实例化外,Verilog中的generate语句还支持更加复杂的应用。

generate always用法

generate always用法generate always用法什么是generate always?generate always是一种在Verilog HDL中常见的用法,它用于生成始终有效的组合逻辑电路。

在使用generate always时,无论何时发生信号变化,都会生成新的电路。

这种用法非常适用于需要在编译时生成多个例化模块实例的情况。

generate always的语法generate always的语法如下:generatealways @ (sensitivity_list)begin : label// 逻辑代码endendgenerate其中,sensitivity_list表示敏感信号列表,当列表中的信号发生变化时,逻辑代码将会执行。

generate always的常见用法1. 生成多实例模块generate always经常被用于生成多个实例模块,尤其是在嵌套的设计中。

通过使用generate always,可以轻松生成多个实例模块,而无需手动复制和修改代码。

module MyModule #(parameter N = 4);genvar i;generatefor (i = 0; i < N; i = i + 1) begin : gen_blockinst_module #(i) instance (.clk(clk), .data (data[i]));endendgenerateendmodule上述例子中,使用generate always和for循环生成了N个实例模块inst_module,并传入了不同的参数值i。

2. 生成位选择器generate always也可以用来生成位选择器,可以根据不同的输入信号选择不同的位。

这在需要对多个信号进行选择操作时非常有用。

module MyModule #(parameter N = 4);genvar i;wire [N-1:0] data_in;generatefor (i = 0; i < N; i = i + 1) begin : gen_block always @ (data_in[i])beginif (data_in[i])selected_data = data_in[i];endendendgenerateendmodule上述例子中,使用generate always和for循环生成了N个选择器,根据输入信号data_in的不同位选择不同的数据,并将其存储在selected_data中。

verilog for循环用法

verilog for循环用法

在Verilog中,for循环用于重复执行一段代码,以下是for循环的语法:

```verilog

for (initialize_expression; condition_expression;

update_expression)

begin

// 执行的代码

end

```

其中,`initialize_expression`用于初始化循环变量,

`condition_expression`是循环的条件,只有在条件为真时才会执行循环体中的代码,`update_expression`用于更新循环变量的值。

下面是一个示例,展示如何使用for循环来计算1到10的累加和:

```verilog

reg [7:0] sum;

initial

begin

sum = 0;

for (integer i = 1; i <= 10; i = i + 1)

begin

sum = sum + i;

end

$display("Sum: %d", sum);

end

```

在上述示例中,我们首先定义了一个8位的寄存器sum并将

其初始化为0。

然后使用for循环从1到10遍历,每次将i的

值加到sum中。

最后,使用$display来打印出计算得到的累加和。

请注意,for循环中的表达式可以是任意合法的Verilog表达式,不仅限于简单的增量操作。

veriloggenerate用法

`veriloggenerate` 是一个用于在Verilog 代码中生成硬件描述的指令。

它通常与`module`、`endmodule` 和`generate` 一起使用,以实现复杂的硬件设计。

使用方法如下:

1. 在Verilog 文件中包含所需的头文件和模块声明。

2. 使用`module` 关键字定义一个模块。

3. 在模块内部,使用`generate` 关键字指定要生成的硬件描述。

4. 使用`endmodule` 关键字结束模块定义。

5. 在顶层模块中实例化生成的硬件描述。

下面是一个简单的示例:

```verilog

// 包含所需的头文件

`include "defines.v"

`include "my_module.v"

module top;

// 实例化生成的硬件描述

my_hardware my_instance (

.clk(clk),

.rst(rst),

.data_in(data_in),

.data_out(data_out)

);

endmodule

```

在这个示例中,`my_hardware` 是一个由`my_module.v` 中的`generate` 指令生成的硬件描述。

在顶层模块`top` 中,我们实例化了`my_hardware` 并连接了相应的信号。

verilog的for循环的电路

文章标题:深入探讨Verilog中的for循环电路设计1. 引言Verilog作为一种硬件描述语言,广泛应用于数字电路设计和硬件描述。

其中,for循环是Verilog语言中常用的一种结构,可以用于迭代、控制和优化电路设计。

本文将深入探讨Verilog中for循环的电路设计,探讨其原理、应用和优化方法。

2. Verilog中的for循环在Verilog中,for循环是一种用于重复执行一定次数的语句块的控制结构。

它可以帮助设计者更高效地实现电路功能、减少代码量和提高设计灵活性。

在数字电路设计中,for循环可以应用于生成多路复用器、计数器、同步电路等模块,极大地方便了电路设计者。

3. for循环电路设计原理在Verilog中,for循环可以通过控制参数、计数器和条件判断来实现电路设计。

在生成多路复用器时,可以利用for循环依次控制各路输出的选择信号,从而实现多路复用功能。

通过对for循环的内部原理和电路结构进行深入理解,设计者可以更好地优化电路设计,提高电路的速度、面积和功耗等性能指标。

4. 应用实例以计数器为例,可以利用for循环来实现计数器的功能。

通过循环控制计数器的计数次数和输出信号,可以快速、灵活地实现各种计数器类型,如同步计数器、异步计数器等。

for循环还可以用于实现状态机、逻辑电路等模块,提高了Verilog在数字电路设计中的应用范围和灵活性。

5. 优化方法在实际电路设计中,for循环的设计和应用需要注意一些优化方法。

可以适当选择循环变量的范围和步进值,避免过多的嵌套循环和复杂的逻辑设计,以提高电路的性能和可维护性。

合理使用for循环可以减少冗余代码,提高设计的模块化和可扩展性。

6. 总结与展望Verilog中的for循环在数字电路设计中具有重要的作用,可以帮助设计者实现高效、灵活的电路设计。

通过深入理解for循环的原理和应用,设计者可以更好地优化电路设计,提高设计效率和质量。

未来,随着数字电路设计的需求不断增加,for循环在Verilog中的应用将会更加广泛,也需要不断进行优化和改进。

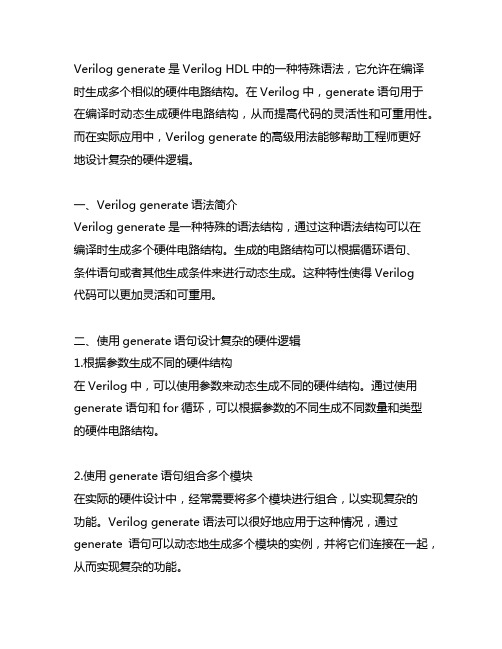

verilog generate的高级用法

Verilog generate是Verilog HDL中的一种特殊语法,它允许在编译时生成多个相似的硬件电路结构。

在Verilog中,generate语句用于在编译时动态生成硬件电路结构,从而提高代码的灵活性和可重用性。

而在实际应用中,Verilog generate的高级用法能够帮助工程师更好地设计复杂的硬件逻辑。

一、Verilog generate语法简介Verilog generate是一种特殊的语法结构,通过这种语法结构可以在编译时生成多个硬件电路结构。

生成的电路结构可以根据循环语句、条件语句或者其他生成条件来进行动态生成。

这种特性使得Verilog代码可以更加灵活和可重用。

二、使用generate语句设计复杂的硬件逻辑1.根据参数生成不同的硬件结构在Verilog中,可以使用参数来动态生成不同的硬件结构。

通过使用generate语句和for循环,可以根据参数的不同生成不同数量和类型的硬件电路结构。

2.使用generate语句组合多个模块在实际的硬件设计中,经常需要将多个模块进行组合,以实现复杂的功能。

Verilog generate语法可以很好地应用于这种情况,通过generate语句可以动态地生成多个模块的实例,并将它们连接在一起,从而实现复杂的功能。

3.使用generate语句实现复杂的状态机状态机是数字逻辑电路中常见的一种电路结构,用来实现有限状态机的控制功能。

在Verilog中,可以使用generate语句动态生成多个状态机的实例,并将它们连接在一起,从而实现复杂的控制逻辑。

三、Verilog generate语法的优势1.提高代码的灵活性和可重用性使用Verilog generate语法可以使得代码更加灵活和可重用。

通过动态生成多个硬件电路结构,可以适应不同的设计需求,并且可以在不同的项目中重复使用。

2.简化复杂逻辑的设计过程对于一些复杂的硬件逻辑,使用Verilog generate语法可以大大简化设计的过程。

Verilog中generate的用法

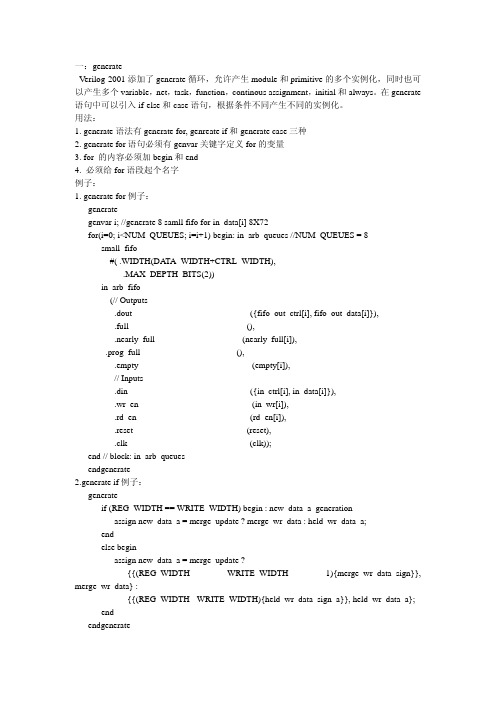

一:generateVerilog-2001添加了generate循环,允许产生module和primitive的多个实例化,同时也可以产生多个variable,net,task,function,continous assignment,initial和always。

在generate 语句中可以引入if-else和case语句,根据条件不同产生不同的实例化。

用法:1. generate语法有generate for, genreate if和generate case三种2. generate for语句必须有genvar关键字定义for的变量3. for 的内容必须加begin和end4. 必须给for语段起个名字例子:1. generate for例子:generategenvar i; //generate 8 samll fifo for in_data[i] 8X72for(i=0; i<NUM_QUEUES; i=i+1) begin: in_arb_queues //NUM_QUEUES = 8 small_fifo#( .WIDTH(DATA_WIDTH+CTRL_WIDTH),.MAX_DEPTH_BITS(2))in_arb_fifo(// Outputs.dout ({fifo_out_ctrl[i], fifo_out_data[i]}),.full (),.nearly_full (nearly_full[i]),.prog_full (),.empty (empty[i]),// Inputs.din ({in_ctrl[i], in_data[i]}),.wr_en (in_wr[i]),.rd_en (rd_en[i]),.reset (reset),.clk (clk));end // block: in_arb_queuesendgenerate2.generate if例子:generateif (REG_WIDTH == WRITE_WIDTH) begin : new_data_a_generationassign new_data_a = merge_update ? merge_wr_data : held_wr_data_a;endelse beginassign new_data_a = merge_update ?{{(REG_WIDTH - WRITE_WIDTH - 1){merge_wr_data_sign}}, merge_wr_data} :{{(REG_WIDTH - WRITE_WIDTH){held_wr_data_sign_a}}, held_wr_data_a};endendgenerate3.generate还可以进行多个assign赋值!module anytest_v(input clk,input[7:0] datain,output[7:0] dataout,output finish);wire[7:0] mem[31:0];wire[32*8-1:0] xxx;//reg[7:0] i;generategenvar i;for(i=0;i<=31;i=i+1)begin :wiertechassign mem[i]= 8'b0;endendgenerateendmoduleps: 对于a[8*i+:8]this is the so-called "Indexed vector part selects"在Verilog-1995中,可以选择向量的任一位输出,也可以选择向量的连续几位输出,不过此时连续几位的始末数值的index需要是常量。

verilog for语句

verilog for语句Verilog的for语句用于循环执行一段代码指定的次数。

for语句的语法如下:```for (循环变量初始化; 循环条件; 循环变量更新) begin// 代码块end```其中:- 循环变量初始化:在进入循环前执行一次的初始化表达式。

- 循环条件:在每次迭代前都会被检查的表达式。

只要条件为真,代码块内的语句就会被执行。

- 循环变量更新:在每次迭代结束后更新循环变量的表达式。

以下是一个用Verilog的for语句实现简单计数的示例:```reg [7:0] count;always @(posedge clk) begincount <= 8'd0; // 初始化计数变量for (count=8'd0; count<8'd10; count=count+1) begin$display("Count: %d", count); // 打印当前计数值endend```本示例中,每当时钟上升沿到来时,计数变量`count`会被初始化为0,并自增1。

在循环内部,会打印当前的计数值。

循环会执行10次(0到9),并在控制台上打印计数值。

需要注意的是,Verilog的for循环在硬件描述语言中的行为与传统编程语言中的for循环不同。

在Verilog中,for循环是硬件描述的一种方式,不会显式地生成循环结构。

取而代之的是,每次循环中的代码会被展开并并行执行,类似于插入多个连续的语句。

因此,在使用Verilog的for循环时,需要确保生成的硬件电路表现与预期一致。

verilogfor用法

verilogfor用法Verilog 是硬件描述语言(Hardware Description Language,HDL)之一,用于描述数字电路和系统的行为和结构。

它是一种高级编程语言,用于设计和模拟硬件电路。

Verilog for循环是一种重复执行特定代码块的控制结构。

它可用于设计和实现各种数字电路功能。

for循环语法如下:```for (initialization; condition; increment) begin// code to be executedend```在for循环中,初始化(initialization)块用于设置循环变量的初始值。

条件(condition)是一个逻辑表达式,用于检查循环是否应该继续执行。

增量(increment)用于指定每次迭代后循环变量的变化方式。

例如,在Verilog中使用for循环创建一个简单的计数器如下所示:```reg [3:0] counter;for (counter=4'b0000; counter<4'b1111; counter=counter+1) begin// code to be executedendend```在上面的例子中,我们使用一个4位的寄存器作为计数器。

在时钟上升沿触发的always块内,我们使用for循环从0000计数到1111、在每次循环迭代中,我们可以在代码块中执行所需的操作。

for循环还可以与其他控制结构(例如if语句)结合使用,以实现更复杂的逻辑。

例如,以下代码使用for循环和if语句实现了一个简单的计数器,并在计数到特定值时输出一个信号:```reg [3:0] counter;wire output;for (counter=4'b0000; counter<4'b1111; counter=counter+1) beginif (counter == 4'b1100) beginoutput = 1'b1;end else beginoutput = 1'b0;endend```在上面的例子中,当计数器的值等于1100时,输出信号output被设置为1、否则,输出信号被设置为0。

[转帖]Verilog的语法及generate使用

![[转帖]Verilog的语法及generate使用](https://img.taocdn.com/s3/m/2da416d78ad63186bceb19e8b8f67c1cfad6ee22.png)

[转帖]Verilog的语法及generate使⽤verilog 单独⽂件调⽤ include来源:Verilog中可以使⽤预处理命令 `include "⽂件名" 来包含新⽂件。

`include "⽂件名"的位置需要在 module声明之后。

这⾥举个例⼦,param.h存放了参数LENTH,顶层mult.v使⽤了它。

mult.v代码如下1module mult (2input clk,3input rst,4input [LENTH-1:0] A,5input [LENTH-1:0] B,6output [LENTH-1:0] C7 );89 `include"param.h"1011reg [LENTH-1:0] c_reg;1213always@(posedge clk or negedge rst)14if(rst == 1'b0)begin15 c_reg <= 32'b0;16end17else begin18 c_reg <= A*B;19end2021assign C = c_reg;2223endmodulearam.h代码如下parameter LENTH = 32;2014-04-10 15:39:17周四来源:verilog 条件编译命令`ifdef、`else、`endif 的应⽤(经常⽤于主程序中添加测试信息。

)通常在Verilog HDL程序中⽤到`ifdef、`else、`endif编译命令的情况有以下⼏种:• 选择⼀个模块的不同代表部分。

• 选择不同的时序或结构信息。

• 对不同的EDA⼯具,选择不同的激励。

1module ifdef_test(out);2output out;3 `define wow4 `define nest_one5 `define second_nest6 `define nest_two7 `ifdef wow8initial $display("wow is defined");9 `ifdef nest_one10initial $display("nest_one is defined");11 `ifdef nest_two12initial $display("nest_two is defined");13 `else14initial $display("nest_two is not defined");15 `endif16 `else17initial $display("nest_one is not defined");18 `endif19 `else20initial $display("wow is not defined");21 `ifdef second_nest22initial $display("second_nest is defined");23 `else24initial $display("second_nest is not defined");View Code1module ifdef_test(out);2output out;3 `define wow4 `define nest_one5 `define second_nest6 `define nest_two7 `ifdef wow8initial $display("wow is defined");9 `ifdef nest_one10initial $display("nest_one is defined");11 `ifdef nest_two12initial $display("nest_two is defined");13 `else14initial $display("nest_two is not defined");15 `endif16 `else17initial $display("nest_one is not defined");18 `endif19 `else20initial $display("wow is not defined");21 `ifdef second_nest22initial $display("second_nest is defined");23 `else24initial $display("second_nest is not defined");25 `endif26 `endif27endmodule运⾏结果为:# wow is defined# nest_one is defined# nest_two is defined2013-06-28 08:32:40 周五1、常量(constant)、参数(parameter)、块标号(block label)最好使⽤⼤写命名,变量(variable)、实例(instance)、结构代码1.1 模-m计数器(缺省为模-10计数器)module mod_m_bin_counter#(parameter M=10) // mod-M(// global clock and asyn resetinput clk,input rst_n,// counter interfaceoutput max_tick,output min_tick,output [N-1:0] q);// signal declarationlocalparam N = log2(M); // number of bits in counterreg [N-1:0] r_reg;wire [N-1:0] r_next;// body// registeralways@(posedge clk, negedge rst_n)if(!rst_n)r_reg <= 0;elser_reg <= r_next;// next-state logicassign r_next = (r_reg == (M-1)) ? 0 : r_reg + 1'b1;//output logicassign q = r_reg;assign max_tick = (r_reg == (M-1)) ? 1'b1 : 1'b0;// log2 constant functionfunction integer log2(input integer n);for(i=0; 2**i<n; i = i + 1)log2 = i + 1;endendfunctionendmodule根据这个模-m计数器,我们再写⼀个testbench。

Verilog generate语句的用法

Verilog-2001之generate语句的用法Verilog-1995 支持通过以声明实例数组的形式对primitive和module进行复制结构建模。

而在Verilog-2001里,新增加的generate语句拓展了这种用法(其思想来源于VHDL语言)。

除了允许复制产生primitive和module的多个实例化,同时也可以复制产生多个net、reg、parameter、assign、always、initial、task、function。

在generate中引入了一种新的变量类型:genvar,用以在generate-for语句中声明一个正整数的索引变量(如果将“X”或“Z”或者“负值”赋给genvar 变量,将会出错)。

genvar 变量可以声明在generate语句内,也可以声明在generate语句外。

generate语句有generate-for、genreate-if和generate-case三种语句;generate-for语句① generate-for语句必须用genvar关键字定义for的索引变量;② for的内容必须用begin…end块包起来,哪怕只有一句;③begin…end块必须起个名字;例1:一个参数化的gray-code to binary-code 转换器;这里采用复制产生多个assign语句的形式来实现;module gray2bin1 (bin, gray);parameter SIZE = 8; // this module is parameterizableoutput [SIZE-1:0] bin;input [SIZE-1:0] gray;genvar i;generatefor(i=0; i<SIZE; i=i+1)begin: bitassign bin[i] = ^gray[SIZE-1:i];endendgenerateendmodule等同于下面的语句:assign bin[0] = ^gray[SIZE-1:0];assign bin[1] = ^gray[SIZE-1:1];assign bin[2] = ^gray[SIZE-1:2];assign bin[3] = ^gray[SIZE-1:3];assign bin[4] = ^gray[SIZE-1:4];assign bin[5] = ^gray[SIZE-1:5];assign bin[6] = ^gray[SIZE-1:6];assign bin[7] = ^gray[SIZE-1:7];例2:还是例1的gray-code to binary-code 转换器;不过这里采用复制产生多个always语句的形式来实现;module gray2bin2 (bin, gray);parameter SIZE = 8; // this module is parameterizableoutput [SIZE-1:0] bin;input [SIZE-1:0] gray;reg [SIZE-1:0] bin;genvar i;generatefor(i=0; i<SIZE; i=i+1)begin: bitalways @(gray[SIZE-1:i]) // fixed part selectbin[i] = ^gray[SIZE-1:i];endendgenerateendmodule等同于下面的语句:always @(gray[SIZE-1:0]) // fixed part selectbin[0] = ^gray[SIZE-1:0];always @(gray[SIZE-1:1]) // fixed part selectbin[1] = ^gray[SIZE-1:1];always @(gray[SIZE-1:2]) // fixed part selectbin[2] = ^gray[SIZE-1:2];always @(gray[SIZE-1:3]) // fixed part selectbin[3] = ^gray[SIZE-1:3];always @(gray[SIZE-1:4]) // fixed part selectbin[4] = ^gray[SIZE-1:4];always @(gray[SIZE-1:5]) // fixed part selectbin[5] = ^gray[SIZE-1:5];always @(gray[SIZE-1:6]) // fixed part selectbin[6] = ^gray[SIZE-1:6];always @(gray[SIZE-1:7]) // fixed part selectbin[7] = ^gray[SIZE-1:7];例3:一个行波进位加法器,在begin…end内部定义局部变量,并且在generate语句内定义genvar变量;module addergen1 (co, sum, a, b, ci);parameter SIZE = 4;output [SIZE-1:0] sum;output co;input [SIZE-1:0] a, b;input ci;wire [SIZE :0] c;assign c[0] = ci;generategenvar i;for(i=0; i<SIZE; i=i+1)begin: bitwire t1, t2, t3; // generated net declarationxor g1 (t1, a[i], b[i]);xor g2 (sum[i], t1, c[i]);and g3 (t2, a[i], b[i]);and g4 (t3, t1, c[i]);or g5 (c[i+1], t2, t3);endendgenerateassign co = c[SIZE];endmodule等同于下面的语句:wire bit[0].t1, bit[0].t2, bit[0].t3;xor bit[0].g1 (bit[0].t1, a[0], b[0]);xor bit[0].g2 (sum[0], bit[0].t1, c[0]);and bit[0].g3 (bit[0].t2, a[0], b[0]);and bit[0].g4 (bit[0].t3, bit[0].t1, c[0]);or bit[0].g5 (c[0+1], bit[0].t2, bit[0].t3);wire bit[1].t1, bit[1].t2, bit[1].t3;xor bit[1].g1 (bit[1].t1, a[1], b[1]);xor bit[1].g2 (sum[1], bit[1].t1, c[1]);and bit[1].g3 (bit[1].t2, a[1], b[1]);and bit[1].g4 (bit[1].t3, bit[1].t1, c[1]);or bit[1].g5 (c[1+1], bit[1].t2, bit[1].t3);wire bit[2].t1, bit[2].t2, bit[2].t3;xor bit[2].g1 (bit[2].t1, a[2], b[2]);xor bit[2].g2 (sum[2], bit[2].t1, c[2]);and bit[2].g3 (bit[2].t2, a[2], b[2]);and bit[2].g4 (bit[2].t3, bit[2].t1, c[2]);or bit[2].g5 (c[2+1], bit[2].t2, bit[2].t3);wire bit[3].t1, bit[3].t2, bit[3].t3;xor bit[3].g1 (bit[3].t1, a[3], b[3]);xor bit[3].g2 (sum[3], bit[3].t1, c[3]);and bit[3].g3 (bit[3].t2, a[3], b[3]);and bit[3].g4 (bit[3].t3, bit[3].t1, c[3]);or bit[3].g5 (c[3+1], bit[3].t2, bit[3].t3);这样,复制产生的实例名称为:xor gates: bit[0].g1 bit[1].g1 bit[2].g1 bit[3].g1 bit[0].g2 bit[1].g2 bit[2].g2 bit[3].g2 and gates: bit[0].g3 bit[1].g3 bit[2].g3 bit[3].g3bit[0].g4 bit[1].g4 bit[2].g4 bit[3].g4 or gates: bit[0].g5 bit[1].g5 bit[2].g5 bit[3].g5复制产生的wire组为:bit[0].t1 bit[1].t1 bit[2].t1 bit[3].t1bit[0].t2 bit[1].t2 bit[2].t2 bit[3].t2bit[0].t3 bit[1].t3 bit[2].t3 bit[3].t3可见,给begin…end块命名的用途!例4:一个行波进位加法器,使用外部定义的变量,这样就不会对外部变量做变动;module addergen1 (co, sum, a, b, ci);parameter SIZE = 4;output [SIZE-1:0] sum;output co;input [SIZE-1:0] a, b;input ci;wire [SIZE :0] c;wire [SIZE-1:0] t [1:3];genvar i;assign c[0] = ci;generatefor(i=0; i<SIZE; i=i+1)begin: bitxor g1 ( t[1][i], a[i], b[i]);xor g2 ( sum[i], t[1][i], c[i]);and g3 ( t[2][i], a[i], b[i]);and g4 ( t[3][i], t[1][i], c[i]);or g5 ( c[i+1], t[2][i], t[3][i]);endendgenerateassign co = c[SIZE];endmodule这样,复制产生的实例名称为:xor gates: bit[0].g1 bit[1].g1 bit[2].g1 bit[3].g1bit[0].g2 bit[1].g2 bit[2].g2 bit[3].g2 and gates: bit[0].g3 bit[1].g3 bit[2].g3 bit[3].g3bit[0].g4 bit[1].g4 bit[2].g4 bit[3].g4 or gates: bit[0].g5 bit[1].g5 bit[2].g5 bit[3].g5而外部变量t与a,b,sum等一样,没有复制产生新的变量组例5:多层generate语句所复制产生的实例命名方式;parameter SIZE = 2;genvar i, j, k, m;generatefor(i=0; i<SIZE; i=i+1)begin: B1 // scope B1[i]M1 N1(); // instantiates B1[i].N1for(j=0; j<SIZE; j=j+1)begin: B2 // scope B1[i].B2[j]M2 N2(); // instantiates B1[i].B2[j].N2for(k=0; k<SIZE; k=k+1)begin: B3 // scope B1[i].B2[j].B3[k]M3 N3(); // instantiates B1[i].B2[j].B3[k].N3 endendif(i>0)for(m=0; m<SIZE; m=m+1)begin: B4 // scope B1[i].B4[m]M4 N4(); // instantiates B1[i].B4[m].N4endendendgenerate下面是复制产生的实例名称的几个例子:B1[0].N1 B1[1].N1B1[0].B2[0].N2 B1[0].B2[1].N2B1[0].B2[0].B3[0].N3 B1[0].B2[0].B3[1].N3B1[0].B2[1].B3[0].N3B1[1].B4[0].N4 B1[1].B4[1].N4generate-if语句根据条件不同产生不同的实例化,即根据模块参数(常量)的条件是否满足来选择其中一段代码生成相应的电路,不如`ifdef …`elsif …`else …`endif;例1:module generate_if (a,b,c,y);input a,b,c;output y;localparam SIZE = 12; // 参数常量generateif (SIZE < 8)assign y = a & b & c;else if (SIZE == 8)assign y = a & b | c;elseassign y = a | b | c; // 最后该语句生成电路;endgenerateendmodule例2:module multiplier(a,b,product);parameter a_width = 8, b_width = 8;localparam product_width = a_width+b_width;// localparam can not be modified directly with the defparam statement or the module instance statement,它是内部使用的局部参数 # input [a_width-1:0] a;input [b_width-1:0] b;output [product_width-1:0] product;generateif((a_width < 8) || (b_width < 8))CLA_multiplier #(a_width,b_width) u0(a, b, product);// instantiate a CLA multiplierelseWALLACE_multiplier #(a_width,b_width)u1(a,b,product);// instantiate a Wallace-tree multiplierendgenerate// The generated instance name is u1endmodule注意:这里的条件都是常量条件,非常量条件不能综合;generate-case语句跟generate-if语句一样的用法,只是采用case语句的形式。

verilog循环语句的使用

verilog循环语句的使用

在Verilog中,循环语句主要有`for`循环和`while`循环两种形式。

1. `for`循环:用于执行一组语句特定次数。

`for`循环的语法如下:

verilog

for (初始化语句; 终止条件; 递增语句) begin

循环体语句

end

其中,初始化语句用于初始化循环计数变量,终止条件用于判断跳出循环的条件,递增语句用于更新循环计数变量的值。

示例:

verilog

for (i = 0; i < 8; i = i + 1) begin

循环体语句

end

2. `while`循环:用于在满足条件时重复执行一组语句。

`while`循环的语法如下:verilog

while (条件) begin

循环体语句

end

其中,条件是一个逻辑表达式,当条件为真时,循环体语句会被重复执行。

示例:

verilog

while (i < 8) begin

循环体语句

i = i + 1;

end

需要注意的是,在Verilog中,循环语句的使用必须遵守以下规则:

- 循环体语句必须被`begin`和`end`包围,用于表示循环体的开始和结束。

- 循环变量需要在循环之前进行初始化,并在循环体内部进行递增或递减等操作,否则可能会导致无限循环。

在实际的Verilog代码中,循环语句通常用于生成重复的硬件结构、模拟连续时间域或执行算法等应用。

verilog generate函数

verilog generate函数Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。

在Verilog中,有一种特殊的函数——generate函数,用于动态生成代码。

generate函数可以根据一组参数创建模块或语句。

本文将介绍generate函数的使用。

一、generate函数的声明generate函数的语法格式如下:generate// 语句或模块的参数列表endgenerate在生成的代码块中,可以包含各种语句和模块,这些语句和模块都将被重复生成。

通常情况下,generate块内的代码是根据其参数进行参数化的。

二、generate函数的类型generate函数有两种类型,分别为generate语句和generate模块。

generate语句用于重复执行Verilog的内置语句,而generate模块用于生成Verilog的模块。

generate语句和generate模块之间的差异比较小,它们都具有相同的语法结构。

三、generate函数的应用1、generate语句的应用generate语句主要用于生成一些相似性很强的代码。

假设我们需要生成一个包含N个寄存器的模块,那么使用generate语句可以轻松实现。

(1)使用generate语句生成N个寄存器:generatefor (i = 0; i < N; i = i + 1) begin: reg_blockreg [7:0] reg_i;endendgenerate(2)使用生成的寄存器:reg_block[0].reg_i = 8'hFF;reg_block[1].reg_i = 8'hFC;……reg_block[N-1].reg_i = 8'hD7;2、generate模块的应用generate模块用于生成多个模块,比如我们需要某种具有相同功能的模块,那么可以使用generate模块来生成这些模块。

verilog控制端口数量的语句

verilog控制端口数量的语句在Verilog中,控制端口数量的语句可以通过使用生成语句和条件语句来实现。

下面是一些示例:1. 使用生成语句生成多个控制端口:```veriloggenvar i;generatefor (i = 0; i < N; i = i + 1) begin : control_portsassign control[i] = enable ? data_in : 0;endendgenerate```上述代码使用generate语句和for循环生成了N个控制端口。

根据条件enable的值,控制端口将连接到data_in或者置为0。

2. 使用条件语句实现不同数量的控制端口:```verilogalways @ (enable or data_in) beginif (enable)case (num_ports)1: control[0] = data_in;2: begincontrol[0] = data_in[0];control[1] = data_in[1];end3: begincontrol[0] = data_in[0];control[1] = data_in[1];control[2] = data_in[2];end// 更多控制端口的情况...endcaseelsecontrol = 0;end```上述代码使用条件语句根据num_ports的值来选择不同数量的控制端口。

根据enable的值,控制端口将连接到相应的data_in信号,或者置为0。

3. 使用参数化模块实现可配置的控制端口数量:```verilogmodule control_module #(parameter NUM_PORTS = 4) (input wire enable,input wire [NUM_PORTS-1:0] data_in,output wire [NUM_PORTS-1:0] control);assign control = enable ? data_in : 0;endmodule```上述代码定义了一个参数化模块control_module,可以通过参数NUM_PORTS来配置控制端口的数量。

generate for语句用法

generate for语句用法

for语句是一种循环结构,在编程中常用来重复执行一段代码,直到达到指定的条件。

for语句的基本用法如下:

1. 使用for循环遍历一个集合或序列:

```

for item in sequence:

# 代码块

```

这种用法适用于需要对一个列表、元组、字符串或其他可迭代对象中的每个元素进行操作的情况。

循环将在每次迭代时将一个元素赋值给变量item,并执行代码块。

2. 使用for循环遍历一个范围:

```

for i in range(start, stop, step):

# 代码块

```

这种用法适用于需要按照指定的步长从一个起始值循环递增或递减到一个结束值的情况。

循环将在每次迭代时将当前值赋值给变量i,并执行代码块。

3. 结合else语句使用for循环:

```

for item in sequence:

# 代码块

else:

# 代码块

```

当for循环中的所有迭代都完成后,将执行else块中的代码。

这种用法在需要在循环结束后执行一些操作时非常有用。

需要注意的是,Python中的for循环实际上是遍历一个可迭代

对象,在每次迭代中将对象中的元素赋值给指定的变量。

因此,for循环不像某些其他编程语言中的循环那样需要指定循环的

次数。

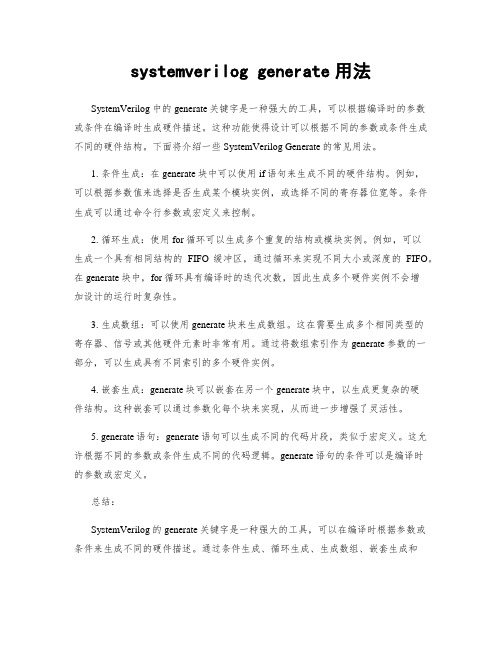

systemverilog generate用法

systemverilog generate用法SystemVerilog中的generate关键字是一种强大的工具,可以根据编译时的参数或条件在编译时生成硬件描述。

这种功能使得设计可以根据不同的参数或条件生成不同的硬件结构。

下面将介绍一些SystemVerilog Generate的常见用法。

1. 条件生成:在generate块中可以使用if语句来生成不同的硬件结构。

例如,可以根据参数值来选择是否生成某个模块实例,或选择不同的寄存器位宽等。

条件生成可以通过命令行参数或宏定义来控制。

2. 循环生成:使用for循环可以生成多个重复的结构或模块实例。

例如,可以生成一个具有相同结构的FIFO缓冲区,通过循环来实现不同大小或深度的FIFO。

在generate块中,for循环具有编译时的迭代次数,因此生成多个硬件实例不会增加设计的运行时复杂性。

3. 生成数组:可以使用generate块来生成数组。

这在需要生成多个相同类型的寄存器、信号或其他硬件元素时非常有用。

通过将数组索引作为generate参数的一部分,可以生成具有不同索引的多个硬件实例。

4. 嵌套生成:generate块可以嵌套在另一个generate块中,以生成更复杂的硬件结构。

这种嵌套可以通过参数化每个块来实现,从而进一步增强了灵活性。

5. generate语句:generate语句可以生成不同的代码片段,类似于宏定义。

这允许根据不同的参数或条件生成不同的代码逻辑。

generate语句的条件可以是编译时的参数或宏定义。

总结:SystemVerilog的generate关键字是一种强大的工具,可以在编译时根据参数或条件来生成不同的硬件描述。

通过条件生成、循环生成、生成数组、嵌套生成和generate语句,设计人员可以更灵活地创建硬件结构,并根据不同的参数和条件进行优化和调整。

这些功能使得SystemVerilog在设计复杂的硬件系统时非常有用。

verilog generate for 例化模块

verilog generate for 例化模块Generate statements in Verilog are used to instantiate multiple copies of a module with different parameter values or configurations. This allows for code reuse and simplification of design.To instantiate a module using generate statements, you need to define the module inside a generate block and use generate loops to iterate over different parameter values or configurations. Here is an example of how to use generate statements to instantiate a module called"my_module" multiple times:verilogmodule my_module #(parameter WIDTH = 4) (input [WIDTH-1:0] A,input [WIDTH-1:0] B,output [WIDTH-1:0] C);module logic goes hereendmodulemodule top_module;Example using generate statements to instantiate multiple copies of my_modulegenerategenvar i;for (i = 0; i < 4; i = i + 1) begin : gen_blockmy_module #(i+1) m (.A(A),.B(B),.C(C[i]));endendgeneraterest of the top module codeendmoduleIn this example, the module "my_module" has a parameter "WIDTH"which determines the bit width of its inputs and outputs. We use the generate statement to instantiate four copies of "my_module" with different WIDTH values (1, 2, 3, 4), and connect them to the inputs A and B, and the output C.Note that the generate statement is defined inside the "top_module" module, and the instantiated modules are enclosed within a generate block named "gen_block". The parameter values (i+1) for the instantiated modules are determined using the "genvar" variable "i".This is a simple example, but you can use generate statements to instantiate modules with more complex configurations or hierarchical structures.。