VS1053原理图

四位移位寄存器

摘要当前,电子信息化高速发展,电子产品成了日常生活中必不可少的一部分。

移位寄存器在大部分电子产品中是必不可少的一部分。

本论文介绍了实现并行存取的四位移位寄存器的设计过程,从电路的构思到整个电路的完成以及其版图的设计都有一个详细的描述。

所设计的寄存器在时钟脉冲的控制下,实现数据的并行输入、并行输出,串行输入并行输出等功能。

整个设计过程全部在LINUX系统下用Cadence软件进行设计的,用Cadence软件进行电路设计并仿真。

最后,利用Cadence软件进行版图的设计,电气规则的检查和LVS的对比匹配验证。

关键词:寄存器;并行存取;版图AbstractAt present, the rapid development of electronic information technology, electronics has become an indispensable part of daily life. Most of the shift register in electronic products is essential. This paper describes the realization of access to the four parallel shift register the design process, from concept to the circuit as a whole circuit of its territory and the completion of the design has a detailed description. The design of the register under the control of the clock, the parallel data input, output parallel, serial input parallel output functions. The entire design process in LINUX system with Cadence software designed and was used Cadence software for circuit design and simulation. Finally, use Cadence software to design the territory, electrical inspection rules and LVS comparison of the match to verify.Key words:register; parallel access; territory目录引言 (1)1 设计要求 (1)2 电路构思及其理论 (1)2.1 设计思路 (1)2.2 设计构思的理论依据 (2)2.2.1 寄存器描述 (2)2.2.2 移位寄存器的特点和分类 (2)3 系统电路的设计及原理说明 (2)3.1 系统框图及说明 (2)3.2 电路设计说明 (3)3.3 关键器件介绍 (4)3.3.1 边沿D触发器 (5)3.3.2 3个二输入与非门构成的选择器 (6)4 仿真验证叙述及效果分析 (6)4.1 电路仿真 (6)4.2电路仿真结果分析 (6)5 工程设计 (7)5.1 Cadence软件介绍 (7)5.2 电路设计 (7)5.3 版图设计及验证 (8)5.3.1 版图设计 (8)5.3.2 版图验证 (9)6 调试测试分析 (10)7 结束语 (10)参考文献 (11)附录 (12)引言当今电子信息化的社会,电子产品在日常生活中随处可见。

基于VS1053芯片的录音装置设计

硬 件 部分 介 绍 : 本 次 设 计所 做 的是 耩 于 S T M 3 2 的 录 音器 ,解 码 芯 片 V S 1 0 5 3 的作 用 不 言而 喻,因为此次录 音文件是保存在S D 卡 上的,自然少不 了对s D 卡的 介 绍。S T M 3 2 F 1 0 3 系列微处 理器是首款基 于A R M v 7 一 M 体 系结构 的3 2 位标 准R I S C ( 精 简指令集 )处理器 ,提供很高的代 码效率,在通常8 位和 l 6 位 系统 的存储空 间上发挥 了A R M 内核的高性能。该系列微处理器工 作频率为7 2 t  ̄ i z , 内置 高达 1 2 8 K 字 节 的F l a s h 存储器 。 其 内 部 结构 图如 图 l 所示:

P V I ) f 辘 电 瓶 扮 刺 嚣

RI ' C 时时. I 呻 A  ̄ : R T C州 僻 的 舟础 映 删 鞠 雠 P OR: 上 电 位

!

嫡

蒜 t %

潞鹰 慧瑚. 荦电 2O , 6、 f

e 1 ) R : 电 位

旺‘ ¨ 现l 拜礴锚帮

。

u

1 O . 内含能驱动3 O欧负载的耳机驱动器; l 1 . 模拟,数字,i / o单独供 电; 1 2 . 为 用户 代 码 和 数据 准 备 的 1 6 K B 片 上R A M 1 3 . 可 扩展 外 部 D A C 的I 2 S 接 口: l 4 . 用 于控 制 和 数据 的 串行 接 口 ( S P I ): 1 5 . 可 被用 作 微 处 理器 的从 机 ; l 6 . 特 殊应 用 的 S P I F l a s h  ̄ l 导; l 7 . 供 调试 用 途 的U A R T 接口: l 8 . 新功能可 以通过软件和 8 G P I O添加。 V S 1 0 5 3 解 码 芯 片 电路 原牲利

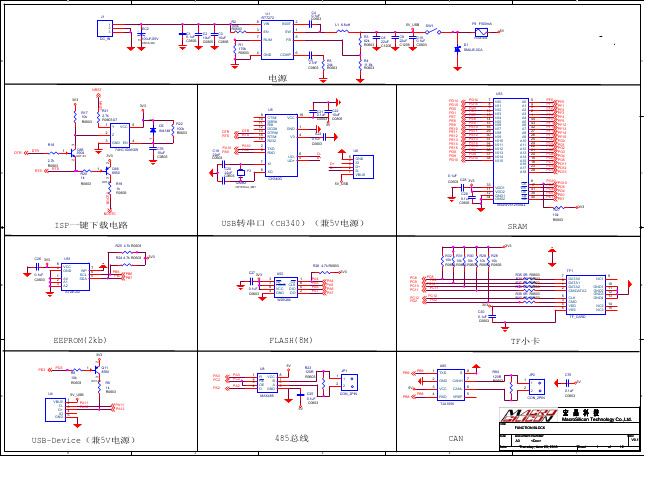

安富莱STM32-V5开发板_原理图

[2] PF0/FSMC_A0 [2] PF1/FSMC_A1 [2] PF2/FSMC_A2 [2] PF3/FSMC_A3 [2] PF4/FSMC_A4 [2] PF5/FSMC_A5

[11] PF6/LCD_PWM [5,9] PF7/NRF24L01_CSN

[3,5] PF8/SF_CS [8] PF9/ADC3_IN7 [8] PF10/ADC3_IN8

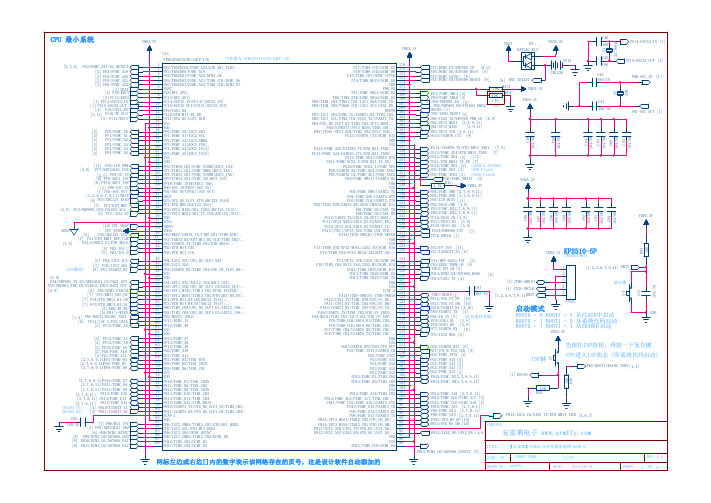

可替换为 STM32F417IGT6/LQFP-176

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44

PE2/TRACECLK/FSMC_A23/ETH_MII_TXD3 PE3/TRACED0/FSMC_A19 PE4/TRACED1/FSMC_A20/DCMI_D4 PE5/TRACED2/FSMC_A21/TIM9_CH1/DCMI_D6 PE6/TRACED3/FSMC_A22/TIM9_CH2/DCMI_D7 VBAT PI8[RTC_AF2] PC13[RTC_AF1] PC14-OSC32_IN(PC14)[OSC32_IN] PC15-OSC32_OUT(PC15)[OSC32_OUT] PI9/CAN1_RX PI10/ETH_MII_RX_ER PI11/OTG_HS_ULPI_DIR VSS VDD PF0/FSMC_A0/I2C2_SDA PF1/FSMC_A1/I2C2_SCL PF2/FSMC_A2/I2C2_SMBA PF3/FSMC_A3[ADC3_IN9] PF4/FSMC_A4[ADC3_IN14] PF5/FSMC_A5[ADC3_IN15] VSS VDD PF6/TIM10_CH1/FSMC_NIORD[ADC3_IN4] PF7/TIM11_CH1/FSMC_NREG[ADC3_IN5] PF8/TIM13_CH1/FSMC_NIOWR[ADC3_IN6] PF9/TIM14_CH1/FSMC_CD[ADC3_IN7] PF10/FSMC_INTR[ADC3_IN8] PH0-OSC_IN(PH0)[OSC_IN] PH1-OSC_OUT(PH1)[OSC_OUT] NRST PC0/OTG_HS_ULPI_STP[ADC123_IN10] PC1/ETH_MDC[ADC123_IN11] PC2/SPI2_MISO/MII_TXD2/ADC123_IN12/.. PC3/SPI2_MOSI/MII_TX_CLK/ADC123_IN13/.. VDD VSSA VREF+ VDDA PA0-WKUP/UART4_TX/TIM5_CH1/TIM8_ETR/.. PA1/UART4_RX/ETH_MII_RX_CLK/TIM5_CH2/.. PA2/USART2_TX/TIM9_CH1/ETH_MDIO/.. PH2/ETH_MII_CRS PH3/ETH_MII_COL

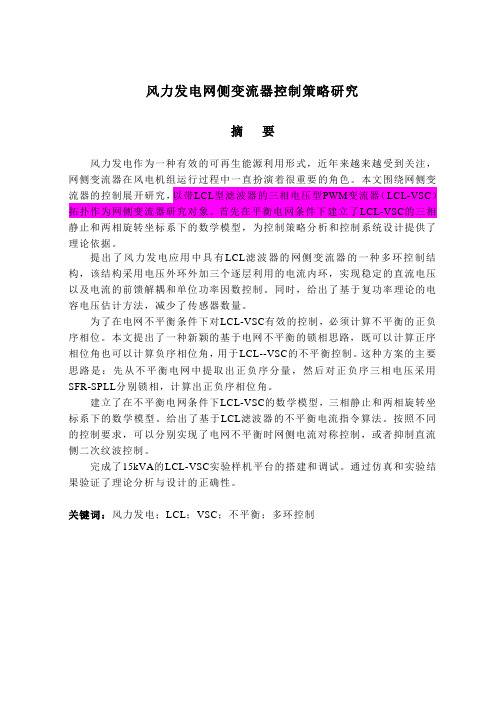

风力发电网侧变流器控制策略研究

风力发电网侧变流器控制策略研究摘要风力发电作为一种有效的可再生能源利用形式,近年来越来越受到关注,网侧变流器在风电机组运行过程中一直扮演着很重要的角色。

本文围绕网侧变流器的控制展开研究,以带LCL型滤波器的三相电压型PWM变流器(LCL-VSC)拓扑作为网侧变流器研究对象。

首先在平衡电网条件下建立了LCL-VSC的三相静止和两相旋转坐标系下的数学模型,为控制策略分析和控制系统设计提供了理论依据。

提出了风力发电应用中具有LCL滤波器的网侧变流器的一种多环控制结构,该结构采用电压外环外加三个逐层利用的电流内环,实现稳定的直流电压以及电流的前馈解耦和单位功率因数控制。

同时,给出了基于复功率理论的电容电压估计方法,减少了传感器数量。

为了在电网不平衡条件下对LCL-VSC有效的控制,必须计算不平衡的正负序相位。

本文提出了一种新颖的基于电网不平衡的锁相思路,既可以计算正序相位角也可以计算负序相位角,用于LCL--VSC的不平衡控制。

这种方案的主要思路是:先从不平衡电网中提取出正负序分量,然后对正负序三相电压采用SFR-SPLL分别锁相,计算出正负序相位角。

建立了在不平衡电网条件下LCL-VSC的数学模型,三相静止和两相旋转坐标系下的数学模型。

给出了基于LCL滤波器的不平衡电流指令算法。

按照不同的控制要求,可以分别实现了电网不平衡时网侧电流对称控制,或者抑制直流侧二次纹波控制。

完成了15kVA的LCL-VSC实验样机平台的搭建和调试。

通过仿真和实验结果验证了理论分析与设计的正确性。

关键词:风力发电;LCL;VSC;不平衡;多环控制Research on Control Strategy of Grid-side Converterfor Wind Power GenerationABSTRACTThe wind power generation is a kind of effective renewable energy source, which is received more and more attention in recent years. The grid-side converter plays a very important role in the wind power generation. This thesis does some research on control strategy of the grid-side converter, taking three-phase voltage source PWM converter with LCL filter (LCL-VSC) as the object of study. Firstly, under the balanced voltage condition, LCL-VSC mathematical model is established in the three-phase static and two-phase rotate coordinates, to provide the theory for the control strategy analysis and the control system design.Then a multiloop control scheme is proposed for LCL-VSC. Within this scheme, 3 cascaded inner current loops along with an outer voltage loop are used to achieve stable dc-link voltage, currents decoupling and feedforward, as well as the unity power factor control. With this scheme, the capacitor voltage estimation is performed with complex power theory resulting the omission of the transducers for the capacitor voltage measurement.To control the LCL-VSC effectively under unbalanced grid condition, the positive and negative sequence phase should be calculated. This thesis proposed a novel phase locked loop (PLL) based on the unbalanced grid condition, which may calculate the positive sequence phase angle and the negative sequence phase angle, used for LCL-VSC unbalanced control. The main idea of this method is first to draw the posive and negative sequence components under the unbalanced grid condition, then to get the phases of positive and negative sequence with the SFR-SPLL separately.The LCL-VSC mathematical model for unbalanced control is established under unbalanced grid condition. The reference current algorithm is given based on the LCL-VSC. For different purposes, it can be realized either symmetrical grid-side current or constant DC-side voltage without twice order ripple.Finally, a 15kVA LCL-VSC experimental system is established. The simulation and the experimental result verify the theoretical analysis and the design.Keywords: Wind power generation; LCL; VSC; unbalance; Multi-loop control目录第一章绪论 (1)1.1论文的研究背景和选题意义 (1)1.1.1风力发电及其意义 (1)1.1.2国内外风电产业发展概况 (1)1.1.3风力发电变流器的产业现状 (2)1.1.4论文的选题意义 (3)1.2风力发电中的网侧变流器研究现状 (3)1.2.1风力发电中的电气系统 (3)1.2.2网侧变流器的拓扑结构 (5)1.2.3网侧变流器控制策略的研究现状 (6)1.3本论文的主要目标和主要工作 (8)第二章基于LCL-VSC网侧变流器建模与控制 (9)2.1引言 (9)2.2三相LCL-VSC数学模型 (10)2.2.1三相静止(a , b, c)坐标系下的数学模型 (11)2.2.2两相静止坐标系(D, Q)下的数学模型 (12)2.2.3两相旋转坐标系(d, q)下的数学模型 (14)2.3LCL-VSC多环控制策略 (14)2.3.1系统控制结构 (17)2.3.2并网电流指令算法 (18)2.3.3电流控制器设计与稳定性校验 (20)2.3.4直流电压环控制器设计 (25)2.3.5基于复功率理论的电容电压估计 (26)2.4多环控制策略仿真与分析 (27)2.4.1电流环仿真 (28)2.4.2电压环仿真 (30)2.5总结 (30)第三章电网不平衡及其关键问题研究 (31)3.1引言 (31)3.2三相电网不平衡 (32)3.2.1电网不平衡理论分析 (32)3.2.2不平衡系统的研究方法 (33)3.2.3正负序检测 (35)3.3软件锁相环(SSFR-SPLL)及其设计 (41)3.3.1基本原理 (41)3.3.2PLL模型的简化 (43)3.3.3参数计算 (44)3.4基于双SFR_SPLL在不平衡电网中的应用 (48)3.4.1基本结构 (48)3.4.2仿真分析 (49)3.5总结 (51)第四章LCL-VSC不平衡控制策略 (52)4.1引言 (52)4.2不平衡电网下VSC数学模型 (52)4.2.1三相静止坐标系(a-b-c)下的数学模型 (53)4.2.2同步旋转坐标系(d, q)下的数学模型 (55)4.3电网不平衡时电流指令算法 (58)4.4双矢量电流控制策略研究 (61)4.4.1系统控制结构 (61)4.4.2抑制网侧负序电流的控制策略 (62)4.4.3抑制直流侧二次纹波的控制策略 (63)4.5仿真分析 (64)4.6总结 (65)第五章系统设计及实验分析 (66)5.1LCL-VSC样机设计 (66)5.1.1主电路参数选择 (67)5.1.2IPM模块选择 (67)5.1.3控制模块处理器的选择 (68)5.1.4功能模块电路设计 (69)5.1.5试验系统软件设计 (72)5.2系统实验结果分析 (75)5.2.1平衡电网VSC控制 (75)5.2.2不平衡电网与锁相环 (76)5.2.3不平衡电网VSC双电流环控制 (77)第六章总结与展望 (79)6.1总结 (79)6.2展望 ................................................................... 错误!未定义书签。

ATK-VS1053 MP3模块用户手册_V1.0

2.1 模块简介............................................................................................................................2 2.2 模块引脚说明....................................................................................................................3 2.3 模块使用说明................................................................................................................ MP3 模块用户手册

高性能音频编解码模块

2.1 模块简介

ATK-VS1053 MP3 模块是 ALIENTEK 开发的一款高性能音频编解码模块,该模块接口 丰富、功能完善,仅需提供电源(3.3V/5.0V),即可通过单片机(8/16/32 位单片机均可)控 制模块实现音乐播放,或者录音等功能,模块其资源图如图 2.1.1 所示:

User Manual

ATK-VS1053 MP3 模块用户手册

高性能音频编解码模块

用户手册

ALIENTEK 广州市星翼电子科技有限公司

修订历史

VS1053的应用

VS1053的应用VS1053本身是一款非常强大的MP3解码芯片,然而大多是人实践上才用了它很小一部份功能。

我也是第一次使用VS1053,所以也只用了它非常少的功能。

1. 最常见的方法就是,通过MCU控制VS1053进行解码。

用这中方法是最为简单的,只要正确使用VS1053的命令就可以实现。

当然这样可以快速使用VS1053,是入门的最好方法,但是成本比较高。

2. 直接使用VS1053进行控制,这样就节约了一块MCU。

不过需要应用VSIDE平台,所以使用起来相当比较麻烦。

本人就讲讲使用第一种方法的应用,等以后利用第二种方法进行开发时,在和大家一起学习。

VS1053的应用其实非常简单,基本的步骤如下:1. 编写好SPI总线驱动代码;2. 编写好VS1053初始化代码;3. 编写正弦波测试代码;4. 内存测试代码。

完成以上几个步骤后就可以进行MP3解码了。

/************************************************************** ************************* FunctionName : VS1053SineTest()* Description : 正弦波测试* EntryParameter : freq - 测试频率 0x24,0x44等* ReturnValue : None*************************************************************** ***********************/void VS1053SineTest(uint8 freq){uint8 i;uint8 test[] = {0x53, 0xEF, 0x6E, 0x24, 0x00, 0x00, 0x00,0x00}; // 向vs发送正弦测试命令uint8 back[] = {0x45, 0x78, 0x69, 0x74, 0x00, 0x00, 0x00, 0x00}; // 向vs发送退出测试命令VS_XRESET_CLR(); // xreset = 0VS1053_Delay(100);SSP1Send(0xFF); // 发送一个字节的无效数据,启动SPI传输VS_CS_SET(); // cs = 1VS_XDCS_SET(); // xdcs = 1VS_XRESET_SET(); // xreset = 1VS1053_Delay(100);VS1053WriteReg(VS_SCI_MODE, 0x0820); // enter vs1003 test modelwhile (VS_DREQ_PIN() == 0); // wait for DREQ Highlevel GPIOSetValue(1, 2, 0); // xdcs = 0test[3] = freq; // 写入频率for (i=0; i<8; i++){VS1053WriteData(test[i]); // 程序执行到这里后应该能从耳机听到一个单一频率的声音}VS_XDCS_SET(); // xdcs = 1VS1053_Delay(100000);GPIOSetValue(1, 2, 0); // xdcs = 0for (i=0; i<8; i++){VS1053WriteData(back[i]); // 退出正弦测试}VS_XDCS_SET(); // xdcs = 1VS1053_Delay(200);/************************************************************** ************************* FunctionName : VS1053RamTest()* Description : 内存测试,0x8000表示测试完成,0x83FF表示完好* EntryParameter : None* ReturnValue : 完好返回0,否则返回1*************************************************************** ***********************/uint8 VS1053RamT est(void){uint16 res = 0x0000;uint8 i;uint8 test[] = {0x4D, 0xEA, 0x6D, 0x54, 0x00, 0x00, 0x00, 0x00}; //VS_XRESET_CLR(); // xreset = 0VS1053_Delay(100);SSP1Send(0xFF);VS_CS_SET(); // cs = 1VS_XDCS_SET(); // xdcs = 1VS_XRESET_SET(); // xreset = 1VS1053_Delay(100);VS1053WriteReg(VS_SCI_MODE, 0x0820); // Allow SCI tests while (VS_DREQ_PIN() == 0); // wait for DREQ Highlevel //After this sequence wait for 1100000 clock cycles.//The result can be read from the SCI register SCL_HDATA0 GPIOSetValue(1, 2, 0); // xdcs = 0for (i=0; i<8; i++)VS1053WriteData(test[i]); // 写入测试代码}VS_XDCS_SET(); // xdcs = 1VS1053_Delay(10000);res = VS1053ReadReg(VS_SCI_HDAT0); // 如果得到的值为0x83FF,则表明完好。

stm32开发板原理图

Y5 1 4 3

C41 0.1uF C0603 VGND IOVDD0 IOVDD1 IOVDD2 6 14 19 CVDD CVDD0 CVDD1 CVDD2 CVDD3 RX TX 5 7 24 31 26 27 4 16 20 21 22 35 38 43 45 C35 0.1uF C0603 VGND C36 0.1uF C0603 C37 0.1uF C0603 C38 0.1uF C0603 R43 100k IOVDD R0603

C76 10uF C0805

U6 6 5 DD+ D+ D5 4 3 2 1 GND ID D+ DVBUS

PD14 PD15 PD0 PD1 PE7 PE8 PE9 PE10 PE11 PE12 PE13 PE14 PE15 PD8 PD9 PD10

PD14 PD15 PD0 PD1 PE7 PE8 PE9 PE10 PE11 PE12 PE13 PE14 PE15 PD8 PD9 PD10

5

4

3

2

1

J1 1 2 3 DC_IN R2 100k R0603 C1 0.1uF C0603 C2 10uF C0805 C3 10uF C0805 R1 179k R0603 8 3 7 1

U1 RT7272 VIN EN RLIM B00T SW FB 2 1 5 + EC2 2 100uF/25V

C42 0.01uF C0603R44 22R R0603 C43 0.01uF C0603 RIGHT R45 22R R0603

AGND

C60 18pF C0603

2

R53 1M R0603 30 31

U57 XI/CLKIN XO TXN TXP RXN RXP LINKLED ACTLED NC1 NC2 NC3 NC4 DNC VBG RSVD1 RSVD2 RSVD3 RSVD4 RSVD5 PMODE2 PMODE1 PMODE0 EXRES1 T0CAP 1V20 RSVD 1 2 5 6 25 27 46 47 12 13 7 18 38 39 40 41 42 43 44 45 10 R58 12.4k R0603 4.7uF C0603 0.01uF C0603 AGND R66 10k R0603 R65 10k R0603 AGND R64 10k R0603 R63 10k R0603 R62 10k R0603 R61 10k R0603 3V3 R60 10k R0603 R59 10k R0603 TXN TXP RXN RXP LINKLED ACTLED

嵌入式实时操作系统μCOS原理与实践1

4、文件管理:

对外存中信息进行管理的文件系统

关于μC/OS-II

•UCOSII 是一个可以基于ROM 运行的、可裁减的 、抢占式、实时多任务内核,具有高度可移植性, 特别适合于微处理器和控制器,是和很多商业操作 系统性能相当的实时操作系统(RTOS)。为了提供 最好的移植性能,UCOSII 最大程度上使用ANSI C 语言进行开发,并且已经移植到近40 多种处理器 体系上,涵盖了从8 位到64 位各种CPU(包括DSP) 。

• 事件

两个任务通过事件进行通讯的示意图所示:

注释:任务1 是发信方,任务2 是收信方。任务1 负责把信息发送到 时间上,这项操作叫做发送事件。任务2 通过读取事件操作对事件进 行查询,如果有信息则读取,否则等待。读事件操作叫做请求事件。

事件控制块(ECB)

• 为了把描述事件的数据结构统一起来,UCOSII 使用叫做事件控制 块(ECB)的数据结构来描述诸如信号量、邮箱(消息邮箱)和消息 队列这些事件。事件控制块中包含包括等待任务表在内的所有有关 事件的数据,事件控制块结构体定义如下: • typedef struct { INT8U OSEventType; //事件的类型 INT16U OSEventCnt; //信号量计数器 void *OSEventPtr; //消息或消息队列的指针 INT8U OSEventGrp; //等待事件的任务组 INT8U OSEventTbl[OS_EVENT_TBL_SIZE];//任务等待表 #if OS_EVENT_NAME_EN > 0u INT8U *OSEventName; //事件名 #endif } OS_EVENT;

UCOSII中与任务相关的几个函数

1) 建立任务函数

基于51单片机的自动洗衣机的设计

摘要目前,随着物联网的兴起,智能家电又有了更高的需求,洗衣机的全自动化、多功能化、智能化是其发展方向,也是未来发展的一大趋势。

本文介绍了基于89C51单片机的全自动洗衣机的设计。

整个系统是以单片机及其外部设备组成,主要通过单片机IO口控制12864液晶显示器显示信息,并通过按钮控制洗衣机的进水,漂洗,脱水功能及电子音乐的播放功能。

关键词:12864液晶显示器;电子音乐;PWM调制;L298电机驱动;目录摘要 (I)第1章绪论 (1)1.1 课题开发背景 (1)1.2 设计的目的和意义 (2)第2章设计方案 (3)2.1设计任务 (4)2.2洗衣机的设计方案 (5)第3章硬件设计 (7)3.1 控制电路的系统组成 (8)3.2 硬件设计 (9)3.2.1 复位电路及原理 (9)3.2.2L298驱动电路及原理 (9)3.2.312864液晶显示电路及原理 (10)3.2.4状态信号灯指示电路 (10)3.2.5时钟电路 (11)第4章软件设计 (11)4.1 主程序设计 (12)第5章展望与总结 (12)致谢 (13)附录 (14)附录A 程序 (15)第1章概述1.1 课题开发背景随着人民生活水平的提高,越来越多的人需要使用洗衣机。

现在洗衣机越来越高度自动化,只要衣服放入洗衣机,简单的按两个键,就会自动注水,一些先进的电脑控制洗衣机,还能自动的感觉衣物的重量,自动的添加适合的水量和洗涤剂,自动的设置洗涤的时间和洗涤的力度,洗涤完以后自动的漂洗甩干,更有些滚筒洗衣机还会将衣物烘干,整个洗衣的过程完成以后还会用动听的音乐声提醒用户,用户可以在洗衣的过程做其它的事,节省了不少的时间。

总之,每一项技术的进步极大地推动了洗衣过程自动化程度的提高。

1.2 设计的目的和意义目前中国洗衣机市场正进入更新换代期,市场潜力巨大,人们对于洗衣机的要求也越来越高,目前的洗衣机主要有强弱洗涤功能、进排水系统故障自动诊断功能、暂停等几大功能,在许多方面还不能达到人们的需求。

五轴工业机器人控制系统设计

五轴工业机器人整体结构设计摘要五轴工业机器人是一种工业上的关节机器人,其广泛应用于世界的工业自动化领域,在世界上,我国的五轴工业机器人技术相比于国外发达国家无论是从时间还是技术方面都比较落后,并且很多零部件以及芯片都离不开外货进口。

五轴工业机器人控制系统是五轴工业机器人智能化和人工化的核心系统之一,因此控制系统的功能强度,性能的好坏直接影响着五轴工业机器的整体控制性能以及工作状态。

本文将对五轴工业机器人的控制系统进行硬件系统的设计、软件的选择以及程序的编写,并对它运动轨迹进行规划,对伺服控制系统的电机进行选择、对运作位置进行设计。

关键词:五轴工业机器人;软硬件控制;电机的选择;控制系统设计Design of five-axis Industrial Robot Control SystemAbstractFive-axis industrial robot is an industrial joint robot widely.It is used in the world's industrial automation field. Compared with developed countries, Chinese five-axis industrial robot technology is relatively backward in terms of time and technology, and many parts and chips cannot be separated from foreign imports. Five-axis industrial robot control system is one of the intelligent and artificial core systems of five-axis industrial robot. The function of the control system,whose strength and performance is good or bad directly affect the overall control performance of five-axis industrial robot and the stability of the working state.This design will carry out hardware system design, software selection and program preparation for the control system of the five-axis industrial robot, and planing it’s motion trajectory, selectting the motor of the servo control system, and designing the operation position.Key words:Five-axis industrial robot,hardware and software controlling,Motor selection,control system designing.目录1 前言 (1)1.1本设计的目的、内容及意义 (1)1.2本设计在国内外的发展概况 (3)1.2.1国外研究现状 (3)1.2.2国内研究现状 (3)1.3本设计应解决的主要问题 (4)1.4 研究的基本思路和方法 (4)2对于五轴工业机器人工作的原理分析 (5)2.1五轴工业机器人运作原理 (6)2.2五轴工业机器人控制系统的综合评述 (6)2.2.1五轴工业机器人控制系统的特点 (6)2.2.2五轴工业机器人的贴标工艺 (6)3五轴工业机器人硬件控制系统的设计 (7)3.1控制原理的分析 (7)3.2硬件控制系统组成与内部选择 (7)3.2.1硬件控制系统的组成部分 (7)3.2.2硬件控制系统的内部选择 (8)3.3CPU硬件控制系统的设计 (9)3.3.1CPU硬件控制系统构架设计 (9)3.3.2CPU的控制器的外部电路的设计 (10)3.3.3 JTAG接口线路的设计 (12)3.3.4总控制芯片最小系统设计 (13)3.3.5 FPGA逻辑处理单元设计 (15)3.4伺服电机及伺服驱动器的选择 (17)3.5控制柜的设计 (19)3.5.1控制柜内部电源设计 (19)3.5.2变压器的设计 (21)3.5.3中间继电器的选择 (21)3.5.4急停按钮与指示灯的选择 (22)3.5.5 PLC的选择 (24)3.5.6 I/O板的设计 (26)3.5.7 工控机的选择 (27)3.5.7 导线的选择 (28)3.5.8 控制柜的设计 (29)4.五轴工业机器人的轨迹规划 (30)4.1轨迹规划应考虑的问题 (30)4.2五轴工业机器人的轨迹规划 (31)4.2.2圆弧轨迹规划 (32)5软件的选择与电机的仿真 (33)5.1软件的选择 (33)5.1.1 DEV C++软件界面的介绍 (33)致谢 ...................................................................................................................错误!未定义书签。

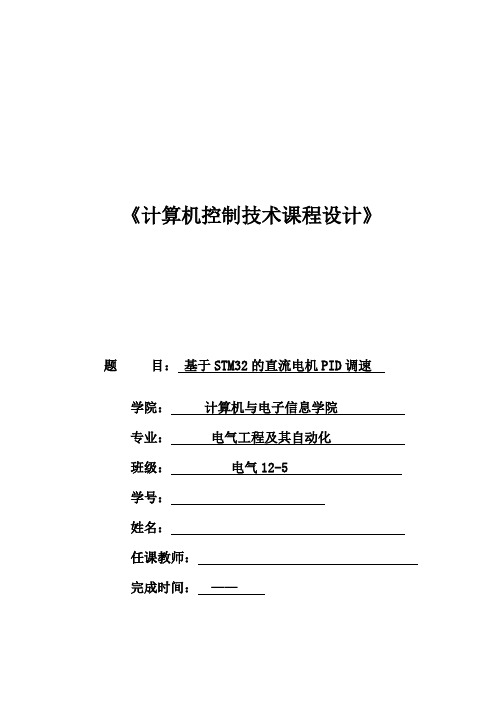

基于STM32的直流电机PID调速系统设计

《计算机控制技术课程设计》题目:基于STM32的直流电机PID调速学院:计算机与电子信息学院专业:电气工程及其自动化班级:电气12-5 学号:姓名:任课教师:完成时间:——基于STM32的直流电机PID调速摘要电机转速控制在运动控制系统中占有至关重要的地位,本设计将电机转速控制作为研究对象;以PID为基本控制算法,STM32F103单片机为控制核心,产生受PID算法控制的PWM脉冲实现对直流电机转速的控制。

同时利用光电传感器将电机速度转换成脉冲频率反馈到单片机中,实现转速闭环控制,达到转速无静差调节的目的。

在系统中采320×240TFTLCD显示器作为显示部件,通过4个按键通过界面切换方式设置P、I、D、V四个参数和正反转控制,启动后可以通过显示部件了解电机当前的运行状态和系统的CPU温度。

该系统控制精度高,具有很强的抗干扰能力。

关键词:PID 直流电机反馈调节Based on the STM32 PID speed control of dc motorAbstractMotor speed control occupies a crucial position in the motion control system, the design of the motor speed control for the study; in the basic PID control algorithm, STM32F103 microcontroller core, by the PID control algorithm generates a PWM pulse to achieve DC speed control. At the same time the use of photoelectric sensors to convert the motor speed to pulse frequency feedback to the microcontroller to achieve closed-loop speed control, to speed static error adjustment purposes. Mining 320 × 240TFTLCD monitor as a display unit in the system, through four key settings P, I, D, V four parameters and reversing control through the interface switching mode, start to understand the current state of the motor and the system through the display unit CPU temperature. The system control and high precision, has a strong anti-jamming capability.Keywords: PID DC motor feedback regulation目录1. 绪论 (1)研究背景与意义 (1)本文主要研究方法 (1)2. 设计方案与论证 (2)系统设计方案 (2)控制器模块设计方案 (2)3. 系统硬件电路设计 (3)整体电路设计 (3)整体理论 (3)整体简单结构图和资源分配图 (3)最小单片机系统设计 (4)STM32F103复位电路 (6)电源电路 (6)电机驱动电路设计 (7)光电码盘编码器电路设计 (7)显示电路设计 (8)按键电路设计 (10)4. 系统软件设计 (10)PID算法 (10)PID参数整定方法 (11)电机速度采集算法 (12)程序流程图 (12)5. 系统调试 (13)软件调试 (13)系统测试与分析 (14)6. 总结与展望 (15)参考文献 (16)附录一部分程序源程序 (17)附录二系统界面实物图和PCB图 (20)1.绪论1.1研究背景与意义电动机在现代的工业中,是主要的驱动设备,尤其是直流电动机,由于它的平滑调速性和结构上的简单,使其成为许多电器,如洗衣机,电梯等的驱动。

复旦大学模拟电路二级运放实例

udan

专用集成电路与系统国家重点实验室

RFIC

整理者

版本号 1.0

日期 2007.10.10

说明 详细介绍二级运放原理和设计仿真, 供新手 入门参考

尹睿

版权所有,不得侵犯!传播与修改请保留版权信息。

目录

1 2 引言 ..................................................................................................................... 1 电路分析 .............................................................................................................. 2 2.1 2.2 2.3 2.4 2.5 2.6 2.7 3 3.1 3.2 3.3 3.4 电路结构 ....................................................................................................... 2 电路描述 ....................................................................................................... 2 静态特性 ....................................................................................................... 3 频率特性 ....................................................................................................... 5 相位补偿 ....................................................................................................... 7 调零电阻 ....................................................................................................... 7 偏置电路 ..................................................................................................... 10 共模输入范围 .............................................................................................. 13 输出动态范围 .............................................................................................. 13 单位增益带宽(GBW) .............................................................................. 14 输入失调电压 .............................................................................................. 14

VS1053B中文资料应用

4.2 推荐工作值 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.3 模拟电路特性 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

• EarSpeaker 空间效果注 2 处理

• 低音和高音控制 • 只用一个单独的 12..13MHz 时钟运作 • 也可以使用一个 24..26MHz 时钟运作 • 内建 PLL 时钟乘法器 • 低功耗运作 • 芯片内建高质量和通道间无相位误差的立体声 DAC • 过零交叉注 3(Zero‐cross)侦测和平滑的音量调整 • 立体声耳机驱动器可以驱动一个 30Ω 的负载 • 安静的电源通断功能 • 可扩展外部 DAC 的 I2S 接口 • 分离的模拟、数字、IO 供电电源 • 供用户代码和数据使用的片内 RAM • 用于控制和数据的串行接口 • 可以作为从模式的辅助处理器使用 • 特殊应用可使用 SPI FLASH 存储器引导 • 可用于调试的 UART 接口 • 可用软件增加新功能和提供最多 8 个 GPIO • 符合 RoHS 无铅标准的封装(绿色)

7.7.1 两个 SCI 写操作 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 7.7.2 两个 SDI 字节 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 7.7.3 在两个 SDI 字节之间的 SCI 操作 . . . . . . . . . . . . . . . . . . . . . . 25

VS1053b音频解码器编码器

VS1053b是单片Ogg Vorbis/MP3/AAC/WMA/MIDI音频解码器,及IMA ADPCM编码器和用户加载的Ogg Vorbis编码器。

它包含了一个高性能、有专利的低功耗DSP处理器内核VS_DSP4、工作数据存储器、供用户应用程序和任何固化解码器一起运行的16KiB 指令RAM及0.5KiB多的数据RAM、串行的控制和输入数据接口、最多8个可用的通用I/O引脚、一个UART、并有一个优质的可变采样率立体声ADC(“咪”、“线路”、“线路+咪”或“线路*2”)和立体声DAC、和跟随的一个耳机功放及一个公共电压缓冲器。

特性●Ogg Vorbis解码;MPEG1&2音频阶层III(CBR+VBR+ABR);阶层I和II可选;MPEG4/2AAC‐LC(+PNS),HE‐AAC V2(级别3)(SBR+PS);WMA4.0/4.1/7/8/9所有特性注1(profiles)(5‐384kbps);WAV(PCM+IMA ADPCM);通用MIDI1/SP‐MIDI格式0的文件●用软件插件进行Ogg Vorbis编码(2007第四季可用)●“咪/线路”的输入信号可实现IMA ADPCM编码(立体声)●支持MP3和WAV的数据流●EarSpeaker空间效果注2处理●低音和高音控制●只用一个单独的12..13MHz时钟运作●也可以使用一个24..26MHz时钟运作●内建PLL时钟乘法器●低功耗运作●芯片内建高质量和通道间无相位误差的立体声DAC●过零交叉注3(Zero‐cross)侦测和平滑的音量调整●立体声耳机驱动器可以驱动一个30Ω的负载●安静的电源通断功能●可扩展外部DAC的I2S接口●分离的模拟、数字、IO供电电源●供用户代码和数据使用的片内RAM●用于控制和数据的串行接口●可以作为从模式的辅助处理器使用●特殊应用可使用SPI FLASH存储器引导●可用于调试的UART接口●可用软件增加新功能和提供最多8个GPIO●符合RoHS无铅标准的封装(绿色环保)。

MP3音乐播放器芯片VS1053B芯片使用教程

if(ucMaskCode & ucSendData) {

Macro_Set_SI_High(); } else {

Macro_Set_SI_Low(); }

Macro_Set_CLK_High(); ucMaskCode >>= 1;

} }

/******************************************************************************

MP3 音乐播放器芯片 VS1053B 芯片使用教程

MP3,MP4,数码相机曾经是奢侈品。科技发展了,这些东西也就成了普通手 机的附属品了。但是作为手艺人学习这些芯片了解这些高性能芯片是很有必要的。 学习了解它既拓展了自己的眼界,也可以提升自己对嵌入式系统的认识。原子战 舰板上就板载了一颗高性能 MP3 音乐播放器芯片 VS1053B 芯片。通过原子源码对 一些参数的修改,也能欣赏美妙的音乐。这是一款真正的数字产品。还可以作为 录音机使用。

VS1053B,LCD,RDA5802 收音机芯片,ADXL345 重力加速度传感器芯片等等这些芯片, 它们有一个共同点:寄存器,寄存器地址,数据帧,命令字,I2C, SPI 协议等等。学会这些 外设芯片的驱动程序编写方法,才能真正发挥 ARM 处理器的强大功能。 下面是单片机程序的主要部分预览: /* * MP3 模块测试程序 *

* 用途:MP3 模块测试程序

*

vs1003 的硬件测试程序,主控芯片为 STC12LE5A60S2

*

其他的微处理器(带 SPI 接口的)只需稍加修改即可适用

*

对于不带硬 SPI 接口的微处理器可以用 IO 进行 SPI 的时序模拟

风机叶片声信号特征提取与故障检测研究

风机叶片声信号特征提取与故障检测研究摘要:风能作为清洁能源,风电在近几年实现高速发展,风力发电机容量快速增加、装机规模不断扩大。

但伴随着风电行业的快速发展,风机的故障问题日益凸显,因此对风电机组的各部分进行状态监测和故障诊断是十分必要的。

叶片长期工作在复杂的露天环境中,很容易发生故障,造成人员安全事故和巨大的经济损失。

因此对风机叶片的故障状态进行检测具有重要意义。

本文主要分析风机叶片声信号特征提取与故障检测研究。

关键词:风机叶片;故障检测;声信号;MFCC;SVM引言目前大多数学者主要通过获取叶片的振动、声发射,超声波等信号进行故障检测,另外还有学者通过红外成像和机器视觉等图像处理技术检测叶片故障状态。

但是在获取叶片的振动信号和声发射信号时需要安装相应的传感器,成本高且安装难度较大;超声波信号需要与表面接触且信号处理复杂,不利于叶片故障状态的及时检测;图像检测方法会受到环境的制约,且检测方法较为复杂。

1、叶片故障声学检测基本原理首先,消除复杂环境中的背景噪声,提高信噪比。

风扇叶片在地形环境下工作,探测声音信号经常受到各种背景噪声的影响,如随机载荷、风速、雨水、叶片周围的随机噪声,由于叶片早期故障能量低,容易隐藏在背景噪声中,所以目前风扇启动条件通常不低于平均速度是必要的此外,由于高频信号分量衰减快,刀片式麦克风部署位置偏远,实际传感器采集的高频信号分量能量很低,不利于故障判断,可以对高频信号分量进行滤波。

在“摘要”部分,选择要预处理原始音频信号的pass-band滤波器。

然后提取叶片的声学特性。

麦克风采集的音频信号在健康叶片的正常工作状态下主要由叶片扫描。

然而,随着风扇叶片寿命的延长,可能会出现周期性的异常噪声,因此故障叶片工作时的声音信号频谱不可避免地随正常工作状态而周期性变化。

因此,只需提取反映叶片健康状况信息的光谱特征,即可消除风扇叶片的故障。

音频信号频谱的变化可以用多种方式来表示。

能够结合信号频率和算法来表示高频和低频,可以选择频谱特性,以便准确描述音频信号的频谱变化。