高速电路传输线反射问题的分析与解决

信号反射问题解决方法

为大家介绍一下高速信号的反射问题和解决方案:信号沿传输线向前传播时,每时每刻都会感受到一个瞬态阻抗,这个阻抗可能是传输线本身的,也可能是中途或末端其他元件的。

如果信号感受到的阻抗是恒定的,那么他就会正常向前传播,只要感受到的阻抗发生变化,信号就会发生反射。

信号发生反射的原因是源端与负载端的阻抗不匹配引起的,因此要进行阻抗匹配来解决反射问题,反射系数公式为:ρ为反射系数,Z1为信号最初所在区域的瞬时阻抗,Z2为信号进入另一区域的瞬时阻抗。

解决信号反射的方法有一下几种方法:一、串联终端匹配:示意图如下图(1)所示:图(1)在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

所以当R的电阻值等于Z0时反射信号完全被电阻吸收(假设理想的驱动器的输出阻抗为零)。

这种匹配方法简单在源端只需加入一个电阻原件,相对于其他匹配方法来说匹配电阻的功耗是最小的,不会给驱动器带来额外的直流电流,也不会给信号和地直接引入额外的阻抗,成本低,也节省电路板上的空间。

CPU作为输出信号时防止反射信号就用串联终端匹配,USB信号也采用这种方法做阻抗匹配。

二、并联终端匹配在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。

实现形式分为单电阻和双电阻两种形式。

1、单电阻并联端接:在芯片的输入阻抗很高的情况下,对单电阻形式来说,负载端的并联电阻值必须与传输线的特征阻抗相近或相等。

其连接方式如图2所示:图2这样设计的缺点是会带来直流损耗,匹配电阻接地会使信号的下降沿下降过快,会影响信号的占空比。

由于一般芯片的的输入阻抗很高,所以为了达到阻抗匹配需使匹配电阻阻抗和传输线阻抗相接近,即阻抗不会太大,所以电流驱动能力需要很强。

由于典型的TTL或CMOS电路的驱动能力很小,这种单电阻的并联匹配方式很少出现在这些电路中。

如何解决电路中的反射问题

如何解决电路中的反射问题在电路设计中,反射是一个常见但令人头疼的问题。

它会导致电路性能下降,甚至损坏设备。

为了解决电路中的反射问题,我们可以采取以下措施:1. 了解反射问题的原因反射问题主要是由信号在电路中发生的不完全匹配引起的。

当信号从一个传输介质(如电缆)传播到另一种传输介质(如电路板)时,由于阻抗不匹配,信号会反射回原来的介质。

这种反射会导致信号波形失真、干扰和信号功率损失。

2. 使用合适的阻抗匹配技术为了减少反射问题,我们可以使用阻抗匹配技术。

在设计电路时,应确保传输线和驱动器/接收器之间的阻抗匹配。

这可以通过选择合适的传输线特性阻抗以及正确匹配驱动器和接收器的阻抗来实现。

3. 使用终端阻抗终端阻抗是电路中的一个重要参数,它可以消除信号的反射。

终端阻抗应该与传输线的特性阻抗相匹配,这样可以最大程度地抑制反射。

4. 使用终端电阻终端电阻是另一个有效的方法,可以减少反射问题。

通过在传输线末端添加一个与线路特性阻抗相匹配的电阻,可以吸收反射信号。

5. 使用衰减器衰减器是一种有源电路元件,可以减少信号的功率并降低反射。

衰减器可以在电路中插入,以减小反射并平衡信号的幅度。

6. 使用终端串联电容终端串联电容是一种常见的电路设计技巧,也可以用于解决反射问题。

通过在传输线的末端串联一个适当的电容,可以阻止高频信号的反射并改善信号传输。

7. 优化布局和接地设计良好的布局和接地设计也可以帮助解决反射问题。

确保信号路径短、布线规整,并避免尖锐的转弯或多余的分支。

此外,良好的接地设计可以减少信号的干扰和反射。

总结:电路中的反射问题是一个常见但需要重视的问题。

为了解决这个问题,我们可以利用阻抗匹配技术、终端阻抗、终端电阻、衰减器、终端串联电容以及良好的布局和接地设计。

通过结合这些方法,我们可以有效地降低反射问题,并提高电路的性能和可靠性。

消除传输线的反射带来的影响的方法

消除传输线的反射带来的影响的方法消除传输线的反射带来的影响是保证信号传输质量和稳定性的重要任务之一。

反射信号可能会导致信号失真、噪声增加以及其他不良影响,因此需要采取一系列措施来解决这些问题。

本文将就这方面的方法进行探讨。

1.增加终端阻抗匹配:终端阻抗匹配是消除传输线反射的基本方法。

当信号源的输出阻抗与传输线的特性阻抗相匹配时,传输线上的反射信号将被最小化。

通常,使用特性阻抗和终端阻抗相等的传输线,如50欧姆同轴电缆,以确保阻抗匹配。

2.添加终端电阻:在一些情况下,无法完全匹配终端阻抗。

因此,添加一个匹配终端的电阻来吸收反射信号是一种常见的方法。

这种电阻被称为终端电阻或终端阻抗,并且应与特性阻抗相等。

这样做可以使反射信号被吸收,避免与主信号相互干扰。

3.采用衰减器:衰减器是一种用于降低信号幅度的电路。

在传输线的末端或关键节点处安装衰减器可以有效地消除反射信号。

衰减器的阻抗应与特性阻抗相匹配,以确保在不引入过多信号噪声的同时实现衰减效果。

4.使用终端网络:终端网络是一种由电阻、电容和电感等元件组成的网络。

它被安装在信号源和传输线之间,用于调整阻抗并消除反射信号。

终端网络的设计可以根据特定需求进行调整,以匹配传输线和信号源的特性阻抗。

5.调整传输线长度:传输线长度的选择对于消除反射信号也起着重要作用。

当传输线长度为特定波长的整数倍时,反射信号可以在较远的位置被吸收,从而减少反射对信号质量的干扰。

因此,可以通过调整传输线长度来最小化反射信号。

6.使用阻抗转换器:阻抗转换器是一种被广泛用于消除传输线反射的设备。

它将信号源的输出阻抗与特性阻抗匹配,将传输线的输入阻抗与特性阻抗相匹配。

这样做可以有效地减少反射信号,提高信号传输的质量和稳定性。

7.增加终端接地:良好的接地是消除传输线反射信号的关键。

将终端接地良好地连接到地线可以有效地降低信号的反射。

同时,减少接地导线的长度和电阻也是必要的,以确保信号的良好接地。

传输线反射的理论分析

传输线反射的理论分析作者:鲁政嘉来源:《硅谷》2008年第17期[摘要]信号完整性是指信号在信号线上的质量。

信号完整性问题由多种因素引起,归结起来有反射、串扰、过冲和下冲、振铃、信号延迟等,其中反射和串扰是引发信号完整性问题的两大主要因素。

从反射形成机理、反射对信号的影响、端接电阻匹配方式等几个方面介绍反射的形成和性质,并说明应如何减小和避免传输线中的反射。

[关键词]反射振铃阻抗匹配中图分类号:TN94 文献标识码:A 文章编号:1671-7597(2008)0910131-01一、反射形成机理反射就是信号在传输线上的回波现象。

在高速的PCB中导线必须等效为传输线,按照传输线理论,如果源端与负载端具有相同的阻抗,反射就不会发生了。

如果二者阻抗不匹配就会引起反射。

一般布线的几何形状、不正确的线端接、经过连接器的传输及电源平面的不连续等因素均会导致此类反射。

信号沿传输线传播时,其路径上的每一步都有相应的瞬态阻抗,无论是什么原因使瞬态阻抗发生了变化,信号都将产生反射现象,瞬态阻抗变化越大,反射越大。

信号到达瞬态阻抗不同的两个区域的交界面时,在导体中只存在一个电压和一个电流回路,交界面的电压和电流一定连续,则有:而由欧姆定律知:当交界面两侧的阻抗不同时,以上四个关系不可能同时成立,这就说明在交界面上必然有反射回发射端的电压,以平衡交界面两端不匹配的电压和电流。

入射信号电压向着分界面传播,而传输信号电压远离分界面而传播,入射电压穿越分界面时,产生反射电压,则有:相应的当入射电流穿越分界面时,反射电流和传输电流的关系为:按照欧姆定律,每个区域中的电压与电流的关系为:通过换算可以得到:由此可以看出,缩小和的差值,有利于减小反射电压,在实际运用中,通过给传输线端接匹配阻抗来实现。

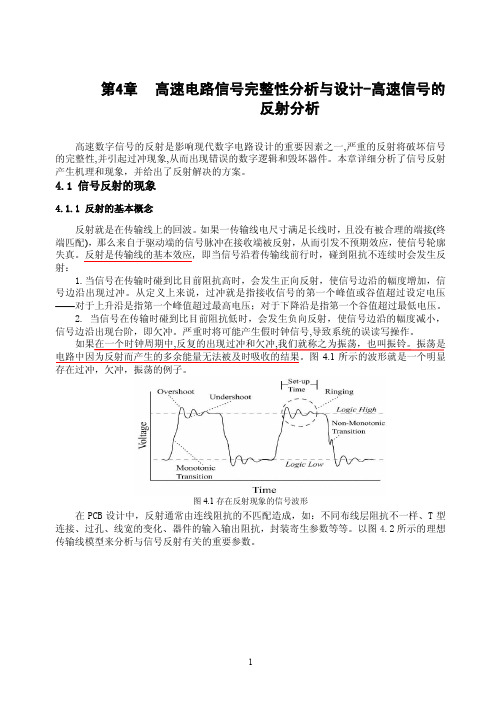

二、反射对信号的影响反射的结果对模拟正弦信号形成驻波,对数字信号则表现为上升沿、下降沿的振铃、过冲和欠冲。

过冲指信号跳变的第一个峰值(或谷值)超过规定值,对于上升沿是指最高电压,对于下降沿是指最低电压。

高速信号反射问题分析及端接解决方案

关于高速信号的反射问题分析及端接解决方案摘要:随着现在信息化程度不断加深,数字信号的传输速度加快,信号的工作频率也在不断提高,信号完整性问题日益突出。

本文针对高速pcb设计中容易出现的反射问题,对反射产生的现象和原理进行相关分析,并讨论几种减弱反射的阻抗匹配和端接方案,分析每个方法的电路组成和使用优点和缺点。

关键词:信号完整性;高速信号;反射;端接中图分类号:tn79 文献标识码:a 文章编号:1007-9599 (2012)23-0000-02在电子行业迅速发展的今天,高速化和集成化已经涉及到了生活的各个方面。

随着信号频率的提高,电路板的集成度增加,pcb层数的增加,导致各种信号完整性问题。

在数字电路中,反射引起的信号过冲和下冲,主要容易导致电路噪声容限降低和输入输出延迟等问题,严重时更是会击穿元器件。

1 反射的形成和机理在信号传输过程中,路径上的每一步都有相应的瞬态阻抗,如果信号沿互联线传播时受到的瞬态阻抗发生变化,一部分信号将会被反射,另一部分发生失真并继续传播下去。

主要引起的原因就是阻抗不匹配,阻抗失配越严重,反射影响就越大。

在这里,定义反射系数为ρ,表示信号反射的大小。

计算公式为:。

式中:是反射电压;是入射电压;是传输线瞬态阻抗;是反射处瞬态阻抗。

做设计时,当信号源内阻小于传输线阻抗时,源端出现负反射,引起常说的振铃现象,也叫做过衰减。

当信号源内阻大于传输线阻抗时,源端发生正反射,信号会有攀升现象,也叫欠衰减。

在高速pcb设计时,当出现反射引起的信号完整性问题,如何根据问题波形处理阻抗匹配是关键。

2 阻抗匹配与端接方案对于阻抗不匹配引起的信号反射,目标是根据传输线的特性阻抗的值,在源端或者终端进行阻抗匹配,使电路满足源反射系数或者负载反射系数为0.常用的有两种方法:(1)使负载阻抗与传输线阻抗匹配,即并行端接;(2)使源阻抗与传输线阻抗匹配,即串行端接。

只要负载端或源端有一个达到反射匹配,反射将被消除。

高速电路中平行传输线间的串扰分析及解决方案,串扰,传输线,H.

高速电路中平行传输线间的串扰分析及解决方案,串扰,传输线,HyperLynx,仿真1引言当信号线的长度大于传输信号的波长时,这条信号线就应该被看作是传输线(长线),并且需要考虑印制板上的线间互连和板层特性对电气性能的影响[2]。

在高速系统中,信号线通常被建模为一个R—L—C梯形电路的级连[2]。

由于信号线上各处的分布参数存在差异,尤其是在芯片的输入、输出引脚处,这种差异更加明显。

当几条高速信号并行走线且这些信号线之间的距离很近时,就不能忽略串扰对系统的影响,信号频率变高、边沿变陡、印刷电路1 引言当信号线的长度大于传输信号的波长时,这条信号线就应该被看作是传输线(长线),并且需要考虑印制板上的线间互连和板层特性对电气性能的影响[2]。

在高速系统中,信号线通常被建模为一个R—L—C梯形电路的级连[2]。

由于信号线上各处的分布参数存在差异,尤其是在芯片的输入、输出引脚处,这种差异更加明显。

当几条高速信号并行走线且这些信号线之间的距离很近时,就不能忽略串扰对系统的影响,信号频率变高、边沿变陡、印刷电路板的尺寸变小、布线密度加大等使得高速电路的串扰问题日益突出。

串扰过大可能引起电路的误触发,导致系统无法正常工作。

这就要求对高速串扰物体进行仿真分析并采取相应的措施使串扰减小到合理的范围。

2 串扰的理论基础串扰(crosstalk)是指在两个不同的电性能之间的相互作用。

产生串扰被称为Aggressor,而另一个收到串扰的被称为Victim。

通常一个网络既是Aggressor(入侵者),又是Victim(受害者),如图1所示。

依照离散式等效模间的线网称为干扰源网络来描述相邻传输线的串扰模型,传输线AB和CD的特性阻抗为Z0,且终端匹配电阻R=Z0。

如果位于A点的驱动源为干扰源,则A—B间的线网称为干扰源网络(AggressorLine),C—D间的线网称为被干扰网络(Victim Line)。

</tr>串扰是由同一PCB板上的2条信号线与地平面引起的,是2条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。

电路设计流程如何应对高速信号传输与时延问题

电路设计流程如何应对高速信号传输与时延问题在现代电子设备中,高速信号传输与时延问题是电路设计中常见且重要的挑战。

随着技术的发展,数据传输速度不断提高,传输信号的频率也越来越高,因此在电路设计中必须有效地解决高速信号传输和时延问题。

本文将介绍电路设计流程中如何应对这些问题,并提供一些解决方案和建议。

一、信号传输和时延问题的背景在理解电路设计流程中如何应对高速信号传输与时延问题前,有必要了解一些基本背景知识。

高速信号传输是指在电路中传输的信号具有很高的频率和数据传输速率,通常在几百兆赫兹(MHz)到几十吉赫兹(GHz)范围内。

这些高频信号具有短周期和快速上升/下降时间,因此容易受到电磁干扰、时延与信号失真的影响。

高速信号传输的时延问题主要包括传输线长、传播速度、信号损耗等因素。

在高速电路中,信号在传输线上会出现传播延迟,这可能导致时序错误和数据失真。

此外,传输线长度与信号传播速度之间的不匹配也会导致信号反射和时延不匹配。

因此,在电路设计流程中需要采取一系列措施来解决这些问题。

二、电路设计流程中的解决方案与实施步骤以下是电路设计流程中针对高速信号传输与时延问题的一般解决方案与实施步骤。

1. 信号完整性分析与仿真首先,必须进行信号完整性分析与仿真。

这包括对信号传输线路的建模和仿真,以评估传输线的传输损耗、时延和信号完整性。

利用专业软件来模拟高速信号在传输线上的行为,可以帮助工程师找出潜在的问题并采取相应的补救措施。

2. 优化电路拓扑结构根据仿真结果,可以对电路拓扑结构进行优化。

这可能包括调整布线、改变引脚分配和分割电源地平面等措施,以减少信号传输线的长度和复杂性,从而降低传输时延并提高信号完整性。

同时,还可以考虑使用阻抗匹配和终端电阻来减少信号反射和串扰。

3. 选择适当的材料和元件在高速电路设计中,材料和元件的选择非常重要。

选择低损耗、低时延的高速信号传输线材,如瓷介质或聚四氟乙烯(PTFE),可以提高信号传输的质量。

高速电路信号完整性分析与设计四--反射分析

源端 图 4.2 负载端 理想传输线模型及相关参数

理想传输线 L 被内阻为 R0 的数字信号驱动源 VS 驱动,传输线的特性阻抗为 Z0,负载阻抗 为 RL。理想的情况是当 R0=Z0=RL 时,传输线的阻抗是连续的,不会发生任何反射,但能量 一半消耗在源内阻 R0 上,另一半消耗在负载电阻 RL 上(传输线无直流损耗,即无耗传输线) 。 如果负载阻抗大于传输线的特性阻抗,Z0<RL 那么负载端多余的能量就会反射回源端, 由于负载端没有吸收全部能量,称为欠阻尼。如果负载阻抗小于传输线的特性阻抗,即 Z0> RL,负载试图消耗比当前源端提供的能量更多的能量,称为过阻尼。欠阻尼和过阻尼都会产 生反向传播的波形,某些情况下在传输线上会形成驻波(有三种情况,将在下面进行讨论) 。 当 Z0=RL 时,负载完全吸收到达的能量,没有任何信号反射回源端,称为临界阻尼。从系统 设计的角度来看,由于临界阻尼情况很难满足,所以最可靠适用的方式轻微的过阻尼,因为 这种情况没有能量反射回源端。 负载端阻抗与传输线阻抗不匹配会在负载端(B 点)反射一部分信号回源端(A 点) ,反 射电压信号的幅值由负载反射系数ρL 决定,见下式:

4

的直线,并延伸到负载特性曲线。与负载线的交点定义了 t= TD 时负载端的电压和电流,其 中 TD 是传输线的时间延迟。交替使用的斜率 1/Zo 和-1/Zo 重复这个过程,直到传输线矢量 到达负载线与源端线的交点。传输线矢量与负载及源头 I-V 曲线的交点给出了稳态的电压和 电流值。

图 4.6 用于计算非线性负载多次反射的 Bergeron 图

Байду номын сангаас

OSCILLOSCOPE

Design file: UNNAMED0.TLN Designer: fzpc BoardSim/LineSim, HyperLynx 7.000 6.000 5.000 4.000 Probe Probe Probe Probe 1:U(A0) 2:U(B0) 3:RS(A0).1 4:RS(A0).2

传输线反射原理

传输线反射原理传输线反射原理1. 什么是传输线反射?传输线反射是在电信领域经常遇到的现象。

当信号在传输线上传播时,由于传输线的特性以及信号的特点,信号会遇到反射,并在传输线上形成反射波。

2. 反射的原因传输线反射的原因主要是由于传输线的阻抗不匹配导致的。

当信号通过传输线传播时,如果传输线的特性阻抗与信号源或负载的阻抗不匹配,就会发生反射现象。

3. 传输线反射的影响传输线反射会对信号的传输产生不良影响,包括:•信号失真:反射波与原始信号叠加,导致信号形状发生变化。

•信号衰减:反射波使得信号的能量减少。

•系统性能下降:反射波会干扰其他信号的传输,降低系统的可靠性和性能。

4. 如何减小传输线反射?为了减小传输线反射,我们可以采取以下措施:•使用阻抗匹配器:通过在传输线上插入阻抗匹配器,使得传输线的阻抗与信号源或负载的阻抗匹配,减少反射的强度。

•使用终端阻抗匹配:根据传输线的不同特性,选择合适的终端阻抗,使之与信号源或负载的阻抗匹配。

•使用终端电阻:在传输线的终端加入合适大小的电阻,以消除反射波。

5. 如何测量传输线反射?为了测量传输线反射,可以使用以下方法:•反射系数:通过测量传输线上的反射波与入射波之间的幅度比值,计算反射系数,从而了解反射的程度。

•反射损耗:通过测量传输线上反射波的功率与入射波的功率之比,计算反射损耗,从而评估反射的影响程度。

•频谱分析:通过对传输线上的信号进行频谱分析,检测反射波的频率特性,从而了解反射的特点。

6. 总结传输线反射是影响信号传输质量的重要因素,主要由传输线阻抗不匹配引起。

为了减小反射的影响,我们可以采取阻抗匹配等措施。

同时,通过测量反射系数、反射损耗以及进行频谱分析等方法,我们可以评估反射的程度和特点,进一步优化传输线的性能。

7. 阻抗匹配器的原理阻抗匹配器是一种电路元件,用于调整传输线的阻抗,使其与信号源或负载的阻抗匹配。

阻抗匹配器的原理如下:•对于电阻匹配器,它是由一个电阻网络组成。

高速数字电路中信号反射的分析及解决方案

&’! 时 " 电路板上的信号导线就会呈现出传输线效

应 "整 个 系 统 为 分 布 式 系 统 "此 时 这 种 电 路 即 为 高 速电路 $ 当前 "电子系统与电路全面进入高速 % 高频 设计领域 $ 随着 () 工艺的不断提高 " 驱动器的上升 沿和下降沿由原来的十几 *+ 减小到几 *+" 有的甚 至达到 ,+ 量级 $ 这时必须要考虑由传输线效应引起 的信号完整性反射噪声问题 " 这已经成为高速数字 电路设计中的一个主要问题 $

图!

并联端接匹配示意图

&(!

串联端接 串行端接匹配技术是在源端的终端匹配技术 ’ 由

*++ 来 提 高 驱 动 器 的 能 力 ( 匹 配 电 阻 值 通 过 6?@ABC?:D 软件中的终端向导功能寻找最佳的端接

电 阻 值 (最 终 确 定 端 接

*AB21+GRS’*TU1V FWW;A2S’J4* 6FB17F:2GRS!:;TU1V UARG?S4J444:;A+

童 智 勇 ! 韩 月 秋 9 基 于 @4@) 模 型 的 仿 真 分 析 在 高 速 U)A 系统设计中的应用 0729 电子技术应用 !-/// !1- "1!.1%9 王 庄 昕 ! 汪 至 中 9 高 速 电 路 设 计 中 的 终 端 匹 配 技 术 0729 北 良 !张 涌 9 有效设计阻抗匹配电路改善数字电路信 方交通大学学报 !-//- !-& )$ ("5-.5&9 号传输的完整性 0729 电测与仪表 !-//& !- "!5.$!9

高速电路板的反射问题分析及仿真

高速电路板的反射问题分析及仿真文章基于PADS中Hyperlynx仿真软件结合实例仿真,分析高速电路板由于传输线上的阻抗不连续导致信号反射问题的抑制办法,并给出抑制反射的各种端接技术——串联端接、并联端接、戴维南端接,通过仿真结果进行对比阐述,此端接技术可以有效的抑制反射问题。

标签:高速PCB;反射;Hyperlynx仿真软件引言当今是高速化发展的信息时代,使得高速PCB的应用也越来越广泛。

针对于高速PCB的开发设计,必须认真研究分析具体情况,根据规则合理进行布局、布线。

文章基于PADS中Hyperlynx仿真软件,将高速电路板布局的相关问题比较透彻的进行仿真,结合理论分析,得出了一些有效的解决措施。

对于电子工程师今后绘制PCB板,有一定的指导意义。

1 产生反射的原因导致信号反射的原因是因为传输线上的阻抗不连续。

当传输线上的阻抗是连续的,不会产生反射,此为理想传输线模型。

如果传输线的特性阻抗小于负载阻抗,那么将负载端多余的能量反射回源端,由于负载端全部能量没有被吸收,故称这种情况为欠阻尼。

如果传输线的特性阻抗大于负载阻抗,此时与当前源端提供的能量相比,负载试图消耗更多的能量,因此通过反射通知源端输送更多的能量,这种情况称为过阻尼。

欠阻尼和过阻尼都会引起反向传播的波形,某些情况下在传输线上会形成驻波。

2 反射引起的振铃效应通过Hyperlynx软件,构建原理图建立仿真模型,将源端、接收端和传输线激活。

设置型号均为74HCXX:GATE-2的两接收端器件,型号为74AC11X:LINE-D的源端器件。

第一段为微带线传输线,第二段为带状线传输线,原理图如图1所示。

仿真结果如图2所示,因为阻抗不匹配,从图2可以发现,在阻抗突变界面上产生多次反射,不同程度的畸变(振铃)出现在源端波形和接收端波形中。

由于智能端接分析功能,可从Hyperlynx中查阅推荐电阻值为28.1欧姆。

再次进行仿真,如图3所示。

观察3.0ns之后的接收端和源端波形的波动幅度,比较图2和图3,可以看出端接电阻后的仿真图中源端和接收端的波动幅度较小。

高速线路PCB设计:传输线效应

高速线路PCB设计:传输线效应在高速线路中,由于传输线阻抗变化的问题,会有一部分的信号能量被反射,假设信号是一个跑步的人,人从A端想要跑到B端,在人经过线路每一块的导体时都会改变其电压值,一开始他在阻抗为50Ω的线路上跑,碰到过孔时阻抗的变化会产生让其速度变慢并产生一定的反弹,一直到终端为1MΩ时,此时几乎带着100%的能量被反弹回A端,反弹到A端时,由于A端为25Ω,会有一部分能量被留住,一部分能量被反弹,反弹的能量约为初始值的1/3。

而这1/3的信号再次到达B端后,又会被反射,以此类推。

在示波器上可以看到信号的上升沿和下降沿产生振荡直至能量减弱信号幅度随之减小。

基于上述模型,传输线会对整个电路设计带来一下效应:反射信号、延时和时序错误、多次跨越逻辑电平门限错误、过冲与下冲、串扰、电磁辐射信号轮廓失真信号在接收端将被反射,信号轮廓将失真。

失真变形的信号对噪声的敏感性、EMI若显著增加,这可能会造成整改系统的失效。

反射信号产生的主要原因:过长的布线、未进行阻抗匹配的接收端、未进行阻抗匹配的传输线(由于过量电容、电感的阻抗失配)信号延时信号在逻辑电平的高、低门限之间变化时,信号迟滞不跳变。

过多的信号延时可能导致时序错误和元器件功能混乱,通常在多个接收端时会出现问题。

信号延时产生的主要原因:驱动过载、布线过长信号电平错误信号的振荡发生在逻辑电平门限附近,在跳变的过程中可能多次跨越逻辑电平门限,导致逻辑功能紊乱。

信号过冲与下冲布线太长或信号变化太快都可以导致过冲与下冲发生,虽然大多数芯片器件接收端有输入保护二极管,但有时这些过冲电平会远远超过器件的电压范围,导致器件损坏。

信号串扰在一根信号线上有信号通过时,与之相邻的信号线上会感应出相关信号,异步信号和时钟信号更容易产生串扰。

解决串扰的方法:移开发生串扰的信号或屏蔽被严重干扰的信号。

信号距离地平面越近,或者加大线间距,都可以减少串扰的发生。

电磁辐射电流流过导体会产生磁场。

高速数据传输线路中的反射与传输特性分析

高速数据传输线路中的反射与传输特性分析随着科技的不断进步,高速数据传输已经成为现代社会中不可或缺的一部分。

无论是在通信领域还是在计算机网络中,高速数据传输线路的稳定性和可靠性对于数据的传输质量至关重要。

在实际应用中,我们常常会面临一些问题,比如信号的反射和传输特性。

本文将对高速数据传输线路中的反射和传输特性进行分析和探讨。

首先,我们来看一下高速数据传输线路中的反射问题。

当信号在传输线路中传输时,会遇到各种不同的障碍物,比如连接器、电缆、分支等。

这些障碍物会导致信号的反射,从而降低传输的质量。

反射信号会与原始信号相叠加,形成波形失真和信号衰减。

为了解决这个问题,我们可以采取一些措施,比如使用合适的连接器和电缆,以及安装衰减器和终端阻抗匹配器。

通过这些措施,可以有效减少信号的反射,提高传输的稳定性和可靠性。

接下来,我们来讨论高速数据传输线路的传输特性。

传输特性是指信号在传输线路中的衰减、延迟和失真等方面的表现。

在高速数据传输中,信号的传输特性对于数据的完整性和准确性起着重要的影响。

传输特性的分析可以帮助我们了解信号在传输过程中的变化,并采取相应的措施来优化传输效果。

首先是衰减特性。

随着信号在传输线路中传播,会逐渐衰减,导致信号强度的降低。

这是由于电缆材料和电磁波传播特性造成的。

为了减少衰减,我们可以选择合适的电缆和信号放大器,以增强信号的强度。

其次是延迟特性。

信号在传输线路中传播需要一定的时间,这就是延迟。

延迟会导致信号的同步问题,特别是在多路传输和远程通信中。

为了解决这个问题,我们可以使用延迟补偿器和时钟同步技术来保持信号的同步。

最后是失真特性。

高速数据传输线路中的失真主要包括时域失真和频域失真。

时域失真是指信号波形的扭曲和失真,频域失真是指信号频谱的变化。

为了减少失真,我们可以使用均衡器和滤波器来调整信号的波形和频谱。

综上所述,高速数据传输线路中的反射和传输特性是影响数据传输质量的重要因素。

通过分析和理解这些特性,我们可以采取相应的措施来优化传输效果,提高数据传输的稳定性和可靠性。

眼图医生:反射以及如何在高速系统处理反射

眼图医生:反射以及如何在高速系统处理反射欢迎回到“眼图医生”系列!在第一部分中,我强调了过度均衡一个信号导致的问题。

在本文中,我想探讨另一种常见的信号完整性问题:反射以及减轻反射的常见方式。

传输线理论告诉我们,源输出直至接收组件输入之间可能遇到的信号阻抗中的任何变化所产生的反射。

本质上讲,当交流(AC)信号在传输线向下行进时遭遇阻抗变化时,一些信号被反射回发射机,而该信号的其余部分将继续射向接收器。

信号经历的阻抗变化越大,反射越大,从而造成更多的信号失真。

阻抗变化受下列变化影响:导线宽度、相邻的导线和器件之间的间距,以及距参考平面的距离。

然而,印刷电路板(PCB)发生这些阻抗的变化时,并不总是那么明显。

一个非常有用的做法是检查PCB布局或系统图,以快速识别可能通过模拟需要多次分析的任何问题区域。

执行这类检查时,您应该跟踪从源到接收器的信号,寻找任何违反表1所列指南的行为,以及我接下来会讨论的故障点。

单端型差分型导线宽度必须是常量差分导线间距(耦合)和导线宽度必须是常量导线和其他器件和导线之间的间距应至少三倍于导线宽度恒定参考平面必须存在于导体整个长度的相同距离表1:最大限度减少反射的检查指南并非每次都必须遵守表1中有关传输线的指南。

以下为可能发生违反这些准则的常见区域:球栅阵列(BGA)走线——尤其针对通向内部行/列的多输入/输出(I / O)器件。

导通孔,您必须对此格外小心,以确保当传输线路信号导通孔经过PCB层时,看到一个恒定的固定参考平面。

在线器件和连接器。

器件和连接器的印刷电路板(PCB)封装与将它们相连的传输线封装相比,通常具有不同尺寸,这导致阻抗变化,从而造成反射变化。

当通向BGA器件或从BGA器件走线时,通过管理走线宽度和相邻的导通孔或焊盘的间距,来保持一个恒定阻抗。

图1所示为从DS125DF1610 16通道12.5Gbps重定时器数据表(一个196引脚数BGA器件)中摘录的一些常用注意事项。

电路设计流程如何应对高速信号传输与时延问题

电路设计流程如何应对高速信号传输与时延问题高速信号传输与时延问题是电路设计流程中常见的挑战。

在设计过程中,若不能有效地处理这些问题,可能会导致信号失真、时钟偏移和系统错误等不良后果。

因此,本文将介绍如何应对电路设计过程中的高速信号传输与时延问题。

一、信号传输问题的原因及影响高速信号传输问题主要源于信号的传输速度快、频率高、时钟精度要求高等特点。

以下是几个常见的信号传输问题及其影响:1. 时钟抖动:时钟抖动是指时钟信号频率的不稳定性,可能导致数据误差、时序错误等问题。

2. 串扰:高速信号传输时,信号之间可能发生串扰,导致信号失真。

3. 端口反射:当信号到达传输终点时,可能会发生端口反射,造成信号波形的失真和干扰。

二、解决高速信号传输问题的方法为了解决高速信号传输过程中遇到的问题,设计师可以采用以下方法:1. 时钟源的优化:合理选择时钟源,并增加时钟源的稳定性和精确度,可有效减少时钟抖动。

2. 信号完整性设计:利用滤波器、终端阻抗匹配和屏蔽罩等方法,避免信号之间的串扰,提高信号传输的准确性。

3. 驱动电流的控制:通过控制驱动电流的大小,能够减少端口反射产生的信号波形失真和干扰。

4. 延时补偿技术:通过引入延时补偿电路,可以对超高速信号进行时延补偿,以确保各个信号的同步传输。

三、电路设计流程中的注意事项在电路设计流程中,设计师需要注意以下几个方面:1. 信号完整性分析:在设计开始之前,应对电路进行信号完整性分析,包括信号的传输路径、时延要求、时钟精度等因素,为解决高速信号传输问题做准备。

2. 仿真与验证:在设计过程中,可以通过使用仿真工具对电路进行验证,以确定设计方案的可行性,避免出现一些隐蔽的高速信号传输问题。

3. 布局与布线规范:合理的布局和布线有助于降低信号传输过程中的串扰和反射等问题。

设计师应遵循相关的布局和布线规范,确保设计的完整性。

4. 时延分析与优化:通过时延分析工具,对信号传输过程中的时延进行评估和优化,以满足设计要求。

传输线与反射剖析

等于入射电压的幅度乘以反射系数。 反射系数描述了反

射回源端的那部分电压。传输系数描述了通过交界面进 入第二区域的部分入射电压。

5

传输线与反射

1.2 反射形成机理

为了减少和消除反射,在高速电路板设计中的

要注意四点:

1. 使用可控阻抗互连线;

2. 传输线两端至少有一端需要匹配;

3. 采用使多分支产生的影响最小化的布线拓扑结 构; 4. 使几何结构的不连续(突变)最小化。

26

传输线与反射

1.7 使用TDR测量反射

TDR ( Time Domain Reflectometry )时域反射测量

TDR能够发射边沿快速上升的阶跃信号,上升

边沿一般为 35ps 到 150ps ,然后测量反射的瞬

态幅度,利用反射电压得到被测器件的阻抗。

可以认为TDR是一个快速阶跃信号发生器和高

2

传输线与反射

1.0 引言

只要信号遇到瞬态阻抗突变,反射就会发生。

反射可能发生在线末端,或者是互连线拓扑结构发生 改变的地方,如拐角、过孔、T型结构、接插件等处。 因此设计互连线的目的就是尽可能保持信号受到的阻 抗恒定。 首先要保持互连线的特性阻抗恒定。因此,制造阻抗 可控电路板变得越来越重要。减小桩线(stub)长度、 使用菊花链代替分支结构、使用真正的点对点拓扑结 构等设计技巧,都是为了保持瞬态阻抗恒定。 其次改进拓扑结构设计并增加分立电阻元件应对阻抗 的突变,从而保证信号受到的瞬态阻抗恒定。

• 在区域1,分界处总电流由入射电流和反射电流决定, 它们传播方向相反。区域1分界面处净电流为Iinc-Irefl。 在区域2中,电流等于 Itrans 。分别从分界面两侧看进去, 电流相同的条件是:

传输线中信号反射的研究

传输线中信号反射的研究彭元杰,何怡刚,郭杰荣,汪胜辉,曹斌芳(湖南大学电气与信息工程学院 湖南长沙 410082)摘 要:现代高速电路设计中的信号完整性问题,尤其是过度的反射现象,常常造成严重的电路问题。

研究了反射形成的机理,即阻抗突变引发信号反射,通过分析给出了减少反射的措施。

由Altium Designer 的信号完整性分析工具对设想进行了验证,仿真结果表明:适当的端接能大幅度改善传输线中信号的反射。

关键词:信号完整性;阻抗突变;反射;端接中图分类号:TN41 文献标识码:A 文章编号:10042373X (2007)212179203Study for Signal R eflections in T ransmission LinesPEN G Yuanjie ,H E Y igang ,GUO Jierong ,WAN G Shenghui ,CAO Binfang(College of Electrical and Information Engineering ,Hunan University ,Changsha ,410082,China )Abstract :Signal integrity ,especially ,excessive reflection on modern high speed circuit design often cause serious circuit malf unction.The mechanism in forming reflection was studied ;that is ,the change in the instantaneous impedance caused signal reflection.The analysis worked out some measures on reducing reflection.The assumption was validated by signal integrity tool of Altium Designer.Simulation results indicate that proper termination can greatly improve signal reflection in transmis 2sion lines.K eywords :signal integrity ;change in the instantaneous impedance ;reflection ;termination收稿日期:2007203221基金项目:湖南省教育厅科研项目(05C717)1 引 言现代电子技术飞速发展,数字系统的时钟速率越来越高,信号边缘速率越来越快,PCB (印制电路板)系统已不再像以往设计中仅仅只是支撑电子元器件的平台,而变成了一个高性能的系统结构。

信号反射问题解决方法

为大家介绍一下高速信号的反射问题和解决方案:信号沿传输线向前传播时,每时每刻都会感受到一个瞬态阻抗,这个阻抗可能是传输线本身的,也可能是中途或末端其他元件的。

如果信号感受到的阻抗是恒定的,那么他就会正常向前传播,只要感受到的阻抗发生变化,信号就会发生反射。

信号发生反射的原因是源端与负载端的阻抗不匹配引起的,因此要进行阻抗匹配来解决反射问题,反射系数公式为:ρ为反射系数,Z1为信号最初所在区域的瞬时阻抗,Z2为信号进入另一区域的瞬时阻抗。

解决信号反射的方法有一下几种方法:一、串联终端匹配:示意图如下图(1)所示:图(1)在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

所以当R的电阻值等于Z0时反射信号完全被电阻吸收(假设理想的驱动器的输出阻抗为零)。

这种匹配方法简单在源端只需加入一个电阻原件,相对于其他匹配方法来说匹配电阻的功耗是最小的,不会给驱动器带来额外的直流电流,也不会给信号和地直接引入额外的阻抗,成本低,也节省电路板上的空间。

CPU作为输出信号时防止反射信号就用串联终端匹配,USB信号也采用这种方法做阻抗匹配。

二、并联终端匹配在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。

实现形式分为单电阻和双电阻两种形式。

1、单电阻并联端接:在芯片的输入阻抗很高的情况下,对单电阻形式来说,负载端的并联电阻值必须与传输线的特征阻抗相近或相等。

其连接方式如图2所示:图2这样设计的缺点是会带来直流损耗,匹配电阻接地会使信号的下降沿下降过快,会影响信号的占空比。

由于一般芯片的的输入阻抗很高,所以为了达到阻抗匹配需使匹配电阻阻抗和传输线阻抗相接近,即阻抗不会太大,所以电流驱动能力需要很强。

由于典型的TTL或CMOS电路的驱动能力很小,这种单电阻的并联匹配方式很少出现在这些电路中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

武汉理工大学班级:___电子与通信工程153班_____ 姓名:_________ ___________ 学号:________1049731503239_______ 教师:____ ____________高速电路传输线反射问题分析与解决(武汉理工大学信息工程学院,武汉,430070)摘要:高速数字信号的传输线反射问题是影响现代数字电路设计的重要原因因素之一,严重的反射将破坏信号的完整性,并引起过冲现象,从而出现错误的数字逻辑和影响电路上元器件的正常使用。

本文重点的分析高速电路中信号反射产生的原因,和给出解决反射问题的方案。

关键词:传输线;反射;解决方案Abstract: Reflection high-speed digital signal is an important factor affecting the modern digital circuit design, serious reflection would undermine the integrity of the signal, and cause overshoot phenomenon, which appears erroneous digital logic and destruction devices. This paper analyzes in detail the causes of signal reflections and phenomena, and give a reflection solution.Keyword: Transmission line;reflection; solution1.引言反射就是在传输线上的回波,如果传输线的长度满足长线时,且没有合适的终端匹配,那么来自于驱动端的信号脉冲在接收端被反射,从而引起非预期效应,使信号轮廓失真。

反射是传输线的基本效应,即当信号沿着传输线传输时,碰到阻抗不连续时会发生反射。

当信号在传输时,碰到了比目前高的阻抗时会发生正向发射,使得信号边沿的幅度增加,信号边沿会出现过冲。

过冲就是指接收信号的第一个峰值或者谷值超过了设定电压,对于上升沿是指第一个峰值超过最高电压;对于下降沿是指第一个谷值超过了最低电压。

当信号在传输时碰到比目前阻抗低时,会产生负向反射,使得信号边沿的幅度减小,信号边沿出现台阶,即欠冲。

严重时,可能会产生假时钟信号,导致系统的读写出现误读或者误写等操作。

在一个时钟周期中,反复的出现过冲和欠冲,我们就称之为振荡。

振荡是电路中因为反射而产生的多余能力无法及时吸收的结果。

在印制电路板中,反射通常由连线阻抗的不匹配造成,如:不同布线层阻抗不一样、T型连接、过孔、线宽的变化、器件的输入输出阻抗,封装寄生参数等等。

以下图 1.1理想传输线模型来分析与信号反射有关的重要参数。

理想传输线L被内阻R0的数字信号驱动源VS驱动,传输线的特性阻抗为Z0,负阻抗为Rl。

理想的情况是当且仅当R0=Z0=RL时,传输线的阻抗是连续的,不会发生任何反射,但能量一半消耗在源内阻R0上,另一半消耗在负载电阻RL 上。

如果负载阻抗大于传输线的特性阻抗,Z0<RL那么负载端多余的能量就会反射回源端,由于负载端没有吸收全部的能量,称为欠阻尼。

如果负载阻抗小于传输线的特性阻抗,即Z0<RL,负载试图消耗比当前源端提供的能量更多的能量,称为过阻尼。

欠阻尼与过阻尼都会产生反向传播的波形,某些情况下在传输线上会形成驻波。

当Z0=RL时,负载完全吸收到达的能量,没有任何信号反射回源端,称为临界阻尼。

从系统的设计与实现来看,由于临界阻尼情况很难满足,所以最可靠适用的方式是轻微的过阻尼,因为这种情况下没有足够的能量反射回源端。

负载端阻抗与传输线阻抗不匹配会发生在负载端,反射一部分信号回源端,反射电压信号的幅度由负载反射系数ρ决定,见下式:ρ=(RL-Z0)/(RL+Z0)(1.1)上式中,ρ称为负载电压反射系数,其定义是反射电压与入射电压之比。

由(1.1)可知,-1<ρ<1,当RL=Z0时,ρ=0,将不会产生反射。

即只要根据传输线的特性阻抗进行终端匹配,就能消除反射。

从原理上说,反射滤波的幅度可以大到入射电压的幅度,极性可正可负。

当RL<Z0时,ρ<0,处于过阻尼状态,反射滤波极性为负;当RL>0时,ρ>0处于欠阻尼状态,反射波极性为正。

如果传输线由两段不同特性阻抗的传输线组成,则连接点处也会产生信号的反射。

传输线上出现的分叉点就是这样一个阻抗不连续点。

反射信号产生的原因有,过长的走线;未被匹配终端的传输线,过量电容或电感以及阻抗失配。

当信号在终端处的阻抗不连续点被反射时,信号的一部分将反射回源头。

当反射信号到达源头时,若源头端阻抗不等于传输线阻抗就会产生第二次反射。

因此若传输线的两端在阻抗不连续的情况下,信号将在驱动线路和接收线路之间来回反射。

信号反射波因传输线的损耗将最后达到直流稳态。

2.产生反射现象的因素产生反射现象的原因的因素有信号上升沿时间、传输线的端接、短分支节线、容性分支节线、拐角和通孔、载重线、电感性间断线等。

2.1上升时间对反射的影响当上升时间变得大于传输线延迟时间的两倍时,传输线为短线,上升时间对波的形状不会存在影响。

因为信号到达负载端时,产生了反射,反射信号回到源端,但是此时源端的信号正处于上升阶段,这样的反射会在信号缓慢的上升过程中被吸收掉,从而不会影响信号电平的幅值。

但是如果上升时间小于传输线延时时间的两倍时,上升时间开始会对波的形状产生重要影响。

2.2串联传输线的反射影响通常,电路板上走线的宽度必须被压缩,因为它可能经过通孔或在密集区域的周围布线。

如果走线的宽度有一小段发生变化,特性阻抗就会改变,一般是增加。

有三个特征会决定短的传输线片段的影响:不连续性的延时,不连续性特性阻抗,信号上升时间。

当延时与上升时间相比很长时,反射系数将饱和。

反射系数的最大值与不连续性的反射有关。

2.3短分支传输线的反射影响分析短线的影响是比较复杂的,因为要考虑很多反射的问题。

当信号离开驱动端,首先会遇到分支点。

这里我们会看到两段传输线并联产生一个低的阻抗,则一个负反射将会返回到源端。

2.4容性分支在传输线中间引起的反射影响附着在走线中间的测试点,通孔,封装引线,甚至一小段分支,作用就像一个集总电容。

发射信号最初不会受到影响,但是当它从走线末端返回到源端时,就会受到反射回到接收端就为负的电压,使得接收到的信号下降,导致下冲。

传输线中间理想电容的影响依赖于信号的上升时间和电容的大小。

电容越大,阻抗越小,就会产生更大的负极性反射电压,导致接收端出现更大的下冲。

在时域内,电容的阻抗为:Zcap=V/(Cdv/dt)2.5拐角和通孔的影响当信号沿着均匀的互连线传输是,发射信号不存在反射集失真。

如果均匀互连线存在90度的弯角,就有阻抗的改变,则发生反射及信号的失真。

90度的拐角导致了均匀互连线阻抗的不连续性,影响了信号的完整性。

将90度的拐角换成45度的弯曲将会减小这种影响,如果改用常宽的圆弧状弯曲,影响会进一步的减小。

拐角对信号传输线的唯一影响是由于走线弯曲处的额外宽度,这个额外的线宽作用就像一个容性的不连续性。

这个容性的不连续性导致了信号的反射和时延。

如果走线的弯曲处是常宽的,走线宽度没什么变化,信号在拐弯的每一点遇到的阻抗都是相同的,那么就不会有反射。

3.抑制反射的端接技术消除反射现象的方法一般有:布线时的拓扑法和相应的端接技术。

常用布线时的拓扑结构有:点到店,菊花链,星型,分支和周期性负载等结构。

如下图所示:(a)点到点(b)菊花链(c)星型(d)远端分支(e)周期性负载点到点:点到点的拓扑结构比较简单,只要在发送端或接受端进行适当的阻抗匹配。

菊花链:当网络的整个走线长度延时小于信号的上升或者下降时间时,用菊花链拓扑结构会比较好,这时网络上的负载都可以看作为容性负载。

菊花链同时也限制了信号的速率,只能工作在低速电路中。

星型:使用星型的拓扑结构时,对每个分支都进行均衡设计,要求每个分支的接收端负载一致,并选择适当的匹配方式。

远端分支:跟星型类似,只不过分支是靠近接收端的。

这种拓扑结构中,也要限制远端stub的长度,使stub上的传输延时小于信号的上升沿,这样每个接收端都可以被看作为一个简单的容性负载。

周期性负载:周期性负载的拓扑结构同样要求每段stub的长度足够小,使得stub上的产生延时小于信号上升沿,这种主干传输和所有的stub端组合起来的结构可以看作为一段新的传输线,其特征阻抗要比原来主干传输性的特征阻抗小,传输速率也比原来的低,因此在进行足感匹配是要注意。

3.1单端端接技术传输线的长度符合下式的条件应使用端接技术:L>t/(2p)式中,L为传输线线长,t为源端信号的上升时间,p为传输线上每单位长度的带载传输延时。

传输线的端接原则:如果负载反射系数或源反射系数二者任一为零,反射将被消除。

通常采用两种方法(1)使负载阻抗与传输线阻抗匹配,即并行端;(2)是源阻抗与传输线阻抗匹配,即串行端接。

并行端接主要是在尽量靠近负载端的位置加上拉或者下拉电阻以实现终端的阻抗匹配,根据不同的应用环境,并行端接可以分成以下几类:(1)简单的并行端接这种端接方式是简单的在负载端加入一个下拉电阻来实现匹配,采用此端接的条件是驱动端必须能够提供输出高电平是的驱动电流以保证通过端接电阻的搞电平电压满足门限电压要求。

在输出为高电平的状态时,这种并行端接电路消耗电流过大,对于50欧的端接负载,维持TTL搞电平消耗电流高达48mA,因此一般器件很难靠近的支持这种端接电路。

优点:并行端接提供了一张简单的设计方案。

它是一种最简单的终接方案。

在大多数情况下,这种方法只需要一个附加元件,如果传输线的两端需要端接就需要要个电阻。

缺点:并行端接浪费电阻的直流功耗。

这种方法无论在高电平还是低电平,都需要驱动端具有稳定的直流,这样就增加了驱动端的直流负载。

当传输线的一端接容性负载时,端接时,上升沿斜率就会变化。

当末端接时,在时间常数Z0c内,电压是激励信号幅值的2倍。

当增加并行端接时,上升的时间会更快。

当采用并行端接时,必须注意到,对TTL级,线阻抗小于100欧姆时采用这种端接方式,要求直流输出为24mA。

因此对于电池驱动系统,不推荐采用并行端接方案。

另外,端接电阻要消耗多达0.25W的功率,这对于仅消耗几豪瓦功率的CMOS系统来说是不合适的,功耗的大小依赖于占空比:对于低占空比,连接电阻到底使用有最低功耗,对高占空比,连接电阻到VCC使得有最低的功耗。

还有一点就是,大的下拉电阻可能会使下降沿比上升沿快,这会导致占空比内信号的失真。