高速串行背板总线的仿真设计

高速PCB设计中GHz串行信号的完整性分析与仿真

An l ssa d S mu a i n o n e rt f GHz S ra i n li g S e d PCB De i n a y i n i lto n I t g iy o e i lS g a n Hih- p e sg

中板 级 高 速 P B设 计 将 面 临 新 的 信 号 完 整 性 问 C

应、 介质损 耗 、 间串扰等 进 行 了详 细 的分 析 ; 究 了这 些信 号 完整 性 问题 对 于 s 仿 真 的影 码 研 I 响 ; 出解决 G z 号完整 性 1 的方案 , 给 H 信 " 7题 并验 证 了方 案的有 效性 。 关键 词 : 串行 器/ 串器 ; 号完 整性 ; 耗 ; 解 信 损 预加 重 ; 图 眼

al e a l l x mp e.

K e r s: ERDES; sg a n e r y;ls ; p e e h ss y iga y wo d S in litg t i os r- mp a i ;e e da r m

随着对 信息 流量 需求 的不断 增 长 , 传统 并行 接

L P n DU a — ig L N J ・ n U ig . Xio n n 2 A u l g o

,

( .Isi t f nomai n ier g nomainE gneigUnvri ,Z e gh u4 0 0 ,C ia 1 n tueo fr t n E gn ei ,Ifr t n ier iest hn zo 5 0 2 hn ; t I o n o n y 2,P Ii I p r n,Ifr t nE gn eigU iest,Z e gh u4 0 0 oic at t nomai n ier nvri t a De me o n y hn zo 5 0 2,C ia hn )

《DDR4高速并行总线的信号完整性仿真分析》范文

《DDR4高速并行总线的信号完整性仿真分析》篇一一、引言随着科技的快速发展,电子系统的数据传输速率和数据处理能力需求不断提高。

在众多数据传输技术中,DDR4(第四代双倍速率动态随机存取存储器)以其高速并行传输的特点被广泛应用。

然而,随着数据传输速率的增加,信号完整性的问题变得日益突出。

因此,对DDR4高速并行总线的信号完整性进行仿真分析显得尤为重要。

本文将详细探讨DDR4高速并行总线的信号完整性仿真分析的方法和结果。

二、DDR4高速并行总线概述DDR4是一种同步动态随机存取存储器,其数据传输速率远高于前几代产品。

它采用并行传输的方式,通过多条数据线同时传输数据,大大提高了数据传输效率。

然而,随着数据传输速率的增加,信号的衰减、反射、串扰等问题也逐渐凸显出来,影响了信号的完整性。

三、信号完整性仿真分析方法为了确保DDR4高速并行总线能够稳定、高效地传输数据,我们采用了信号完整性仿真分析的方法。

这种方法通过对总线系统进行建模,模拟实际工作情况下的信号传输过程,从而预测和分析可能出现的信号完整性问题。

1. 建模与仿真:首先,我们根据DDR4总线的实际结构和工作原理,建立了详细的物理模型。

然后,利用仿真软件对模型进行仿真,模拟信号在总线上的传输过程。

2. 信号衰减分析:在仿真过程中,我们重点关注信号的衰减情况。

通过分析信号在传输过程中的幅度变化,我们可以了解信号的衰减程度和原因。

3. 反射与串扰分析:除了信号衰减外,我们还关注信号的反射和串扰问题。

通过仿真分析,我们可以找出反射和串扰的来源,并采取相应的措施进行优化。

4. 时序分析:时序是高速总线设计中另一个关键因素。

我们通过仿真分析时序参数,确保数据的正确传输和接收。

四、仿真结果与分析通过仿真分析,我们得到了以下结果:1. 信号衰减:在高速传输过程中,信号的衰减是不可避免的。

然而,通过优化电路设计和采用适当的匹配措施,我们可以有效地减小信号的衰减程度。

RapidIO高速串行总线的信号完整性仿真

面无法获得 芯片的有效 II BS模型 , 另外进入高频 、

射 频 研究 领域后 , 号输 出波 形更 像正 弦波 , 时必 信 这

使得数字信号和模拟信号 间的界线模糊 了, 传输信 号的波长和板 中传输线长度可 比拟 , 分布参数显现 出不 可忽 视 的影 响 , 而千 兆 位 板 级 设 计 与低 速板 从 设计 有着 显著 的 区别 , 其 背 板 的设 计 难 度 显著 增 尤 加。

Absr c : e Ra dl h g p e e a u in li e rt i a in i ef r d by usn ee to t a t Th pi O ih s e d s r lb s sg a ntg y smult s p ro me ig 3 i i o D l cr — ma n tc f l g e i e d EDA o t r . n p e—smu ain,h nte td p rmee s a o tPCB d sg r fe t ey i s fwa e I r i lt o t e i r se a a tr b u e i a e efc i l n v

a e mo i e . mu ain c a g st e i t o e e d n n e p re ea d r p a ra ,a d be o s r df d Si lto h n e hed sg me d d p n i g o x e inc n e e ttil n c me i n h a n s e a l e i to n h g p e e a usta s s in tc noo . n idip ns e d sg meh d i ih s e d s r lb r n miso e h l g b n i y Ke r s: pil hg p e e a us sg a ntg iy; i lto y wo d Ra d O ih s e d s r lb ; in li e rc smu ai n i

大规模高速背板的信号完整性设计与仿真

p e r s p e c t i v e o f s t a c k , wi r i n g a n d d r i l l i n g d e s i g n . I n t h e e n d , p r o j e c t s i g n a l i n t e g r i t y wa s a n a l y z e d b y P o w e r S I ( S i g r i t y

大 规模 高速 背 板 的信 号 完 整 性 第 4 4卷 第 4期 ( 总第 1 5 4期 )

大 规 模 高 速 背 板 的信 号 完 整 性 设 计 与仿 真

羿 昌宇,祖翔 宇

( 中 国 航 空 无 线 电 电子 研 究 所 ,上 海 2 0 0 2 4 1 )

A bs t r a c t : I n t h i s pa p e r, t h e ne c e s s i t y t o d e s i g n a l a r g e - s c a l e hi g h - s pe e d ba c k pl a ne i s a n a l y z e d f r o m t h e p e r s p e c t i ve o f J o i n t Ta c t i c a l Ra d i o S ys t e m s c a l e . S o me p r o bl e ms o f h i g h s p e e d ba c k pl a n e d e s i g n a r e a n a l y z e d , i n c l u d i ng r e le f c t i o n, c r o s s t a l k, wa s t a g e a n d a t t e nu a t i o n , p o we r i nt e g r i t y e t c , a n d s o me d e s i g n pr i n c i p l e s a r e p r e s e n t e d . An e f f e c t i v e b l u e p r i n t wa s d e s i g ne d f o r b a c k p I l a n e s y s t e m b a s e d o n S e r i a l Ra p i d l O h i g h — s pe e d b us ,a n a l y s i s a n d s c h e me we r e g i v e n ro f m t h e

高速串行背板总线的仿真设计

高速串行背板总线的仿真设计刘胜利 王砚方 沈国保(中国科技大学近代物理系 合肥 230026)摘要 本文描述了一种基于高速串行背板的系统级信号完整性仿真,重点分析了两种关键网络即1.25Gbps 的差分传输结构和125MHz 的时钟分配网络。

给出了仿真结果并分析了波形畸变的原因。

关键词 差分传输 信号完整性 仿真 背板1引言:近年来, 高速数字设计领域正在面对越来越多的信号完整性(SI )问题, 即更多的时候需将数字信号视为模拟信号并保证其传输质量。

这一方面是由于时钟频率不断提高,信号边沿越来越快,另一方面也是由于大规模,超大规模芯片的集成度不断增长及其广泛应用,电路板上的功能密度和信号的互连密度不断增加,从而使得电路的分布参数,电磁相互作用的场特性越来越明显。

另有其它原因如时间和经费等使信号完整性设计已逐渐成为高速数字设计任务中的一个重要组成部分,而仿真则成为信号完整性设计与分析的重要手段。

本设计考虑了一种用于高速串行空分开关互连结构的背板。

其串行数据互连的波特率是1.25Gbps ,这意味着最大可能的基频为625MHz ;数据以差分模式进行传输,信号上升沿和下降沿300PS 左右,按照H. Johnson 定义的转折频率(Knee Frequency)〖1〗,主要频率成份达1.17GHz ,因此一种子板-背板-子板的系统级信号完整性仿真,及由此确定一种优化的背板PCB 参数成为整个系统设计不可缺少的部分。

此外,系统主时钟分配网络也采用了差分传输模式,信号上升沿和下降沿350PS 左右,它提供了125MHz 的系统时钟,也作为仿真设计中重点考虑的关键网络。

尽管这样一种千兆位互连背板的设计还需考虑其它信号完整性因素,但限于篇幅,这里仅就上述两种关键网络的仿真分析进行描述。

本文首先讨论了仿真前模型的选择和提取及相关的设计考虑,然后基于布局前的系统级仿真确定了背板的PCB 层叠结构及布线参数,最后详细描述了系统设计完成后即布局后的仿真结果。

高速串行RapidIO总线背板信号完整性仿真研究

高速串行RapidIO总线背板信号完整性仿真研究

李彦;吴培明;寇小明

【期刊名称】《鱼雷技术》

【年(卷),期】2011(019)003

【摘要】信号完整性(SI)是高速电路设计面临的一个主要问题.对109Hz以上高速信号的信号完整性问题从原理上进行了详细分析,并针对损耗、串扰、反射等因素提出了改善信号完整性的方法.在高速串行RapidIO总线背板的设计中,探索出一套利用HyperLynx工具进行仿真分析和设计验证的方法,即利用前仿真工具LineSim 对影响信号完整性的主要参数进行评估,形成设计指导数据;利用后仿真工具BoardSinn对布线后的高速背板进行验证,从理论上证明了高速串行RapidIO总线背板的设计是可行的.

【总页数】5页(P167-171)

【作者】李彦;吴培明;寇小明

【作者单位】中国船舶重工集团公司第705研究所,陕西,西安,710075;中国船舶重工集团公司第705研究所,陕西,西安,710075;中国船舶重工集团公司第705研究所,陕西,西安,710075

【正文语种】中文

【中图分类】TJ630.6

【相关文献】

1.大规模高速背板的信号完整性设计与仿真 [J], 羿昌宇;祖翔宇

2.RapidIO高速串行总线的信号完整性测试 [J], 侯红英

3.RapidIO高速串行总线的信号完整性仿真 [J], 侯红英

4.高速串行总线RapidIO与PCI Express协议分析比较 [J], 梁小虎;王乐;张亚棣

5.高速背板互连的信号完整性仿真方法 [J], 孔繁;盛卫星;马晓峰;韩玉兵

因版权原因,仅展示原文概要,查看原文内容请购买。

《2024年DDR4高速并行总线的信号完整性仿真分析》范文

《DDR4高速并行总线的信号完整性仿真分析》篇一一、引言随着科技的不断进步,高速并行总线技术得到了广泛应用。

作为当前最流行的内存接口之一,DDR4(Double Data Rate 4 Generation)技术以其高速、高带宽和低功耗等优势成为许多现代电子系统的重要组成部分。

然而,在高速传输过程中,信号完整性的问题往往对系统性能和可靠性产生重大影响。

因此,本文旨在通过对DDR4高速并行总线的信号完整性进行仿真分析,为相关研究和应用提供理论依据和实践指导。

二、DDR4高速并行总线概述DDR4是一种先进的内存技术,其数据传输速率远高于传统的DDR3和DDR2等内存技术。

DDR4总线采用并行传输方式,通过多个信号线同时传输数据,从而大大提高了数据传输速率和带宽。

然而,随着数据传输速率的提高,信号完整性的问题愈发突出。

三、信号完整性仿真分析方法针对DDR4高速并行总线的信号完整性仿真分析,本文采用以下方法:1. 建模:首先建立DDR4高速并行总线的模型,包括信号线、电源线、地线等。

2. 仿真:使用专业的仿真软件对模型进行仿真分析,包括时序分析、噪声分析、串扰分析等。

3. 评估:根据仿真结果,评估信号完整性的各项指标,如信号衰减、串扰、反射等。

四、仿真结果与分析1. 时序分析:通过仿真分析,我们发现DDR4总线的时序性能良好,各信号线的传输延迟差异较小,满足高速传输的要求。

2. 噪声分析:在噪声分析中,我们发现由于电磁干扰和电源噪声等因素的影响,部分信号线上出现了较大的噪声。

这可能导致信号失真和误码等问题,影响系统的性能和可靠性。

3. 串扰分析:串扰是高速并行总线中常见的信号完整性问题之一。

通过仿真分析,我们发现不同信号线之间的串扰较为严重,特别是在高频传输时。

这可能导致信号的畸变和误判,影响系统的正常工作。

4. 信号衰减与反射:在仿真过程中,我们还发现信号线上的衰减和反射问题较为突出。

由于传输线的阻抗不匹配和信号的反射等因素,可能导致信号的失真和畸变。

高速互连系统的仿真设计

高速互连系统的仿真设计(Simulation For High-Speed Interconnect System)网络事业部南京研究所朱顺临摘要摘要本文介绍了运用Cadence公司的SigXplor和Ansoft公司的Spicelink解决高速PCB 互连系统设计中的信号完整性问题,着重介绍基于Spicelink电磁场分析工具的3D建模方法,基于Schematic Capture 的Spice仿真过程,运用Cadence公司的Sigxplor实现线卡和背板组成的高速互连系统的仿真过程和设计优化过程。

系统级仿真提高了我们对系统设计结果的可预见性,通过仿真能及时优化设计方案,它和高速测量一起,将成为我们解决高速设计问题的基本方向。

关键词关键词系统级仿真、场分析、三维建模、Spice仿真、模块化引言引言利用Cadence公司的SpecctraQuest和SigXplor设计工具进行系统级前仿真可以验证设计方案的可行性,SpecctraQuest和SigXplor设计工具不仅可以对一块PCB板的信号流进行分析,而且可以通过设置Design Link对同一系统内其它组成部分如背板、接线器、传输线及其各个功能模块或插板进行综合分析,完成系统级的SI分析。

针对系统级的SI分析工具可以对多板、接线器等系统组成部分进行分析,得出一系列的约束条件(Constraint)给系统的各个组成部分。

在验证系统设计方案的同时得出解决SI问题的最大设计空间(Solution space),通过系统级仿真,我们可以完成关键元器件的选择、系统时钟网络及系统各部分的延迟的优化、拓扑结构的选择及重要网络的端接方案的确定等设计过程。

在系统级SI仿真和设计验证中,还要考虑系统对不同功能单元的兼容性,互换性、系统的满载和空载(如空载时Stub对SI的影响),不同拓扑结构对SI的影响,要考虑到各个功能单元的最大时序余量,给它们更大的时序空间,增加各个模块的可实现性。

使用芯禾Expert系列软件实现高速链路仿真

使用芯禾Expert系列软件实现高速链路仿真高速串行通道(Serdes)是目前绝大多数通信系统中用到的数据传输通道,为满足人们对、视频传输所带来的日益增长的带宽需求,通信设备中高速串行通道上的信号速率以每五年翻一倍的速度举行提升。

从最初的单链路10Mb/s速率一路提升到当前业界广泛应用的25Gb/s速率,而且将来还会向着56G、112G等更高速率持续演进,图1所示即为以太网联盟定义的以太网速率升级路途图。

图1 将来五年以太网速率升级路途图对于几十Gbps速率的高速串行链路,单纯依赖以往的设计阅历,已经无法确保高速链路设计的正确性。

因此,需要采纳各种高频电磁场的工具软件,在设计前和设计完成后对高速串行链路举行前仿真和后仿真分析,充分验证高速串行链路的各种电气性能是否满足设计要求,从而确保一次性地设计胜利,满足产品上市的时光需求。

当前业界已经有多款高频电磁场仿真工具,如ANSYS Electronics系列仿真工具(包括HFSS、SIWave、SystemSI、Nexxim等)、KeySight ADS/EMPro等、 Sigrity仿真套件、Synopsys HSpice等。

这些EDA 仿真软件均为国外大厂开发,且经过了多年的业界应用,软件的功能、易用性、仿真精度等各方面都经过了充分验证。

但正如前文所述,人们对以太网带宽持续提升的迫切需求使得路由器、交换机、服务器等数据通信设备中的高速串行链路速率飞快提升,如何实现对更高信号速率链路的精确建模分析,成为了当前EDA仿真软件领域各个厂家均需面向的课题。

另外,随着信号速率的提升,高速链路中以往可以忽视的一些影响因素,如绿油影响、BGA焊球、走线泪滴等,在当前的仿真模型中均需考虑进去。

芯禾的Expert系列软件(Via Expert、Snp Expert、Channel Expert)是彻低在国内研发的一套高频电磁场仿真分析软件,在吸取了上述各第1页共13页。

高速串行信号仿真方法

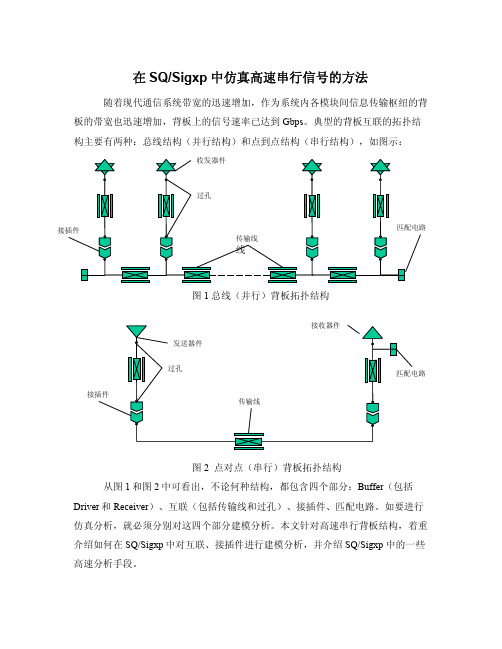

在SQ/Sigxp中仿真高速串行信号的方法随着现代通信系统带宽的迅速增加,作为系统内各模块间信息传输枢纽的背板的带宽也迅速增加,背板上的信号速率已达到Gbps。

典型的背板互联的拓扑结构主要有两种:总线结构(并行结构)和点到点结构(串行结构),如图示:图1 总线(并行)背板拓扑结构图2 点对点(串行)背板拓扑结构从图1和图2中可看出,不论何种结构,都包含四个部分:Buffer(包括Driver和Receiver)、互联(包括传输线和过孔)、接插件、匹配电路。

如要进行仿真分析,就必须分别对这四个部分建模分析。

本文针对高速串行背板结构,着重介绍如何在SQ/Sigxp中对互联、接插件进行建模分析,并介绍SQ/Sigxp 中的一些高速分析手段。

互联:1传输线:理想传输线等效模型如图示:图3 理想传输线等效模型从图中可看出,当信号沿传输线传输时,完成对每一段LC 电路的充放电。

此时有两个主要的参数来表征传输线的特性:特征阻抗Z0和信号传输速率V 。

特征阻抗:C L Z /0= 其中L 为单位长度电感,C 为单位长度电容。

信号传输速率: LC V 1= 其中L 为单位长度电感,C 为单位长度电容。

以上是理想传输线的等效电路模型,从等效电路上看,它是无损的,通常在频率不高,损耗不明显的情况下使用。

而当信号频率升高,传输线上的衰减就不可忽略。

此时,就需要考虑由导体串连等效电阻和介质并联等效电导引起的损耗,此时我们就需要使用有损传输线模型。

有损传输线等效模型如图:图4 有损传输线等效模型从图中可以看出,表征损耗的是等效串连电阻R 和等效并联电导G ,下面分别说明。

等效串连电阻R :直流电阻和趋肤效应引起的电阻。

直流电阻为导体本身的电阻,由导体的物理结构和导体的电阻率决定。

对于PCB 上常用的传输线结构带状线和微带线,其直流电阻近似计算公式为: wt R ρ10= 其中R 为单位长度电阻(ohm/inch ),ρ为导体体电阻率(ohm*meter ),w 为线宽(mils),t 为线厚(microns)。

基于GTH规范的高速背板性能仿真与优化设计

2018年&月第41卷第2期舰船电子对抗SHIPBOARD ELECTRONIC COUNTERMEASUREApr .2018V 〇1.41N 〇.2基于E T H 规范的高速背板性能仿真与优化设计李春来,顾军,王宁,徐瑞荣,黎仁刚(中国船舶重工集团公司第七二三研究所,江苏扬州225101)摘要:在复杂信号系统中,多模块之间数据信号和控制信号的传输都是通过背板实现。

随着所需要处理信号流量的剧增,其面临着传输通道信号速率高达10Gbps 以上、通道包含2组连接器和过孔等阻抗不连续单元以及较长有损 传输线等巨大挑战。

通过HFSS 对传输单元进行建模与S 参数提取,使用Siwave 、Desigrnr 进行通道整体建模仿真, 采用协调仿真方法,对通道反射、损耗、眼图等指标进行预测。

根据仿真结果指导性能优化设计,成功实现基于ETH 收发器规范的高速传输通道设计。

关键词:背板;信号完整性;高速#且抗中图分类号:TN 911.7文献标识码:B文章编号:CN 32-1413(2018)02-0106-06D 01:10.16426/j .cnki .jcdzdk .2018.02.024Performance Simulation and Optimization of High Speed BackplaneBased on GTH SpecificationLIC hun -lai ,G U Ju n ,W A N G N in g ,X U R u i -r 〇n g ,LIRen-gang(The 723 Institute of CSIC , Yangzhou 225101,China )Abstract :In c 〇mplex signal system s , the transmission 〇f data and c 〇ntro 1 signals among multiple modules is achieved through t he backplane.With the signal flow which is required to be processed increases dramaticlly,the system faces challenges such as the signal rate of transmission channels is more than 10 Gbps,the discontinuous units of impedance:two connectors and vias hole in the chan nel , etc ., and long transmission lines with loss.The transmissionunitis modeledanters are extractedthrough H F S S , theSiwave andDesignerareused to model anwhole channel , the coordinate simulationmethod is used to predict the channel reflectioneye pattern . The performance optimization design is guided according to simulation results , high speed transmission channel design based on GTH transceiver specification is realized successfully .Key words : backplane ; signal integrity ; high -speed ; impedanceA n sysH F S S 软件基于模型的物理原型,利用有限元法(FEM ),以变分原理与剖分插值为基础,把连 续求解区域分割成一定数目的小单元,对给定边界的 泛函求极值而得出麦克斯韦方程组,最终得出整个研 究区域的电磁场分布情况。

计算机硬件设计中的高速串行接口仿真与优化

计算机硬件设计中的高速串行接口仿真与优化在计算机硬件设计领域中,高速串行接口(High-Speed Serial Interface)的仿真与优化是非常重要的研究课题之一。

本文将介绍高速串行接口的概念、仿真的意义以及优化方法,并探讨如何在硬件设计中应用这些技术,以提高计算机系统的性能与可靠性。

一、高速串行接口概述高速串行接口是一种用于在计算机系统间传输数据的通信接口,其通过串行传输方式将数据以一定的速率发送和接收。

相比于传统的并行接口,高速串行接口具有带宽高、传输距离远、抗干扰能力强等优点。

它被广泛应用于存储系统、网络设备、图像处理等领域,能够满足现代计算机系统对高速数据传输的需求。

二、高速串行接口仿真的意义1. 性能评估:通过仿真模拟,可以对高速串行接口的性能进行评估。

包括信号的时钟频率、时序约束、传输速率等参数的计算与分析,为系统设计提供参考依据。

2. 信号完整性分析:高速串行接口的传输过程中,存在信号衰减、噪声干扰等问题,仿真能够模拟和分析这些问题,判断是否会对数据传输造成影响,并采取相应的优化措施。

3. 减少开发成本:通过仿真可以在设计阶段就发现问题并进行优化,降低错误带来的成本和延误,避免不必要的硬件修改和重新设计。

三、高速串行接口仿真方法1. 信号完整性仿真:通过电磁场仿真软件,模拟高速信号在PCB板上的传输过程,分析信号的传输电平、抖动、衰减等情况,为电路布局和排线提供指导。

2. 时序仿真:通过时序仿真工具,模拟高速串行接口中各个时钟信号的频率、相位差等参数,确保数据的稳定和正确传输。

3. 信号完整性仿真:利用特定软件对高速串行接口的信号进行仿真,模拟信号传输过程中的各种干扰以及对系统性能的影响,并提供针对性的优化方案。

四、高速串行接口优化方法1. 缓冲技术:通过增加缓冲器的数量和大小,控制数据的传输速率和稳定性,降低信号噪声与抖动。

2. 驱动技术:采用合适的驱动技术,如预加重和均衡技术,来提高信号的传输质量,降低传输误码率。

高速串行差分信号的PCB设计与仿真

【摘要】随着电子设计技术的不断进步,要求更高速率信号的互连。

在传统并行同步数字信号的数位和速率将要达到极限的情况下,开始转向从高速串行信号寻找出路。

HyperTansport(by AMD),Infiniband(by Intel),PCI-Express(by Intel)等第三代I/O总线标准(3GI/O)不约而同地将低压差分信号(LVDS)作为下一代高速信号电平标准。

本文将从LVDS信号仿真、设计,等多方面探讨合适的LVDS信号的实现。

关键词:LVDS,PCB设计,仿真,信号完整性一、前言随着近几年对速率的要求快速提高,新的总线协议不断的提出更高的速率。

传统的总线协议已经不能够满足要求了。

串行总线由于更好的抗干扰性,和更少的信号线,更高的速率获得了众多设计者的青睐。

而串行总线又尤以差分信号的方式为最多。

而在我们的项目中的PCI- Express串行信号线正采用了LVDS技术。

所以以下的叙述中都以串行信号中LVDS信号为代表讲述。

二串行LVDS信号的PCB设计1.差分信号的概念和优点差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。

何为差分信号?通俗地说,就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”,而承载差分信号的那一对走线就称为差分走线。

差分信号与普通的单端信号走线相比,最明显的优势体现在以下三个方面:(1)抗干扰能力强。

因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。

(2)能有效抑制EMI。

由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消。

耦合的越紧密,互相抵消的磁力线就越多。

泄露到外界的电磁能量越少。

(3)时序定位精确。

由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阀值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。

高速背板设计考虑和创新解决方案

采用分布式电源为背板上的不同模块提供电力,提高电源的稳定性和可靠性。

利用热管的导热性能,将背板上的热量迅速传导到其他部位,降低背板的温度。

热管技术

采用液体冷却剂,通过循环流动带走背板上的热量,提高背板的散热效率。

液冷技术

使用导热界面材料填充背板和散热器之间的空隙,提高热传导效率。

导热界面材料

05

金属复合材料

02

利用金属的导热性和强度,与非金属材料结合,提高背板的热传导性和结构强度。

陶瓷材料

03

具有高硬度、高耐磨性以及优异的电绝缘性能,可用于制作高频连接器。

使用分布式电源

在电源入口和出口设置滤波器,减少电源噪声对背板的影响。

电源滤波技术

优化电源线布局

合理安排电源线的布局,减少电源线之间的相互干扰,提高电源传输效率。

CHAPTER

设计实例和分析

缺点

需要开发新的连接器技术和生产工艺,成本较高。

总结词

新型连接器技术能够提高背板的电气性能和可靠性。

详细描述

采用新型连接器技术,如嵌入式连接器,能够实现更紧密的连接,提高信号传输质量和速度,同时减少连接器之间的接触电阻和信号串扰。

优点

提高背板的电气性能和可靠性,实现更高速的数据传输。

连接器设计

03

CHAPTER

常见高速背板设计问题

信号在传输过程中,由于阻抗不匹配、线路损耗等因素,导致信号幅度减小。

信号衰减描述

信号传输距离增加、高频率信号的能量损失更大、电路板阻抗不匹配等。

原因分析

数据传输速率降低、误码率增加、系统性能下降。

影响

信号在传输线中遇到阻抗突变时,会产生反射波,影响信号完整性。

高速连接器和背板测试分析及方案

高速连接器和背板测试分析及方案随着数字电路工作速度的提高,PCB、连接器、背板上信号的传输速率也越来越高,如HDMI 1.3的信号速率达到3.4Gb/s,USB3.0的信号速率已经达到5Gb/s,PCI-E Gen3的信号速率更是高达8Gb/s,SATA下一代的信号速率将达到12Gb/s。

在较低数据速率时,驱动器和接收机一般是导致信号完整性问题的主要因素。

以往人们通常把印刷电路板、连接器、电缆和过孔当成是简单的部件,稍加考虑或者无需考虑其他因素就可以很容易地把它们组成一个系统。

现在,从逻辑电平0 到逻辑电平1 的数据上升时间已不足100 ps,如此高速的信号在传输线路上传输时会形成微波传输线效应,这些传输线效应对于信号的影响会更加复杂。

很多系统内的物理层有许多线性无源元件,它们会因阻抗不连续而产生反射,或者对于不同频率成分有不同的衰减,因此作为互连的物理层特性检验正变得日益关键。

一般用时域分析来描述这些物理层结构的特征,为了获得一个完整的时域信息,必须要测试反射和传输(TDR和TDT)中的阶跃和脉冲响应。

随着信号频率的提高,还必须在所有可能的工作模式下进行频域分析,以全面描述物理层结构的特征。

S参数模型说明了这些数字电路所展示出的模拟特点,如不连续点反射、频率相关损耗、串扰和EMI等。

表1是HDMI 对于线缆的阻抗和衰减要求的一个例子:表1 HDMI对线缆的阻抗和衰减的要求全面的特性检定包括前项和后向传输和反射、所有可能的工作模式以及频域和时域,表2是进行物理层检定通常要测试的时域和频域参数。

表2物理层检定通常需要测试的时域和频域参数传统PCB板的阻抗测试方法不能完全描述信号经过传输线路后的行为特点,因此对于这些高速传输线和连接器的分析也要把时域和频域结合起来,采用更高级的分析方法,其中一种很有效的工具就是物理层测试系统(PLTS)。

PLTS系统的功能物理层测试系统(PLTS)适合用于高速连接器、背板、PCB或电缆的信号完整性分析。

高速数字电路的设计与仿真

高速数字电路的设计与仿真高速数字系统设计成功的关键在于保持信号的完整,而影响信号完整性(即信号质量)的因素主要有传输线的长度、电阻匹配及电磁干扰、串扰等。

设计过程中要保持信号的完整性必须借助一些仿真工具,仿真结果对PCB布线产生指导性意见,布线完成后再提取网络,对信号进行布线后仿真,仿真没有问题后才能送出加工。

目前这样的仿真工具主要有cadence、ICX、Hyperlynx等。

Hyperlynx 是个简单好用的工具,软件中包含两个工具LineSim和BoardSim。

LineSim用在布线设计前约束布线和各层的参数、设置时钟的布线拓扑结构、选择元器件的速率、诊断信号完整性,并尽量避免电磁辐射及串扰等问题。

BoardSim用于布线以后快速地分析设计中的信号完整性、电磁兼容性和串扰问题,生成串扰强度报告,区分并解决串扰问题。

作者使用LineSim工具,对信号的阻抗匹配、传输线的长度、串扰进行了仿真分析,并给出了指导性结论。

阻抗匹配高速数字信号的阻抗匹配非常关键,如果匹配不好,信号会产生较大的上冲和下冲现象,如果幅度超过了数字信号的阈值,就会产生误码。

阻抗匹配有串行端接和并行端接两种,由于串行端接功耗低并且端接方便,实际工作中一般采用串行端接。

以下利用Hyperlynx仿真工具对端接电阻的影响进行了分析。

以74系列建立仿真IBIS模型如图1所示。

仿真时选择一个发送端一个接收端,传输线为带状线,设置线宽0.2mm和介电常数为4.5(常用的FR4材料),使传输线的阻抗为51.7Ω。

设置信号频率为50MHz的方波,串行端接电阻Rs分别取0Ω、33Ω和100Ω的情况,进行仿真分析,仿真结果如图2所示。

图中分别标出了匹配电阻是0Ω、33Ω、100Ω时接收端的信号波形。

从波形看出,0Ω时波形有很大的上冲和下冲现象,信号最差;100Ω时信号衰减较大,方波几乎变成了正弦波;而匹配电阻是33Ω时波形较好。

理想的匹配电阻值,可以利用软件的terminatorWizard工具,自动根据器件的参数模型算出最佳匹配电阻为33.6Ω,实际应用中可以选用33Ω。

高速背板设计心得(谢宝国)参考模板

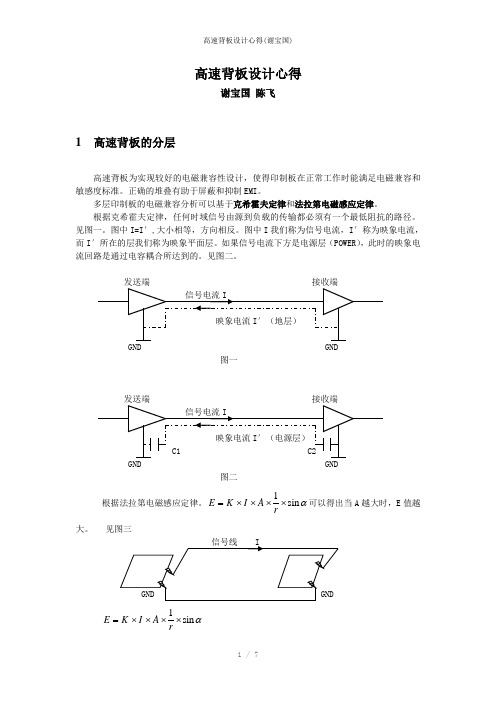

高速背板设计心得谢宝国 陈飞1 高速背板的分层高速背板为实现较好的电磁兼容性设计,使得印制板在正常工作时能满足电磁兼容和敏感度标准。

正确的堆叠有助于屏蔽和抑制EMI 。

多层印制板的电磁兼容分析可以基于克希霍夫定律和法拉第电磁感应定律。

根据克希霍夫定律,任何时域信号由源到负载的传输都必须有一个最低阻抗的路径。

见图一。

图中I=I ′,大小相等,方向相反。

图中I 我们称为信号电流,I ′称为映象电流,而I ′所在的层我们称为映象平面层。

如果信号电流下方是电源层(POWER ),此时的映象电流回路是通过电容耦合所达到的。

见图二。

图一发送端 接收端图二根据法拉第电磁感应定律。

αsin 1⨯⨯⨯⨯=rA I K E 可以得出当A 越大时,E 值越大。

见图三αsin 1⨯⨯⨯⨯=rA I K E图三根据以上两个定律,我们得出在多层印制板分层及堆叠中应遵徇以下基本原则; ① 电源平面应尽量靠近接地平面,并应在接地平面之下。

② 布线层应安排与映象平面层相邻。

③ 电源与地层阻抗最低。

其中电源阻抗Z 0=WD⨯επ120其中D 为电源平面同地平面之间的间距。

W 为平面之间的面积。

④ 在中间层形成带状线,表面形成微带线。

两者特性不同。

重要信号线应紧临地层。

① 六层板在背板设计中推荐D 种情况,在六层板中,它的EMI 性能最优。

② 八层板表三的布线层。

同时电源平面阻抗也比较低。

如果是4个信号层,以表三中E 种情况为最好。

每个信号层都是良好布线层。

在这几种情况中,相邻信号层应布线。

③ 十层板在于两信号层相接,在布线上要注意。

总之,PCB 的分层及叠层是一个比较复杂的事情。

有多方面的因素要考虑。

2高速背板的布线高速信号的布线主要是考虑信号的完整性,即延迟、反射、串扰、同步切换噪声(SSN)和电磁兼容性(EMI)。

2.1时钟信号线时钟信号线既要考虑信号完整性问题,又要考虑EMI问题。

它的处理对高速背板性能的优劣。

时钟信号线在背板中一般走在内层,最好夹在两个平面层之间进行走线,走线的阻抗须进行控制,在不同层切换时保证阻抗的一致性,以防信号反射对时钟的影响。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

高速串行背板总线的仿真设计刘胜利 王砚方 沈国保(中国科技大学近代物理系 合肥 230026)摘要 本文描述了一种基于高速串行背板的系统级信号完整性仿真,重点分析了两种关键网络即1.25Gbps 的差分传输结构和125MHz 的时钟分配网络。

给出了仿真结果并分析了波形畸变的原因。

关键词 差分传输 信号完整性 仿真 背板1引言:近年来, 高速数字设计领域正在面对越来越多的信号完整性(SI )问题, 即更多的时候需将数字信号视为模拟信号并保证其传输质量。

这一方面是由于时钟频率不断提高,信号边沿越来越快,另一方面也是由于大规模,超大规模芯片的集成度不断增长及其广泛应用,电路板上的功能密度和信号的互连密度不断增加,从而使得电路的分布参数,电磁相互作用的场特性越来越明显。

另有其它原因如时间和经费等使信号完整性设计已逐渐成为高速数字设计任务中的一个重要组成部分,而仿真则成为信号完整性设计与分析的重要手段。

本设计考虑了一种用于高速串行空分开关互连结构的背板。

其串行数据互连的波特率是1.25Gbps ,这意味着最大可能的基频为625MHz ;数据以差分模式进行传输,信号上升沿和下降沿300PS 左右,按照H. Johnson 定义的转折频率(Knee Frequency)〖1〗,主要频率成份达1.17GHz ,因此一种子板-背板-子板的系统级信号完整性仿真,及由此确定一种优化的背板PCB 参数成为整个系统设计不可缺少的部分。

此外,系统主时钟分配网络也采用了差分传输模式,信号上升沿和下降沿350PS 左右,它提供了125MHz 的系统时钟,也作为仿真设计中重点考虑的关键网络。

尽管这样一种千兆位互连背板的设计还需考虑其它信号完整性因素,但限于篇幅,这里仅就上述两种关键网络的仿真分析进行描述。

本文首先讨论了仿真前模型的选择和提取及相关的设计考虑,然后基于布局前的系统级仿真确定了背板的PCB 层叠结构及布线参数,最后详细描述了系统设计完成后即布局后的仿真结果。

2 模型的提取:对千兆位数据和时钟分配网络,可用的差分结构是边沿耦合或宽边耦合的Stripline 和边沿耦合的Microstrip 结构。

经过仔细考虑和比较,我们在背板中采用了边沿耦合的Stripline 差分结构。

建立这种差分结构的传输线模型的方法目前主要是采用二维场方法求解。

做为比较,这里给出两种不同的二维场工具计算的结果。

在所采用的参数范围内,两种方法给出了非常近似的结果。

对边沿耦合的Stripline 结构,亦有计算差分特性阻抗的经验公式〖2〗,见公式(1),(2):Stripline Ohms e Z Z t h sDiff----⎪⎪⎭⎫ ⎝⎛-≈+-29.20374.012 (1)()()Ohms t w t h Er Z ⎪⎪⎭⎫⎝⎛++=8.067.024ln 600π (2)Z Diff 为差分特性阻抗,Z 0为单端特性阻抗,s 为差分线边沿距离,h 为差分线与参考平面的距离,t 为导线厚度,w 为线宽, Er 为绝缘介质的介电常数,见图1。

该经验公式可用于验证差分特性阻抗。

用于系统级仿真的传输线模型还包括子板上的传输线部分,它们包括边沿耦合的Stripline 和Microstrip 结构,对这些传输线模型的提取也都是采用场解法,并用经验公式进行了验证,这些公式请参考文献〖2〗。

另外子板上过孔两边的布线用两段传输线代替,为的是模拟过孔的效应。

这里仅给出优化后背板上边沿耦合的Stripline 差分结构的参数,参考图1:FR4绝缘材料, Er=4.5, W = 8 mil, S = 10 mil ,h1=15.5mil, h2=14.2mil, t = 1.377 mil由于工艺所限,差分线距离上下参考平面的距离略有不等, 铜层厚为标准的1oz 铜。

传输线的RLCG 参数由二维场工具Ampredictor 〖3〗提取,表1同时给出了内置有二维场工具的Hyperlynx 计算的结果。

Hyperlynx 在求解时不考虑损耗,因此有些参数无法计算。

系统阻抗的选取与所选用的串行数据收发器及背板接插件有关,最常见的有50Ω单端信号系统和100Ω差分信号系统。

本设计选取系统无负载阻抗55-60Ω,差分阻抗100Ω左右。

表1 背板差分传输结构的RLGC 参数,Reference Fre.=1.17GHz, FR4, Er=4.5, tg δ=0.021千兆位数据收发器为AMCC 的S2064〖4〗,交换结构为AMCC 的 S2061,其原始模型为IBIS 2.1格式,在仿真中采用的是经转换后的SPICE 行为级模型。

子板与背板互连的接插件选用的是AMP 的Z -PACK HM 2mm 125〖5〗针接插件,其模型选用5×4 上升时间400PS 的多行SPICE 模型。

仿真结果相对于以最远端的子板上的S2064驱动,S2016接收的差分信号。

对于时钟信号,驱动芯片模型和接收芯片模型均为差分PECL 的SY100E111〖7〗的SPICE 模型,信号方向是从时钟源到最远端的子板。

3 关键网络的仿真GND 图1 背板边沿耦合的Stripline 结构图2, 数据,驱动端信号波形图3, 数据,接收端信号波形图4, 数据,驱动端和接收端差分信号波形图5, 数据,地噪声0.00E+005.00E-09 1.00E-08VoltsSecs图6, 时钟,驱动端信号波形图9, 时钟,地噪声25Gbps串行数据网络含二组共16个通道,对此网络的仿真选取了最不利布线情况下的数据通道,即该通道在背板上布线最长,且在子板上有一对过孔,同时在此过孔两边信号分别以Microstrip和Stripline两种不同结构传输。

仿真中没有考虑差分对之间的串扰,因在布局前的仿真中已考虑了差分对的间距以及接插件上信号与参考地比例使得串扰的影响可忽略。

SPICE仿真的结果示于图2-7。

对数据通道,在S2064发送端用分段线性化方法模拟了数据0BEH经8B-10B编码后的一部分码型1110101011,另有其平衡码型未给出。

该数据通道的布线总长度在6英寸左右,这也是所有数据通道中最长的。

从图3可看出,存在明显的噪声使单端信号发生畸变,但此噪声很大程度上被差分模式所抑制,因此它是共模的。

而对照图5的地反弹噪声,可看出无论其幅度(0.2V左右)或是频率均与图3中波形的噪声吻合,因此地噪声造成了单端波形的畸变,而这种地噪声是共模的,它是由驱动器S2064的信号电平切换引起地回路中的电压降造成的。

由于这种共模噪声可被差分传输模式抑制,因此这正是对千兆位传输采用差分结构的必要性所在。

此外,对不同阻抗匹配情况下信号波形的仿真指出,10%的传输线阻抗不均匀不会造成严重的波形畸变,当然这种不均匀不应过长。

最后,尽管传输长度只有6英寸左右,仍能看出明显的信号幅度的衰减,如图4,发送端差分信号的摆幅达2.07V,而接收端差分信号的摆幅衰减至1.4V左右,同时信号的边沿亦有损失。

理论上的分析指出,在此频率下,交流损耗占有相当比例,请参阅文献〖6〗。

对125MHz时钟分配网络的仿真也是选取布线最长的通道进行的。

可看出,由于信号频率较低,信号完整性较好。

地噪声表现为很高频率的电平抖动,但幅度小得多,同样当信号电平切换时噪声加强并随后开始衰减,直至再次被信号电平的切换加强。

信号的衰减依然明显,见图8,峰值和上升沿都有损失。

4结论对千兆位数据的传输,采用差分模式是必要的,单端信号和差分信号的完整性差别较大,并主要由地噪声引起;信号的直流和交流损耗应予以考虑。

对125 MHz时钟分配网络,仅从本文所述条件下仿真的结果来看,即便使用单端的传输模式也是可行的;地噪声主要为高频成份,因此,仔细的高频去耦是必要的。

事实上,由于目前的仿真和分析手段的限制,某些影响信号完整性的因素难以计及,如返回电流的跳层,过孔效应的准确描述等,实际的信号完整性可能略差。

因此,设计时应包括所有可能因素的考虑和权衡。

参考文献:1)Howard W. Johnson, M. Graham “High-Speed Digital Design, A Handbook of Black Magic”,Prentice Hall PTR, Englewood Cliffs, New Jersey ;2)“Transmission Line RAPIDESIGNER Operation and Applications Guide”, AN-905, NationalSemiconductor Corporation;3)“A MPredictor Signal Integrity Analyzer, Version 3.0, Application Guide”, AMP4)S2064 Data Sheet, AMCC, Feb 2,1999 / Revision C;5)“AMP Z-PACK TM2mm HM HARD METRIC CONNECTOR SYSTEM”, AMP, Catalog65911, Revised 9/97;6)Edward P. Sayre et al., “OC-48/2.5 Gbps Interconnect engineering Design Rules”,digitalCommunication system Design Conference, 1999;7)Sy100E111 Data Sheet, 1997 Synergy Product Data Book, SYNERGY SEMICONDUCTOR.Simulation Study for a High Speed Serial Bus on a BackplaneShengli Liu Yanfang Wang Guobao Shen(Univ. Of Science and Technology of China, Department of Modern Physics, Hefei 230026) Abstract This paper discribed the simulation studies for the signal integirity of a high speedserial bus on a backplane. Two critical nets, 1.25Gbps differential transmission channel and 125MHz system clock distribution network were given detailed analysis. The simulation results and the analysis for the reasons of waveform distortions were also present.Key Words Signal Integrity Differential Transmission Simulation Backplane。