数电课件ch_03_st

合集下载

数电--第02讲

uo比ui幅度放大且相位相反

电工电子技术

30

实现放大的条件

1、晶体管必须偏置在放大区。发射结正偏,集 电结反偏。

2、正确设置静态工作点,使整个波形处于放大 区。

3、输入回路将变化的电压转化成变化的基极电 流。

4、输出回路将变化的集电极电流转化成变化的 集电极电压,经电容滤波只输出交流信号。

2019/11/30

37

2.3.3 动态分析

1、 三极管的微变等效电路

首先考察输入回路 iB

iB uBE uBE

当信号很小时,将输入 特性在小范围内近似线

性。

rbe

uBE iB

ube ib

对输入的小交流信号 而言,三极管BE间 等效于电阻rbe。

2019/11/30

电工电子技术

38

ib b ube

对输入的小交流信号 而言,三极管BE间 等效于电阻rbe。

电工电子技术

25

例:用估算法计算静态工作点。 已知:EC=12V,RC=4K,RB=300K ,

=37.5。

解: UBE 0.7V

IBE C120.0m 4 A 4 0 A R B 300

ICIB3.5 70.0 41.5mA

U C U E C I C C R C 1 1 . 5 2 4 6 V

2019/11/30

电工电子技术

14

共射放大电路

集电极电阻,将

+EC 变化的电流转变

为变化的电压。

C1

RC

C2

T

RB

RL

EB

2019/11/30

电工电子技术

15

共射放大电路组成

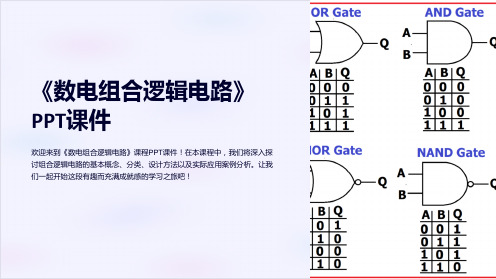

《数电组合逻辑电路》课件

2 设计和分析组合逻辑电路的方法

学习使用真值表、卡诺图和逻辑代数等工具进行组合逻辑电路的设计和分析。

3 应用案例的实际运用

通过实例,了解组合逻辑电路在数字系统和计算机中的应用。

课程大纲

第一章

组合逻辑电路概述

第三章

组合逻辑电路的简化与优化器

组合逻辑电路的基本概念

应用案例分析

在本节中,我们将通过精选的实际应用案例分析,展示组合逻辑电路在数字系统和计算机中的广泛应用。 这些案例将帮助您理解组合逻辑电路的实际应用价值和意义。

常见的组合逻辑电路元器件

组合逻辑电路的元器件有很多种,其中包括逻辑门、触发器、多路选择器等。在本节中,您将熟悉这些 常见的元器件以及它们在组合逻辑电路中的作用。

组合逻辑电路的设计方法

设计一个高效且可靠的组合逻辑电路需要一定的方法和技巧。在本节中,我们将探讨使用真值表、卡诺 图和逻辑代数等工具来进行组合逻辑电路的设计与优化。

组合逻辑电路由多个逻辑门电路组合而成,其输出仅取决于输入的当前状态。 在本节中,您将了解组合逻辑电路的基本概念,如逻辑运算、布尔代数、真 值表等。

组合逻辑电路的分类

根据功能和结构的不同,组合逻辑电路可以被分为多个子类。常见的分类包括编码器、解码器、多路选 择器、加法器等。通过本节,您将深入了解不同类型的组合逻辑电路及其应用。

《数电组合逻辑电路》 PPT课件

欢迎来到《数电组合逻辑电路》课程PPT课件!在本课程中,我们将深入探 讨组合逻辑电路的基本概念、分类、设计方法以及实际应用案例分析。让我 们一起开始这段有趣而充满成就感的学习之旅吧!

课程目标

通过本课程,您将学习到:

1 组合逻辑电路的基本原理和概念

掌握组合逻辑电路中的AND、OR、NOT等基本门电路的工作原理和特性。

学习使用真值表、卡诺图和逻辑代数等工具进行组合逻辑电路的设计和分析。

3 应用案例的实际运用

通过实例,了解组合逻辑电路在数字系统和计算机中的应用。

课程大纲

第一章

组合逻辑电路概述

第三章

组合逻辑电路的简化与优化器

组合逻辑电路的基本概念

应用案例分析

在本节中,我们将通过精选的实际应用案例分析,展示组合逻辑电路在数字系统和计算机中的广泛应用。 这些案例将帮助您理解组合逻辑电路的实际应用价值和意义。

常见的组合逻辑电路元器件

组合逻辑电路的元器件有很多种,其中包括逻辑门、触发器、多路选择器等。在本节中,您将熟悉这些 常见的元器件以及它们在组合逻辑电路中的作用。

组合逻辑电路的设计方法

设计一个高效且可靠的组合逻辑电路需要一定的方法和技巧。在本节中,我们将探讨使用真值表、卡诺 图和逻辑代数等工具来进行组合逻辑电路的设计与优化。

组合逻辑电路由多个逻辑门电路组合而成,其输出仅取决于输入的当前状态。 在本节中,您将了解组合逻辑电路的基本概念,如逻辑运算、布尔代数、真 值表等。

组合逻辑电路的分类

根据功能和结构的不同,组合逻辑电路可以被分为多个子类。常见的分类包括编码器、解码器、多路选 择器、加法器等。通过本节,您将深入了解不同类型的组合逻辑电路及其应用。

《数电组合逻辑电路》 PPT课件

欢迎来到《数电组合逻辑电路》课程PPT课件!在本课程中,我们将深入探 讨组合逻辑电路的基本概念、分类、设计方法以及实际应用案例分析。让我 们一起开始这段有趣而充满成就感的学习之旅吧!

课程目标

通过本课程,您将学习到:

1 组合逻辑电路的基本原理和概念

掌握组合逻辑电路中的AND、OR、NOT等基本门电路的工作原理和特性。

《数字电子技术基础》教学课件第3章 组合逻辑电路

&

A

&

&Y

B

&

解 :1 ) 、根据逻辑图写输出逻辑表达式并化简

Y = AB •A • AB• B = AB • A + AB • B

= AA + B+ BA + B = AB + AB

2)、根据逻辑表达式列真值表

AB

Y

3)、由真值表分析逻辑功能

00

0

01

1

当AB相同时,输出为0

10

1

当AB相异时,输出为1 异或功能。 1 1

常用3线—8线译码器有74LS138

74LS138

逻辑符号(输出0有效):

S1 S2 S3

A2 A1 A0

它能将三位二进制数的每个代码分别译成低电平。 当控制端S1S2S3=100 时,译码器处工作状态, 译码器禁止时,所有输出端都输出无效电平(高电平)。

3、综合 1)同理,四位二进制译码器为4线—16线译码器

Y1 = A1 A0 = m1

Y2 = A1 A0 = m2

Y3 = A1 A0 = m3

5)常用集成2线—4线译码器

74LS139: 双2线—4线译码器

Y13Y12Y11Y10 Y23Y22Y21Y20 74LS139

S1 A11 A10 S2 A21 A20

2、三位二进制译码器

三位二进制译码器即3线—8线译码器, Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0

(3)化简。

得最简与—或表达式: L = AB + BC + AC (4)画出逻辑图。

如果,要求用与非门实现该逻辑电路, 就应将表达式转换成与非—与非表达式:

数字电路课件第3章

V CC

vO 截止

放大

饱和

A

Rb

Rc L

T

O V1

逻辑 0

V2

vI

逻辑 1

三极管反相电路

iC

VCC Rc

反相器传输特性

1

A

L= A

VCC vCE

23

非逻辑符号

3.3.3 非门电路 ─ 三极管反相器

当输入为逻辑0时:

V CC

非逻辑真值表

Rc

0

A

Rb

T

vcc L

1

非逻辑真值表

输入A

0

输出L

1

24

3.3.3 非门电路 ─ 三极管反相器

17

VCC+(5V)

D1 A

D2 B

D3 C

R 3kW

L

二极管与门电路

A

&

B

L=A· B· C

C

与逻辑符号

3.3.1 二极管与门电路

若输入端中有任意一个 为0V,另两个为+5V

VCC+(5V)

0V D1

A

5V D2

B

5V D3

C

R 3kW

0v L

18 输入与输出电压关系

输

入

输出

VA 0 0 0 0 +5 V +5 V +5 V +5 V

11

1. BJT的开关作用

2. BJT的开关时间

3.2 BJT的开关特性

12

1. BJT的开关作用

IBS=VCC/Rc ICS= VCC/Rc CE=VCES≈0.2V

+-VVBB11 RRbb

第2章1数电完整。PPT课件

第二章 门电路

数字电路中,门电路是最基本的逻辑元件。 “门”:即一种开关,在一定条件下它允许信 号 通过,条件不满足,信号就通不过。 即:门电路的输入信号与输出信号之间有一定 基的本逻逻辑辑关门系电。路:故“门与电”路门又、称“为或逻”辑门门、电“路非” 门。 二值逻辑:逻辑0、逻辑1。0的“非”即1。

1 00 1 11

5. 逻辑符号

A B

&

Y

7

2.2 简单的与、或、非门电路

2.二极管或门

1)电路组成(以二输入为例)

2)工作原理

Ua Ub 00 0 3v 3v 0 3v 3v

Da Db

截止 截止 截止 导通 导通 截止 导通 导通

UY

0 2.3v 2.3v 2.3v

4)输出函数式 Y=A+B

5)逻辑符号

三. MOS管开关等效电路(理想情况下) 1、NM OS 管开关等效电路

当UGS≥2v时,TN导通: 当UGS<2v时,TN 截止

2、PMOS管开关等效电路。

当UGS≤-2v时,TP导通: 当UGS>-2v时T, P截止:(等效开关图同上)

§2.2 简单的与、或、非门电路

1. 二极管与门

+VCC

1.电路组成(以二输入为例) A

在输入高平电压上的最大噪

声(或干扰)电压VNH。

VNHVILVON

表征门的 抗干扰能力

3)扇出系数NO

与非门能带同类门的最大个数。表示负载能力。

A B

≥1

Y

3.真值表

A BY 0 00 0 11 1 01 1 11

8

2.2 三极管非门

2.工作原理

1.电原理图

数字电路中,门电路是最基本的逻辑元件。 “门”:即一种开关,在一定条件下它允许信 号 通过,条件不满足,信号就通不过。 即:门电路的输入信号与输出信号之间有一定 基的本逻逻辑辑关门系电。路:故“门与电”路门又、称“为或逻”辑门门、电“路非” 门。 二值逻辑:逻辑0、逻辑1。0的“非”即1。

1 00 1 11

5. 逻辑符号

A B

&

Y

7

2.2 简单的与、或、非门电路

2.二极管或门

1)电路组成(以二输入为例)

2)工作原理

Ua Ub 00 0 3v 3v 0 3v 3v

Da Db

截止 截止 截止 导通 导通 截止 导通 导通

UY

0 2.3v 2.3v 2.3v

4)输出函数式 Y=A+B

5)逻辑符号

三. MOS管开关等效电路(理想情况下) 1、NM OS 管开关等效电路

当UGS≥2v时,TN导通: 当UGS<2v时,TN 截止

2、PMOS管开关等效电路。

当UGS≤-2v时,TP导通: 当UGS>-2v时T, P截止:(等效开关图同上)

§2.2 简单的与、或、非门电路

1. 二极管与门

+VCC

1.电路组成(以二输入为例) A

在输入高平电压上的最大噪

声(或干扰)电压VNH。

VNHVILVON

表征门的 抗干扰能力

3)扇出系数NO

与非门能带同类门的最大个数。表示负载能力。

A B

≥1

Y

3.真值表

A BY 0 00 0 11 1 01 1 11

8

2.2 三极管非门

2.工作原理

1.电原理图

《数字电路技术基础》课件

逻辑函数的化简

总结词

逻辑函数的化简是数字电路设计中重要的一 步,它能够减少电路的复杂性和成本。

详细描述

逻辑函数的化简是指将一个复杂的逻辑函数 表达式简化为更简单或更紧凑的形式。通过 化简,可以减少所需的逻辑门数量,降低电 路的功耗和延迟,提高电路的性能和可靠性 。常用的化简方法包括代数法、卡诺图法和 布尔代数法等。

CHAPTER 06

数字电路的实践应用

数字钟的设计与实现

数字钟简介

数字钟的组成

数字钟是一种利用数字电路技术实现时间 显示的电子设备,通常由石英晶体振荡器 提供稳定的时钟信号。

数字钟一般由秒、分、时计数器、译码显 示电路以及校时电路等部分组成。

数字钟的设计步骤

数字钟的实现方式

首先确定设计方案,然后选择合适的芯片 和元件,接着设计电路原理图,最后进行 调试和测试。

自顶向下设计和自底向上设计等。

CHAPTER 04

组合逻辑电路

组合逻辑电路的分析与设计

组合逻辑电路的分析

通过真值表、逻辑表达式、逻辑图等 工具,对给定的组合逻辑电路进行分 析,了解其逻辑功能。

组合逻辑电路的设计

根据实际需求,利用基本逻辑门电路 (如AND、OR、NOT等)设计组合 逻辑电路。

编码器与译码器

要点一

编码器

将输入的多个信号转换为二进制代码,常用于数据传输和 存储。

要点二

译码器

将输入的二进制代码转换为多个输出信号,常用于地址解 码和数据选择。

加法器与比较器

加法器

实现二进制数的加法运算,输出结果为相加后的和。

比较器

比较两个二进制数的大小,输出结果为比较结果(大于 、小于或等于)。

多路选择器与多路分配器

数字电子技术基础第3章数字电子技术基础课件-PPT精品文档

(3-11)

3.1.2 组合电路的基本设计方法

组合逻辑功辑电路的设计是根据给定的实际逻辑问题, 求出实现其逻辑功能的逻辑电路。 一、设计方法 根据要求,设计出适合需要的组合逻辑电路应该遵循 的基本步骤,可以大致归纳如下: 1、进行逻辑抽象 ①分析设计要求,确定输入、输出信号及它们之间的 因果关系。 ②设定变量,即用英文字母表示有关输入、输出信号, 表示输入信号者称为输入变量,有时也简称为变量,表 示输出信号者称为输出变量,有时也称为输出函数或简 称函数。

数字电子技术基础

(3-1)

第3章 组合逻辑电路

(3-2)

第3章

3.1 3.2 3.3 3.4 3.5 3.6 3.7

组合逻辑电路

概述 组合电路的基本分析方法和设计方法 加法器和数值比较器 编码器和译码器 数据选择器和分配器 用中规模集成电路实现组合逻辑函数 只读存储器 组合电路中的竞争冒险

(3-3)

(Байду номын сангаас-5)

3.1 组合电路的基本分析方法和设计方法

3.1.1 组合电路的基本分析方法 所谓组合逻辑电路的分析,就是根据给定的逻辑电路 图,求出电路的逻辑功能。 给定组合逻辑电路 一、分析方法 ①根据给定的逻辑图写 出输出函数的逻辑表达式。 写输出逻辑表达式 ②化简逻辑表达式,求 出输出函数的最简与或表 达式。 化简 分析其功能 ③列出输出函数的真值 表。 分析其功能 ④描述电路的逻辑功能。 列出真值表

(3-6)

二、分析举例:

A

& & & & Y

B

1:组合逻辑电路如图, 试分析其逻辑功能。

解 :⑴ 、根据逻辑图写输出逻辑表达式并化简

Y AB A AB B AB A AB B AB ( A B ) ( A B )( A B ) A B A B

3.1.2 组合电路的基本设计方法

组合逻辑功辑电路的设计是根据给定的实际逻辑问题, 求出实现其逻辑功能的逻辑电路。 一、设计方法 根据要求,设计出适合需要的组合逻辑电路应该遵循 的基本步骤,可以大致归纳如下: 1、进行逻辑抽象 ①分析设计要求,确定输入、输出信号及它们之间的 因果关系。 ②设定变量,即用英文字母表示有关输入、输出信号, 表示输入信号者称为输入变量,有时也简称为变量,表 示输出信号者称为输出变量,有时也称为输出函数或简 称函数。

数字电子技术基础

(3-1)

第3章 组合逻辑电路

(3-2)

第3章

3.1 3.2 3.3 3.4 3.5 3.6 3.7

组合逻辑电路

概述 组合电路的基本分析方法和设计方法 加法器和数值比较器 编码器和译码器 数据选择器和分配器 用中规模集成电路实现组合逻辑函数 只读存储器 组合电路中的竞争冒险

(3-3)

(Байду номын сангаас-5)

3.1 组合电路的基本分析方法和设计方法

3.1.1 组合电路的基本分析方法 所谓组合逻辑电路的分析,就是根据给定的逻辑电路 图,求出电路的逻辑功能。 给定组合逻辑电路 一、分析方法 ①根据给定的逻辑图写 出输出函数的逻辑表达式。 写输出逻辑表达式 ②化简逻辑表达式,求 出输出函数的最简与或表 达式。 化简 分析其功能 ③列出输出函数的真值 表。 分析其功能 ④描述电路的逻辑功能。 列出真值表

(3-6)

二、分析举例:

A

& & & & Y

B

1:组合逻辑电路如图, 试分析其逻辑功能。

解 :⑴ 、根据逻辑图写输出逻辑表达式并化简

Y AB A AB B AB A AB B AB ( A B ) ( A B )( A B ) A B A B

数字电路全部PPT课件

(10、11、12、13、14、15)

. 位置表示法:(N)16 = (Hn-1Hn-2...H0 H-1H-2..) 16

按权展开式:

(N)2=Hn-116n-1+Hn-216n-2+...+H0160+H-116-1+H-216-2+...

(C07.A4)16= (C07.A4)H= C07.A4H= 12×162+0×161+7×160+10×16-1+4×16-2

小数部分

二、常用计数体制

1、十进制(Decimal)

. (N)10= (Dn-1Dn-2...D0 D-1D-2.. ) 10

(271.59)10= 2×102十7×101十1×100十5×10-1十9×10-2

2020年10月2日

5

2、二进制(Binary)

基数 : 2

位权:2i

数符Bi: 0、1 (可以用低、高电平表示)

正数的三种代码相同,都是数值码最高位加符号位 “0”。

即X≥0时,真值与码值相等,且:X=[X]原= [X]反= [X]补例: 4位二进制数X=1101和Y=0.1101

[X]原= [X]反= [X]补= 01101, [Y]原= [Y]反= [Y]补= 0.1101

2020年10月2日

20

三、二——十进制编码(Binary Code Decimal码)

2020年10月2日

12

二、十六进制与二进制转换

1、十六进制转换为二进制 根据数值关系表用四位二进制数码逐位替代各位

十六进制数码。 (52.4)16=(01010010.0100)2 =(1010010.01)2 2、二进制转换为十六进制 将二进制数从小数点起,分别按整数部分和小数

数字电子技术基础全套课件

= 1×25 + l×24 + 0×23 + 1×22 + 0×21 + l×20 + 1×2-1 + 0×2-2 + 1×2-3 = 32 + 16 + 0 + 4 + 0 + 1 + 0.5 + 0 + 0.125 = (53.625) D

【例1-2】 将十六进制数(4E5.8) H转换为十进制数。 解:(4E5.8) H = 4×(16)2 + E×(16)1 + 5×(16)0 + 8×(16)-1

0

时间

在时间上和数值上是连续变化的电信号

分析方法 逻辑代数

图解法,等效电路,分析计算

1.1.3 数字电路的特点

(1) 稳定性好,抗干扰能力强。 (2) 容易设计,并便于构成大规模集成电路。 (3) 信息的处理能力强。 (4) 精度高。 (5) 精度容易保持。 (6) 便于存储。 (7) 数字电路设计的可编程性。 (8) 功耗小。

八进制转二进制规则是,将每位八进制数码分别用三位二进制 数表示,并在这个0和1构成的序列去掉无用的前导0即得。

【例1-7】将八进制数(5163)O转换成二进制数。

解:将每位八进制数码分别用三位二进制数表示,转换过程 如下

(5163)O = (101 001 110 011)2 = (101001110011)2

解:

整数部分

16 | 427 余数 16 | 26 ………11 低位 16 | 1 ……… 10 (反序)

0 ……… 1 高位

小数部分

0.34357 整数

× 16

5.50000 ……… 5 高位

0.50000

【例1-2】 将十六进制数(4E5.8) H转换为十进制数。 解:(4E5.8) H = 4×(16)2 + E×(16)1 + 5×(16)0 + 8×(16)-1

0

时间

在时间上和数值上是连续变化的电信号

分析方法 逻辑代数

图解法,等效电路,分析计算

1.1.3 数字电路的特点

(1) 稳定性好,抗干扰能力强。 (2) 容易设计,并便于构成大规模集成电路。 (3) 信息的处理能力强。 (4) 精度高。 (5) 精度容易保持。 (6) 便于存储。 (7) 数字电路设计的可编程性。 (8) 功耗小。

八进制转二进制规则是,将每位八进制数码分别用三位二进制 数表示,并在这个0和1构成的序列去掉无用的前导0即得。

【例1-7】将八进制数(5163)O转换成二进制数。

解:将每位八进制数码分别用三位二进制数表示,转换过程 如下

(5163)O = (101 001 110 011)2 = (101001110011)2

解:

整数部分

16 | 427 余数 16 | 26 ………11 低位 16 | 1 ……… 10 (反序)

0 ……… 1 高位

小数部分

0.34357 整数

× 16

5.50000 ……… 5 高位

0.50000

数电实用知识课件

数字钟由秒计数器、分计数器、时计数器、日计数器和闹钟等组成。

数字钟的工作原理

数字钟的工作原理是通过振荡器产生频率为1MHz的信号,该信号被分频后,再被用作秒、 分、时、日等的计数脉冲,各计数器均采用60进制计数器,计数到60后进位到上一级计 数器。

数字钟的设计步骤

设计步骤包括选定电路元件、设计电路图、制作电路板等。

交通灯控制系统的工作原理 交通灯控制系统的工作原理是通过传感器检测交通流量, 控制器根据检测结果控制显示设备的显示,以实现交通流 量的控制。

交通灯控制系统的设计步骤 设计步骤包括确定控制方案、设计电路图、制作电路板等。

06

数电实用技巧与经验分享

如何优化数电设计

01

02

03

04

确定设计目标

明确数字电路的设计目标,以 便在设计和实现过程中保持目

数电利用数字信号传递信息,具有精度高、稳定性好、抗干 扰能力强等优点,在通信、计算机、智能制造等领域得到广 泛应用。

数电的基本单元

01

02

03

逻辑门电路

逻辑门电路是构成数字电 路的基本单元,包括与门、 或门、非门等基本逻辑门。

触发器

触发器是构成时序逻辑电 路的基本单元,包括JK触 发器、D触发器等。

详细描述

介绍基本逻辑门(AND、OR、NOT) 的功能和特性

触发器实验

详细描述

演示如何使用D触发 器构建简单的时序 电路

总结词:掌握触发 器的功能和工作原 理

介绍D触发器的功能 和工作原理

分析实验电路中的 状态转换和输出结 果

寄存器实验

详细描述

演示如何使用寄存器构建简单的 计数器电路

总结词:了解寄存器的基本概念 和工作原理

数字钟的工作原理

数字钟的工作原理是通过振荡器产生频率为1MHz的信号,该信号被分频后,再被用作秒、 分、时、日等的计数脉冲,各计数器均采用60进制计数器,计数到60后进位到上一级计 数器。

数字钟的设计步骤

设计步骤包括选定电路元件、设计电路图、制作电路板等。

交通灯控制系统的工作原理 交通灯控制系统的工作原理是通过传感器检测交通流量, 控制器根据检测结果控制显示设备的显示,以实现交通流 量的控制。

交通灯控制系统的设计步骤 设计步骤包括确定控制方案、设计电路图、制作电路板等。

06

数电实用技巧与经验分享

如何优化数电设计

01

02

03

04

确定设计目标

明确数字电路的设计目标,以 便在设计和实现过程中保持目

数电利用数字信号传递信息,具有精度高、稳定性好、抗干 扰能力强等优点,在通信、计算机、智能制造等领域得到广 泛应用。

数电的基本单元

01

02

03

逻辑门电路

逻辑门电路是构成数字电 路的基本单元,包括与门、 或门、非门等基本逻辑门。

触发器

触发器是构成时序逻辑电 路的基本单元,包括JK触 发器、D触发器等。

详细描述

介绍基本逻辑门(AND、OR、NOT) 的功能和特性

触发器实验

详细描述

演示如何使用D触发 器构建简单的时序 电路

总结词:掌握触发 器的功能和工作原 理

介绍D触发器的功能 和工作原理

分析实验电路中的 状态转换和输出结 果

寄存器实验

详细描述

演示如何使用寄存器构建简单的 计数器电路

总结词:了解寄存器的基本概念 和工作原理

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Digital Fundamentals

Tenth Edition

Floyd

Chapter 3

Floyd, Digital Fundamentals, 10th ed

© 2008 Saddle Education © 2009 Pearson Education, UpperPearson River, NJ 07458. All Rights Reserved

The Inverter

Summary

A

X

The inverter performs the Boolean NOT operation. When the input is LOW, the output is HIGH; when the input is HIGH, the output is LOW. Input Output

A B X

A B A B

X

≥1

X

0 0 1 1

0 1 0 1

0 1 1 1

The OR operation is shown with a plus sign (+) between the variables. Thus, the OR operation is written as X = A + B.

A B X

0 0 1 1

0 1 0 1

1 1 1 0

The NAND operation is shown with a dot between the variables and an overbar covering them. Thus, the NAND operation is written as X = A .B (Alternatively, X = AB.)

The OR Gate

Summary

The OR gate produces a HIGH output if any input is HIGH; if all inputs are LOW, the output is LOW. For a 2-input gate, the Inputs Output truth table is

A B A B

X

≥1

X

The OR operation can be used in computer programming to set certain bits of a binary number to 1.

Floyd, Digital Fundamentals, 10th ed

ห้องสมุดไป่ตู้

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The NAND Gate

Summary

A Multisim circuit is shown. XWG1 is a word generator set in the count up mode. A four-channel oscilloscope monitors the inputs and output. What output signal do you expect to see?

1 0 0 0 1 1 0 1

0

1

1

1 0 0 1’s complement

1

0

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The AND Gate

Summary

A B A

&

X

X

The AND gate produces a HIGH output when B all inputs are HIGH; otherwise, the output is Inputs LOW. For a 2-input gate, the truth table is

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The OR Gate

Example waveforms: A B X

Summary

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The Inverter

Example waveforms: A X

Summary

A

X

A group of inverters can be used to form the 1’s complement of a binary number: Binary number

Summary

A B A B

&

X

X

The AND operation is used in computer programming as a selective mask. If you want to retain certain bits of a binary number but reset the other bits to 0, you could set a mask with 1’s in the position of the retained bits.

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Summary

If the binary number 10100011 is ANDed with the mask 00001111, what is the result? 00000011

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The AND Gate

Summary

A Multisim circuit is shown. XWG1 is a word generator set in the count down mode. XLA1 is a logic analyzer with the output of the AND gate connected to first (upper) line of the analyzer. What signal do you expect to on this line?

A X

LOW (0) HIGH (1) HIGH (1) LOW(0)

The NOT operation (complement) is shown with an overbar. Thus, the Boolean expression for an inverter is X = A.

Floyd, Digital Fundamentals, 10th ed

The output (line 1) will be HIGH only when all of the inputs are HIGH.

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The NAND Gate

Example waveforms: A B X

Summary

A B

Output

X

The AND operation is usually shown with a dot between the variables but it may be implied (no dot). Thus, the AND operation is written as X = A .B or X = AB.

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The NAND Gate

Summary

A B A B

&

X

X

The NAND gate produces a LOW output when all inputs are HIGH; otherwise, the output is HIGH. For a 2-input gate, the truth table is Inputs Output

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Tenth Edition

Floyd

Chapter 3

Floyd, Digital Fundamentals, 10th ed

© 2008 Saddle Education © 2009 Pearson Education, UpperPearson River, NJ 07458. All Rights Reserved

The Inverter

Summary

A

X

The inverter performs the Boolean NOT operation. When the input is LOW, the output is HIGH; when the input is HIGH, the output is LOW. Input Output

A B X

A B A B

X

≥1

X

0 0 1 1

0 1 0 1

0 1 1 1

The OR operation is shown with a plus sign (+) between the variables. Thus, the OR operation is written as X = A + B.

A B X

0 0 1 1

0 1 0 1

1 1 1 0

The NAND operation is shown with a dot between the variables and an overbar covering them. Thus, the NAND operation is written as X = A .B (Alternatively, X = AB.)

The OR Gate

Summary

The OR gate produces a HIGH output if any input is HIGH; if all inputs are LOW, the output is LOW. For a 2-input gate, the Inputs Output truth table is

A B A B

X

≥1

X

The OR operation can be used in computer programming to set certain bits of a binary number to 1.

Floyd, Digital Fundamentals, 10th ed

ห้องสมุดไป่ตู้

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The NAND Gate

Summary

A Multisim circuit is shown. XWG1 is a word generator set in the count up mode. A four-channel oscilloscope monitors the inputs and output. What output signal do you expect to see?

1 0 0 0 1 1 0 1

0

1

1

1 0 0 1’s complement

1

0

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The AND Gate

Summary

A B A

&

X

X

The AND gate produces a HIGH output when B all inputs are HIGH; otherwise, the output is Inputs LOW. For a 2-input gate, the truth table is

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The OR Gate

Example waveforms: A B X

Summary

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The Inverter

Example waveforms: A X

Summary

A

X

A group of inverters can be used to form the 1’s complement of a binary number: Binary number

Summary

A B A B

&

X

X

The AND operation is used in computer programming as a selective mask. If you want to retain certain bits of a binary number but reset the other bits to 0, you could set a mask with 1’s in the position of the retained bits.

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Summary

If the binary number 10100011 is ANDed with the mask 00001111, what is the result? 00000011

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The AND Gate

Summary

A Multisim circuit is shown. XWG1 is a word generator set in the count down mode. XLA1 is a logic analyzer with the output of the AND gate connected to first (upper) line of the analyzer. What signal do you expect to on this line?

A X

LOW (0) HIGH (1) HIGH (1) LOW(0)

The NOT operation (complement) is shown with an overbar. Thus, the Boolean expression for an inverter is X = A.

Floyd, Digital Fundamentals, 10th ed

The output (line 1) will be HIGH only when all of the inputs are HIGH.

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The NAND Gate

Example waveforms: A B X

Summary

A B

Output

X

The AND operation is usually shown with a dot between the variables but it may be implied (no dot). Thus, the AND operation is written as X = A .B or X = AB.

Floyd, Digital Fundamentals, 10th ed

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved

The NAND Gate

Summary

A B A B

&

X

X

The NAND gate produces a LOW output when all inputs are HIGH; otherwise, the output is HIGH. For a 2-input gate, the truth table is Inputs Output

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved