MPC8250处理器及其在宽带接入中的应用

MPC8280多通道HDLC控制器的应用

MPC8280多通道HDLC控制器的应用1 概述时分复用是当前同步通信系统中用以提高数据传输效率的常用方法。

例如第2代移动通信GSM系统,光同步传输网SDH等都是使用时分复用的例子。

在现代通信设备的研发中,常常会遇到高速背板通信、多协议接口、网络管理信令通道等需要同时处理多个同步通信接口数据的情况。

本文介绍了一种采用MPC8280处理器芯片内部的多通道通信控制单元,来处理多个同步通信接口数据的方法。

MPC8280是飞思卡尔公司PowerQUICC II产品线的较新成员。

它采用0.13 μm工艺制造。

内核、I/O的供电电压分别为1.5 V、3.3 V。

MPC8280相比该公司的MPC8260,制造工艺和工作频率均有所提升,但因为核心电压下降,功耗反而下降。

而且,MPC8280片内的DPRAM(双口静态存储器)容量增加了一倍,此外还增加了PCI 和USB。

MPC8280芯片由主内核、SIU、CPM等3个主要功能模块组成,。

MPC8280的处理器主内核称为G2_LE,它是一种PowerPC架构的多级流水线超标量处理器。

MPC8280内核运行频率为166~450 MHz。

SIU模块主要负责60x总线控制、PCI桥及时钟产生。

CPM模块负责处理通信事务,即处理SCC、SMC、FCC、MCC、USB、SPI、I2C等通信控制单元收发数据。

本文所述的多通道HDLC控制器即采用CPM下的MCC(多通道控制器)通信控制单元来实现。

MPC8280片内集成的静态存储器包括DPRAM、全局配置寄存器、SI RAM(串行接口路由表配置空间)。

其中,第1块32 KB的数据DPRAM空间被等分成16个bank(存储空间块)。

CPM 中的通信控制单元除了使用全局配置寄存器进行最基本的参数配置外,还须使用参数配置存储区块进一步配置。

一般CPM中每个通信控制单元都有2个参数配置存储区块,参数配置存储区块均定位在DPRAM中的指定地址。

MPC8250处理器及其在宽带接入中的应用

MPC8250处理器及其在宽带接入中的应用MPC8250处理器及其在宽带接入中的应用摘要:MPC8250是Motorola公司推出的高性能32位嵌入式微处理器MPC82XX系列中的一种,本文介绍MPC8250的结构与特点,并与MPC860的特点进行对比,在此基础之上分析MPC8250应用于宽带接入产品的优势所在。

最后提出一种充分利用MPC8250优点的接入路由器硬件设计方案。

关键词:嵌入式处理器 MPC8250 接入路由器1 MPC8250简介MPC8250是Motorla公司在嵌入式徽顺MPC860基础之上推出的MPC82XX系列微处理器中的一种。

MPC82XX系列保留了MPC860的嵌入式PowerPC内核和通信处理模块CPM并存的体系结构,同时进一步提高了工作频率、集成了更多的外围器件、提供了丰富的总线接口。

其中,MPC8250没有集成在一数据通信设备中不常使用、而且较为昂贵的ATM处理模块,进一步降低了成本。

MPC8250的内部结构基于PowerQUICC结构,主要由PowerPC内核、系统接口单元SIU、通信处理单元CPM构成。

它支持60x总线,其数据线为64位,地址线为32位;支持PCI/LOCAL总线,其数据线为32位,地址线为32位。

内核工作时钟最高300MHz,CPU工作时钟最高200MHz。

内部结构如图1所示。

①PowerPC内核:完成中央处理器的功能,执行高层程序偌,它与SIU和CPM通过独立的指令Cache和数据Cache通信,通过MMU对存储器进行管理。

②系统接口单元SIU:包括CPU的复位、中断控制器、时钟配置等功能。

内部包括60x总线控制器、PCI/LOCAL总线到60x总线的桥接器、存储器控制器、时钟控制器等。

MPC8250的存储控制器部分集成了SDRAM控制器,通过设置寄存器即可完成与SDRAM的接口配置,与MPC860配置UPM表的方式相比,极大地降低了开发的复杂度。

9.2 可编程串行接口8250

常用的可编程串行接口芯片有Intel的8250、8251, 常用的可编程串行接口芯片有Intel的8250、8251, 美国国家半导体公司的16550等 8250与16550完全 美国国家半导体公司的16550等。8250与16550完全 兼容。 兼容。

电子科技大学

微机系统原理及接口技术应用

异步串行数ቤተ መጻሕፍቲ ባይዱ发送格式

电子科技大学

微机系统原理及接口技术应用

(2)发送部分

1.CPU送来的并行数据存放在发送保持寄存器中 1.CPU送来的并行数据存放在发送保持寄存器中 2.数据经过发送移位寄存器进行并串转换 2.数据经过发送移位寄存器进行并串转换 3.按规定格式加上起始位、奇偶校验位和停止位,构成完整 3.按规定格式加上起始位 奇偶校验位和停止位, 按规定格式加上起始位、 的串行数据帧 4.数据由Sout发出 4.数据由Sout发出 数据由Sout 另外,当数据进入到发送移位寄存器后,发送保持寄存器 另外,当数据进入到发送移位寄存器后, 自动变空,以接收下一个待发送的数据。 自动变空,以接收下一个待发送的数据。

状态时,若允许Modem状态中断,就会产生一次中断 状态中断, 状态时,若允许Modem状态中断 接收线路信号检测输入, =0,表明Modem已 . RLSD :接收线路信号检测输入, RLSD =0,表明Modem已 收到数据载波,8250/16550应立即开始接收解调 收到数据载波,8250/16550应立即开始接收解调 后的数据

电子科技大学

微机系统原理及接口技术应用

同步通信: 同步通信: 1.通信开始后,发送设备连续发送字符, 1.通信开始后 发送设备连续发送字符, 通信开始后, 接收设备首先搜索同步字符, 接收设备首先搜索同步字符,在得到同 步字符后开始接收数据。 步字符后开始接收数据。 2. 传送过程中,发送设备和接收设备必须 传送过程中, 要保持完全同步,即使用同一个时钟。 要保持完全同步,即使用同一个时钟。

硬件8250介绍

0 数字信号

1

1

0

1

0

0

0

1

(a)调幅

按数字信号的 值改变载波信 号的幅度 按数字信号的 值改变载波信 号的频率 按数字信号的 值改变载波信 号的相位

(b)调频

(c)调相

7.4.2 串行通信接口标准

一、EIA RS-232C/CCITT V.24标准 • EIA RS—232C,1969年,适合于DTE和 DCE之间相互连接与通信的串行通信规程。 (1987年11月,经修改正式命名为RS— 232D) DTE-Data Terminal Equipment DCE-Data Communication Equipment。

CCITT 信号名

插 脚 号 1

机壳地

101

103 104

发送数据

2 3 接收数据

载波检测

105 终 4 106 5

请求发送

允许发送 Modem就绪

本 地 Modem

远 程 Modem

计 算 机

107 端 6

信号地 102

109 108 125 7 8 20 22 载波检测 终端就绪

电话线

பைடு நூலகம்

呼叫指示

7.4 串行通信及8250接口芯片

•通信概念 数据在单条1位宽的传输线上按时间先 后一位一位地传送;节省传输线(优点); 数据传输率较低(缺点)。 主要适用于长距离、低速率的通信中。 •常用物理标准(RS-232) •8250通信控制器

基本概念

1. 通信方式

– – – – 串行与并行 单工、半双工、全双工 异步通信的字符编码 同步与异步通信

• 例:SDLC/HDLC帧格式: • 假定数据长度为2048位, 通信效率为:2048/(2048+48)=97% 协议开销仅为3% • 一般公式:SDLC/HDLC协议开销=1.0- N/(N+48),其中N为发送数据的比特数。

基于MPC8250和嵌入式Linux的中断处理

对进封} 调‘ } I行装嬲 / l P 重 包 ’ 制 . _ 1 -

.

分配发送时隙

变 0 L l D

4递 l 码 织 l ,转目 s 交. L -换的 , 解 给包 传为I R P 编 1 一

图 1 R WI P C 20的 功 能 划 分 E N— P 8 5

宫 炜 ,王立平

( 安 电子科 技 大学 综合 业务 网国家 重点实验 室 ,陕西 西 安 7 0 7 ) 西 10 1

摘 要 : C 2 0采取 了基 于硬 件 的 中断 现 场 保 护 机 制 , MP 8 5 系统 中断 响 应 时 间 与 所 采 用操 作 系统 相 关

性 较 小 。对 MP 8 5 C 2 0中 断 资 源 的合 理 分 配 并 采取 合 适 的 Lnx中 断 处 理 策略 设 计 中 断 服 务 程 序 对 i u 提 高 系统 的性 能将 有 重要 的 意 义 。

和 FG P A的功 能划分 如 图 1 示 。 所

MP 85 中 f C 20 断孝 号 FG PA 射 频 前 端 ■ 判断用户合法} . S 生 } K 编码 交织 J l I _ Ia i

MP 8 5 C 2 0的 中断 资源 包括 如下 三类 :

a通信 处理 模块 ( P 的 中断 资 源 :C sS C , . C M) F C ,C s

维普资讯

第3 7卷

第 2期

航 空 计 算 技 术

Ae o a tc lCo r n u ia mpui g Te h q tn c niue

Vo . 7 No. 13 2 M a . 0o r2 7

20 0 7年 3月

基 于 MP 8 5 C 2 0和 嵌 入 式 Ln x的 中 断 处 理 iu

PowerPC处理器的发展历程

PowerPC处理器的发展历程作者:沈华汤彦飞李乔杨来源:《计算机光盘软件与应用》2013年第12期摘要:本文简述Freescale的PowerPC处理器的发展历程,按PowerPC处理器应用领域对处理器进行了进行分类和介绍。

关键词:嵌入式处理器;PowerPC;PowerQUICC;Power QorIQ中图分类号:TP752一般情况下的PowerPC,指的是使用PowerPC指令集的处理器。

PowerPC,最初的含义却不是Power,而是Performance Optimized With Enhanced RISC;PC指的是Performance Computing。

PowerPC系列是源自于POWER架构的设计,但进行了大量的改动。

例如,Power PC是open-endian设计,而POWER是大尾段设计;Power PC希望提供更强的浮点处理能力和多线程处理能力。

总的来说,这两种类型的CPU并没有太大的差别,Power PC保留了绝大部分POWER指令,许多应用只要重新编译,就可以分别在两个平台上运行。

随着PowerPC的发展,使用PowerPC构架的处理器已经形成了庞大的家族,在通信、工控、航天国防等要求高性能和高可靠性的领域得到广泛应用。

目前,主流的PowerPC处理器制造商有IBM、Freescale、AMCC、LSI等。

而在嵌入式领域Freescale的PowerPC占主导地位,尤其有E2V公司对扩展温度PowerPC的支持,广泛应用于航空国防领域。

1 Freescale的PowerPC系列Freescale公司是从Motorola公司分离出来的公司,但是把Motorola公司名下所有关于PowerPC处理器的业务都归属到Freescale公司,至此该公司发展迅速,尤其在网络设备市场取得了非常可观的成功。

目前Freescale公司已经调整其PowerPC产品策略,将其划分成3个主要市场:网络设备、汽车电子(MPC5xx系列)和工业控制。

基于PowerPC处理器MPC8250的嵌入式Linux系统开发

-179-1引言我们开发了某型飞机外场维护系统的一个网络终端通讯平台,其硬件核心采用Motorola 公司的嵌入式PowerPC 处理器MPC8250,软件方面采用嵌入式linux 作为操作系统,实现了飞机外场维护与飞机故障诊断系统的安全、快速通信。

这个系统平台具有体积小、功耗低、性能高等特点。

2MPC8250构架与系统硬件平台简介PowerPC 是Linux 较早开始支持的处理器之一。

PowerPC处理器芯片MPC8250基于PowerQUICC (Quad Integrated Com-munications Controller )II 结构,是面向高性能、低功耗、小体积的通信设备而开发的处理器[1]。

其内部集成了一个高性能嵌入式G2内核、一个灵活的系统集成单元SIU 和许多控制领域的常用外围通信组件(组成通信处理模块CPM ,Communica-tions Processor Module ),可用于许多方面,尤其是在通讯和网络系统方面。

G2内核频率在150-200MHz 之间,CPM 、PCI 最高频率为133MHz ,外部频率为66MHz ,可同时处理高达128个全双工时分复用逻辑通道。

根据目标系统的不同,系统硬件平台可以引出所需的MPC8250的外部通讯接口。

我们的系统提供了8M 的flash 用于存放内核镜像文件、文件系统、应用程序和备份数据,64M SDRAM 用作内存,521KB 的flash 用于存放启动代码,此外还有RS232串口、10/100M 以太网口以及JTAG 支持等。

3基于MPC8250的嵌入式linux 系统开发3.1编译环境的定制通常主机与目标板的CPU 都不相同,需要进行交叉编译。

能够进行交叉编译的工具很多,一般使用GNU C ,它包括gcc 、g++编译器,glibc 、newlib 等c 库,binutils 以及其他一系列开发工具。

不同的开发平台需要不同的交叉编译工具。

微型计算机原理与接口技术8250

232C接口采用EIA电平

高电平为+3V~+15V 低电平为-3V~-15V 实际常用±12V或±15V

相互转换

标准TTL电平

高电平:+2.4V~+5V 低电平:0V~0.4V

11.3 通用异步接收发送器8250

串行传输,需要并行到串行和串行到并行 的转换,并按照传输协议发送和接收每个 字符(或数据块) 这些工作可由软件实现,也可用硬件实现 通用异步接收发送器UART是串行异步通 信的接口电路芯片 IBM PC/XT机的UART芯片是INS 8250 后来使用NS16550

2. 时钟信号

时钟输入引脚XTAL1:8250的基准工作时钟 时钟输出引脚XTAL2:基准时钟信号的输出端 波特率输出引脚BAUDOUT*:基准时钟经8250 内部波特率发生器分频后产生发送时钟 接收时钟引脚RCLK:接收外部提供的接收时钟 信号;若采用发送时钟作为接收时钟,则只要将 RCLK引脚和BAUDOUT*引脚直接相连

全双工

站A 站B

半双工

站A

站B

单工

示例

站A

站B

4. 调制解调器

调制(Modulating)

把数字信号转换为电话线路传送的模拟信号 将电话线路的模拟信号转换为数字信号

解调(Demodulating)

调制解调器MODEM

具有调制和解调功能的器件合制在一个装置

示例

11.2 串行接口标准RS-232C

物理层1121rs232c的引脚定义绝大多数设备只使用其中9个信号所以就有了9针连接器次信道为辅助串行通道提供数据控制和通道但其传输速率比主信道要低得多其他跟主信道相同通常较少使用rs232c的引脚1串行数据的接收端rs232c的引脚2当数据终端设备准备好送出数据时就发出有效的rts信号用于通知数据通信设备准备接收数据当数据通信设备已准备好接收数据终端设备的传送数据时发出cts有效信号来响应rts信号rts和cts是数据终端设备与数据通信设备间一对用于数据发送的联络信号rs232c的引脚3通常当数据终端设备一加电该信号就有效表明数据终端设备准备就绪通常表示数据通信设备即数据装置已接通电源连到通信线路上并处在数据传输方式dtr和dsr也可用做数据终端设备与数据通信设备间的联络信号例如应答数据接收rs232c的引脚4当本地调制解调器接收到来自对方的载波信号时该引脚向数据终端设备提供有效信号当调制解调器接收到对方的拨号信号期间该引脚信号作为电话铃响的指示保持有效rs232c的引脚5起屏蔽保护作用的接地端一般应参照设备的使用规定连接到设备的外壳或大地控制数据终端接收串行数据的时钟信号1122rs232c的连接微机利用232c接口连接调制解调器用于实现通过电话线路的远距离通信微机利用232c接口直接连接进行短距离通信

基于MPC8560的吉比特以太网接口设计

基于MPC8560的吉比特以太网接口设计作者:厦门大学时斌随着网络技术的发展,网络通信控制器的应用已经越来越广泛。

集成PowerPC微处理器的MPC8560 PowerQUICC Ⅲ作为一个多用途、高性能的通信微处理器,具有非常灵活的一体化单元系统和外围通信控制器,能被广泛运用于通信和网络系统,是目前为电信和网络市场而设计的最先进的集成通信微处理器之一。

它集成了丰富的网络和通信外围设备,提供了更大的灵活性、扩展能力和更高的集成度。

MPC8560简介MPC8560内部集成了两个处理模块:一个高性能嵌入式PowerPC e500内核和一个通信处理模块(CPM)。

此外,该芯片还提供了片内缓存、DDR控制器、可编程中断控制器、通用I/O口、DMA和I2C等多种接口控制器。

与使用较多的MPC8260最大的不同是,MPC8560增加了两个三速以太网控制器(Three-Speed Ethernet Controller,TSEC),实现了10Mb/s、100Mb/s和1Gb/s 三种不同速度的以太网协议接口控制。

本文将主要讨论如何使用这两个TSEC实现吉比特以太网接口。

吉比特以太网物理层协议及接口参考文献上对于网络协议的介绍往往局限于对协议分层的理论分析,对网络协议尤其是吉比特以太网协议在实际应用中的接口讨论较少,本文将对吉比特以太网协议在应用中的接口作总结性的介绍。

吉比特以太网协议的数据链路层与传统的10/100Mb/s以太网协议相同,但物理层有所不同。

三种协议与OSI七层模型的对应关系如图1所示。

图1三种以太网协议与OSI模型的对应关系从图1可以看出,吉比特以太网协议与10/100Mb/s以太网协议的差别仅仅在于物理层。

图中的PHY表示实现物理层协议的芯片;协调子层(Reconciliation sublayer)用于实现指令转换;MII(介质无关接口)/GMII(吉比特介质无关接口)是物理层芯片与实现上层协议的芯片的接口;MDI(介质相关接口)是物理层芯片与物理介质的接口;PCS、PMA和PMD则分别表示实现物理层协议的各子层。

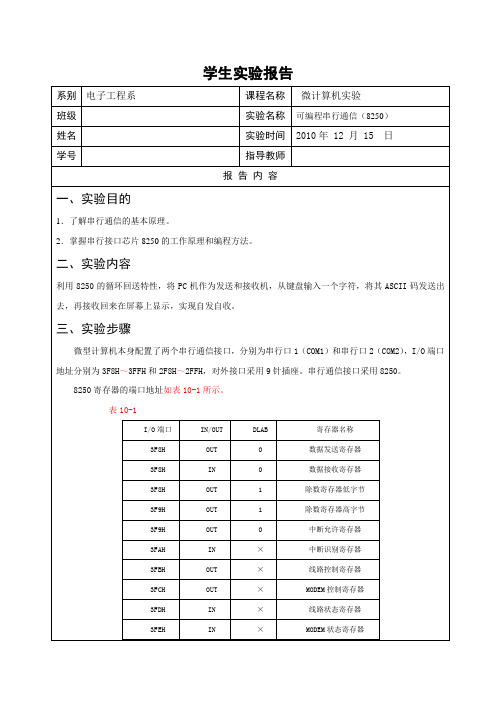

微机实验_可编程串行通信(8250)

微型计算机本身配置了两个串行通信接口,分别为串行口1(COM1)和串行口2(COM2),I/O端口地址分别为3F8H~3FFH和2F8H~2FFH,对外接口采用9针插座。串行通信接口采用8250。

8250寄存器的端口地址如表10-1所示。

表10-1

I/O端口

IN/OUT

DLAB

寄存器名称

60H

1200

00H

30H

2400

00H

18H

4800

00H

0CH

9600

3.中断允许寄存器IER(3F9H)如图10-2所示。

图10-2

4.MODEM控制寄存器MCR(3FCH)如图10-3所示。

图10-3

5.9针串口插座(DB-9)外形如图10-4所示,引脚说明如表10-3所示。

图10-4

表10-3

EXIT:MOVAH,4CH;返回DOS

INT21H

STARTENDP

CODEENDS

ENDSTART

五、实验结论与心得

成绩

教师签名

批改时间

年月日

;内部输出输入反接,中断禁止

MOVAL,13H

OUTDX,AL

MOVDX,3F9H;设中断允许寄存器为0,使4种中断被屏蔽

MOVAL,0H

OUTDX,AL;把接收到的字符显示出来,把键盘输入的字符发

;送出去

FOREVER:MOVDX,3FDH;输入线状态寄存器内容,测试接收是否出错

INAL,DX

TESTAL,1EH

3F8H

OUT

0

数据发送寄存器

3F8H

IN

0

数据接收寄存器

3F8H

厦门才茂工业级TD-SCDMA3GDTUCM8250P-CM8250EP技术参数(精)

厦门才茂TD-SCDMA DTU CM8150P/CM8150EP技术参数一、产品简介厦门才茂CM8250P/CM8250EP TD-SCDMA 3G DTU是一款工业级无线数据传输设备,通过联通WCDMA3G网络为用户提供透明TCP无线远距离数据传输或者透明UDP无线远距离数据传输的功能。

该产品采用ARM9工业级高性能嵌入式处理器,以实时操作系统为软件支撑平台,超大内存,内嵌自主知识产权的TCP/IP协议栈;同时提供串口RS232、RS485接口、RS422接口、TTL接口或者USB接口,设备可以直接客户的串口/USB设备相连;设备支持双数据中心备份,以及多数据中心同步接收数据等功能;设备提供在线维持技术,保持数据终端永久在线,保存数据链路任何时候畅通,实现高速、稳定、可靠的TCP/UDP 透明数据传输功能。

正对对网络流量和产品功耗比较敏感的客户,本产品支持语音、短信、数据触发上线以及超时自动断线的功能,降低流量降低产品功耗,实现低功耗功能。

该产品拥有ARM9工业级处理器和智能三级保护,它不但通过电力3000V电击测试,还拥有专利技术,产品性能稳定可靠。

该产品已广泛应用于电力集中抄表、水表集中抄表、热网监控、燃气监控、水利监控、环保检测、气象检测、地震监测,交通控制等等行业。

CM8250P产品接口图:产品全景正面接口反面接口CM8250P产品配件图片:电源串口线可配天线CM8250EP产品接口图:产品全景正面接口反面接口CM8250EP产品配件图片:可配天线电源整个20PIN排插外观数据线(20PIN排插/RS485/RS232/电源)二、产品特性工业级设计1.工业级CPU:工业级ARM9高性能嵌入式处理,200MPS;带 16KB Dcache,高速缓存数据,加快高速数据访问速度;带16KB Icache,高速指令缓存,加强了指令处理速度。

2.工业级无线模块:采用工业级无线模块,抗干扰强,传输稳定。

厦门才茂TD-SCDMA Camera-CM8250C 技术规范

CM8250C TD-SCDMA 3G Wireless Camera技术规范一、产品概述CM8250C TD-SCDMA 3G Wireless CAMERA 是3G无线视频监控设备,采用高性能的工业级ARM9通信处理器,以嵌入式实时操作系统为软件支撑平台,系统集成了3G无线技术、在线维持技术、视频技术和VPN安全技术,可以为客户提供远程、稳定、可靠的无线视频监控。

可广泛应用于移动车载视频采集、应急指挥现场视频监控、道路交通现场图像监控、汽车客运安全图像监控、野外模拟作战系统图像监控、金融安全监控、机房监控、工业现场仪器仪表监视等多个行业。

二、视频编码器技术参数图像传感器1/3 inch Sony CCD视频制式PAL/NTSC像素数PAL:795(H)×596(V) NTSC:811(H)×508 (V)图像尺寸Color:540TVL, B/W 600TVL日夜功能支持自动光圈N/A镜头特性定焦镜头:8mm/F1.2,可视角度:42°镜头接口M12,镜头可换照度Color 0.1Lux/F1.2, 0 Lux (IR ON)信噪比大于50dB伽玛校正0.45增益控制自动白平衡自动电子快门自动/手动,1/50~1/100000视频压缩标准H.264/M-JPEG视频分辨率D1/HD1/CIF/QCIF视频帧率PAL:25帧/秒,NTSC:30帧/秒,帧率可调视频码率32K~2Mbps码率可调,也可自定义码流类型视频流、复合流视频接口1路BNC模拟视频输出音频压缩标准G.711/G.726/AMR音频码率64Kbps/32Kbps/10.2Kbps音频输入1路,RCA接口三、无线路由器技术参数无线参数a)TD-SCDMA/HSDPA/HSUPA:2010~2025MHzGSM/GPRS/EDGE:850/900/1800/1900MHzb)支持3GPPclass B +24dBmc)数据速率Downlink (Max up to 2.8Mbps)Uplink (Max up to 384Kbps)硬件参数a)CPU:工业级ARM9 CPU,200MPS,16K Dcache,16K Icacheb)FLASH:8MB(可扩展至32MB)c)SDRAM:64MB(可扩展至256MB)d)接口:以太网口:一个10/100 Base-T 以太网口,Shielded RJ-45 1,5 kV isolation transformer,Ethernet IEEE 802-3, 802-2串口:RS232 serial port, (Support RS422/RS485 if needed)Rate:110bps~230400bpsData bits :7 or 8Parity: None, Even, OddStop bits: - 1 or 2Flow contro: None or RTS/CTSProtection – 15 kV ESD and short circuitConsole : RS-232, 115200 bps, 8 data bits,1 stop bit, no parity (8N1) 指示灯:。

Linux环境下基于MPC8250的SP接口驱动程序开发

◇ 具有独立的可编程波特率产生器;

◇ 时 钟 的相 位 和极性 可编程 :

◇ 开漏 输 出可支 持多 主工作 环境 ;

◇ 支 持本地 回环 测试 功能 。

2 l u 下 的设 备 驱 动 i x n

Ln x 备 驱 动 在 Ln x iu 设 iu 内核 中扮演 着 重要 的 角 色 。 它 们是 一 个 个 独立 的 “ 盒 子 ” 黑 。可 使某

1 电 子 元 器 件 主 用 20 .1 W . d c 2 0 71 e n c

维普资讯

第9 卷

2 7第1期 0 年 1 0 11 月

墓缔瘗

V1 N. o o1 . 1 9

NO .2 0 V 07

调 用映射 到 实 际硬件 设 备 的特有 操作 上 ,则是 驱

动 程序 的任 务 。这个 编程 接 口能 够使 驱 动 程序 独

vm

—

it ( m p n ma)

ar ea

_

(s ut fe , s u t tc i r l tc r

s u t ; 内存 重 映射操 作 tc r ) /

立 于 内核 的其它 部分 而建 立 ,必 要 的情 况 下 ,也

6x总 线 0

外 设 总 线

据线 (PD T ) S I A A 、主 发 从 收信 号 ( S) 主 收 MO I、

S I E S I OS S I IO S I K PS L PM I PM S P CL

从发 信 号 ( S )和 片选信 号 (PS L,可 用 在 MIO S IE )

特性 .给 出 了一个LN X系统环境 下 开发基 于MP 8 5 控制 器的S I 口驱动的程序 开发方 法。 IU C 20 P接 关键 词 :S I P ;驱动 ;l u ;MP 8 5 i x n C20

PowerPC产品介绍

1 x PCI 1 x miniPCI

-

-

SATA

MPC8315E 400MHz

128MB DDR2

8M NOR Flash 32M NAND Flash 256Kbits E2PROM

2 x 10/100/1000M

1 x PCI, 1 x miniPCI

PCI-Express, miniPCI -Express

国基科技推出MPC85XX 系列开发系统,由处理器卡和Type-N,Type-S 和Type-A 三种载板组合而成,可分别应用于通信网络、贮存设备和ATCA/μTCA 系统的开发。

PQIII处理器系列,包括MPC8540,MPC8541E,MPC8555E 和MPC8560。主频可高达1GHz 以上、内嵌两个千兆以太网控制器的MPC85xx系列芯片是飞思卡 尔定位于高端通信控制产品的芯片系列,MPC8560可以完整支持ATM 以及TDM 的电信级应用,而MPC8541E 则是高端防火墙的最佳解决方案,在国内外已经 有多款基于此芯片的产品。

16 Mbytes

256M DDR1

256M DDR1

16 Mbytes 16 Mbytes

RAM

Flash

PQIII 处理卡与 Type-S :载板组合开发系统硬件资源 应用场合:网络存储应用

Ethernet

PCI

SATA 接口&USB

1 x 10/100/1000M 4-port 10/100 Ethernet switch

载板尺寸 220mm x 148mm 6 层PCB 印刷

4pin 5V, 12V 电源输入

欢迎来电询问:Tel: 010-82895205,62965536-856 dgq@ zj@

实验八 8250可编程通信实验

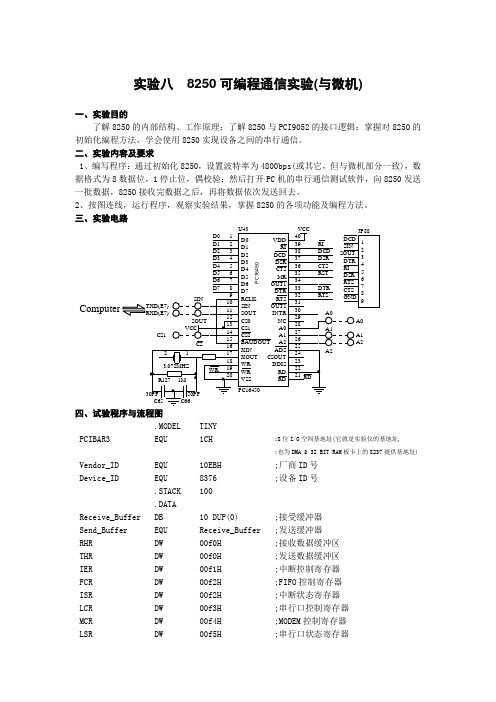

实验八8250可编程通信实验(与微机)一、实验目的了解8250的内部结构、工作原理;了解8250与PCI9052的接口逻辑;掌握对8250的初始化编程方法,学会使用8250实现设备之间的串行通信。

二、实验内容及要求1、编写程序:通过初始化8250,设置波特率为4800bps(或其它,但与微机部分一致),数据格式为8数据位,1停止位,偶校验;然后打开PC机的串行通信测试软件,向8250发送一批数据,8250接收完数据之后,再将数据依次发送回去。

MSR DW00f6H ;MODEM状态寄存器DLL DW 00f0H;波特率除数锁存器低位DLM DW00f1H;波特率除数锁存器高位ADR DW 00E0H ;用于清除PCI9052上一次写操作产生的地址IO_Bit8_BaseAddress DW?msg0 DB ‘BIOS不支持访问PCI $’msg1 DB ‘找不到Star PCI9052板卡 $’msg2 DB ‘读8位I/O空间基地址时出错$’.CODESTART: MOV AX,@DATAMOV DS,AXNOPCALL InitPCICALL ModifyAddress ;根据PCI提供的基地址,将偏移地址转化为实地址CALL INIT8250START2: MOV CX,10 ;接收数据(接收完设定的数据个数) CALL RECEIVE_GROUPMOV CX,10 ;发送数据(发完设定的数据个数)CALL SEND_GROUPJC WARNING1CALL IfExitJZ START2JMP ExitWARNING1: JMP Exit;*************发送一组字符子程序,个数在CX中***********Send_Group PROC NEARLEA SI,Send_BufferSend_Group1: LODSBCALL Send_ByteJC Send_Group2LOOP Send_Group1CLCSend_Group2: RETSend_Group ENDP;*************接收一组字符子程序,存放首地址在DPTR中,个数在R6R7中*********** Receive_Group PROC NEARMOV DX,ADROUT DX,AL ;用于清除PCI9052上一次写操作产生的地址LEA DI,Receive_BufferReceive_Group1: CALL Receive_ByteSTOSBLOOP Receive_Group1CLCRETReceive_Group ENDPINIT8250 PROC NEARMOV DX,ISRMOV AL,06HOUT DX,ALMOV DX,LCRMOV AL,83H ;允许访问波特率因子寄存器OUT DX,ALMOV DX,DLLMOV AL,40 ;除法除数低位寄存器,波特率设为;4800=(3.072*1000000/16)/DLMDLLOUT DX,ALMOV DX,DLM ;00H送高字节寄存器MOV AL,00HOUT DX,ALMOV DX,LCR ;不允许访问波特率因子寄存器MOV AL,1BH ;数据格式为8数据位,1停止位,偶校验OUT DX,ALRETINIT8250 ENDP;*********发送一个字节子程序,发送A中的数,失败置1CY*********Send_Byte PROC NEARPUSH CXPUSH AXMOV CX,1000MOV DX,LSRREP11: IN AL,DXTEST AL,20HJNZ OUTPORT1LOOP REP11POP AXSTCJMP EXIT8250OUTPORT1: POP AXMOV DX,RHROUT DX,ALMOV DX,ADROUT DX,AL ;清除PCI9052产生的RHR地址CLCEXIT8250: POP CXRETSend_Byte ENDP;*********接收一个字节子程序,接收字节在A中,接收失败置1CY*********Receive_Byte PROC NEAR MOV DX,LSR Receive1: IN AL,DX TEST AL,1 JZ Receive1 Receive2: MOV DX,RHR IN AL,DX Receive3: RET Receive_Byte ENDP Exit: MOV AH,4CH INT 21H; IfExit 、InitPCI 、ModifyAddress 子程序请参阅实验二 END START五、实验过程 12、运行程序3、运行“串口助手(ComPort.EXE)”,设置串口(波特率4800,8个数据位,一个停止位,偶校验),打开串口,选择“HEX发送”、“HEX显示”,向8250发送10个字节数据(输入数据之间用空格分隔),是否能接收到10个字节数据,接收到的数据是否与发送数据一致。

最新-MPC8250处理器及其在宽带接入中的应用 精品

MPC8250处理器及其在宽带接入中的应用摘要8250是公司推出的高性能32位嵌入式微处理器82系列中的一种,本文介绍8250的结构与特点,并与860的特点进行对比,在此基础之上分析8250应用于宽带接入产品的优势所在。

最后提出一种充分利用8250优点的接入路由器硬件设计方案。

关键词嵌入式处理器8250接入路由器18250简介8250是公司在嵌入式徽顺860基础之上推出的82系列微处理器中的一种。

82系列保留了860的嵌入式内核和通信处理模块并存的体系结构,同时进一步提高了工作频率、集成了更多的外围器件、提供了丰富的总线接口。

其中,8250没有集成在一数据通信设备中不常使用、而且较为昂贵的处理模块,进一步降低了成本。

8250的内部结构基于结构,主要由内核、系统接口单元、通信处理单元构成。

它支持60总线,其数据线为64位,地址线为32位;支持总线,其数据线为32位,地址线为32位。

内核工作时钟最高300,工作时钟最高200。

内部结构如图1所示。

①内核完成中央处理器的功能,执行高层程序偌,它与和通过独立的指令和数据通信,通过对存储器进行管理。

②系统接口单元包括的复位、中断控制器、时钟配置等功能。

内部包括60总线控制器、总线到60总线的桥接器、存储器控制器、时钟控制器等。

8250的存储控制器部分集成了控制器,通过设置寄存器即可完成与的接口配置,与860配置表的方式相比,极大地降低了开发的复杂度。

范文先生网收集整理③通信处理单元可与内核并行工作,处理通信控制中的底层任务。

内部包括32位通信控制器、通道、用于内部交换数据的32双口、中断控制器、波特率发生器、计数器等。

部分还集成了4个时分复用接口、3个媒体无关接口和非时分复用串行接口。

嵌入式处理器MPC8250与CF卡的接口设计

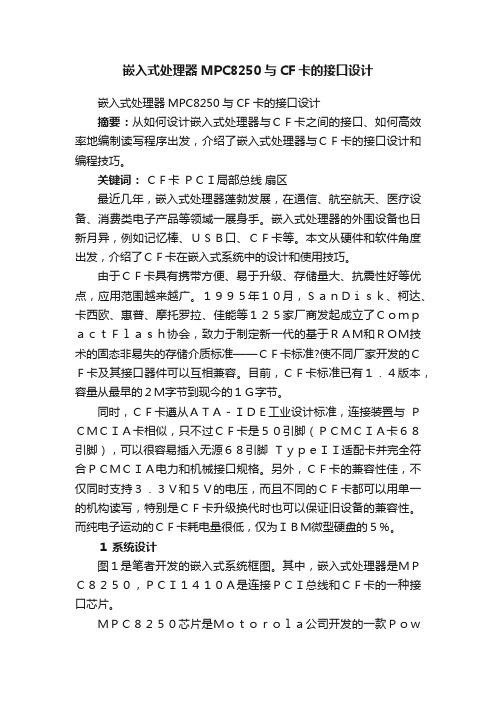

嵌入式处理器MPC8250与CF卡的接口设计嵌入式处理器MPC8250与CF卡的接口设计摘要:从如何设计嵌入式处理器与CF卡之间的接口、如何高效率地编制读写程序出发,介绍了嵌入式处理器与CF卡的接口设计和编程技巧。

关键词:CF卡PCI局部总线扇区最近几年,嵌入式处理器蓬勃发展,在通信、航空航天、医疗设备、消费类电子产品等领域一展身手。

嵌入式处理器的外围设备也日新月异,例如记忆棒、USB口、CF卡等。

本文从硬件和软件角度出发,介绍了CF卡在嵌入式系统中的设计和使用技巧。

由于CF卡具有携带方便、易于升级、存储量大、抗震性好等优点,应用范围越来越广。

1995年10月,SanDisk、柯达、卡西欧、惠普、摩托罗拉、佳能等125家厂商发起成立了CompactFlash协会,致力于制定新一代的基于RAM和ROM技术的固态非易失的存储介质标准——CF卡标准?使不同厂家开发的CF卡及其接口器件可以互相兼容。

目前,CF卡标准已有1.4版本,容量从最早的2M字节到现今的1G字节。

同时,CF卡遵从ATA-IDE工业设计标准,连接装置与PCMCIA卡相似,只不过CF卡是50引脚(PCMCIA卡68引脚),可以很容易插入无源68引脚TypeII适配卡并完全符合PCMCIA电力和机械接口规格。

另外,CF卡的兼容性佳,不仅同时支持3.3V和5V的电压,而且不同的CF卡都可以用单一的机构读写,特别是CF卡升级换代时也可以保证旧设备的兼容性。

而纯电子运动的CF卡耗电量很低,仅为IBM微型硬盘的5%。

1系统设计图1是笔者开发的嵌入式系统框图。

其中,嵌入式处理器是MPC8250,PCI1410A是连接PCI总线和CF卡的一种接口芯片。

MPC8250芯片是Motorola公司开发的一款PowerPC系列嵌入式处理器。

芯片采用小巧而强大的32位超标量体系结构PowerPC603e处理器内核,最高主频为300MHz。

它集成了PCI桥、PCI仲裁器、存储器控制器、中断控制器、DMA控制器、16K字节指令高速缓存和16K字节数据高速缓存等部件。

8250源码解析

8250源码解析

8250是一款经典的串行通信芯片,被广泛应用于计算机和其他设备之间的串行通信。

以下是关于8250源码的解析:

8250是一款可编程的串行通信芯片,通过编程可以设置串行通信的波特率、数据位数、停止位数、奇偶校验等参数。

在8250的源码中,主要包含以下几个部分:

1、初始化程序:初始化程序用于设置8250芯片的初始状态,包括控制寄存器的设置、波特率发生器的设置等。

初始化程序通常在系统启动时运行一次,以确保串行通信的正常进行。

2、发送程序:发送程序用于将数据发送到串行通信线上。

在8250的源码中,发送程序将数据写入到发送缓冲区,然后通过控制寄存器启动发送。

发送程序还需要处理发送中断,以确定数据是否已经成功发送。

3、接收程序:接收程序用于从串行通信线上接收数据。

在8250的源码中,接收程序通过控制寄存器启动接收。

当接收到数据时,接收程序会将数据写入到接收缓冲区,并产生一个接收中断。

4、中断处理程序:中断处理程序用于处理接收和发送中断。

在8250的源码中,中断处理程序会检查接收和发送的状态,并执行相应的操作,例如清空缓冲区、启动发送或接收等。

除了以上几个部分,8250的源码还包括一些辅助函数,例如读写控制寄存器、读写数据寄存器等。

这些函数用于操作8250芯片的各种寄存器,确保串行通信的正常进行。

总的来说,8250的源码结构比较清晰,通过初始化程序、发送程序、接收程序和中断处理程序等几个部分,可以完成串行通信的功能。

在实际使用中,需要根据具体的应用场景和需求进行适当的配置和优化。

串行通信接口技术

(5) 除数锁存器(3F8H/3F9 H,只写)

除 数 锁 存 器 为 16 位 , 由 高 8 位 和 低 8 位锁 存 器 组 成 ,对 时 钟 输 入 ( 1.8432MHZ)进行分频,产生16倍波特率的波特率发生器(即BAUDOUT) 。除数可由下面公式算出:

(4) 设置中断允许寄存器

假设禁止中断,编程如下:

MOV AL, 00H

;禁止所有中断的控制字

MOV DX, 3F9H

OUT DX, AL

;写入中断允许寄存器

10.2.2 PC机与8051双机通信技术

图10-10 PC机与单片机串行通信接口线路图

MC1488将TTL电平转换为RS-232C电平,供电电压为±12V; MC1489则是把RS-232C标准电平转换为TTL电平,供电电 压为+5V

OUT

除数锁存器(高位)

OUT

中断允许寄存器

IN

中断识别寄存器

OUT

通信线控制寄存器

OUT

MODEM控制寄存器

IN

通信线状态寄存器

IN

MODEM状态寄存器

*

通信线控制寄存器7位(DLAB)=0

**

DLAB=1

(1) 通信线控制寄存器(3FBH,只写)

图10-5 通信线控制寄存器

(2) 通信线状态寄存器(3FDH,只读)

状态中断O被UT允1 许,每当MODEM状态寄存器的RI位由高变低时产生一次中断。

● 输出1( )

OUT 1

用户指定O的UMTO2DEM控制功能的输出。通过对MODEM控制寄存器第2位编程置1, 引脚就

变成低电平。

OUT 2

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MPC8250处理器及其在宽带接入中的应用摘要:MPC8250是Motorola公司推出的高性能32位嵌入式微处理器MPC82XX系列中的一种,本文介绍MPC8250的结构与特点,并与MPC860的特点进行对比,在此基础之上分析MPC8250应用于宽带接入产品的优势所在。

最后提出一种充分利用MPC8250优点的接入路由器硬件设计方案。

关键词:嵌入式处理器 MPC8250 接入路由器1 MPC8250简介MPC8250是Motorla公司在嵌入式徽顺MPC860基础之上推出的MPC82XX系列微处理器中的一种。

MPC82XX系列保留了MPC860的嵌入式PowerPC内核和通信处理模块CPM并存的体系结构,同时进一步提高了工作频率、集成了更多的外围器件、提供了丰富的总线接口。

其中,MPC8250没有集成在一数据通信设备中不常使用、而且较为昂贵的ATM处理模块,进一步降低了成本。

MPC8250的内部结构基于PowerQUICC结构,主要由PowerPC内核、系统接口单元SIU、通信处理单元CPM构成。

它支持60x总线,其数据线为64位,地址线为32位;支持PCI/LOCAL总线,其数据线为32位,地址线为32位。

内核工作时钟最高300MHz,CPU工作时钟最高200MHz。

内部结构如图1所示。

①PowerPC内核:完成中央处理器的功能,执行高层程序偌,它与SIU和CPM通过独立的指令Cache和数据Cache 通信,通过MMU对存储器进行管理。

②系统接口单元SIU:包括CPU的复位、中断控制器、时钟配置等功能。

内部包括60x总线控制器、PCI/LOCAL总线到60x总线的桥接器、存储器控制器、时钟控制器等。

MPC8250的存储控制器部分集成了SDRAM控制器,通过设置寄存器即可完成与SDRAM的接口配置,与MPC860配置UPM表的方式相比,极大地降低了开发的复杂度。

③通信处理单元CPU:CPM可与内核并行工作,处理通信控制中的底层任务。

内部包括32位RISC通信控制器、DMA通道、用于内部交换数据的32KB双口RAM、中断控制器、波特率发生器、计数器等。

CPM部分还集成了4个时分复用TDM接口、3个媒体无关接口MII和非时分复用串行接口NMSI三种物理层接口,它们之间的选择由串行接口SI模块控制。

CPM部分最主要的功能模块是它所集成的大量可同时使用的通信控制单元,包括:*1个多通道通信控制器MCC,可工作于HDLC模式,物理层接口为TDM方式,最多可以同时与4个TDM接口相连;*3个快速通信控制器FCC,可工作于HDLC、10M/100Mbit/s以太网和透明模式,物理层接口为TDM或MII方式,当物理层工作于TDM方式时,最高可以支持T3/E3速率;*4个串行通信控制器SCC,可工作于HDLC、UART、同步UART、BISYNC、10Mbit/s以太网、AppleTalk、透明模式,物理层接口为TDM或NMSI方式;*2个串行管理控制器SMC,可工作于UART或透明方式,物理层接口为TDM或NMSI方式;[!--empirenews.page--]*1个I2C控制器;*1个SPI控制器。

2 MPC8250与MPC860的对比现有的很多宽带接入产品多是以Motorola公司的PowerQUICC系列CPU MPC860为核心构建的。

与MPC8250相比,除了通信控制单元类型不够丰富、存储控制器的UPM方式开发难度高等缺点之外,另一个显著的劣热是工作时钟频率低。

这不仅制约了系统的处理能力,也增加了软件开发的难度。

表1简要对比了MPC8250与MPC860的特点。

表1 MPC8250与MPC860的对比MPC8250MPC860内核工作时钟300MHz50MHzCPM工作时钟200MHz50MHz总线数据宽度64bit32bitPCI总线支持有无存储器控制器个数128MCC1无FCC3无SCC44SMC223 MPC8250在宽带接入中的应用在目前的宽宽带接入中,一个显著的特点就是硬件接口和协议类型均呈现出多样化、复杂化的特征,这就对宽带接入产品提出了更高的要求。

一方面,要在面积有限的电路板上支持更多类型的接口;另一方面,要处理更多、更复杂的通信协议。

以宽带执着入中常见的接入路由器为例,一般需要提供以下功能:①对内提供2个100Mbit/s以太网接口;②对外应提供各种类型的广域网接口模块;③支持PPP、PPPoE、LAPB等链路层协议;④支持IP、IPX等网络层协议;⑤支持RIP、OSPF、BGP等路由协议;④支持组插、安全管理、VPN等机制。

可见,接入路由器以及类似的家庭网关、宽带接入集线路等设备的特点是不仅硬件接口多;而且由于协议众多,需要处理器具有相当的处理能力。

MPC8250本身即可通过内部集成的FCC支持3个100Mbit/s以太网接口或E1/E3接口,内部还集成了PCI总线控制器,因此可以减少使用外围扩展芯片;而且被减少的外围扩展芯片:PCI桥芯片和100Mbit/s以太网MAC芯片是硬件设计使用外扩芯片中引脚较多、接口较复杂的芯片。

同时MPC8250还提供了4个SCC,可用于提供数据速率较低的通信接口,如10Mbit/s以太网接口、E1接口、ISDN PRI/BRI接口、X.25接口等。

此外,MPC8250内核的工作时钟和CPM工作时钟均达到了百MHz级别。

可见,将MPC8250用于宽带接入产品的设计可以充分利用MPC8250的优点,提供更为强大的处理能力,并在提高硬件集成度、降低软件开发难度的同时降低硬件成本。

4 基于MPC8250的接入路由器设计根据上文对接入路由器的功能分析,接入器由器的硬件主要由中央处理器、广域网接口模块、局域网(以太网)接口模块、维护、调试接口模块、内存SDRAM、引导Flash等同部分构成。

其中:MPC8250可通过内部集成的FCC支持2个100Mbit/s以太网接口,由于FCC支持标准的MII接口,因此可以直接与以太网的物理层收发器相连接;MPC8250内部集成了PCI总线控制器,可以用于提供与加密模块的接口;同时MPC8250仍然保留了4个SCC,可用于提供广域网接口;由于内部的SMC不提供Modem控制信号,因此为了支持远程拨号维护,扩串口控制芯片;此外,SDRAM、Flash、Bootrom、NVRAM等器件均通过60x总线与MPC8250连接。

基于MPC8250的接入路由器内部硬件结构如图2所示。

[!--empirenews.page--]除MPC8250外各模块设计说明如下:①总线驱动:由于MPC8250的总线驱动能力有限,而60x总线上器件较多,除SDRAM与MPC8250直接相连外,其它器件与MPC8250的物理距离均较远,因此采用74LVC245提供数据总线的驱动,采用74LVTH244提供地址总线的驱动,采用74LVTH244为走线较长的总线控制信号(部分片选、R/W、OE等)提供总线驱动。

②广域网接口卡:主要完成电平转换功能,以PCMCIA插卡的形式提供。

其中SCC1、SCC2对应插卡1,SCC3、SCC4对应插卡2,插卡可以是多协议串口卡、ISDN PRI接口卡、E1接口卡等。

如果是多协议串口卡则一块插卡提供两路广域网接口,即SCC1、SCC2通过插卡1分别对应一路广域网接口。

此时SCC1、[1][2]下一页SCC2的物理层接口均应工作在NMSI方式;如果是ISDN PRI或E1/T1接口卡则一块插卡提供一路扩域网接口,此时SCC1、SCC2的物理层接口均应工作在TDM方式。

③网络加密模块:以PMC 插卡形式提供,提供用于VPN的加密/解密功能。

④以太网物理层接口芯片:完成以太网线路侧与以太网MAC收发器之间的电平转换、保护等功能,遵循与MAC层之间的MII接口规范,与MPC8250的FCC通过MII接口直接相连。

⑤串口通信芯片:由于MPC8250内部SMC接口的UART方式没有Modem控制信号,无法支持远程拨号连接,因此,需要扩展串口通信芯片,使用双路UART收发器实现。

常见的双路UART收发器均支持硬件流控,内部带有FIFO的缓存,支持DMA方式。

两路UART中:一路用做本地维护串口同时在开发过程中用做调试串口;一路用做远程维护串口。

串口通信芯片与MPC8250以60x总线相连。

⑥SDRAM:用于存放用户的数据和代码,为程序的运行和保存临时文件提供空间。

采用商用的168引脚的64/128Mbyte内存条,与MPC8259以60x总线相连。

数据宽度为64位。

MPC825提供了SDRAM控制器,与MPC860的UPM表编程相比,只需进行寄存器的设置,降低了开发的难度。

⑦Flash:用于存储操作系统内核、文件系统映像和用户程序文件。

与MPC8250以60x总线相连,设计为类似SDRAM内存条的Flash插卡形式,可支持8/16/32MB不同大小的Flash插卡。

数据宽度为32位。

⑧Bootrom:存储操作系统内的引导程序与MPC8250以60x总线相连。

Bootrom实际上也是一块Flash芯片,大小为512KB,数据宽度为8位。

⑨NVRAM:保存系统和用户的配置文件,与MPC8250以60x总线相连,大小为64/128KB。

⑩EPLD:给出必须的逻辑控制信号、时序调整信号、译码片选信号等,要用Altera、Xilinx等公司的产品。

[!--empirenews.page--]5 MPC8250与Flash的接口设计在接入路由器的设计中,要求兼容8/16/32MB不同大小的Flash插卡,即在驱动程序中应能检测出不同大小的Flash插卡,而Flash插槽的数据总线宽度为32位。

因此使用4片16位的Flash,以存储器扩展的方式完成MPC8250与Flash的接口设计,如图3所示。

Chip1、Chip3、Chip2、Chip4为4片Flash芯片。

其中Chip1与Chip3、Chip2与Chip4分别对应数据线的低16位和高16位,Chip1与Chip2、Chip3与Chip4分别构成2个存储器Bank,对应MPC8250的2个片选CS3和CS4。

由于构成的是32位Flash插卡,最大32MB,因此使用MPC8250的地址线A[8~29]与Flash插槽的A[21~0]相连,假设Flash的地址空间为0xF0000000~0xf1ffffff,那么当分别使用8/16/32MB大小的Flash插卡时,以INTEL的28F 系列Flash为例,每个存储器Bank的地址空间分配如表2所列。

表2 Flash地址空间的分配Flash插卡大小芯片使用芯片型号Bank1地址空间Bank2地址空间8MB4×2MB28F1600xf0000000~0xf03fffff0xf1000000~0xf13fffff16MB4×4MB28F3200xf0000000~0xf07fffff0xf1000000~0xf17fffff32MB4×8MB28F6400xf0000000~0xf0ffffff0xf1000000~0x0xf1ffffff在驱动程序的初始化过程中,可分别在2个存储器Bank的起始地址0xf0000000和0xf1000000处读取芯片的制造商标识和芯片标识,以此确定所使用的Flash芯片,从而确定Flash插卡的大小,然后即可按上表确定的地址空间使用Flash,这样就实现了对Flash插卡大小的自动检测。