第5章 寄存器设计应用

数字电子技术基础第五章

4. 画状态转换图和时序图 圆圈内表示 Q2 Q1 Q0 的状态;箭头 表示电路状态转换的方向;箭头上方的 Q2 Q1 Q0 “ x / y ”中,x 表示转换所需的输入变 量取值, y/ 0 表示现态下的输出值。本例 /0 /0 /0 /0 000 001 中没有输入变量,故 010 011 101 x100 处空白。 /1 x/y 现

电路工作前加负脉冲清零;工作时应置 RD = 1。 FF0 1J C1 1K R

FF1 1J C1 1K R

1

Q0

Q1

CP RD

FF2 1J Q2 C1 1K R Q2

Y

EXIT

时序逻辑电路

1. 写方程式 (1) 输出方程 Y = Q2n Q0n (2) 驱动方程 J0 = K0 = 1 J1 = K1 = Q2n Q0n J2 = Q1n Q0n , K2 = Q0n (3) 状态方程 代入 Q J0 n= K0 = 1 n Q 2 n FF 0 FF FF n +1 n 2 0 1 n n nQ n Q0 =J J Q + K Q n n K = 1 Q + 1 Q 0 0 0 0 Q0 Q0 0 & 1J Q 0 0 1 & 1J 0 =Q 2 2 n 1 1J 代入 J1 = K1 = Q2 Q0n C1 n + K Q nC1 n Q n C1 n Q1n+1 = J Q = Q 1 1 1 1 2 0 Q1 1K 1K & 1K n+ Q n Q n n +K n = Q nQ nQ R R R Q2n+1 = Q K Q JJ 1 0 2 0Q 2 2 2 2 2 2 2 CP 2 RD 代入 J2 = Q1n Q0n ,K2 = Q0n Q0n Y

单片机 第五章2 单片机的定时器计数器

若晶振频率为6MHz,1个机器周期为1/6 x 10-6 x12=2μs 则最小定时时间为:[213 –(213 -1)]x2μs=2μs 最大定时时间为:[213 –0] x2μs=16384μs =16.384ms

2、 方式1 (T1,T0) 当M1M0两位为 01时,定时 /计数器被选为工作方式 1,16位计数器,其逻辑结构 如图 所示。

8FH TCON TF1 8EH TR1 8DH TF0 8CH TR0 8BH IE1 8AH IT1 89H IE0 88H IT0

TF1(TCON.7, 8FH位)----定时器T1中断请求溢出标志位。 TF0(TCON.5, 8DH位)----定时器T0中断请求溢出标志位。 TR1(TCON.6, 8EH位)----T1运行控制位。 0:关闭T1;1:启动T1运行。只由软件置位或清零。 TR0(TCON.4, 8CH位)----T0运行控制位。 0:关闭T0;1:启动T0运行。只由软件置位或清零。

1、 方式0 (T1,T0)

当 M1M0两位为 00时,定时 /计数器被选为工作方式 0, 13位计数器,其逻辑结 构如图所示。

振荡器 ÷12 C/ T = 0 TL0 低5位 C/ T = 1 控制 T0 端 TR0 GATE INT0 端 TH0 高8 位 TF0 中断

+

在方式0下,计数工作方式时,计数值的范围是: 1~8192(213 ) 定时工作方式时,定时时间的计算公式为: (213一计数初值)×晶振周期×12 或(213一计数初值)×机器周期

例4:用定时器l 以工作方式2计数,每计100次进行累计器加1操作.

(1)计算计数初值. 28—100=156D=9CH TH1=9CH,TL1=9CH TMOD寄存器初始化:MlM0=10,C/T=1,GATE=0 因此 TMOD=60H (2)程序设计序设计

2023年大学_EDA技术与VHDL第二版(潘松著)课后习题答案下载

2023年EDA技术与VHDL第二版(潘松著)课后习题答案下载EDA技术与VHDL第二版(潘松著)课后答案下载第1章 EDA技术概述1.1 EDA技术及其发展1.1.1 EDA技术的发展1.1.2 EDA技术的涵义1.1.3 EDA技术的基本特征1.2 EDA技术的主要内容及主要的EDA厂商1.2.1 EDA技术的主要内容1.2.2 主要EDA厂商概述1.3 EDA技术实现目标1.3.1 超大规模可编程逻辑器件1.3.2 半定制或全定制ASIC1.3.3 混合ASIC1.4 EDA技术应用1.4.1 EDA技术应用形式1.4.2 EDA技术应用场合1.5 EDA技术的发展趋势1.5.1 可编程器件的发展趋势1.5.2 软件开发工具的发展趋势1.5.3 输入方式的发展趋势__小结思考题和习题第2章大规模可编程逻辑器件2.1 可编程逻辑器件概述2.1.1 PLD的'发展进程2.1.2 PLD的种类及分类方法2.2 简单可编程逻辑器件2.2.1 PLD电路的表示方法及有关符号 2.2.2 PROM基本结构2.2.3 PLA基本结构2.2.4 PAL基本结构2.2.5 GAL基本结构2.3 复杂可编程逻辑器件2.3.1 CPLD基本结构2.3.2 Altera公司器件2.4 现场可编程逻辑器件2.4.1 FPGA整体结构2.4.2 Xilinx公司FPGA器件2.5 在系统可编程逻辑器件2.5.1 ispLSl/pLSl的结构2.5.2 Lattice公司ispLSI系列器件 2.6 FPGA和CPLD的开发应用2.6.1 CPLD和FPGA的编程与配置2.6.2 FPGA和CPLD的性能比较2.6.3 FPGA和CPLD的应用选择__小结思考题和习题第3章 EDA设计流程与开发3.1 EDA设计流程3.1.1 设计输入3.1.2 综合3.1.3 适配3.1.4 时序仿真与功能仿真3.1.5 编程下载3.1.6 硬件测试3.2 ASIC及其设计流程3.2.1 ASIC设计方法3.2.2 一般的ASIC设计流程3.3 可编程逻辑器件的开发环境 3.4 硬件描述语言3.5 IP核__小结思考题和习题第4章硬件描述语言VHDL4.1 VHDL概述4.1.1 VHDL的发展历程4.1.2 VHDL的特点4.2 VHDL程序基本结构4.2.1 实体4.2.2 结构体4.2.3 库4.2.4 程序包4.2.5 配置4.3 VHDL基本要素4.3.1 文字规则4.3.2 数据对象4.3.3 数据类型4.3.4 运算操作符4.3.5 VHDL结构体描述方式 4.4 VHDL顺序语句4.4.1 赋值语句4.4.2 IF语句4.4.3 等待和断言语句4.4.4 cASE语句4.4.5 LOOP语句4.4.6 RETIARN语句4.4.7 过程调用语句4.4.8 REPORT语句4.5 VHDL并行语句4.5.1 进程语句4.5.2 块语句4.5.3 并行信号代人语句4.5.4 并行过程调用语句4.5.5 并行断言语句4.5.6 参数传递语句4.5.7 元件例化语句__小结思考题和习题第5章 QuartusⅡ软件及其应用5.1 基本设计流程5.1.1 建立工作库文件夹和编辑设计文件 5.1.2 创建工程5.1.3 编译前设计5.1.4 全程编译5.1.5 时序仿真5.1.6 应用RTL电路图观察器5.2 引脚设置和下载5.2.1 引脚锁定5.2.2 配置文件下载5.2.3 AS模式编程配置器件5.2.4 JTAG间接模式编程配置器件5.2.5 USBBlaster编程配置器件使用方法 __小结思考题和习题第6章 VHDL应用实例6.1 组合逻辑电路设计6.1.1 基本门电路设计6.1.2 译码器设计6.1.3 数据选择器设计6.1.4 三态门设计6.1.5 编码器设计6.1.6 数值比较器设计6.2 时序逻辑电路设计6.2.1 时钟信号和复位信号6.2.2 触发器设计6.2.3 寄存器和移位寄存器设计6.2.4 计数器设计6.2.5 存储器设计6.3 综合实例——数字秒表的设计__小结思考题和习题第7章状态机设计7.1 一般有限状态机7.1.1 数据类型定义语句7.1.2 为什么要使用状态机 7.1.3 一般有限状态机的设计 7.2 Moore型有限状态机设计 7.2.1 多进程有限状态机7.2.2 单进程有限状态机7.3 Mealy型有限状态机7.4 状态编码7.4.1 状态位直接输出型编码 7.4.2 顺序编码7.4.3 一位热码编码7.5 状态机处理__小结思考题和习题第8章 EDlA实验开发系统8.1 GW48型实验开发系统原理与应用8.1.1 系统性能及使用注意事项8.1.2 GW48系统主板结构与使用方法8.2 实验电路结构图8.2.1 实验电路信号资源符号图说明8.2.2 各实验电路结构图特点与适用范围简述8.3 GW48CK/GK/EK/PK2系统信号名与芯片引脚对照表 __小结思考题和习题第9章 EnA技术实验实验一:全加器的设计实验二:4位加减法器的设计实验三:基本D触发器的设计实验四:同步清零计数器的设计实验五:基本移位寄存器的设计串人/串出移位寄存器实验六:同步预置数串行输出移位寄存器的设计实验七:半整数分频器的设计实验八:音乐发生器的设计实验九:交通灯控制器的设计实验十:数字时钟的设计EDA技术与VHDL第二版(潘松著):内容简介《EDA技术与VHDL》主要内容有Altera公司可编程器件及器件的选用、QuartusⅡ开发工具的使用;VHDL硬件描述语言及丰富的数字电路和电子数字系统EDA设计实例。

微机原理与汇编语言实用教程_第5章_运算程序设计及应用举例

/webnew/

第5章 运算程序设计及应用举例 章

5.1.4 除法指令 1.无符号数除法指令DIV (Unsigned Divide Instruction) 指令格式:DIV SRC (AX) (SRC) (AX)/(SRC)商、AH AH (AX) (AX)/ 功能:如果SRC是字节操作数,则把AX中的无符号数除以SRC,得到8位 的商送AL中,8位的余数送AH中,即:AL AL 8 AH AL (SRC)余数。 如果SRC是字操作数,则把DX和AX中的无符号数除以SRC,得到16位的 商送AX中,16位的余数送DX中,即:AX (DX,AX)/(SRC)余数。 指令对标志位的影响无定义。 (DX,AX)/(SRC)商、DX

IMUL指令除了运算对象是有符号数之外,其它都与MUL指令一样,但计算结果 不同。如果乘积的高半部分有符号扩展,则CF=OF=0,否则CF=OF=1。 例5.8 有符号数0B4H与11H相乘。 MOV AL,0B4H MOV BL,11H IMUL BL ;(AL)=0B4H=-76D ;(BL)=11H=17D ;AX)=(AL)×(BL)=(-76)×17=-1292D=0FAF4H ;CF=OF=1

/webnew/

第5章 运算程序设计及应用举例 章

例5.4 DATA SUB1 SUB2 SUB3 DATA 双精度数带借位减法运算。 SEGMENT DW 7788H,5566H DW 3344H,1122H DW 0,0 ENDS … MOV AX,SUB1 SUB AX,SUB2 MOV SUB3,AX MOV AX,SUB1+2 SBB AX,SUB2+2 MOV SUB3+2,AX …

/webnew/

第5章 运算程序设计及应用举例 章

第5章习题答案

间接寻址(Indirect Addressing)

寄存器寻址(Register Addressing)

寄存器间接(Register indirect Addressing) 偏移寻址(Displacement Addressing)

变址寻址(Indexing)

变址寄存器(index register)

000

RS 型 OP (6 位) 01 R t (3 位) 10 Rs (3 位) RX 型 OP (6 位) 01 R t (3 位) 11 Rx (3 位)

Offset16 (16 位)

XI 型 OP (6 位) 11 Rx (3 位) Offset16 (16 位) 00 Imm16 (16 位)

可执行程序文件(Executable program file)

链接程序(Linker / Link editor)

装入程序(Loader)

全局指针(Global pointer )

伪指令(pseudo-instruction)

CISC(Complex Instruction Set Computer) RISC(Reduced Instruction Set Computer)

微机原理第5章存储器系统

3. 工作方式

数ห้องสมุดไป่ตู้读出 字节写入:每一次BUSY正脉冲写

编程写入

入一个字节

自动页写入:每一次BUSY正脉冲写

入一页(1~ 32字节)

字节擦除:一次擦除一个字节 擦除

片擦除:一次擦除整片

72

4. EEPROM的应用

可通过编写程序实现对芯片的读写; 每写入一个字节都需判断READY / BUSY

主存储器 虚拟存储系统

磁盘存储器

8

Cache存储系统

对程序员是透明的 目标:

提高存储速度

Cache

主存储器

9

虚拟存储系统

对应用程序员是透明的。 目标:

扩大存储容量

主存储器

磁盘存储器

10

3. 主要性能指标

存储容量(S)(字节、千字节、兆字节等) 存取时间(T)(与系统命中率有关)

端的状态,仅当该端为高电平时才可写 入下一个字节。

P219例

73

四、闪速EEPROM

特点:

通过向内部控制寄存器写入命令的方法 来控制芯片的工作方式。

74

工作方式

数据读出

读单元内容 读内部状态寄存器内容 读芯片的厂家及器件标记

CAS:列地址选通信号。

地址总线上先送上行地址,后送上列地址,它们 分别在#RAS和#CAS有效期间被锁存在锁存器中。

WE:写允许信号

DIN: 数据输入

WE=0 WE=1

数据写入 数据读出

DOUT:数据输出

49

3. 2164在系统中的连接

与系统连接图

50

三、存储器扩展技术

51

1. 存储器扩展

1 A15 1 A14 1 A13

5第五章 应用指令及高功能指令简介

CP1H机型梯形图

CPM1A机型梯形图

2. MOVB和XFRB指令 和 指令

MOVB根据控制字C的控制,传送指定通道所指定的多个位到目的通道

例

XFRB指令是传送指定通道所指定的多个位 到目的通道

n: 传送位数

m:目的通道开始位 I:源通道开始位

例

3. MOVD和XFER指令 和 指令

例:使用一个按钮,接入0.00端,灯H1、H2、H3分别接入输

出端10.00、10.01、10.02。要求第一次按按钮,灯H1 亮, 再按一次按钮,灯H1、H2同时亮,第三次按按钮,三个灯 都亮,再按一次按钮,灯全灭,依次循环。

2. SFTR指令 指令

左右移位SFTR指令能将数据从低位移向高位,或反向移动。

第二节 数据传送指令

数据传送有: 数据传送有:

传送MOV 倍长传送MOVL 取反传送MVN 倍长取反传送MVNL 位传送MOVB 多位传送XFRB 数字传送MOVD 块传送XFER等。

上述指令在CPM1A和CP1H中基本一致。 上述指令在CPM1A和CP1H中基本一致。 CPM1A 中基本一致

1. MOV、MOVL和MVN、MVNL指令 、 和 、 指令

结果标志 符号地址 实际地址 实际地址 备注 CP1H CPM1A

> P_GT CF005 255.05

= P_EQ CF006, 255.06

< P_LT CF007 255.07

>= P_GE Cபைடு நூலகம்000

<> P_NE CF001

<= P_LE CF002

的数据大于5且小于 例: D1的数据大于 且小于 时,100.00有输出 的数据大于 且小于20时 有输出

汇编语言第5章作业答案

习题51.试说明以下指令中各操作数的寻址方式,如果是存储器寻址,请给出其EA计算公式,并说明所使用的段寄存器。

(1)MOV AL,08H 源操作数:立即数寻址目的操作数:寄存器寻址(2)MOV [0120H],BL 源操作数:寄存器寻址目的操作数:直接寻址,EA=0120H,使用DS段寄存器(3)ADD [BX],AL 源操作数:寄存器寻址目的操作数:寄存器间接寻址,EA=(BX),使用DS段寄存器(4)PUSH [SI]0200H 源操作数:变址寻址,EA=(SI)+0200H,使用DS段寄存器目的操作数:隐含寻址(指令中未直接体现)(5)SUB AX,[BP] 源操作数:寄存器间接寻址,EA=(BP),使用SS段寄存器目的操作数:寄存器寻址(6)AND V AR1+4,DL 源操作数:寄存器寻址目的操作数:直接寻址,EA=V AR1+4,使用DS段寄存器(7)PUSHF 源操作数、目的操作数均为隐含寻址(8)MOV ES : [BX]0100H, AL 源操作数:寄存器寻址目的操作数:基址寻址,EA=(BX)+0100H,用ES段寄存器(9)ADC BYTE PTR [BP][SI]0210H,45H源操作数:立即数寻址目的操作数:基址变址寻址,EA=(BP)+(SI)+0210H,使用SS段寄存器(10)OR ARRY[BX][DI],CL源操作数:寄存器寻址目的操作数:基址变址寻址,EA=(BX)+(DI)+ARRY,使用DS段寄存器2.试分析下列汇编指令是否存在语法错误,如果有语法错误存在,请说明是怎样的错误。

(1)PUSH 8243H错误,单操作数指令不能使用立即数(2)POP AL错误,进栈、出栈指令的操作数应为16位(3)MOV AL,6543H错误,源、目的操作数类型不匹配(4)ADD [0100H],64H错误,目的操作数应使用PTR运算符指出类型,否则具有二义性正确的写法:ADD BYTE PTR [0100H],64H,(或使用WORD PTR)(5)ADC V AR1,V AR2错误,8086指令系统的双操作数指令中,必须有一个是寄存器,不能两个操作数同为内存单元(6)MOV DS,ES错误,段寄存器间不能使用MOV指令直接传递数据,必须通过通用寄存器作为中转(7)MOV DS,0620H错误,使用MOV指令向段寄存器传递数据时,不能使用立即数(8)LEA BX,AX错误,L EA指令的源操作数必须为内存单元(9)DEC AL,AH错误,DEC指令为单操作数指令(10)SHR BL,3错误,当移位次数大于1时,在移位指令中特定使用CL寄存器给出移位次数正确的写法:MOV CL, 3SHR BL, CL3.试说明分别执行下列各组指令后,CF、OF、AF、ZF、SF、PF这六个状态标志分别是怎样的取值。

《单片机原理及应用》第5章 定时器及应用

计数工作方式

通过引脚T0(P3.4)和T1(P3.5)对外部脉冲信号计数。 当输入脉冲信号产生由1至0的下降沿时定时器的值加1。 CPU检测一个1至0的跳变需要两个机器周期,故最高计 数频率为振荡频率的1/24。 为了确保某个电平在变化之前被采样一次,要求电平保持 时间至少是一个完整的机器周期。 对输入脉冲信号的基本要求如图5-2所示。

外部事件

计数电路 时间单位脉冲 单片机 计数完成信号

5.2 89C51定时器概述

• 89C51有两个16位的定时器/计数器,即定时器0(T0)和 定时器1(T1)。它们实际上都是16位加1计数器。 • T0由两个8位特殊功能寄存器TH0和TL0构成;T1由TH1 和TL1构成。

• 每个定时器都可由软件设置为定时工作方式或计数工作方

• 例:当P3.4引脚上的电平发生负跳变时,从P1.0输出一个 500μs的同步脉冲。请编程序实现该功能。查询方式, fosc=6MHz。

解:(1)模式选择 选T0为模式2,外部事件计数方式。当P3.4引脚上的电平发生 负跳变时,T0计数器加1,溢出标志TF0置1;然后改变T0为 500μs定时工作方式,并使P1.0输出由1变为0。T0定时到产生 溢出,使P1.0输出恢复高电平,T0又恢复外部事件计数方式。

T0的低5位:01100B=0CH即(TL0)=0CH T0的高8位:11110000B=F0H即(TH0)=F0H

(2)计算最大定时时间T

T0的最大定时时间对应于初值为0. 则:T=213×1/6 × 10-6×12=16.384ms

例2:利用T0的工作模式0产生1ms定时,在P1.0引脚输出 周期为2ms的方波。设单片机晶振频率fosc=12MHz。编 程实现其功能。 解:要在P1.0引脚输出周期为2ms的方波,只要使P1.0每隔 1ms取反一次即可。 (1)选择工作模式 T0的模式字为TMOD=00H,即 M1M0=00,C/T=0,GATE=0,其余位为0。 (2)计算1ms定时时T0的初值

计算机组成原理第5章习题参考答案

第5 章习题参考答案第5 章习题参考答案1.请在括号内填入适当答案。

在CPU 中:(1)保存当前正在执行的指令的寄存器是(IR);(2)保存当前正在执行的指令地址的寄存器是(AR)(3)算术逻辑运算结果通常放在(DR)和(通用寄存器)。

2.参见图 5.15 的数据通路。

画出存数指令“ STO Rl, (R2)”的指令周期流程图,其含义是将寄存器Rl 的内容传送至(R2)为地址的主存单元中。

标出各微操作信号序列。

解:STO R1, (R2)的指令流程图及为操作信号序列如下:STO R1, (R2)(PC)→ARPC O, G, AR i(M) → DR R/W=R(DR) → IR DR O , G, IR i(R2) → AR R2O , G, AR i(R1) → DR R1O , G, DR i(DR) → M R/W=W~3.参见图 5.15 的数据通路,画出取数指令“LAD (R3),R0”的指令周期流程图,其含义是将 (R3)为地址主存单元的内容取至寄存器 R2 中,标出各微操作控制信号序列。

解:LAD R3, (R0) 的指令流程图及为操作信号序列如下:LAD (R3), R0(PC)→ AR PC O, G, AR i(M) → DR R/W=R(DR) → IR DR O , G, IR i(R3) → AR R3O , G, AR i(M) → DR R/W=R(DR) → R0DR O , G, R0i~4.假设主脉冲源频率为 10MHz,要求产生 5 个等间隔的节拍脉冲,试画出时序产生器的逻辑图。

解:5.如果在一个 CPU 周期中要产生 3 个节拍脉冲;T l=200ns,T2=400ns,T3=200ns,试画出时序产生器逻辑图。

解:取节拍脉冲 T l、 T2、T3的宽度为时钟周期或者是时钟周期的倍数即可。

所以取时钟源提供的时钟周期为 200ns,即,其频率为 5MHz. ;由于要输出 3 个节拍脉冲信号,而 T3的宽度为 2 个时钟周期,也就是一个节拍电位的时间是 4 个时钟周期,所以除了 C4外,还需要 3 个触发器—— C l、C2、C3;并令T1C 1C2;T1C 2C3;T3C1 C 3,由此可画出逻辑电路图如下:6.假设某机器有 80 条指令,平均每条指令由 4 条微指令组成,其中有一条取指微指令是所有指令公用的。

数字电子技术 第5章 时序逻辑电路的分析

40

5.8异步计数器

1.异步计数器的概念:异步计数器中的 触发器不会同时改变状态,因为它们没 有共同的时钟脉冲

41

2. 三位异步二进制计数器

42

波形图

Q0:2分频 Q1:4分频 Q2:8分频

Q0 Q1’ Q2

43

3.四位异步十进制计数器

1 CP 2 3 4 5 6 7 8 9 10

起译码 作用

电路分析: Di输入的数据,在cp 上升沿作用下,逐位 向左移动,经过4个 脉冲,将把输入的第 1个数传送到输出D0。

电压波形

34

5.5.MSI移位寄存器

M=0 M=1

串行输出

74LS95右移 移位寄存器

并 行 输 出

(1)电路形式:电路接成串行移位右移,并行输入,并行输出。 (2)工作原理:当方式控制M=1时,允许数据以并行方式输入,在cp2作用下,并 行存入J-K FF,并以并行方式输出Data.Q0~Q3。当M=0时,并行输入被禁止, 允许串行输入到J-K FF,在cp1作用下逐位右移。

1

1

1

1

4位异步二进制计数器(74LS93)

电路特点: 74LS93是一个MSI.模2×8进制计数器。从电路形式上看,第1 个FF为2进制,第2~4个FF是8进制计数器。采用两个时钟脉冲 CPA,CPB,有2个复位输入端,为方便灵活使用。

46

74LS93应用

用74LS93构成模16计数器。 将QA(第一级FF输出)作为CPB 使用,成为模16计数器。

(4)将驱动方程分别代入J-K FF的特性方程:

001 000 (2)时序电路的输出为Q3Q2Q1

(3)各FF的驱动方程: J1=Q3 K1=1 J2=1 K2=1 J3=Q2Q1 K3=1

第5章习题答案

习题51、中央处理器有哪些基本功能?由哪些基本部件组成?2、什么是指令周期、CPU周期和时钟脉冲周期?三者有何关系?3、参见图5.1所示的数据通路。

画出存数指令“STOI Rs,(Rd)”的指令周期流程图,其含义是将源寄存器Rs的内容传送至(Rd)为地址的主存单元中。

4、参见图5.13所示的数据通路。

画出取数指令“LDA (Rs),Rd”的指令周期流程图,其含义是将(Rs)为地址的主存单元的内容传送至目的寄存器Rd。

标出相应的微操作控制信号序列。

5、参见图5.15所示的数据通路。

画出加法指令“ADD Rd,(mem)”的指令周期流程图,其含义是将Rd中的数据与以mem为地址的主存单元的内容相加,结果传送至目的寄存器Rd。

6、假设CPU结构如图5.56所示,其中有一个累加寄存器AC、一个状态条件寄存器和其它4个寄存器,各部分之间的连线表示数据通路,箭头表示信息传送方向。

要求:(1)标明图中a、b、c、d这4个寄存器的名称;(2)简述指令从主存取出到产生控制信号的数据通路;(3)简述数据在运算器和主存之间进行存/取访问的数据通路。

图5.56 CPU结构图7、简述程序与微程序、指令与微指令的区别。

8、微命令有哪几种编码方法,它们是如何实现的?9、简述机器指令与微指令的关系。

10、某机的微指令格式中有10个独立的控制字段C0~C9,每个控制字段有Ni个互斥控制信号,Ni的值如下:请回答:(1)如果这10个控制字段,采用编码表示法,需要多少控制位?(2)如果采用完全水平型编码方式,需要多少控制位?11、假设微地址转移逻辑表达式如下:μA4=P2·ZF·T4μA3=P1·IR15·T4μA2=P1·IR14·T4μA1=P1·IR13·T4μA0=P1·IR12·T4其中μA4~μA0为微地址寄存器的相应位,P1和P2为判别标志,ZF为零标志,IR15~IR12为指令寄存器IR的相应位,T4为时钟脉冲信号。

《数字逻辑》第5章作业与习题

二、习题

1)填空题

1.在数字系统中,用二进制代码表示特定对象的过程称为

;n

位二进制编码器有 个输入,有 个输出。

2.将十进制数的十个数字编成二进制代码的过程叫做

。

个。

8.输出高电平有效的 4 线-16 线译码器的输入 A3~A0=1010 时,输出 Y15~

Y0=

。

9.全加器与半加器的区别是

。

10.当输入信号改变状态时,输出端可能出现虚假过渡干扰脉冲的现象叫做

。

2)单选题

1.在二进制译码器中,若输入有 4 位代码,则输出最多有( )信号。

①2个

②4个

③8个

④ 16 个

5.能实现从多个输入端中选出一路作为输出的电路称为( )。

① 触发器

②计数器

③ 数据选择器 ④ 译码器

6.把代码所表示的特定含义翻译出来的过程称为( )。

① 译码

② 编码

③ 数据选择 ④ 奇偶校验

7.用输出高电平有效的译码器实现组合逻辑电路时,还需或门

8.用输出低电平有效的译码器实现组合逻辑电路时,还需要( )。

① 与非门 ② 或非门 ③ 与门

④ 或门

9.半导体数码管的每个显示线段都是由( )构成的。

① 灯丝 ② 发光二极管 ③ 发光三极管 ④ 熔丝

3)问答与设计题

1. 组合逻辑电路在功能和电路组成上各有什么特点?

4

2. 二进制编码器和优先编码器各有何特点?优先编码器适于什么场合?试 举例说明。

3. 什么是数据选择器?数据选择器有什么功能和用途? 4. 什么是译码器?二进制译码器有哪些特点和用途? 5. 什么是奇偶校验器?奇偶校验器有什么功能和用途? 6. 常用的组合逻辑集成部件包括哪些类型? 7. 分析教材 P134 图 4.64 所示电路的逻辑功能,写出 Y1、Y2 的函数表达 式,列出真值表,并指出电路完成什么功能。 8. 用 Verilog HDL 设计 1 位全减器电路,设 X、Y、BI 分别为被减数、减 数、来自低位的借位,DO、BO 分别为差、向高位的借位。 9. 采用 function 块语句设计高电平有效的 8 线-3 线编码器,然后用函数调 用的方法实现此编码器电路。假设输入信号为 din[7:0],输出信号为 dout[2:0]。 10. 用 Verilog HDL 设计输出为低电平有效的 2 线-4 线译码器电路,使能信 号为低电平有效。 11. 分别用 assign 语句和 always 块中的赋值语句设计一个 4 位二进制数的加 /减运算电路。当控制信号 M=0 时进行加法运算,而 M=1 时进行减法运算。注 意加法运算时要考虑来自低位的进位输入和向高位的进位输出,减法运算时要考 虑来自低位的借位和向高位的借位。采用这两种语句赋值时,对变量的类型各有 什么要求? 12. 用 Verilog HDL 设计将余 3BCD 码转换成 8421BCD 码的码转换电路。 13. 分析下面 Verilog HDL 源程序,说明程序描述电路的功能。

计导-课后习题参考答案(第5章

第5章计算机组成一、复习题1.计算机由哪三个子系统组成?答:计算机由中央处理单元、主存储器和输入/输出子系统组成。

2.CPU又哪几个部分组成?答:;CPU由算术逻辑单元(ALU)、控制单元和寄存器组成。

3.ALU的功能是什么?答:ALU(即算术逻辑单元)用于算术运算和逻辑运算。

4.描述一下几种不同的寄存器。

答:寄存器是用来临时存放数据的高速独立的存储单元。

寄存器有三种:数据寄存器、指令寄存器和程序计数器。

其功能如下:①数据寄存器:数据寄存器用来保存复杂运算的中间结果,可以提高运算速度。

②指令寄存器:指令寄存器存储CPU从内存中逐条取出的指令,解释并执行指令。

③程序计数器:程序计数器保存当前正在执行的指令,当前的指令执行完后,计数器自动加1,指向下一条指令的地址。

5.控制单元的功能是什么?答:控制单元控制各部件协调工作,对取到指令寄存器中的指令进行译码并产生控制信号以完成操作。

控制通过线路的开(高电平)或关(低电平)来实现。

6.字和字节有什么区别?答:数据是以称之为字的位组的形式在存储器中传入和传出。

字就是指执行一条指令时可以处理的二进制数位数。

不同的机器字可以取8位、16位、32位,甚至是64位。

而字节是指8位二进制位。

7.主存的功能是什么?答:主存是存储单元的集合,用于临时存储数据和程序。

8.兆字节的近似值和实际值的字节数如何对应?答:其实际值是220字节,近似值是106字节。

9.存储地址用哪种数的表示法表示?答:地址本身也使用位模式表示,通常用无符号二进制整数表示。

10.RAM和ROM有何区别?答:RAM是随机存取存储器,是主存的主要组成部分。

具有可随机读写、易失性的特点。

ROM是只读存储器,具有只读、非易失性特点。

11.SRAM和DRAM有何区别?答:SRAM技术使用传统的触发器门电路,通电时数据始终存在,不需要刷新,速度快但价格昂贵;DRAM技术使用电容器,内存单元需要周期性地刷新(因为漏电),速度慢,但是便宜。

组成原理第5章

第5章计算机组成原理课程设计在上一章中,我们详细地介绍了计算组成原理课程设计平台系统,知道了在模式开关的控制下有两种不同的工作平台。

《计算机组成原理》的所有课程设计都将在这两种工作模式下完满的得到实施。

一个完整的课程设计可以用多种形式来描述。

例如,一个简单的设计可能用硬件描述语言来描述就够了。

但一个复杂的设计可能要分成若干个功能模块来描述,而其中的每一个功能模块可能用硬件描述语言来描述,也可能用原理图来描述,这样的描述方式就是混合输入的设计方法。

结合《计算机组成原理》课程设计的特点和学生的实际情况,原理图输入方式最适合课程设计的实施。

以此为基点,《计算机组成原理》课程设计的步骤如图5-1所示。

课程设计共分三个阶段:1、设计初始阶段在该阶段中,学生根据所学内容,按照《计算机组成原理》课程设计的要求,在课程设计报告书中完成方案设计并画出逻辑线路图。

2、编程设计阶段在该阶段中,学生将以PC机为平台,在WINDOWS环境下,利用编程软件系统在PC机上生成所画出的逻辑线路,这就是所谓的原理图输入方式。

在逻辑线路的生成过程中,可调用元件库提供的元件(例算术逻辑部件、多路开关、寄存器、译码器、逻辑门等),也可以自定义元件。

这与常规《计算机组成原理》课程设计相比较,充分地体现了设计的灵活性,满足了学生的灵活设计思路,是对设计能力的最好体现。

当原理图输入完毕后,编程软件系统可对原理图文件进行编译、优化、适配,将错误消灭在设计阶段。

最后生成对isp LSI的编程文件。

3、isp LSI编程和测试阶段当一个设计完成且产生编程文件后,就可以对isp LSI进行编程。

对isp LSI的编程是由编程软件系统中的下载软件驱动的。

对ispLSI编程与测试阶段图5-1 课程设计步骤下载结束后,逻辑线路就固化在isp LSI1032E中,在模式开关的控制下选用不同的平台,利用提供的开关、指示灯、存储器等硬件资源对逻辑线路进行功能测试,若有错误,则通过审查、修改原理图文件、重新下载、重新测试直至成功为止。

数电课件第五章锁存器和触发器

不同类型的触发器具有不同的工 作特性和应用场景,可以根据实 际需求选择合适的触发器类型。

03 锁存器和触发器的应用

在时序逻辑电路中的应用

存储数据

锁存器和触发器可以用于存储数 据,在时序逻辑电路中作为寄存 器使用,保存数据以便后续处理。

控制信号

锁存器和触发器可以用于控制信号 的传递,在时序逻辑电路中作为控 制门使用,根据输入信号的变化来 控制输出信号的输出。

数电课件第五章锁存器和触发器

目录

• 锁存器概述 • 触发器概述 • 锁存器和触发器的应用 • 锁存器和触发器的实例分析 • 总结与展望

01 锁存器概述

定义与特点

01

02

定义:锁存器是一种具 特点 有存储功能的电路,能 在特定条件下保存数据, 即使在电源关闭或电路 其他部分出现故障的情 况下也能保持数据的完 整性。

分析

通过仿真验证了74HC74的触发器功能,并对其工作原理有了更深入的理解。

05 总结与展望

锁存器和触发器的重要性和应用价值

锁存器和触发器是数字电路中的基本元件,在时序逻辑电路和组合逻辑 电路中有着广泛的应用。

锁存器能够存储二进制数据,在数字系统中起到数据存储和传输的作用; 触发器则能够记忆二进制数据的状态,常用于实现时序逻辑电路如计数 器和寄存器等。

03

04

05

具有记忆功能,能够保 存前一个状态;

在时钟信号的驱动下, 通常由逻辑门电路构成, 完成数据的存储和读取; 如与门、或门和非门等。

工作原理

在时钟信号的控制下,锁存器在数据输入端接收数据,并在数据输出端输出数据。

当时钟信号处于低电平状态时,锁存器处于关闭状态,无法接收新的数据输入。

微机原理及接口技术课件第5章 存储器

引脚号

2764

27128

27256

27512

引脚号

2764

27128

27256

27512

1

VPP

VPP

VPP

A15

15

D3

D3

D3

D3

2

A12

A12

A12

A12

16

D4

D4

D4

D4

3

A7

A7

A7

A7

17

D5

D5

D5

D5

4

A6

A6

A6

A6

18

D6

D6

D6

D6

5

A5

A5

A5

A5

19

D7

D7

D7

D7

6

A4

例如:6264静态RAM的容量为8K x 8bit NMC41257的容量为256K x 1bit

某一芯片有多少个存储单元,每个存储单元存储若干位,由于其数值一般 都比较大,存储容量常以字节(Byte)表示。因此常以K表示210,以M表示 220,G表示230。如256KB等于256×210×8bit,32MB等于32×220×8bit。

A4

行 译

存储器阵列

VCC

…

…

码

128x128

GND

A10

WE

I/O1

…

…

…

输入数 据控制

列I/O 列译码

OE

I/O8

CE

…

… …

…

CE

1

WE

0 0

& 0

A0A1A2A3

0

EDA技术第5章

利用EDA工具进

行仿真和验证

状态机一般由三个模块构成:状态寄存器、次态逻辑和输出逻辑。

在使用VHDL描述状态机时,通常从状态机的三个基本模块入手,可分为:

(1)单进程(一段式)

将整个状态机的三个模块合并起来,写到一个进程里面,在该进程中既描述状

态转移,又描述状态的输入和输出。

(2)两进程(二段式)

(2)条件(事件、输入信号):当条件被满足,会执行状态的迁移。

(3)动作(操作、输出控制信号):条件满足后执行的动作。

(4)次态(下一个状态):条件满足后要迁移的新状态。

有限状态机分类

(1)根据状态迁移是否受时钟控制:同步有限状态机 & 异步有限状态机

(2)隐式有限状态机 & 显式有限状态机

(3)根据状态机的信号输出方式:摩尔(Moore)型 & 米勒(Mealy)型

IF rst =‘1’ THEN

Z <= ‘1’ ;

END IF;

current_state <= S1;

WHEN S3 =>

END CASE;

ELSE

Z <= ‘0’ ;

END PROCESS;

current_state <= next_state;

END CASE;

END IF;

END PROCESS;

(4)运行速度块,比CPU高出近两个数量级,在高速运算和控制方面有优势;

(5)可靠性高。如复位时间、与CPU相比,复位时间短很多。

由状态机构成的硬件系统广泛应用在一般CPU无法胜任的领域,如超高速

串行或并行AD、DA的控制,硬件串行通信接口RS232、PS/2、USB的实现

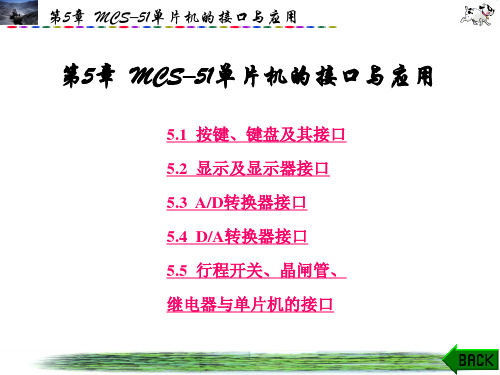

第5章 MCS–51单片机的接口与应用 99页 5.8M

(1) 用键盘连接的I/O线的二进制组合表示键码。例如用4行、

4列线构成的16个键的键盘,可使用一个8位I/O口线的高、低4 位口线的二进制数的组合表示16个键的编码,如图5.4(a)所示。 各键相应的键值为88H、84H、82H、81H、48H、44H、42H、 41H、28H、24H、22H、21H、18H、14H、12H、11H。这种键 值编码软件较为简单直观,但离散性大,不便安排散转程序的 入口地址。

第5章 MCS–51单片机的接口与应用 JNB ACC.2,K2 JNB ACC.3,K3 JNB ACC.4,K4 JNB ACC.5,K5 JNB ACC.6,K6 ;检测2号键是否按下,按下转 ;检测3号键是否按下,按下转 ;检测4号键是否按下,按下转 ;检测5号键是否按下,按下转 ;检测6号键是否按下,按下转

;0号键功能程序

;0号键功能程序执行完返回 ;0号键功能程序

JMP START

……………………… PROM7: ……………………… JMP START …

;1号键功能程序执行完返回

;7号键功能程序 ;7号键功能程序执行完返回

第5章 MCS–51单片机的接口与应用

5.1.4 行列式键盘

行列式键盘又叫矩阵式键盘。用I/O口线组成行、列结构, 按键设置在行列的交点上。例如4×4的行列结构可组成16个键 的键盘。因此,在按键数量较多时,可以节省I/O口线。 1.行列式键盘的接口 行列式键盘的接口方法有许多,例如直接接口于单片机的 I/O口上;利用扩展的并行I/O接口;用串行口扩展并行I/O口接 口;利用一种可编程的键盘、显示接口芯片8279进行接口等。 其中,利用扩展的并行I/O接口方法方便灵活,在单片机应用系

MOVX @DPTR,A

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数据对象

VHDL中凡是可以赋予一个值的对象都可称为数据对象。

数据对象有3类,即信号(SIGNAL)、变量(VARIABLE)和常量 (CONSTANT)。

在VHDL中,被定义的标识符必须确定为某类数据对象,同时还必 须被定义为某种数据类型。

1

常量(Constant)说明

为一个常数名赋予一个固定的值,通常在程序开始前进行。 格式:CONSTANT 常数名:数据类型:=表达式 1、CONSTANT vcc:REAL:=5.0 2、CONSTANT daly :TIME:=100us 3、TYPE mem IS ARRAY (0 TO 2,7 DOWNTTO 0)OF STD_LOGIC;

VHDL描述的语言现象说明

4. 上升沿检测表式和信号属性函数EVENT

clk„EVENT

当0--1 或者 1 --0 其值为布尔值true,否则为false

clk„EVENT 表示clk有一个跳变 and clk=‟1„, 变后又测得clk为高电平'1„

两者相与(AND)后返回值为true 对信号clk的上升沿进行检测

格式:SIGNAL 信号名:数据类型 约束条件 表达式;

例:SIGNAL count :STD_LOGIC_VECTOR (3 DOWNTO 0)

ARCHITECTURE arc OF mux21a IS signal d,e:BIT; BEGIN d<= a AND (NOT s); e<= b AND s; y <= d OR e; END ARCHITECTURE arc ;

5. 不完整条件语句与时序电路

图4-5 例4-7的电路图(Synplify综合)

5. 不完整条件语句与时序电路 【例4-8】 ... IF a1 > b1 THEN q1 <= '1' ; ELSE q1 <= '0' ; END IF; ...

图4-6 例4-8的电路图(Synplify综合)

STD_LOGIC_ARITH

STD_LOGIC_UNSIGNED 由STD-LOGIC_VECTOR转换为INTEGER

STD_LOGIC与STD _LOGIC _VECTOR数据类型是VHDL语法以 外添加的数据类型,属于用户自定义数据类型。 由于经常使用,把常用数据类型放在一个库里。每个库包含多个包, 每个包又包含多个函数、过程、数据类型定义、信号定义、常数定 义、元件定义语句等。 STD_LOGIC与STD _LOGIC _VECTOR就包含在IEEE库的STD _LOGIC _1164包集合中。 实体说明前,最常用的说明语句为: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; VHDL标准中规定标准库STD和工作库WORK是默认打开的,而 IEEE没有。

VHDL描述的语言现象说明

4. 上升沿检测表式和信号属性函数EVENT

如果clk的数据类型定义为STD_LOGIC,则在 时间段内,clk 从其数据类型允许的9种值中的任何一个值向另一值跳变,如由 ‘0‟变成‘1‟、由‘1‟变成‘0‟或由‘Z‟变成‘0‟,都认为发生了 事件 虽然STD_LOGIC一般只有‘0‟和‘1‟

5. 不完整条件语句与时序电路

【例4-7】 ENTITY COMP_BAD IS PORT( a1,b1 : IN BIT; q1 : OUT BIT ); END ; ARCHITECTURE one OF COMP_BAD IS BEGIN PROCESS (a1,b1) BEGIN IF a1 > b1 THEN q1 <= '1' ; ELSIF a1 < b1 THEN q1 <= '0' ;-- 未提及当a1=b1时,q1作何操作 END IF; END PROCESS ; END ;

《CPLD与FPGA的应用》

第5章 寄存器设计应用

寄存器描述的VHDL程序

D触发器的描述

图4-4 D触发器

寄存器描述的VHDL程序

【例】 有Q1过渡,Q不用 LIBRARY IEEE ; BUFFER类型 USE IEEE.STD_LOGIC_1164.ALL ; ENTITY DFF1 IS PORT (CLK : IN STD_LOGIC ; BUFFER D : IN STD_LOGIC ; D Q Q : OUT STD_LOGIC ); END ; CLK ARCHITECTURE bhv OF DFF1 IS SIGNAL Q1 : STD_LOGIC ; --类似于在芯片内部定义一个数据的暂存节点 BEGIN Q1 PROCESS (CLK,Q1) (双横 OUT BEGIN D Q IF CLK'EVENT AND CLK = '1' 线--是 注释符 THEN Q1 <= D ; CLK 号) END IF; END PROCESS ; Q <= Q1 ; --将内部的暂存数据向端口输出 END bhv;

VHDL描述的语言现象说明

上升沿检测表式和信号属性函数EVENT

CLK„EVEN词EVENT是信号属性函数,用来获得信号行为信息的函数称 为信号属性函数 <信号名>'EVENT “clk'EVENT”就是对clk标识符的信号在当前的一个极小的时间段 内发生事件的情况进行检测。所谓发生事件,就是clock在其数据类 型的取值范围内发生变化,从一种取值转变到另一种取值(或电平方 式)。

CONSTANT romdata :mem:=((„0‟,„0‟,‟,„0‟,„0‟,„0‟,„0‟,„0‟,„0‟), („0‟,„1‟,‟,„1‟,„1‟,„0‟,„0‟,„0‟,„1‟), („1‟,„1‟,‟,„1‟,„1‟,„1‟,„1‟,„1‟,„1‟));

2

变量(Variable)说明

实现时序电路的不同表述

【例】 ... PROCESS (CLK) BEGIN IF CLK'EVENT AND (CLK='1') AND (CLK'LAST_VALUE='0') THEN Q <= D ; --确保CLK的变化是一次上升沿的跳变 END IF; END PROCESS ;

实现时序电路的不同表述

VHDL描述的语言现象说明

3. 信号定义和数据对象

信号定义

SIGNAL Q1:STD_LOGIC; 表示在描述的器件DFF1内部定义标识符Q1的数据对象为 信号SIGNAL,其数据类型为STD_LOGIC。 由于Q1被定义为器件的内部节点信号,数据的进出不像 端口信号那样受限制,所以不必定义其端口模式(如IN、OUT 等)。 定义Q1的目的是为了在设计更大的电路时使用由此引入 的时序电路的信号,这是一种常用的时序电路设计的方式。 有Q1过渡,Q不用BUFFER类型。

VHDL描述的语言现象说明 1. 标准逻辑位数据类型STD_LOGIC

BIT数据类型定义: TYPE BIT IS('0','1'); --只有两种取值 STD_LOGIC数据类型定义:

TYPE STD_LOGIC IS ('U','X','0','1','Z','W','L','H','-');

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY bcdadder IS

PORT (op1,op2:IN integer RANGE 0 TO 9;

result :OUT integer RANGE 0 to 31 ); END bcdadder; 定义一个常量,整 数型,值为6

USE 库名.程序包名.ALL;

LIBRARY <设计库名>; USE < 设计库名>.<程序包名>.ALL ; LIBRARY WORK ; LIBRARY STD ; USE STD.STANDARD.ALL ;

常用预定义程序包有以下四个: (1)STD_LOGIC_1164程序包 (2)STD_LOGIC_ARITH程序包 (3)STD_LOGIC_SIGNED程序包 (4)STD_LOGIC_UNSIGNED程序包

‟LAST_VALUE 信号属性函数,它表示最近一次事件发生前的值。

CLK„EVENT

AND

CLK=‟1„ AND CLK‟LAST_VALUE=„0‟

保证了CLK在 时刻内的跳变确实是从'0'变到'1'的。

CLK„EVENT

AND

CLK=‟0„ AND CLK‟LAST_VALUE=„1‟

保证了CLK在 时刻内的跳变确实是从‘1'变到‘0'的。

库

库是专门用于存放预先编译好的程序包的地方,对应一个文件目录, 程序包的文件就放在此目录中,其功能相当于共享资源的仓库,所有已 完成的设计资源只有存入某个“库”内才可以被其他实体共享。常用的 库有IEEE库、STD库和WORK库。

LIBRARY 库名 ;

程序包

程序包是用VHDL语言编写的一段程序,可以供其他设计单元调用 和共享,相当于公用的“工具箱”,各种数据类型、子程序等一旦放入 了程序包,就成为共享的“工具”,类似于C语言的头文件,使用它可 以减少代码的输入量,使程序结构清晰。程序包分为包头和包体两部分。

BEGIN IF bin>9 THEN tmp:=adj; ELSE tmp:=0; END IF; result<= bin+tmp; END PROCESS;