Chapter 2 VHDL Models

VHDL-2章

2.3.2 实体说明 实体说明是1个设计实体的外部视图,它 包括实体名称、类属说明和端口说明等信息。 实体说明的一般格式如下: ENTITY 实体名称 IS [ GENERIC GENERIC(类属表);] [ PORT PORT(端口表);] [ BEGIN { 实体语句 }] END [ ENTITY ][ 实体名称 ];

2.2

1位全加器的描述实例 1位全加器的描述实例

1位全加器有3个输入端a、b、 c_in和2个输出端sum、c_out,如图 2.1a所示;它是由2个半加器和1个 或门构成,如图2.1b所示;图2.1c 是1位全加器的逻辑图。

a b c_in

全加器

sum c_out

a b

U1 半加器

temp_sum

2.3 基本的VHDL模型结构 基本的VHDL模型结构

2.3.1 设计实体 设计实体是VHDL中的基本单元和最重要的 抽象,它把一个任意复杂程度的模块视为一个 单元,它可以代表整个系统、1块电路板、1个 芯片或者是1个门电路,它可以复杂到象一个 微处理器,也可以简单到一个逻辑门。1个设 计实体由1个实体说明和若干个结构体组成。 实体说明是设计实体的接口部分,它表示设计 实体对外部的特征信息;结构体是设计实体的 实现方案描述。1个设计实体中的若干个结构 体,分别代表同一实体说明的不同实现方案。

第2章 硬件描述语言VHDL基本概念 硬件描述语言VHDL基本概念 在比较传统的数字系统设计中,描 述硬件的方法通常是逻辑电路图和逻辑 表达式(布尔方程),随着系统复杂程 度的增加,上述描述方法变得过于复杂, 不便于使用。为了能够在更高层次上描 述硬件,人们从20世纪60年代起就不断 提出硬件描述语言(HDL),但其中绝 大部分是专有产品而不是标准化产品。 目前已经标准化的HDL主要有VHDL和 Verilog HDL。

VHDL入门教程

VHDL入门教程VHDL(Very High-speed Integrated Circuit HardwareDescription Language)是一种用于设计数字电路的硬件描述语言。

它是IEEE 1076标准中规定的一种语言,广泛应用于数字电路的设计、仿真和综合等领域。

本文将为大家介绍VHDL的基础知识和入门教程。

一、VHDL的基本概念1. 实体(Entity):VHDL代码的最高层次,用于定义模块的输入、输出和内部信号。

2. 架构(Architecture):定义了实体中的各个信号和组合逻辑的行为。

3. 信号(Signal):表示数据在电路中的传输和操作。

4. 进程(Process):定义了组合逻辑的行为,用于描述信号之间的关系。

5. 实体声明(Entity Declaration):用于描述模块的名称、输入、输出和内部信号。

6. 架构声明(Architecture Declaration):用于描述模块的内部逻辑。

二、VHDL的基本语法1.实体声明语法:```entity entity_name isport ( port_list );end entity_name;```其中,entity_name是实体的名称,port_list是实体的输入、输出和内部信号。

2.架构声明语法:```architecture architecture_name of entity_name issignal signal_list;beginprocess (sensitivity_list)begin--逻辑行为描述end process;end architecture_name;```其中,architecture_name是架构的名称,entity_name是实体的名称,signal_list是架构的内部信号,sensitivity_list是触发事件的信号列表。

三、VHDL的基本例子下面以一个简单的4位加法器为例介绍VHDL的编写和仿真流程。

《VHDL语言教程》课件

VHDL语言的应用领域和实际案例

通信系统

用于设计编码器、解码器、协议处理和通信接 口。

嵌入式系统

用于设计嵌入式控制器、传感器接口和外设控 制。

图像处理

用于设计数字图像滤波、边缘检测和图像压缩 算法。

自动驾驶

用于设计数字信号处理、传感器融合和控制算 法。

VHDL语言的未来发展和趋势

VHDL语言将继续发展,以适应新兴技术和需求,如人工智能、物联网和边缘计算。

总结和课程建议

通过本课程,您将掌握VHDL语言的基础知识和应用技巧,为您在

1 实体(Entity)

定义模块的接口和名称。

2 体(Architecture)

描述模块的行为和内部结构。

3 过程(Process)

4 信号(Signal)

定义模块基于输入信号做出相应输出的操作。

用于在模块之间传递数据。

VHDL语言的模拟器和仿真工具

模拟器

用于测试和验证设计的正确性和 功能。

波形仿真

可视化信号波形,以便分析和调 试。

调试工具

帮助定位设计中的错误和问题。

VHDL语言的硬件描述和设计方法

1

结构化设计

将设计分解为可重用的模块,提高灵活

行为级建模

2

性和可维护性。

使用过程描述模块的行为和操作。

3

数据流建模

使用信号和变量描述模块的数据流和计

引导配置

4

算过程。

定义模块间的连接和信号传递关系。

《VHDL语言教程》PPT课 件

欢迎来到《VHDL语言教程》PPT课件,让我们一起探索VHDL语言的定义、历 史背景以及它在数字电路设计中的重要性。

什么是VHDL语言?

vhdl 2

四、文件(1) 文件的定义:实体中用来传输大量数据的一种载体 对象,它是VHDL-93标准新通过的。 物理意义:无。 书写格式:

FILE 文件名 [,文件名…] :文件类型 IS [方向] 路径表达式;

文件类型的定义格式:

TYPE 文件类型名 IS FILE OF 数据类型;

文件说明的小例子:

四、文件(2)

二、用户定义的数据类型(1) 优点:为程序编写提供了自由度和灵活性。 遵循原则:先定义、后使用。 可枚举类型 1、作用:设计中方便数字逻辑的表示。 2、定义格式:

TYPE 枚举数据类型名 IS (枚举元素,枚举元素,…);

3、枚举类型举例:

TYPE boolean IS (false,true); TYPE bit IS (’0’,’1’); TYPE week IS (mon,tue,wed,thur,fri,sat,sun);

三、变量(2) 变量说明时可以不用赋初始值。这时它将取系统 默认值,即所属数据类型的最小值或者最左值。 变量使用的注意事项: a、初始赋值符号和程序中赋值符号均为“:= ”; b、变量所赋的值应与定义的数据类型一致; c、变量的定义和作用范围仅限于进程和子程序; d、变量的赋值是直接的、立即生效的,因此变量 赋值语句中不允许出现附加延迟。 如何将一个变量的值带出它的作用范围?

五、信号和变量的区别(2) P1: PROCESS VARIABLE a,b : integer; BEGIN WAIT UNTIL clk = ’1’; a : = 10; b : = 20; a : = b; b : = a; END PROCESS;

五、信号和变量的区别(3) SIGNAL a,b : integer; P2: PROCESS BEGIN a <= 10; b <= 20; WAIT FOR 10 ns; a <= b; b <= a; WAIT FOR 10 ns; END PROCESS;

vhdl课后习题答案

vhdl课后习题答案VHDL课后习题答案在学习VHDL(VHSIC Hardware Description Language)这门课程时,课后习题是巩固知识、提高能力的重要方式。

通过认真完成课后习题并查看答案,我们可以更好地理解和掌握VHDL的相关知识,提高自己的编程能力。

下面我们将通过几个典型的VHDL课后习题答案来展示VHDL的魅力和应用。

1. 课后习题一题目:使用VHDL编写一个简单的门电路,包括AND门、OR门和NOT门,并进行仿真验证。

答案:首先,我们定义AND门、OR门和NOT门的输入输出信号。

然后,使用VHDL语言编写各个门电路的逻辑实现,并进行仿真验证。

最后,我们可以观察仿真波形图,验证门电路的功能是否符合预期。

2. 课后习题二题目:使用VHDL编写一个4位全加器,并进行综合、布线和时序分析。

答案:首先,我们定义全加器的输入输出信号。

然后,使用VHDL语言编写4位全加器的逻辑实现,并进行综合、布线和时序分析。

最后,我们可以观察综合和布线报告,分析全加器的资源利用情况和时序性能。

3. 课后习题三题目:使用VHDL编写一个有限状态机(FSM),实现一个简单的计数器,并进行状态转移图和状态转移表的分析。

答案:首先,我们定义有限状态机的状态和状态转移条件。

然后,使用VHDL 语言编写有限状态机的逻辑实现,并进行状态转移图和状态转移表的分析。

最后,我们可以观察状态转移图和状态转移表,验证有限状态机的状态转移是否符合预期。

通过以上几个VHDL课后习题答案的展示,我们可以看到VHDL在数字电路设计和硬件描述方面的强大应用。

通过学习VHDL并完成课后习题,我们可以提高自己的编程能力,掌握数字电路设计的基本原理和方法。

希望大家在学习VHDL的过程中能够认真完成课后习题,并不断提高自己的编程水平。

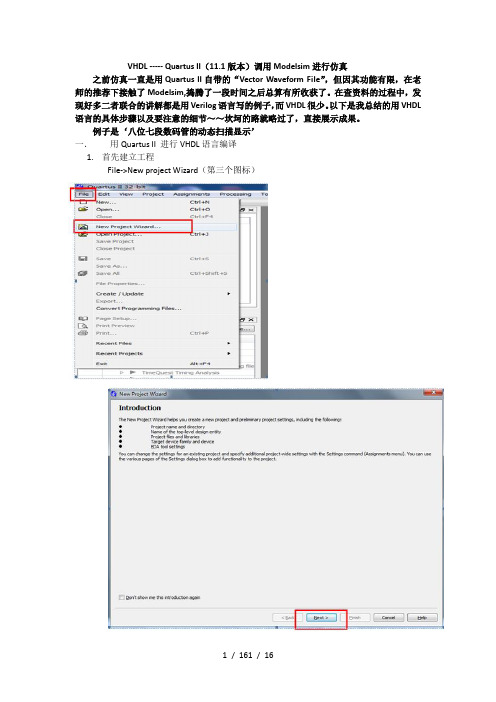

VHDLQuartusII调用Modelsim进行仿真

VHDL ----- Quartus II(11.1版本)调用Modelsim进行仿真之前仿真一直是用Quartus II自带的“Vector Waveform File”,但因其功能有限,在老师的推荐下接触了Modelsim,捣腾了一段时间之后总算有所收获了。

在查资料的过程中,发现好多二者联合的讲解都是用Verilog语言写的例子,而VHDL很少。

以下是我总结的用VHDL 语言的具体步骤以及要注意的细节~~坎坷的路就略过了,直接展示成果。

例子是‘八位七段数码管的动态扫描显示’一.用Quartus II 进行VHDL语言编译1.首先建立工程File->New project Wizard(第三个图标)填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish,然后单击yes。

2.新建VHDL源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法)注意:程序中的实体名必须和之前建工程时所命名的文件名相同!然后保存一下,不用改动,直接单击保存。

3.编译快捷键按钮在界面中上方的红色倒三角,显示编译成功之后关闭编译报告。

4.设备设置具体的实验器件根据提供的实验板设定Assignment->Device4.引脚分配Assignment->Pin Planner在Location下的方格中填入对应的硬件引脚,也是根据实验板而定6.引脚分配好之后再次编译一下,使分配的引脚起作用。

一、调用Modelsim1、设置仿真工具为Modelsim-alteraTool->Options->EDA Tool Options,在Modelsim-Altera后面的地址改为Modelsim-Altera.exe在你电脑中的位置,然后点击OK。

2、写TestBench文件,这里使用Quartus II生成的模板Processing->start->Start TestBench Template Writer,显示成功后关闭生成报告。

VHDL_第1-2章

6

Ruan Jun

WUHAN UNIVERSITY OF TECHNOLOGY

Chapter 1 Introduction

• 1.1 Modern digital design

– Digital electronics is ever more significant in consumer good. Products that used to be thought of as analogue, such as radio, television and telephones, are or are becoming digital. – The lifetimes of products have lessened. In a period of less than a year, new models will probably have replaced all the digital electronic products in your local store.

Ruan Jun

WUHAN UNIVERSITY OF TECHNOLOGY

Ruan Jun

WUHAN UNIVERSITY OF TECHNOLOGY

ruanjun@

4

What will you gain from this course ??

• Learning a new language VHDL • Learning CAD tools • Designing and simulating hardware units, such as adders, multipliers, and so forth. • Understanding inner details of processors • Designing processors of your own

VHDL课件第2章.

第2章 大规模可编程逻辑器件

采用ISP技术之后,硬件设计可以变得像软件设计那样灵活 而易于修改,硬件的功能也可以实时地加以更新或按预定的 程序改变配置。这不仅扩展了器件的用途,缩短了系统的设 计和调试周期,而且还省去了对器件单独编程的环节,因而 也省去了器件编程设备,简化了目标系统的现场升级和维护 工作。

第2章 大规模可编程逻辑器件

在20世纪90年代初,Lattice公司又推出了在系统可编程 大规模集成电路(ispLSI)。所谓“在系统可编程特性”(In System Programmability,缩写为ISP),是指在用户自己设计 的目标系统中或线路板上,为重新构造设计逻辑而对器件进 行编程或反复编程的能力。在系统编程器件的基本特征是利 用器件的工作电压(一般为5 V),在器件安装到系统板上后, 不需要将器件从电路板上卸下,可对器件进行直接配置,并 可改变器件内的设计逻辑,满足原有的PCB布局要求。

第2章 大规模可编程逻辑器件

2.1 可编程逻辑器件概述

可编程逻辑器件(Programmable Logic Devices,简称 PLD)是一种由用户编程以实现某种逻辑功能的新型逻辑器 件。它诞生于20世纪70年代,在20世纪80年代以后,随着集 成电路技术和计算机技术的发展而迅速发展。自问世以来, PLD经历了从PROM、PLA、PAL、GAL到FPGA、ispLSI等 高密度PLD的发展过程。在此期间,PLD的集成度、速度不 断提高,功能不断增强,结构趋于更合理,使用变得更灵活 方便。

第二部分 VHDL的模型

entity)

实体的组成:实体名、类属表、端口表、实体说明部 分、实体语句等部分。

根据IEEE标准,实体的一般格式为:

ENTITY 实体名 IS [GENERIC (类属表);] PORT (端口表); END 实体名;

2013-7-14

卢庆莉 编写

一、类属(GENERIC)

属类说明是实体中的可选项,放在端口之前, 其一般书写格式为:-----说明类属在可编程器件 的开发工具中一般都不支持,只有在EDA的工具 中才支持。 GENERIC [CONSTANT] 名字表 : [IN] 子类型标识 [ := 静态表达式 ,…..]

bit_vector (1 to n);

bit);

End

and_gate;

2013-7-14

卢庆莉 编写

2.1.2 结构体(ARCHITECTURE)

用VHDL语言描述结构体功能有三种方法: (1)行为描述法:以算法的形式来描述数据 变换。 (2)数据流描述法:是按照数据流动的方向 来进行描述的。 (3)结构描述法:是按照逻辑元件的连接进 行描述的。

一个通信模式;

一个数据类型。 端口说明一般格式:

PORT (端口名,端口名 :模式数据类型名; … 端口名,端口名 : 模式数据类型名);

2013-7-14 卢庆莉 编写

1、端口名

端口名是赋于每个外部引脚的名字,名字的 含义要与惯例接轨,例如:D开头的端口名表示数 据;A开头的端口名表示地址等。端口名通常用几 个英文字母或一个英文字母加数字表示。合法的 端口名: CLK,RESET,A0,D3

2013-7-14

卢庆莉 编写

②从计算机领域而言,行为描述和高级编程 语句相类似,所以计算机业内人士通常称之 为高级描述。

第2章 VHDL的高级议题

IS

1、格式

一、函数

函数调用的格式:

函数名(实参列表);

函数常在赋值语句或表达式中使用。

2、转换函数

功能:数据从一种类型转换到另一种类型。

【例】编写一个将8位二进制数转换成整数的函数,并 进行函数调用。

2、转换函数

一、函数

函数说明:

TYPE log8 IS ARRAY(0 TO 7) OF std_logic; FUNCTION vector_to_int(a:log8) RETURN integer IS

ห้องสมุดไป่ตู้

END 过程名;

注意: (1)每个形参必须包含:对象类型、通信模式、数据类型。

(2)模式为out和inout的参变量,是过程的返回值。 过程调用的格式: 过程名(实参列表);

二、过程

2.1 子程序

【例】

过程说明:

PROCEDURE addvec(add1,add2:in bit_vector; cin:in bit; signal sum:out bit_vector; signal cout:out bit) IS ... END addvec;

过程调用: addvec(A,B,C,S,F);

第2章

VHDL的高级议题

2.2 属性语句

一、信号属性语句

利用信号的属性来获取信号的行为信息和功能信息。

1、返回单一值的信号属性

(1)s’EVENT:若信号在当前△时间内发生事件,则 返回真,否则返回假。 (2)s’ACTIVE :若信号在当前△时间内发生事务,则 返回真,否则返回假。 (3)s’LAST_EVENT :s从上一次事件发生到目前的 时间差。

vhdl的名词解释

vhdl的名词解释VHDL,即VHSIC(Very High-Speed Integrated Circuits) Hardware Description Language,是硬件描述语言的一种。

它是一种用于描述数字电路和系统的语言,广泛应用于电子设计自动化(EDA)领域,特别是在数字电路设计、验证和仿真上。

VHDL的设计初衷是为了提供一种高层次的抽象,使设计人员能够更容易地描述复杂的硬件系统。

在VHDL中,主要有以下几个概念和关键词需要理解和解释。

1. 实体(entity)实体是VHDL代码中描述设计组件的顶层概念。

它类似于面向对象编程中的类定义,定义了一个模块的接口特性,包括输入、输出、信号和配置等。

实体在设计中起到了模块化的作用,能够将整个电路划分为相互独立且可复用的部分。

2. 体系结构(architecture)体系结构是对实体的具体实现描述。

它包含了实体中组件的结构和行为信息,以及内部信号和寄存器等。

体系结构中定义了组件的内部逻辑,以及如何将输入转换为输出。

一个实体可以有多个体系结构,用于实现不同的功能或优化设计。

3. 信号(signal)信号是数据在VHDL设计中的基本单元。

它类似于编程语言中的变量,用于在不同的组件之间传递数据。

在VHDL中,信号可以是标量(单个值)或向量(多个值)。

通过信号的赋值和传输,不同的组件能够进行数据的交互和处理。

4. 进程(process)进程是VHDL中的一种行为描述方式。

它类似于软件中的线程,可以定义一个并发执行的代码块。

进程可以响应信号的变化、执行逻辑操作、进行状态转换等。

通过进程,设计者可以描述顺序逻辑和组合逻辑的行为。

5. 泛型(generic)泛型是VHDL中的一种参数化机制。

它类似于编程语言中的函数模板或宏定义,用于在实体或体系结构中定义一组可配置的属性。

通过泛型,可以实现各种配置的复用,使得设计更加灵活和可扩展。

6. 测试台(testbench)测试台是用于验证和仿真VHDL设计的环境。

vhdl others用法

vhdl others用法VHDL是一种用于硬件描述语言的编程语言,它广泛应用于数字系统设计和硬件描述领域。

除了常见的VHDL语言的基本用法外,还有一些其他能够增强代码可读性和提高设计效率的技巧和方法。

本文将以"VHDL 其他用法"为主题,一步一步回答如下问题。

1. 介绍一些提高代码可读性的VHDL技巧和方法。

代码的可读性对于设计师和团队合作非常重要。

在VHDL中,可以采取以下一些方法来提高代码的可读性。

- 使用有意义的变量和信号名称:为了增强代码的可读性,应该选择具有描述性的变量和信号名称。

这样可以让其他人更容易理解代码的含义和功能。

- 使用注释:在代码中添加注释可以提供关于代码逻辑、功能和目的的详细说明。

这样其他人可以更容易理解代码的意图。

- 模块化设计:将大型的设计任务分解成小的模块,这样可以降低代码的复杂性。

每个模块都有自己的功能和输入输出接口,这样可以更容易理解和维护代码。

- 使用枚举类型:枚举类型可以为信号和变量定义一组具体的命名值,使代码更加清晰和易于理解。

2. 介绍一些提高设计效率的VHDL技巧和方法。

设计效率是一个重要的考量因素。

在VHDL中,可以采取以下一些方法来提高设计效率。

- 重用代码:将常用的功能和模块封装成库文件和组件,以便在其他设计中重复使用。

这样可以减少代码的重复编写,提高设计效率。

- 使用泛型:泛型允许在设计时动态地定义参数,并根据参数的值自动生成合适的硬件结构。

这样可以快速进行设计的定制化和参数化,提高设计效率。

- 使用生成语句:生成语句能够根据特定的规则生成多个实例。

这样可以在设计中实现重复的结构,并减少对复杂性和维护性的影响。

- 使用函数和过程:函数和过程可以使设计更加模块化和可重用。

它们可以用于实现特定的功能、算法和处理逻辑。

使用函数和过程可以减少代码的复杂性,并提高设计效率。

3. 介绍一些其他VHDL技巧和方法。

除了提高代码可读性和设计效率的技巧和方法之外,还有一些其他的VHDL技巧和方法。

第二章 VHDL语言应用基础3(子程序,库)

LIBRARY IEEE; -- 函数应用实例 USE IEEE.STD_LOGIC_1164.ALL; USE WORK.packexp.ALL ; ENTITY axamp IS PORT(dat1,dat2 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); dat3,dat4 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); out1,out2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END; ARCHITECTURE bhv OF axamp IS BEGIN out1 <= max(dat1,dat2); --用在赋值语句中的并行函数调用语句 PROCESS(dat3,dat4) BEGIN out2 <= max(dat3,dat4); --顺序函数调用语句 END PROCESS; END;

BEGIN

sam1(A(0), A(1), A(2), N(0));

sam1(A(2), A(0), A(1), N(1));

过程的调用即启动了对过 程体的顺序语句的调用, 调用3次。

sam1(A(1), A(2), A(0), N(2));

M(0)<= N(0); M(1)<= N(1); M(2)<= N(2); END art1;

WORK库。WORK库是现行作业库。设计者所描述的VHDL语 句不需要任何说明,将都存放在WORK库中。WORK库对所有

设计都是隐含可见的,因此在使用该库时无需进行任何说明。

用户定义库。用户定义库简称用户库,是由用户自己创建并定 义的库。设计者可以把自己经常使用的非标准(一般是自己开发 的)包集合和实体等汇集成在一起定义成一个库,作为对VHDL 标准库的补充。用户定义库在使用时同样要首先进行说明。

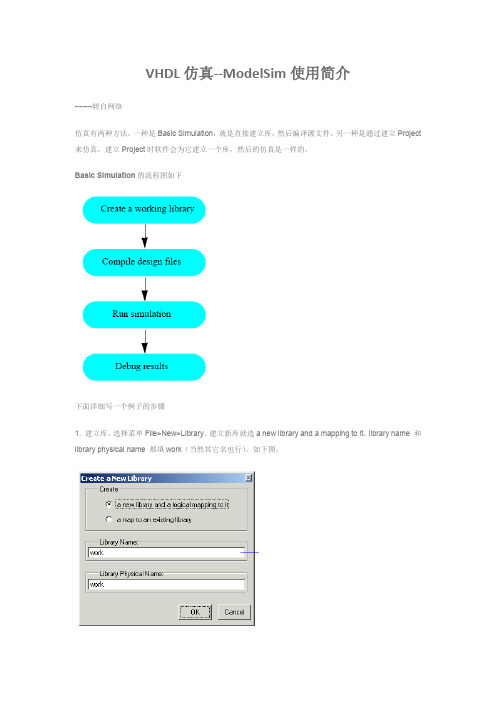

VHDL仿真ModelSim使用简介

VHDL仿真--ModelSim使用简介-------转自网络仿真有两种方法。

一种是Basic Simulation,就是直接建立库,然后编译源文件。

另一种是通过建立Project 来仿真,建立Project时软件会为它建立一个库,然后的仿真是一样的。

Basic Simulation的流程图如下下面详细写一个例子的步骤1. 建立库。

选择菜单File>New>Library。

建立新库就选a new library and a mapping to it,library name 和library physical name 都填work(当然其它名也行)。

如下图。

确定后,在Work Space区的Library选项卡里就能看到新建的库work。

2. 编译VHDL或Verilog HDL源文件。

选择菜单Compile>Compile,在弹出的窗口中打开Model Sim安装文件夹下的/modeltech/examples/tutorials/vhdl/basicSimulation/ (里面是软件自带教程的例子逻辑,Verilog HDL对应的例子在/examples/tutorials/verilog/basicSimulation里)。

将里面的counter.vhd 和tcounter.vhd一起选中,点击Compile,然后点击Done关闭弹出窗口。

这两个源文件就编译好了,在Work Space区里的Library卡里可以看到库work下出现了两个编译完成的entity(或module),如下图。

3. 仿真。

在Work Space区的library选项卡中,展开库work前的加号,双击test_counter,载入到仿真。

这时Work Space区中新增了一些选项卡,弹出了Objects面板。

选择菜单View>Debug Windows>Wave调出波形窗口。

在Work Space面板的Sim选项卡中右击test_counter,选择Add>Add to Wave。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.1.3 Event Scheduling The assignment to signal x does not happen instantly. Each of the values assigned to signal x contain an AFTER clause. The mechanism for delaying the new value is called scheduling an event.

Example 2.6 3-input AND gate entity andgate is port(a, b, c: in bit; x: out bit); end andgate; architecture structure of andgate is begin x<=a and b and c; end structure;

Example 2.11 Better multiple driver model

architecture better of multiplexer is begin q <= i0 when a = ‘0’ and b = ‘0’ else i1 when a = ‘1’ and b = ‘0’ else i2 when a = ‘0’ and b = ‘1’ else i3 when a = ‘1’ and b = ‘1’ else ‘X’; end better;

Example 2.10 Bad multiple driver model library IEEE; use IEEE.std_logic_1164.all; entity multiplexer is port (i0, i1, i2, i3, a, b : in std_ulogic; q : out std_ulogic); end multiplexer; architecture bad of multiplexer is begin q <= i0 when a = ‘0’ and b = ‘0’ else ‘0’; q <= i1 when a = ‘1’ and b = ‘0’ else ‘0’; q <= i2 when a = ‘0’ and b = ‘1’ else ‘0’; q <= i3 when a = ‘1’ and b = ‘1’ else ‘0’; end bad;

2.4 Signal assignments

2.4.1 Signal delays

There are two kinds of delays: inertial delay and transport delay. Inertial: b <= a AFTER 20 ns; Transport: b <= TRANSPORT a AFTER 20 ns;

Example 2.1 Entity of two-input AND gate entity and2 is port( x, y : in bit; z: out bit); end entity and2; Example 2.2 Entity of 1-OF-4 multiplexer entity mux is port( a, b, c, d : in bit; s0, s1: in bit; x : out bit); end mux;

Each VHDL file should include a header. -------------------------------------------------------------------- Design unit : andgate(structure) -- File name : andgate.vhd -- Description : Two-input and gate -- Limitations : None lists -- System : VHDL'93 -- Author : Fan Bishuang -- Email : fbshfj@ -- Revision : Version 1.0 16/5/06 -------------------------------------------------------------------

Chapter 2 VHDL Models

VHDL terms: Entity Architecture Configuration Package Driver Bus Attribute Generic Process

2.1 Entities and architectures

2.1.1Entities

architecture and2_gate of and2 is signal internal : bit; begin internal <= a and b; c <= internal after (rise + (load * 2 ns)) when internal = ‘1’ else internal after (fall + (load * 3 ns)); end and2_gate;

2.1.2 Architectures

Example 2.3 Architecture of two-input AND gate architecture ex1 of and2 is begin z <= x and y; end architecture ex1; Example 2.4 Architecture of 1-OF-4 multiplexer ARCHITECTURE dataflow OF mux IS SIGNAL s : INTEGER RANGE 0 TO 3; BEGIN s <= 0 WHEN s0 = ‘0’ AND s1 = ‘0’ ELSE 1 WHEN s0 = ‘1’ AND s1 = ‘0’ ELSE 2 WHEN s0 = ‘0’ AND s1 = ‘1’ ELSE 3; x <=a AFTER 0.5 NS WHEN s = 0 ELSE b AFTER 0.5 NS WHEN s = 1 ELSE c AFTER 0.5 NS WHEN s = 2 ELSE d AFTER 0.5 NS; END dataflow;

Inertial delay of 20 ns

Transport delay of 20 ns

2.4.2 Drivers Drivers are sources on signals.

Example 2.9 A signal with two drivers architecture test of test is begin a <= b after 10 ns; a <= c after 10 ns; end test; Synthesizing the example would short c and b together.

2.5 Generiபைடு நூலகம்s

Generics are parameters that are used to pass information into entities. z <= x and y after 5 ns; z <= x and y after delay; Example 2.12 2-input AND gate delay entity and2 is generic(rise, fall : time; load : integer); port(a, b : in bit; c : out bit); end and2;

2.3 Netlists Example 2.5 inverter entity inverter is port (a: in bit; x: out bit); end inverter; architecture structure of inverter is begin x <= not a; end structure;

2.1.3 Concurrent Signal Assignment Inside a VHDL architecture, there is no specified ordering of the assignment statements. The order of execution is solely specified by events occurring on signals that the assignment statements are sensitive to. An event on a signal is a change in the value of that signal.

component orgate port(a, b, c, d : in bit; x : out bit); end component; signal s0_inv, s1_inv, x1, x2, x3, x4 : bit; begin g1 : inverter port map (s0, s0_inv); g2 : inverter port map (s1, s1_inv); g3 : andgate port map (a, s0_inv, s1_inv, x1); g4 : andgate port map (b, s0, s1_inv, x2); g5 : andgate port map (c, s0_inv, s1, x3); g6 : andgate port map (d, s0, s1, x4); g7 : orgate port map (x2 => b, x1 => a, x4 => d, x3 => c, x => x); end netlist;

2.2 Identifiers, spaces and comments • VHDL is not case sensitive(unlike C). • Identifiers may consist of letters, numbers and underscores(‘_’), but the first character must be a letter and two underscores in succession are not allowed. Reserved words(entity, architecture, is, begin, port and so on) can not be identifiers. • There is no difference between one whitespace character and many.