GW48使用说明

日立空调机组GW协议转换器使用说明书

——目录——1.LONWORKS技术概况2.G/W协议转换器3.机组测的设定和接线4.试运行5.LONWORKS变量SNVT定义6.报警代码转换表1.LONWORKS技术概况美国Echelon公司1991年推出的LON技术,又称LONWORKS技术是计算机控制技术第三代的现场总线技术。

LONWORKS技术是一个实现控制网络系统的完整平台。

这些网络包括智能设备或节点。

括智能设备或节点与它们所处的环境进行交互作用,以及通过不同的通信介质与其它节点进行通信。

这种通信采用一种通用的、基于消息的控制协议-LONTALK协议。

由于LONTALK协议已固化在神经元芯片(微处理器)内,节点通过网络变量的形式交换信息,又有现成的网络管理工具进行网络管理。

所以建立一个LONWORKS控制网络在网络通讯上几乎不需要任何调试工作量。

LONWORKS技术的网络通信对用户是透明的,神经元芯片自动完成LONWORK S的所有七层的网络协议,用户所要作的只有两件事:第一件事是指定哪些信息是通过网络变量传递的,也就是定议网络变量;第二件事是指定信息传递传递的发起者和接收者,也就是做Binding(网络变量的捆绑)。

2.G/W协议转换器(其型号为HARC70-C)G/W协议转换器是日立公司提供的通信用网关设备(可简称G/W)。

是把广州日立冷机有限公司内部用的H-link通信协议转换成公开的LONTALK协议的设备。

是便于用户通过通信网络监控日立的冷水机组为目的开发的一种通信协议转换器。

1)系统构成方式以下是用G/W协议转换器联接到BMS(楼宇控制系统)系统时的系统构成简图。

对于构成系统的其它部品请参阅相应的使用说明书。

注意事项:1)冷水机组测的通信线上一定要加上附带的线圈和电容。

2)屏蔽线要采用D类接地标准备注:上位装置可使用LONWORKS /RS232C型的G/W(ECHELON制SLTA-10 通用的LONTALK 收发器等)及相应的软件。

2023年大学_EDA技术与VHDL第二版(潘松著)课后习题答案下载

2023年EDA技术与VHDL第二版(潘松著)课后习题答案下载EDA技术与VHDL第二版(潘松著)课后答案下载第1章 EDA技术概述1.1 EDA技术及其发展1.1.1 EDA技术的发展1.1.2 EDA技术的涵义1.1.3 EDA技术的基本特征1.2 EDA技术的主要内容及主要的EDA厂商1.2.1 EDA技术的主要内容1.2.2 主要EDA厂商概述1.3 EDA技术实现目标1.3.1 超大规模可编程逻辑器件1.3.2 半定制或全定制ASIC1.3.3 混合ASIC1.4 EDA技术应用1.4.1 EDA技术应用形式1.4.2 EDA技术应用场合1.5 EDA技术的发展趋势1.5.1 可编程器件的发展趋势1.5.2 软件开发工具的发展趋势1.5.3 输入方式的发展趋势__小结思考题和习题第2章大规模可编程逻辑器件2.1 可编程逻辑器件概述2.1.1 PLD的'发展进程2.1.2 PLD的种类及分类方法2.2 简单可编程逻辑器件2.2.1 PLD电路的表示方法及有关符号 2.2.2 PROM基本结构2.2.3 PLA基本结构2.2.4 PAL基本结构2.2.5 GAL基本结构2.3 复杂可编程逻辑器件2.3.1 CPLD基本结构2.3.2 Altera公司器件2.4 现场可编程逻辑器件2.4.1 FPGA整体结构2.4.2 Xilinx公司FPGA器件2.5 在系统可编程逻辑器件2.5.1 ispLSl/pLSl的结构2.5.2 Lattice公司ispLSI系列器件 2.6 FPGA和CPLD的开发应用2.6.1 CPLD和FPGA的编程与配置2.6.2 FPGA和CPLD的性能比较2.6.3 FPGA和CPLD的应用选择__小结思考题和习题第3章 EDA设计流程与开发3.1 EDA设计流程3.1.1 设计输入3.1.2 综合3.1.3 适配3.1.4 时序仿真与功能仿真3.1.5 编程下载3.1.6 硬件测试3.2 ASIC及其设计流程3.2.1 ASIC设计方法3.2.2 一般的ASIC设计流程3.3 可编程逻辑器件的开发环境 3.4 硬件描述语言3.5 IP核__小结思考题和习题第4章硬件描述语言VHDL4.1 VHDL概述4.1.1 VHDL的发展历程4.1.2 VHDL的特点4.2 VHDL程序基本结构4.2.1 实体4.2.2 结构体4.2.3 库4.2.4 程序包4.2.5 配置4.3 VHDL基本要素4.3.1 文字规则4.3.2 数据对象4.3.3 数据类型4.3.4 运算操作符4.3.5 VHDL结构体描述方式 4.4 VHDL顺序语句4.4.1 赋值语句4.4.2 IF语句4.4.3 等待和断言语句4.4.4 cASE语句4.4.5 LOOP语句4.4.6 RETIARN语句4.4.7 过程调用语句4.4.8 REPORT语句4.5 VHDL并行语句4.5.1 进程语句4.5.2 块语句4.5.3 并行信号代人语句4.5.4 并行过程调用语句4.5.5 并行断言语句4.5.6 参数传递语句4.5.7 元件例化语句__小结思考题和习题第5章 QuartusⅡ软件及其应用5.1 基本设计流程5.1.1 建立工作库文件夹和编辑设计文件 5.1.2 创建工程5.1.3 编译前设计5.1.4 全程编译5.1.5 时序仿真5.1.6 应用RTL电路图观察器5.2 引脚设置和下载5.2.1 引脚锁定5.2.2 配置文件下载5.2.3 AS模式编程配置器件5.2.4 JTAG间接模式编程配置器件5.2.5 USBBlaster编程配置器件使用方法 __小结思考题和习题第6章 VHDL应用实例6.1 组合逻辑电路设计6.1.1 基本门电路设计6.1.2 译码器设计6.1.3 数据选择器设计6.1.4 三态门设计6.1.5 编码器设计6.1.6 数值比较器设计6.2 时序逻辑电路设计6.2.1 时钟信号和复位信号6.2.2 触发器设计6.2.3 寄存器和移位寄存器设计6.2.4 计数器设计6.2.5 存储器设计6.3 综合实例——数字秒表的设计__小结思考题和习题第7章状态机设计7.1 一般有限状态机7.1.1 数据类型定义语句7.1.2 为什么要使用状态机 7.1.3 一般有限状态机的设计 7.2 Moore型有限状态机设计 7.2.1 多进程有限状态机7.2.2 单进程有限状态机7.3 Mealy型有限状态机7.4 状态编码7.4.1 状态位直接输出型编码 7.4.2 顺序编码7.4.3 一位热码编码7.5 状态机处理__小结思考题和习题第8章 EDlA实验开发系统8.1 GW48型实验开发系统原理与应用8.1.1 系统性能及使用注意事项8.1.2 GW48系统主板结构与使用方法8.2 实验电路结构图8.2.1 实验电路信号资源符号图说明8.2.2 各实验电路结构图特点与适用范围简述8.3 GW48CK/GK/EK/PK2系统信号名与芯片引脚对照表 __小结思考题和习题第9章 EnA技术实验实验一:全加器的设计实验二:4位加减法器的设计实验三:基本D触发器的设计实验四:同步清零计数器的设计实验五:基本移位寄存器的设计串人/串出移位寄存器实验六:同步预置数串行输出移位寄存器的设计实验七:半整数分频器的设计实验八:音乐发生器的设计实验九:交通灯控制器的设计实验十:数字时钟的设计EDA技术与VHDL第二版(潘松著):内容简介《EDA技术与VHDL》主要内容有Altera公司可编程器件及器件的选用、QuartusⅡ开发工具的使用;VHDL硬件描述语言及丰富的数字电路和电子数字系统EDA设计实例。

固德威储能逆变器GW5048-ESA用户手册说明书

用户手册储能逆变器GW5048-ESA目录用户手册 V1.4-2022-06-30目录01 产品介绍 (5)1.1 功能 (5)1.2 特性 (5)1.3 选择电池 (5)1.4 尺寸 (6)02 产品规划 (7)2.1 BACK-UP负载 (7)2.2 逆变器工作模式 (7)2.2.1 一般模式 (7)2.2.2 离网模式 (9)2.2.3 待机模式 (9)2.2.4 经济模式 (9)03 安装 (10)3.1 附件清单 (10)3.2 安装环境要求 (10)3.4 安装电池柜 (12)3.5 安装挂装件 (12)3.6 安装BoS系统 (12)3.7 安装逆变器 (13)04 安装系统 (14)4.1 打开BoS盖子 (14)4.2 BoS接线 (15)4.2.1 系统接线 (16)4.2.2 连接保护地线 (17)4.2.3 连接光伏阵列 (18)4.2.4 连接电池 (18)4.2.5 连接电池管理系统(BMS) (19)4.2.6 连接交流线和交流断路器 (21)目录用户手册 V1.4-2022-06-30 4.2.7 连接电网 (22)4.2.8 连接BACK-UP负载 (23)4.3 连接电表 (24)05 操作 (26)5.1 断路器和旁路开关 (26)5.2 启动 (27)5.3 关机 (28)5.4 LED指示灯 (29)06 网络连接 (30)6.1 WiFi 配置 (30)6.2 SolarGo (31)6.3 CEI自动测试功能 (31)07 故障解决 (32)08 技术参数 (33)09 认证、标准和审批 (37)版权声明用户手册 V1.4-2022-06-30因产品版本升级或其他原因,文档内容会不定期进行更新,如无特殊约定,文档内容不可取代产品标签或用户手册中的安全注意事项。

文档中的所有描述仅作为使用指导。

以及本手册中使用的其他GOODWE商标归固德威技术股份有限公司所有。

GW48结构图信号名与芯片引脚对照表

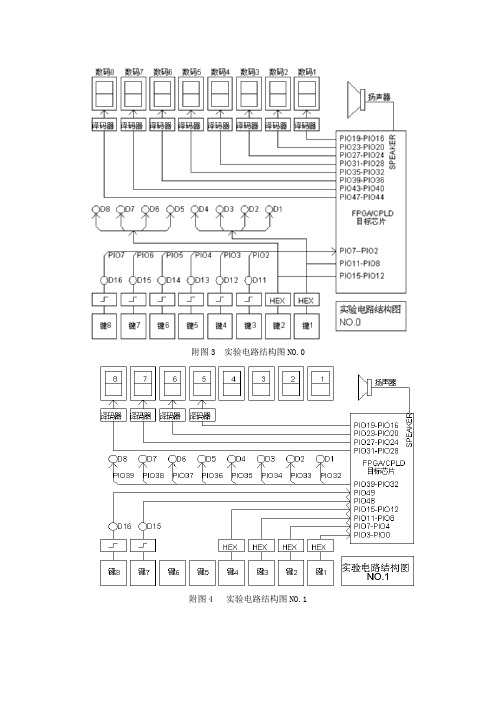

附图3 实验电路结构图NO.0附图4 实验电路结构图NO.1附图5 实验电路结构图NO.2实实实实实实实NO.3实实实实实实实实实实实实实实实实实实实实实实实实D9D16D15D14D13D12D11D10D8D7D6D5D4D3D2D1PIO8PIO9PIO10PIO11PIO12PIO13PIO14PIO15S P E A K E R实实实12345678实实实实FPGA/CPLD PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8PIO15-PIO8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16附图6 实验电路结构图NO.3附图7 实验电路结构图NO.4D1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实实实实实实实NO.5S P E A K E R实实实FPGA/CPLD 实实实实12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16实实实实实实实实实实实实实实实实实实实实实实实实PIO15-PIO8PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8附图8 实验电路结构图NO.5附图9 实验电路结构图NO.6D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图S P E A K E R扬声器FPGA/CPLD 目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器附图10 实验电路结构图NO.7附图11 实验电路结构图NO.8附图12 实验电路结构图NO.9附图13 实验电路结构图NO.B实验电路结构图 N O .5AD 16D 15D 14D 13D 12D 11D 10D 9D 8D 7D 6D 5D 4D 3D 2D 1P I O 8J P 2(1/2,3/4)J P 2(5/6)P I O 8SPEAKER目标芯片F P G A /C P L D(23)(24)1216272610C L O C K 750K H Z A 750K H Z A F I T102C 30103C 29D A -5--+5D A 0--+5P I O 38P I O 37P I O 35C O M MD A W RC O M P ADE O C A D E N J P 22018161412108642191715131197531021V R 110K V C C +5V A I N 0A I N 1r e f (-)r e f (+)I N -1I N -06922257171415818192021E U 1A D C 0809P I O 16P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32P I O 33P I O 35P I O 34m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T扬声器P I O 39-P I O 36P I O 43-P I O 40P I O 47-P I O 4412345678数码数码数码数码数码数码数码数码译码器译码器译码器单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7P I O 15P I O 14P I O 13P I O 12P I O 11P I O 10P I O 9P I O 8键1键2键3键4键5键6键7键8附图14 实验电路结构图NO.5AD 8D 7D 6D 5D 4D 3D 2D 1译码器译码器译码器D 16D 15D 14D 13D 12D 11D 10D 9实验电路结构图 N O .5BV C C目标芯片F PG A /C P L D串行通讯接口接口电路J 75413P I O 45P I O 46P S /2接口单片机接口电路235接P C 机R S -232B 412M H Z A键复位P I O 11P I O 12P I O 13P I O 14SPEAKERA T 89C 2051E U 3P 34P 33P 32X 1X 2P 31P 30P 35R S TG N D P 37P 10P 11P 12P 13P 14P 15P 16P 17V C C 1234567891011121314151617181920P I O 15P I O 24P I O 25P I O 26P I O 27P I O 28P I O 29P I O 30P I O 31扬声器P I O 39-P I O 36P I O 43-P I O 40P I O 47-P I O 4412345678数码数码数码数码数码数码数码数码单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7P I O 15P I O 14P I O 13P I O 12P I O 11P I O 10P I O 9P I O 8键1键2键3键4键5键6键7键8附图15 实验电路结构图NO.5BD 16D 15D 14D 13D 12D 11D 10D 9D 1P I O 8D 2P I O 9D 3P I O 10D 4P I O 11D 5P I O 12D 6P I O 13D 7P I O 14D 8P I O 15译码器译码器译码器实验电路结构图 N O .5CF PG A /C P L DJ P 251p F C 27J P 2(C O M P )C O M PP I O 37L M 311V C C 10K-12+124823T L 082/1A I N 0A O U T5.1K102103+510K5.1K5.1KR 72765T L 082/2841+12-12D A 0--+5D A -5--+5滤波0滤波1F I TC O M M E U 2D A C 0832********J P 2(9,10)P I O 38D A W R 2W R 1F B93211I O U T 1I O U T 212/C S W R 2X F E R A G N D D G N D V R E F 8V C C20+5V C CD 0D 1D 2D 3D 4D 5D 6D 7765416151413P I O 24P I O 25P I O 26P I O 27P I O 28P I O 29P I O 30P I O 31P I O 43-P I O 40P I O 35-P I O 32P I O 23-P I O 20P I O 19-P I O 16目标芯片P I O 47-P I O 44译码器译码器P I O 15-P I O 812345678数码数码数码数码数码数码数码数码单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7键1键2键3键4键5键6键7键8附图16 实验电路结构图NO.5CD A C C1K REFS 1KREFSNO.5DPIO34PIO27SDASCL TEST NC NC NC PIO19PIO17PIO34PIO27GNDNC NC DOUTDIN SK CS 24CXX93CXXVCC87654321VCC GNDVCC 87654321VCC TLC549VCC PIO30PIO2987654321PIO28CSDOUT I/OCK VCC GNDREF-AIN REF+JSL141312111098765PIO26PIO24PIO25PIO31VCCLOADDACD DACC DACB DACA LDAC CLKDATA REFD REFC REFB REFA TLC5620GND VCCREFSS VCC REFSJTLJAVPIO19PIO18TLV1572PIO17SCLKVCC FS DO AINGND VREF PIO34CS 87654321VCC 4321REFSSREFINCLK VCC PIO17PIO34PIO198031VIN-VIN+CS 87654321DOUT GNDADC08031VCC ADCCD1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实实实实实实实S P E A K E R实实实FPGA/CPLD 实实实实12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16实实实实实实实实实实实实实实实实实实实实实实实实PIO15-PIO8实实实实实实实实实PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8附图17 实验电路结构图NO.5D附录2 GW48结构图信号名与芯片引脚对照表。

各量表使用说明解读

指导手册瑞文标准推理测验 (3)高级瑞文推理测验 (4)明尼苏达多相人格调查表 (4)卡特尔人格测试 (8)艾森克个性测验 (14)爱德华个人偏好测验 (15)90项自觉症状 (17)生活事件量表 (18)A型行为类型问卷 (19)(Type A Behavior Pattern Scale,TABP) (19)家庭环境量表 (22)OLSON婚姻质量问卷 (22)防御方式问卷(DSQ) (24)惧怕否定评价量表(FNE) (25)个人评价问卷(PEI) (26)社交回避及苦恼量表(SAD) (27)情绪-社交孤独问卷(ESLI) (27)情感量表:正性情感、负性情感、情感平衡 (28)YALE-BROWN强迫量表 (28)社交焦虑量表 (28)焦虑自评量表(SAS) (29)抑郁自评量表(SDS) (29)简明精神病量表 (30)躁狂量表 (30)精神症状全面量表 (31)UCLA孤独量表 (31)康奈尔医学指数 (32)密西根酒精调查表(MAST) (32)纽卡斯尔抑郁诊断量表(NDI) (33)BECK抑郁自评问卷(BDI) (33)状态-特质焦虑问卷(STAI) (34)艾森克情绪稳定性 (35)流调用抑郁自评量表 (36)汉密顿焦虑量表 (37)汉密顿抑郁量表(HRSD) (37)生活满意度量表 (38)总体幸福感量表(GWB) (38)阿森斯失眠量表 (39)贝克焦虑量表(BAI) (39)简易应对方式问卷 (40)(Simplified Coping Style Questionnaire) (40)健康状况问卷 (41)(Short Form 36 Health survey Questionnaire,SF-36) (41)老年抑郁量表 (42)[The Geriatric Depression Scale] (42)(Brink,Yesavage,Lum,Heersema,Adey,&Rose,1982) (42)纽芬兰纪念大学幸福度量表 (43)Memorial University of Newfoudland Scale of Happiness (43)(Kozma & Stones,1980) (43)疲劳量表-14 (44)(Fatigue Scale-14,FS-14) (44)匹茨堡睡眠质量指数量表(PSQI) (45)气质问卷 (45)社会支持评定量表 (45)世界卫生组织生存质量测定量表(WHOQOL) (46)心理健康测查表 (48)(Psychological Health Inventory,PHI) (48)医院焦虑抑郁量表 (54)应付方式问卷 (54)瑞文标准推理测验简介:瑞文标准推理测验(Raven's Standard Progressive Matrices)是英国心理学家瑞文(J.C.Raven)1938年设计的非文字智力测验。

GW隔离开关技术参数

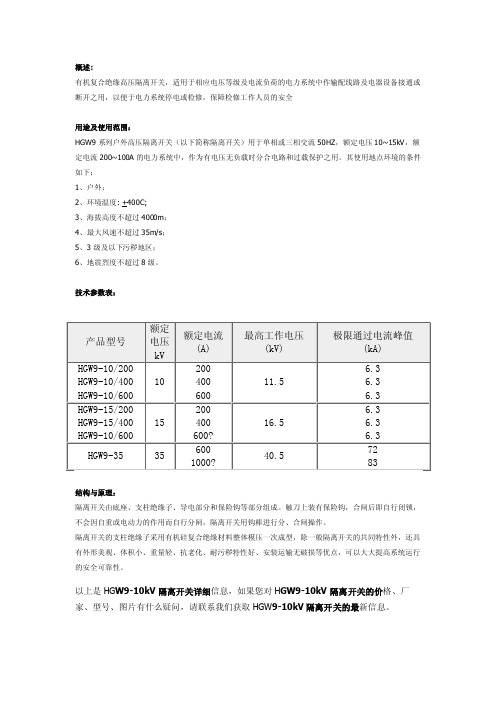

概述:有机复合绝缘高压隔离开关,适用于相应电压等级及电流负荷的电力系统中作输配线路及电器设备接通或断开之用,以便于电力系统停电或检修,保障检修工作人员的安全用途及使用范围:HGW9系列户外高压隔离开关(以下简称隔离开关)用于单相或三相交流50HZ,额定电压10~15kV,额定电流200~100A的电力系统中,作为有电压无负载时分合电路和过载保护之用。

其使用地点环境的条件如下:1、户外;2、环境温度: +400C;3、海拔高度不超过4000m;4、最大风速不超过35m/s;5、3级及以下污秽地区;6、地震烈度不超过8级。

技术参数表:10kV交流高压户外隔离开关技术规范书工程项目:广西电网公司年月目录1 总则2 使用环境条件3 技术参数和要求4 试验5 供货范围6 技术资料和图纸交付进度7 运输要求8 技术服务1总则1.1本设备技术规范书适用于10kV系统户外隔离开关和接地开关,本技术规范书提出了该产品的功能设计、结构、性能、和试验等方面的技术要求。

1.2需方在本规范书中提出了最低限度的技术要求,并未规定所有的技术要求和适用的标准,未对一切技术细则作出规定,也未充分引述有关标准和规范的条文,供方应提供一套满足本规范书和现行有关标准要求的高质量产品及其相应服务。

1.3如果供方没有以书面形式对本规范书的条款提出异议,则意味着供方提供的设备(或系统)完全满足本规范书的要求。

如有异议,应在投标书中以“对规范书的意见和与规范书的差异”为标题的专门章节加以详细描述。

1.4本设备技术规范书经需供双方确认后作为订货合同的技术附件,与合同正文具有同等的法律效力。

1.5供方须执行现行国家标准和行业标准。

应遵循的主要现行标准如下。

EDA之1位全加器

EDA技术实验教案实验一1位全加器原理图输入设计一、实验目的1、熟悉MAX+plusII软件的基本使用方法。

2、熟悉GW48-ES EDA实验开发系统的基本使用方法。

3、了解原理图输入设计方法。

二、实验内容设计并调试好一个1位二进制全加器,并用GW48-ES EDA实验开发系统(拟采用的实验芯片的型号为EPF10K20TC144-4或EP1K30TC144-3)进行系统仿真、硬件验证。

设计1位二进制全加器时要求先用基本门电路设计一个1位二进制半加器,再由基本门电路和1位二进制半加器构成1位二进制全加器。

三、实验条件1、开发条件:MAX+plusII2、实验设备:GW48-ES EDA实验开发系统、联想电脑3、拟用芯片:EPF10K20TC144-4或EP1K30TC144-3四、实验设计半加器(h_adder.gdf)全加器(f_adder.gdf)实验结果半加器仿真波形半加器引脚锁定实验芯片:EPF10K20TC144-4选用模式:模式5设计实体I/O标识I/O来源/去向结构图上的信号名芯片引脚号a 键1 PIO0 8b 键2 PIO1 9so 二极管D1 PIO8 20co 二极管D2 PIO9 21 全加器仿真波形全加器引脚锁定实验芯片:EPF10K20TC144-4选用模式:模式5设计实体I/O标识I/O来源/去向结构图上的信号名芯片引脚号ain 键1 PIO0 8bin 键2 PIO1 9cin 键3 PIO2 10sum 二极管D1 PIO8 20cout 二极管D2 PIO9 21全加器真值表ain 0 1 0 1 0 1 0 1 bin 0 0 1 1 0 0 1 1 cin 0 0 0 0 1 1 1 1 sum 0 1 1 0 1 0 0 1 cout 0 0 0 1 0 1 1 1实验二1位全加器VHDL文本输入设计一、实验目的1、熟悉MAX+plusII软件的基本使用方法。

Verilog hdl—简易电子琴设计

文理学院简易电子琴设计专业:自动化学号:2012118064:一天虹影实验目的使用VerilogHDL语言进行前端设计,并使用Quaruts软件在GW48-PK2实验上实现仿真,实现硬件电子琴。

电子琴要求有8个音阶,使用外部时钟信号3MHz,能同步显示音阶。

1、 设计一个简易电子琴。

要求能演奏的音域为D 调的do 到E 调do 。

2、 用GW48-PK2中的8个按键作为琴键。

3、 GW48-PK2中有蜂鸣器。

4、 可以使用GW48-PK2上的12MHz 作为输入时钟信号设计思路通过可编程逻辑器件(PLD )和VHDL 硬件描述语言来实现电子琴的基本要求。

设计的主体是数控分频器,对输入的频率按照与每个音阶对应的分频系数进行分频,得到各个音阶对应的频率分别在蜂鸣器和数码管上以声音和频率数值的形式作为输出。

设计组成与原理下图为系统的工作原理框图。

分频置 数按 键分 频器12MHZ蜂 鸣 器数码管显示1.音名与频率的关系音乐的12平均率规定:每2个八度音(如简谱中的中音1与高音1)之间的频率相差1倍。

在2个八度音之间,又可分为12个半音。

灵位,音符A(简谱中的低音6)的频率为440HZ,音符B到C之间、E到F之间为半音,其余为全音。

由此可以计算出简谱中所有的音符的频率,在这我们只需计算出中音1到高音1的频率即可。

如下所示:表一简谱音名与频率的对应关系由于各音符对应的频率多为非整数,而分频系数又不能为小数,故必须将计算得到的分频数四舍五入取整。

若分频器时钟频率过低,则由于分频系数过小,四舍五入取整后的误差较大;若时钟频率过高,虽然误差变小,但分频数将变大。

实际的设计应综合考虑两方面的因素,在尽量减少频率误差的前提下取合适的时钟频率。

本实验要求用12MHZ的时钟脉冲信号,所以不必考虑这方面的因素。

实际上,只要各个音符间的相对频率关系不变,弹奏出来的音调听起来是不会走调的。

2.分频系数与初始值(预置数)本例设计的音乐电子琴选取12MHZ的系统时钟频率。

实验三:PWM信号发生器

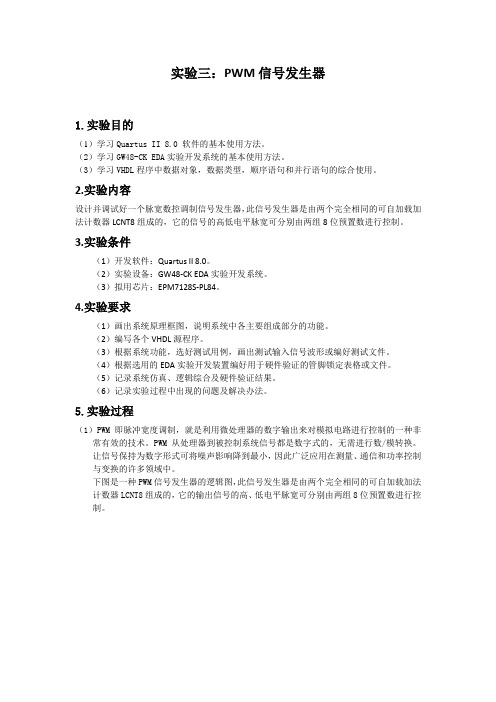

实验三:PWM信号发生器1.实验目的(1)学习Quartus II 8.0 软件的基本使用方法。

(2)学习GW48-CK EDA实验开发系统的基本使用方法。

(3)学习VHDL程序中数据对象,数据类型,顺序语句和并行语句的综合使用。

2.实验内容设计并调试好一个脉宽数控调制信号发生器,此信号发生器是由两个完全相同的可自加载加法计数器LCNT8组成的,它的信号的高低电平脉宽可分别由两组8位预置数进行控制。

3.实验条件(1)开发软件:Quartus II 8.0。

(2)实验设备:GW48-CK EDA实验开发系统。

(3)拟用芯片:EPM7128S-PL84。

4.实验要求(1)画出系统原理框图,说明系统中各主要组成部分的功能。

(2)编写各个VHDL源程序。

(3)根据系统功能,选好测试用例,画出测试输入信号波形或编好测试文件。

(4)根据选用的EDA实验开发装置编好用于硬件验证的管脚锁定表格或文件。

(5)记录系统仿真、逻辑综合及硬件验证结果。

(6)记录实验过程中出现的问题及解决办法。

5.实验过程(1)PWM即脉冲宽度调制,就是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术。

PWM从处理器到被控制系统信号都是数字式的,无需进行数/模转换。

让信号保持为数字形式可将噪声影响降到最小,因此广泛应用在测量、通信和功率控制与变换的许多领域中。

下图是一种PWM信号发生器的逻辑图,此信号发生器是由两个完全相同的可自加载加法计数器LCNT8组成的,它的输出信号的高、低电平脉宽可分别由两组8位预置数进行控制。

如果将初始值可预置的加法计数器的溢出信号作为本计数器的初始预置值加载信号LD,则可构成计数器初始值自加载方式的加法计数器,从而构成数控分频器。

图中D 触发器的一个重要功能就是均匀输出信号的占空比,提高驱动能力,这对驱动,诸如扬声器或电动机十分重要。

(2)VHDL源程序①8位可自加载加法计数器的源程序LCNT8.VHD--LCNT8.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY LCNT8 ISPORT(CLK,LD:IN STD_LOGIC;D:IN INTEGER RANGE 0 TO 255;CAO:OUT STD_LOGIC);END ENTITY LCNT8;ARCHITECTURE ART OF LCNT8 ISSIGNAL COUNT:INTEGER RANGE 0 TO 255;BEGINPROCESS(CLK)ISBEGINIF CLK'EVENT AND CLK='1'THENIF LD='1'THEN COUNT<=D;ELSE COUNT<=COUNT+1;END IF;END IF;END PROCESS;PROCESS(COUNT)ISBEGINIF COUNT=255 THEN CAO<='1';ELSE CAO<='0';END IF;END PROCESS;END ARCHITECTURE ART;②PWM信号发生器的源程序PWM.VHD--PWM.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY PWM ISPORT(CLK:IN STD_LOGIC;A,B:IN STD_LOGIC_VECTOR(7 DOWNTO 0);PWM:OUT STD_LOGIC);END ENTITY PWM;ARCHITECTURE ART OF PWM ISCOMPONENT LCNT8 ISPORT(CLK,LD:IN STD_LOGIC;D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);CAO:OUT STD_LOGIC);END COMPONENT LCNT8;SIGNAL CAO1,CAO2:STD_LOGIC;SIGNAL LD1,LD2:STD_LOGIC;SIGNAL SPWM:STD_LOGIC;BEGINU1:LCNT8 PORT MAP(CLK=>CLK,LD=>LD1,D=>A,CAO=>CAO1);U2:LCNT8 PORT MAP(CLK=>CLK,LD=>LD2,D=>B,CAO=>CAO2);PROCESS(CAO1,CAO2)ISBEGINIF CAO1='1'THEN SPWM<='0';ELSIF CAO2'EVENT AND CAO2='1'THEN SPWM<='1';END IF;END PROCESS;LD1<=NOT SPWM;LD2<=SPWM;PWM<=SPWM;END ARCHITECTURE ART;(3)仿真结果验证PWM.VHD的时序仿真结果(4)逻辑综合结果6.实验总结经过本次实验,我学会了Quartus II 8.0 开发系统的基本操作,并对它有了一定的了解和认识。

杭州康芯SOPC实验开发系统说明

杭州康芯SOPC实验开发系统说明(型号:GW48-PK2S)1、关于ASIC、CPLD、sopc、FPGAASIC(Application Specific Intergrated Circuits)即专用集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

目前用CPLD(复杂可编程逻辑器件)和FPGA(现场可编程逻辑阵列)来进行ASIC设计是最为流行的方式之一,它们的共性是都具有用户现场可编程特性,都支持边界扫描技术,但两者在集成度、速度以及编程方式上具有各自的特点。

ASIC的特点是面向特定用户的需求,品种多、批量少,要求设计和生产周期短,它作为集成电路技术与特定用户的整机或系统技术紧密结合的产物,与通用集成电路相比具有体积更小、重量更轻、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

在二○世纪九十年度末,可编程逻辑器件(PLD)的复杂度已经能够在单个可编程器件内实现整个系统。

完整的单芯片系统(SOC)概念是指在一个芯片中实现用户定义的系统,它通常暗指包括片内存储器和外设的微处理器。

最初宣称真正的SOC――或可编程单芯片系统(SOPC)――能够提供基于PLD的处理器。

在2000年,Altera发布了Nios处理器,这是Altera Excalibur嵌入处理器计划中第一个产品,它成为业界第一款为可编程逻辑优化的可配置处理器。

本文阐述开发Nios处理器设计环境的过程和涉及的决策,以及它如何演化为一种SOPC工具。

Altera很清楚地意识到,如果我们把可编程逻辑的固有的优势集成到嵌入处理器的开发流程中,我们就会拥有非常成功的产品。

基于PLD的处理器恰恰具有应用所需的特性。

一旦定义了处理器之后,设计者就“具备”了体系结构,可放心使用。

因为PLD和嵌入处理器随即就生效了,可以马上开始设计软件原型。

CPU周边的专用硬件逻辑可以慢慢地集成进去,在每个阶段软件都能够进行测试,解决遇到的问题。

GW48PK2S实验系统说明

功能可重购的8个发光管:D16-D9

ቤተ መጻሕፍቲ ባይዱ

系统复位键

功能可重购的8个发光管:D16-D9

4X4键盘/液晶接口 SD卡口

GWA1C6A型适配板

立体声输出 以太网口

USB口

KX

康芯科技

PS2口

CPLD

麦克风输入

数字声输入

RS232串口

跳线向上接20MHz FPGA与实验主系统接口 跳线向下接Clock0 实验用FPGA 全彩色VGA口 Clock0跳线选择时钟

JTAG口

EPCS1 Flash 高速ADC/DAC板

SOPC用RAM/Flash板插口

IP核复位键

KX

康芯科技

ByterBlasterMV编程口

液晶显示/4X4键盘控制口

4行X20字液晶显示器

KX

直流电机与步进电机控制口

康芯科技

DDS函数信号发生器板插口

+/-12V电压开关 接PC机并口 FPGA I/O口 IP核复位键

KX

康芯科技

GW48-PK2S型EDA/SOPC 实验开发系统

杭州康芯电子有限公司

GW48-PK2S型EDA/SOPC实验开发系统

KX

康芯科技

4行X20字字符型液晶

KX

康芯科技

实验电路模式显示

4X4键盘

实验电路模式选择键

KX

康芯科技

模式显示

决定重购电路的模式选择键

功能可重购的8个数码管

功能可重购的8个发光管:D8-D1

KX

康芯科技

KX

康芯科技

KX

I/O开关 VGA接的I/O口说明 VGA口

康芯科技

16个与FPGA接的发光管

8位并行加法器的设计

实验一:8位加法器的设计1.实验目的(1)学习isEXPERT/MAX+plus Ⅱ/Foudation Series软件的基本使用方法。

(2)学习GW48-CK EDA实验开发系统的基本使用方法。

(3)了解VHDL程序的基本结构。

2.实验内容设计并调试一个由两个4位二进制并行加法器级联而成的8位二进制并行加法器,并用GW48_CK EDA实验开发系统(拟采用的实验芯片的型号为isPLSI1032E OLCC_84)进行硬件验证。

3.实验条件(1)画出系统的原理框架图,说明系统中各主要部分的功能。

(2)编写各个VHDL源程序。

(3)根据选用的软件编好用于系统仿真的测试文件。

(4)根据选用的软件及EDA实验开发装置编好用于硬件验证的管脚锁定文件。

(5)记录系统仿真、硬件验证结果。

(6)记录式样过程中出现的问题及解决方法。

4.实验设计(1)系统原理图框架4位二进制并行加法器2个4位二进制并行加法器级联而成的8位加法器(2)VHDL源程序1)4位二进制并行加法器的源代码adder4b.vhdlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder4b isport(c4:in std_logic;a4:in std_logic_vector(3 downto 0);b4:in std_logic_vector(3 downto 0);s4:out std_logic_vector(3 downto 0);co4:out std_logic);end entity adder4b;architecture art of adder4b issignal s5:std_logic_vector(4 downto 0);signal a5,b5:std_logic_vector(4 downto 0);begina5<='0'&a4;b5<='0'&b4;s5<=a5+b5+c4;s4<=s5(3 downto 0);co4<=s5(4);end architecture art;2)8位二进制并行加法器的源代码adder8b.vhdlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder8b isport(c8:in std_logic;a8:in std_logic_vector(7 downto 0);b8:in std_logic_vector(7 downto 0);s8:out std_logic_vector(7 downto 0);co8:out std_logic);end entity adder8b;architecture art of adder8b iscomponent adder4b isport(c4:in std_logic;a4:in std_logic_vector(3 downto 0);b4:in std_logic_vector(3 downto 0);s4:out std_logic_vector(3 downto 0);co4:out std_logic);end component adder4b;signal sc:std_logic;beginu1:adder4bport map(c4=>c8,a4=>a8(3 downto 0),b4=>b8(3 downto 0), s4=>s8(3 downto 0),co4=>sc);u2:adder4bport map(c4=>sc,a4=>a8(7 downto 4),b4=>b8(7 downto 4),s4=>s8(7 downto 4),co4=>co8);end architecture art;(3)波形仿真文件Module adder8b;C8,a8[7..0],b8[7..0],s8[7..0],co8 pin;Test_vectors(C8,a8[7..0],b8[7..0]->s8[7..0],co8);[0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,]->[x,x,x,x,x,x,x,x,x]; [1,0,0,0,1,0,0,0,1,0,0,0,1,0,0,0,1,]->[x,x,x,x,x,x,x,x,x]; [0,0,0,1,0,0,0,1,0,0,0,1,0,0,0,1,0,]->[x,x,x,x,x,x,x,x,x]; [1,0,0,1,1,0,0,1,1,0,0,1,1,0,0,1,1,]->[x,x,x,x,x,x,x,x,x]; [0,0,1,0,0,0,1,0,0,0,1,0,0,0,1,0,0,]->[x,x,x,x,x,x,x,x,x]; [1,0,1,0,1,0,1,0,1,0,1,0,1,0,1,0,1,]->[x,x,x,x,x,x,x,x,x]; [0,0,1,1,0,0,1,1,0,0,1,1,0,0,1,1,0,]->[x,x,x,x,x,x,x,x,x]; [1,0,1,1,1,0,1,1,1,0,1,1,1,0,1,1,1,]->[x,x,x,x,x,x,x,x,x]; [0,1,0,0,0,0,0,0,0,1,0,0,0,1,0,0,0,]->[x,x,x,x,x,x,x,x,x]; [1,1,0,0,1,1,0,0,1,1,0,0,1,1,0,0,1,]->[x,x,x,x,x,x,x,x,x]; [0,1,0,1,0,1,0,1,0,1,0,1,0,1,0,1,0,]->[x,x,x,x,x,x,x,x,x]; [1,1,0,1,1,1,0,1,1,1,0,1,1,1,0,1,1,]->[x,x,x,x,x,x,x,x,x]; [0,1,1,0,0,1,1,0,0,1,1,0,0,1,1,0,0,]->[x,x,x,x,x,x,x,x,x]; [1,1,1,0,1,1,1,0,1,1,1,0,1,1,1,0,1,]->[x,x,x,x,x,x,x,x,x]; [0,1,1,1,0,1,1,1,0,1,1,1,0,1,1,1,0,]->[x,x,x,x,x,x,x,x,x]; [1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,1,]->[x,x,x,x,x,x,x,x,x]; End;(4)管脚锁定文件管脚锁定设计图管脚锁定文件//adder8b.ppn//part: isPLSI1032E OLCC_84 //fromat:pinnanme pintype lock c8 in 11a87 in 73a86 in 17a85 in 19a84 in 2a83 in 29a82 in 60a81 in 44a80 in 1b87 in 69b86 in 18b85 in 16b84 in 42b83 in 27b82 in 53b81 in 84b80 in 43s87 out 71s86 out 70s85 out 59s84 out 58s83 out 62 s82 out 61 s81 out 28 s80 out 30 co8 out 725.实验结果及总结(1)系统仿真情况系统功能仿真结果时序仿真结果(2)硬件验证情况(3)实验开发过程中出现的问题及解决的方法1)在进行仿真时,value总会随着初始设定值的改变而改变,一开始不明白,总是去调节,后面发现者value的值就是设定的初始值的第一位值,对仿真并没影响,于是把他隐藏了。

日立空调机组GW协议转换器使用说明书

——目录——1.LONWORKS技术概况2.G/W协议转换器3.机组测的设定和接线4.试运行5.LONWORKS变量SNVT定义6.报警代码转换表1.LONWORKS技术概况美国Echelon公司1991年推出的LON技术,又称LONWORKS技术是计算机控制技术第三代的现场总线技术。

LONWORKS技术是一个实现控制网络系统的完整平台。

这些网络包括智能设备或节点。

括智能设备或节点与它们所处的环境进行交互作用,以及通过不同的通信介质与其它节点进行通信。

这种通信采用一种通用的、基于消息的控制协议-LONTALK协议。

由于LONTALK协议已固化在神经元芯片(微处理器)内,节点通过网络变量的形式交换信息,又有现成的网络管理工具进行网络管理。

所以建立一个LONWORKS控制网络在网络通讯上几乎不需要任何调试工作量。

LONWORKS技术的网络通信对用户是透明的,神经元芯片自动完成LONWORK S的所有七层的网络协议,用户所要作的只有两件事:第一件事是指定哪些信息是通过网络变量传递的,也就是定议网络变量;第二件事是指定信息传递传递的发起者和接收者,也就是做Binding(网络变量的捆绑)。

2.G/W协议转换器(其型号为HARC70-C)G/W协议转换器是日立公司提供的通信用网关设备(可简称G/W)。

是把广州日立冷机有限公司内部用的H-link通信协议转换成公开的LONTALK协议的设备。

是便于用户通过通信网络监控日立的冷水机组为目的开发的一种通信协议转换器。

1)系统构成方式以下是用G/W协议转换器联接到BMS(楼宇控制系统)系统时的系统构成简图。

对于构成系统的其它部品请参阅相应的使用说明书。

注意事项:1)冷水机组测的通信线上一定要加上附带的线圈和电容。

2)屏蔽线要采用D类接地标准备注:上位装置可使用LONWORKS /RS232C型的G/W(ECHELON制SLTA-10 通用的LONTALK 收发器等)及相应的软件。

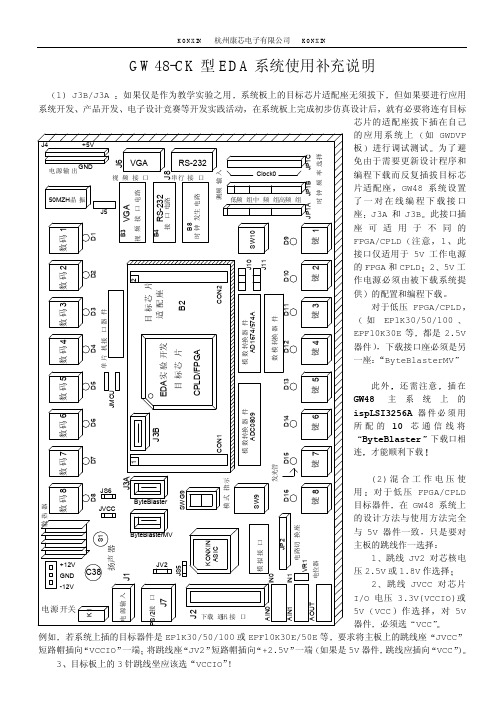

GW48补充说明1

杭州康芯电子有限公司

KONXIN

GW48-CK 型 EDA 系统使用补充说明

1) J3B/J3A 如果仅是作为教学实验之用 系统板上的目标芯片适配座无须拔下 但如果要进行应用 系统开发 产品开发 电子设计竞赛等开发实践活动 在系统板上完成初步仿真设计后 就有必要将连有目标 芯片的适配座拔下插在自己 的 应 用 系 统 上 如 GWDVP J4 +5V 板 进行调试测试 为了避 免由于需要更新设计程序和 VGA RS-232 GND 电源输 出 Clock0 编程下载而反复插拔目标芯 视 频 接 口 串行 接 口 片适配座 GW48 系统设置 低频 组中 频 组高频 组 50MZH晶 振 了一对在线编程下载接口 J5 座 J3A 和 J3B 此接口插 座 可 适 用 于 不 同 的 FPGA/CPLD 注意 1 此 接口仅适用于 5V 工作电源 的 FPGA 和 CPLD 2 5V 工 作电源必须由被下载系统提 供 的配置和编程下载 对于低压 FPGA/CPLD 如 EP1K30/50/100 EPF10K30E 等 都是 2.5V 下载接口座必须是另 器件 一座 ByteBlasterMV

D13

键4

D12

D4

键3

D11

D3

键2

D2

D10

2

键1

B3

D1

B4

D9

JP1A

时 钟 频 率 选择

测频 输 入

J8

JP1B

JP1C

J6

数码7

(2) 混 合 工 作 电 压 使 用 对 于 低 压 FPGA/CPLD ByteBlaster 目标器件 在 GW48 系统上 JVCC 的设计方法与使用方法完全 与 5V 器件一致 只是要对 ByteBlasterMV 主板的跳线作一选择 1 跳线 JV2 对芯核电 +12V JV2 压 2.5V 或 1.8V 作选择 C38 GND 2 跳线 JVCC 对芯片 -12V I/O 电压 3.3V(VCCIO)或 电源开关 5V VCC 作 选 择 对 5V 下载 通 接 口 讯 器件 必须选 VCC 例如 若系统上插的目标器件是 EP1K30/50/100 或 EPF10K30E/50E 等 要求将主板上的跳线座 JVCC 短路帽插向 VCCIO 一端 将跳线座 JV2 短路帽插向 +2.5V 一端 如果是 5V 器件 跳线应插向 VCC 3 目标板上的 3 针跳线坐应该选 VCCIO

数字电子锁报告及VHDL源程序

一、系统功能概述数字密码锁实现:1、了不需要带钥匙,只要记住开锁密码即可开锁的功能。

2、在输入密码正确后,还可以修改密码。

3、在输入密码的过程中,不显示密码,只显示无规律的提示某位密码是否输入完毕,防止了密码的泄漏,大大加强了密码锁的保密性。

本演示系统实现了:1、输入密码正确后,正确小灯(led)亮,错误小灯(led1)不亮;2、正确修改密码后,正确小灯(led)不亮,错误小灯(led1)不亮;3、输入错误密码,正确小灯(led)不亮,错误小灯(led1)亮,并有1KHz闹铃声产生;4、按下reset后,密码归为初始密码。

开锁代码为8位二进制数,当输入代码的位数和位值与锁内给定的密码一致,且按规定程序开锁时,方可开锁,并点亮开锁指示灯D3。

否则系统进入“错误”状态,并发出报警信号。

开锁程序由设计者确定,并锁内给定的密码是可调的,且预置方便,保密性好。

串行数字锁的报警方式是点亮指示灯D6,并使喇叭鸣叫来报警,报警动作直到按下复位开关,报警才停止。

此时,数字锁自动进入等待下一次开锁的状态。

二、系统组成以及系统各部分的设计1、系统结构描述要求:系统(或顶层文件)结构描述,各个模块(或子程序)的功能描述;(1)源代码;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity code isport( c lk: in std_logic;--电路工作时的时钟信号clk1:in std_logic;--闹铃产生需要的时钟信号k: in std_logic;--高电平表示输入1led: out std_logic;--输入正确时亮led1:out std_logic;--输入错误时亮reset: in std_logic;-- 按下时复位want: in std_logic;--是否修改密码alarm: out std_logic;--输出闹铃声show: out std_logic_vector(3 downto 0));--提示作用end;architecture a of code issignal temp: std_logic_vector(3 downto 0);--输入一位加1signal code: std_logic_vector(7 downto 0);--储存密码signal getcode: std_logic_vector(7 downto 0);--储存修改后的密码signal counter: std_logic_vector(3 downto 0);--计数signal allow: std_logic;--是否允许修改密码signal ring:std_logic;--是否接通闹铃beginprocess(clk)beginif ring='1' thenalarm<=clk1;--闹铃接通elsealarm<='0';--闹铃截至end if;if reset='1' then--按下reset后,密码归为初始密码getcode<="00000000";--初始密码counter<="0000";--内部计数code<="11001000";--密码led<='0';led1<='0';allow<='0';elsif clk'event and clk='1' then--输入clk脉冲,则接收1位密码getcode<=getcode(6 downto 0)&k;--将这1位密码并入getcode中的最后一位if counter="1000" then--输入为8位数码时比较if code=getcode thenled<='1';--正确灯亮led1<='0';ring<='0';allow<='1';--允许修改密码elsif allow='1' and want='1' then--如果允许输入且想输入code<=getcode;--输入新密码led<='0';led1<='0';elseallow<='0';led<='0';led1<='1';--错误灯亮ring<='1';--闹铃响end if;counter<="0000";--重新计数elsecounter<=counter+1; --累加temp<=temp+1;--为防止泄露密码,特别设置end if;end if;show <= temp;end process;end;2、系统以及各个模块的仿真波形(1)错误输入密码时的仿真波形(2)输入正确密码时的仿真波形3、下载时选择的开发系统模式以及管脚定义表1 GW48-CK开发系统工作模式:5我设计的数字密码锁简单、实用,基本满足课程设计的要求,并且在单个模块运行状态下,可以实现所有的要求。

德国瑞德GW系列用户使用说明书

2 安全.............................................................5 2.1 遵守指导说明................................................ 5 2.2 警告标志和符号解释........................................5 2.3 避免危险...................................................... 5 2.4 预期用途...................................................... 5 2.5 操作安全的基本说明........................................6

4.9 连接燃气管,针对燃气类型检查燃烧器设置........... 20 4.9.1 燃气管连接的重要说明...............................20 4.9.2 连接燃气管...............................................20 4.9.3 进入设备内部...........................................20 4.9.4 检查燃烧器的预先设置...............................21

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子设计自动化课程设计指导书主要技术:VerilogHDL;Protel;FPGA;EPLD设计内容:1、VerilogHDL●简易电子琴●数字式秒表●简易数字频率计●A/D采样控制器●任意波形发生器2、Protel●Schematic绘制●PCB绘制南通大学电子信息学院二00六年六月课程设计指导书一、目的:课程设计是教学中的一个重要环节,对学生来说是一次工程技术人员工作的锻炼,通过课程设计,学生不仅可以系统地复习、巩固本课程的基本知识,而且还可以学到如何把书本上的知识运用于解决工程实际问题的方法。

随着电子技术的迅猛发展,传统的电子设计方法设计周期长、设计成本高、安装调试复杂,尤其是大规模、较复杂的电子线路设计,已明显跟不上电子技术飞速发展的需要。

本课程设计采用电子线路计算机辅助设计手段,让学生掌握最新的数字电子线路设计和分析方法,培养学生运用先进的电子设计自动化(EDA)技术进行电子线路设计和分析的能力。

通过本课程设计,学生应达到以下要求:1、掌握电子线路的一般设计方法及步骤;2、较熟练地使用电子线路计算机辅助设计软件QuartusII和Protel;3、比较熟练地使用常用的集成电路、晶体管元器件手则;4、学会运用计算机辅助设计软件对所设计的电子线路进行分析和调试;5、学会编制设计文件、绘制较为复杂的电子线路图。

二、要求:1、设计与计算学生根据所选课题的任务、要求和条件进行总体案的设计,通过论证与选择,确定总体方案。

此后运用计算机辅助设计软件对方案中单元电路进行详细的逻辑设计(包括元器件的选用和电路参数的计算)、仿真分析,同时画出电路及仿真图。

2、安装与调试学生设计的逻辑电路经指导教师审查通过后,学生即可向实验室领取实验箱,进行编程(下载),测试是否达到设计要求,针对发现的问题进行电路修改,调整元器件,排除电路故障,并重新下载调试和测试,使之达到设计要求。

3、撰写总结报告总结报告是学生对课程设计全过程的系统总结,学生应按规定的格式编写设计说明书,说明书的主要内容有:①课题名称②设计任务和要求。

③方案选择与论证。

④方案的原理框图,电路图,以及它们的说明;单元电路的设计与计算说明;EPLD芯片引脚的使用说明;电路仿真分析时序图和分析说明等。

⑤电路调试。

对调试中出现的问题进行分析,并说明解决的措施;测试、记录、整理与结果分析。

⑥收获体会、存在的问题和进一步的改进意见等。

三、成绩评定-2-课程设计指导书课程设计结束后,教师将根据以下几方面来评定成绩:1、设计方案的正确性与合理性。

2、能较好地掌握和使用EDA软件,具备在安装调试中分析解决问题的能力以及创新能力等。

3、总结报告。

4、答辩情况(课程的论证和回答问题的情况)。

5、设计过程中的学习态度、工作作风和科学精神。

四、设计题目(设计题目为两部分,VerilogHDL部分选2题,Protel部分选一题。

)VerilogHDL部分1、简易电子琴设计任务与要求:①设计并制作一个简易电子琴。

②音阶信号发生器能产生1-1共8个音阶信号。

③同时按下两键时,只发出一个音阶信号。

2、数字式秒表设计任务与要求:①设计并制作符合要求的电子秒表。

②秒表由6位七段LED显示器显示,其中两位显示“分”,两位显示“秒”,两位显示百分秒(分辨率为0.01秒)。

③计时最大值为99分59.99秒,误差小于0.01秒。

④具有清零、启动计时、暂停计时、继续计时等功能。

⑤控制操作按键不得超过2个。

3、简易数字频率计设计任务与要求:①设计一个数字频率计,闸门时间为1秒,最高可测频率为100MHZ。

②频率由8位数码管显示输出。

4、A/D采样控制器设计任务与要求:①利用CPLD或FPGA目标器件设计一采样控制器,按照正确的时序直接控制ADC0809的工作(选择一个通道工作)。

②A/D转换结果由数码管显示。

③调节输入信号大小,A/D转换结果即随着变化。

④选择适当的工作频率-3-课程设计指导书-4- 5、任意波形发生器设计任务与要求:①利用CPLD或FPGA目标器件设计一任意波形波形发生器,按照正确的时序直接控制DAC0832的工作。

波形数据存储在LPM_ROM中。

②输出波形的频率由一个键在几种频率中切换。

③由一个键作为选择控制,使DAC0832产生三角波或正弦波。

Protel部分1、schematic绘制;2、PCB绘制。

五、时间安排二周课程设计安排:第一天至第二天:学习使用EDA软件、了解实验箱的功能(由教师讲解并辅导);第三天至第七天:选择设计题目,确定设计方案,查阅有关集成电路和电子元器件手则;上机进行电路设计和仿真分析;第八天至第九天:对芯片编程,进行电路调试;第十天:整理资料,撰写课程设计报告。

六、设计软件与器材1、Quartus Ⅱ软件、Protel软件;2、EDA实验箱附录1.GW48 EDA系统使用说明第一节GW48教学实验系统原理与使用介绍第二节实验电路结构图第三节GW48CK/GK EDA系统和GWDVP-B应用板2.Protel绘制schematic、PCB方法课程设计指导书附录1:GW48 EDA系统使用说明第一节 GW48教学实验系统原理与使用介绍一、GW48系统使用注意事项a:闲置不用GW48 EDA系统时,关闭电源,拔下电源插头!!!b:EDA软件安装方法可参见光盘中相应目录中的中文README.TXT;详细使用方法可参阅本书或《EDA技术实用教程》、或《VHDL实用教程》中的相关章节。

c:在实验中,当选中某种模式后,要按一下右侧的复位键,以使系统进入该结构模式工作。

d:换目标芯片时要特别注意,不要插反或插错,也不要带电插拔,确信插对后才能开电源。

其它接-5-课程设计指导书-6-口都可带电插拔(当适配板上的10芯座处于左上角时,为正确位置)。

e :系统板上的空插座是为单片机AT89C2051准备的,除非进行单片机与FPGA/CPLD 的接口实验和开发,平时在此座上不允许插有任何器件,以免与系统上的其它电路发生冲突。

单片机与系统的连接情况可参阅以下的附图2-13。

该单片机和相应的编程器需自备或另购。

f :对工作电源为5V 的CPLD (如1032E/1048C 、95108或7128S 等)下载时。

最好将系统的电路“模式”切换到“ b ”,以便使工作电压尽可能接近5V 。

g:GW48详细使用方法可参见教学软件:EDA-VHDL 多媒体CAI.ppt二、GW48系统主板结构与使用方法附图1-1C 为GW48型EDA 实验开发系统的主板结构图,该系统的实验电路结构是可控的。

即可通过控制接口键SW9,使之改变连接方式以适应不同的实验需要。

因而,从物理结构上看,实验板的电路结构是固定的,但其内部的信息流在主控器的控制下,电路结构将发生变化。

这种“多任务重配置”设计方案的目的有3个:1.适应更多的实验与开发项目;2. 适应更多的PLD 公司的器件;3. 适应更多的不同封装的FPGA 和CPLD 器件。

系统板面主要部件及其使用方法说明如下。

以下是对GW48系统主板功能块的注释,但请注意,有的功能块仅GW48-GK 系统存在:(1) SW9 :按动该键能使实验板产生12种不同的实验电路结构。

这些结构如第二节的13 张实验电路结构图所示。

例如选择了“NO.3”图,须按动系统板上的SW9键,直至数码管SWG9显示“3”,于是系统即进入了(2) B2 用的目标芯片包括目前世界上最大的六家FPGA/CPLD 厂商几乎所有CPLD 、FPGA 和所有ispPAC 等模拟EDA 器件 。

第三节的表中已列出多种芯片对系统板引脚的对应关系,以利在实验时经常查用。

(3) J3B/J3A :如果仅是作为教学实验之用,系统板上的目标芯片适配座无须拔下,但如果要进行应用系统开发、产品开发、电子设计竞赛等开发实践活动,在系统板上完成初步仿真设计后,就有必要将连有目标芯片的适配座拔下插在自己的应用系统上(如GWDVP 板)进行调试测试。

为了避免由于需要更新设计程序和编程下载而反复插拔目标芯片适配座,GW48系统设置了一对在线编程下载接口座:附图1-1B 、GW48系统目标板插座引脚信号图附表1-1 在线编程坐各引脚与不同PLD 公司器件编程下载接口说明课程设计指导书J3A和J3B。

此接口插座可适用于不同的FPGA/CPLD(注意,1、此接口仅适用于5V工作电源的FPGA 和CPLD;2、5V工作电源必须由被下载系统提供)的配置和编程下载。

对于低压FPGA/CPLD,(如EP1K30/50/100、EPF10K30E等,都是2.5V器件),下载接口座必须是另一座:ByteBlasterMV。

(4)混合工作电压使用:对于低压FPGA/CPLD目标器件,在GW48系统上的设计方法与使用方法完全与5V器件一致,只是要对主板的跳线作一选择(见GW48系统主板):JV2:跳线JV2对FPGA/CPLD芯核电压2.5V或1.8V作选择;SEL18:此跳线仅GW48-GK系统设有。

跳线SEL18选择“AH18”(对于普通GW48-GK系统);选择“BH18”(对于ASIC实验系统GW48-GK/IC)。

JVCC:跳线JVCC对芯片I/O电压3.3V(VCCIO)或5V(VCC)作选择,对5V器件,必须选“5.0V”。

例如,若系统上插的目标器件是EP1K30/50/100或EPF10K30E/50E等,要求将主板上的跳线座“JVCC”短路帽插向“3.3V”一端;将跳线座“JV2”短路帽插向“+2.5V”一端(如果是5V器件,跳线应插向“5.0V”)。

(5)并行下载口:此接口通过下载线与微机的打印机口相连。

来自PC机的下载控制信号和CPLD/FPGA 的目标码将通过此口,完成对目标芯片的编程下载。

编程电路模块能自动识别不同的CPLD/FPGA芯片,并作出相应的下载适配操作。

(6)键1~键8 :为实验信号控制键,此8个键受“多任务重配置”电路控制,它在每一张电路图中的功能及其与主系统的连接方式随SW9的模式选择而变,使用中需参照第二节中的电路图。

-7-课程设计指导书方法参考“实验电路结构 NO.5”。

(10)“时钟频率选择”P1A/JP1B/JP1C :为时钟频率选择模块。

通过短路帽的不同接插方式,使目标芯片获得不同的时钟频率信号。

对于“CLOCK0”JP1C,同时只能插一个短路帽,以便选择输向“CLOCK0”的一种频率:信号频率范围:0.5Hz – 100MHz(对GW48-GK系统),由于CLOCK0可选的频率比较多,所以比较适合于目标芯片对信号频率或周期测量等设计项目的信号输入端。

JP1B分三个频率源组,即如系统板所示的“高频组”、“中频组”和“低频组”。

它们分别对应三组时钟输入端。