Verilog课题

verilog语法题

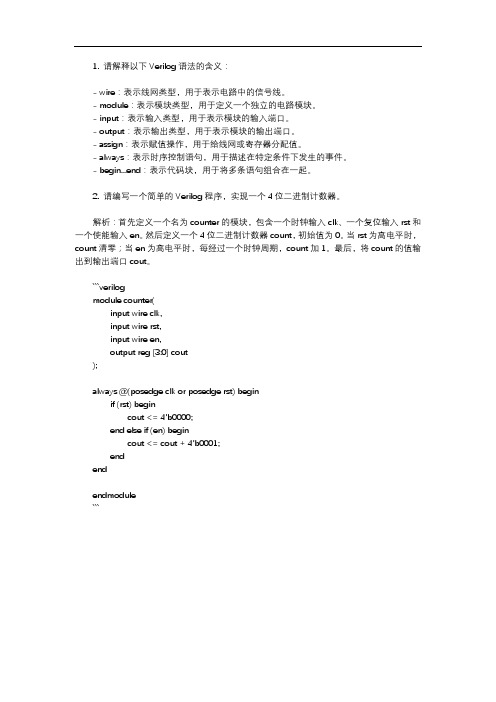

1. 请解释以下Verilog语法的含义:

- wire:表示线网类型,用于表示电路中的信号线。

- module:表示模块类型,用于定义一个独立的电路模块。

- input:表示输入类型,用于表示模块的输入端口。

- output:表示输出类型,用于表示模块的输出端口。

- assign:表示赋值操作,用于给线网或寄存器分配值。

- always:表示时序控制语句,用于描述在特定条件下发生的事件。

- begin...end:表示代码块,用于将多条语句组合在一起。

2. 请编写一个简单的Verilog程序,实现一个4位二进制计数器。

解析:首先定义一个名为counter的模块,包含一个时钟输入clk、一个复位输入rst和一个使能输入en。

然后定义一个4位二进制计数器count,初始值为0。

当rst为高电平时,count清零;当en为高电平时,每经过一个时钟周期,count加1。

最后,将count的值输出到输出端口cout。

```verilog

module counter(

input wire clk,

input wire rst,

input wire en,

output reg [3:0] cout

);

always @(posedge clk or posedge rst) begin

if (rst) begin

cout <= 4'b0000;

end else if (en) begin

cout <= cout + 4'b0001;

end

end

endmodule

```。

三次样条的s曲线加减速算法 verilog

《三次样条的s曲线加减速算法 verilog》1. 引言在近年来的工程实践中,对于加减速算法的需求越来越迫切。

特别是在Verilog领域,随着数字逻辑设计的复杂度不断提升,对于运动控制的要求也日益严格。

三次样条的s曲线加减速算法成为现代Verilog设计中的一个热门话题。

本文将从深度和广度两个方面进行全面评估,并据此撰写有价值的文章。

2. 三次样条的s曲线加减速算法2.1 三次样条曲线简介三次样条曲线是一种用于模拟和逼真地描述曲线轨迹的方法。

它通过一系列的插值点来构建平滑的曲线,具有良好的光滑性和连续性。

在Verilog设计中,三次样条曲线常常被用于描述运动轨迹,实现精确的加减速控制。

2.2 S曲线加减速算法S曲线是一种具有平滑加减速过程的曲线形状。

其特点是起始和结束的加减速过程较为平滑,可以有效减少机械系统的冲击和损耗。

在Verilog设计中,S曲线加减速算法常常被应用于运动控制系统,以实现高效、精准的运动控制。

3. 从简到繁,由浅入深地探讨三次样条的s曲线加减速算法3.1 算法基础在Verilog中,实现S曲线加减速算法的关键是理解三次样条曲线的原理和计算方法。

通过插值和数学建模,可以得到在Verilog中实现S曲线加减速的数学表达式和计算方法。

3.2 Verilog实现通过Verilog HDL语言,可以将S曲线加减速算法实现为硬件逻辑。

利用FPGA或ASIC等数字逻辑芯片,可以将S曲线加减速算法应用于实际的运动控制系统中。

3.3 实际应用结合实际的机械系统和运动控制需求,可以将S曲线加减速算法应用于各种场景中,实现高效、精准的运动控制。

机械臂、CNC数控机床、自动化生产线等领域都可以受益于S曲线加减速算法的应用。

4. 主题文字的多次提及在上述内容中,我们多次提到了“三次样条的s曲线加减速算法”,这是我们在本文中关注的核心主题。

其在Verilog设计中的应用对于实现精准、高效的运动控制具有重要意义。

Verilog设计练习十例及答案

设计练习进阶前言:在前面九章学习的基础上,通过本章的练习,一定能逐步掌握Verilog HDL设计的要点。

我们可以先理解样板模块中每一条语句的作用,然后对样板模块进行综合前和综合后仿真,再独立完成每一阶段规定的练习。

当十个阶段的练习做完后,便可以开始设计一些简单的逻辑电路和系统。

很快我们就能过渡到设计相当复杂的数字逻辑系统。

当然,复杂的数字逻辑系统的设计和验证,不但需要系统结构的知识和经验的积累,还需要了解更多的语法现象和掌握高级的Verilog HDL系统任务,以及与C语言模块接口的方法(即PLI),这些已超出的本书的范围。

有兴趣的同学可以阅读Verilog语法参考资料和有关文献,自己学习,我们将在下一本书中介绍Verilog较高级的用法。

练习一.简单的组合逻辑设计目的: 掌握基本组合逻辑电路的实现方法。

这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。

在Verilog HDL中,描述组合逻辑时常使用assign 结构。

注意equal=(a==b)1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

模块源代码:" qual(equal),.a(a),.b(b)); 简单时序逻辑电路的设计目的:掌握基本时序逻辑电路的实现。

在Verilog HDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。

在可综合的Verilog HDL模型,我们通常使用always块和@(posedge clk)或@(negedge clk)的结构来表述时序逻辑。

下面是一个1/2分频器的可综合模型。

eset(reset),.clk_in(clk),.clk_out(clk_out));endmodule仿真波形:练习:依然作clk_in的二分频clk_out,要求输出与上例的输出正好反相。

编写测试模块,给出仿真波形。

练习三. 利用条件语句实现较复杂的时序逻辑电路目的:掌握条件语句在Verilog HDL中的使用。

verilog实验报告

verilog实验报告Verilog实验报告引言:Verilog是一种硬件描述语言(HDL),用于设计和模拟数字电路。

它是一种高级语言,能够描述电路的行为和结构,方便工程师进行数字电路设计和验证。

本实验报告将介绍我在学习Verilog过程中进行的实验内容和所获得的结果。

实验一:基本门电路设计在这个实验中,我使用Verilog设计了基本的逻辑门电路,包括与门、或门和非门。

通过使用Verilog的模块化设计,我能够轻松地创建和组合这些门电路,以实现更复杂的功能。

我首先创建了一个与门电路的模块,定义了输入和输出端口,并使用逻辑运算符和条件语句实现了与门的功能。

然后,我创建了一个测试模块,用于验证与门的正确性。

通过输入不同的组合,我能够验证与门的输出是否符合预期。

接下来,我按照同样的方法设计了或门和非门电路,并进行了相应的测试。

通过这个实验,我不仅学会了使用Verilog进行基本门电路的设计,还加深了对逻辑电路的理解。

实验二:时序电路设计在这个实验中,我学习了如何使用Verilog设计时序电路,例如寄存器和计数器。

时序电路是一种具有状态和时钟输入的电路,能够根据时钟信号的变化来改变其输出。

我首先设计了一个简单的寄存器模块,使用触发器和组合逻辑电路实现了数据的存储和传输功能。

然后,我创建了一个测试模块,用于验证寄存器的正确性。

通过输入不同的数据和时钟信号,我能够观察到寄存器的输出是否正确。

接下来,我设计了一个计数器模块,使用寄存器和加法电路实现了计数功能。

我还添加了一个复位输入,用于将计数器的值重置为初始状态。

通过测试模块,我能够验证计数器在不同的时钟周期内是否正确地进行计数。

通过这个实验,我不仅学会了使用Verilog设计时序电路,还加深了对触发器、寄存器和计数器的理解。

实验三:组合电路设计在这个实验中,我学习了如何使用Verilog设计组合电路,例如多路选择器和加法器。

组合电路是一种没有状态和时钟输入的电路,其输出只取决于当前的输入。

《Verilog数字系统设计教程》夏宇闻第四版思考题答案(第2章)

《Verilog数字系统设计教程》夏宇闻第四版思考题答案(第2章)1.Verilog语⾔有什么作⽤?可描述顺序执⾏和并⾏执⾏的程序结构;⽤延迟表达式或事件表达式来明确的控制过程的启动时间;通过命名的事件来触发其它过程⾥的激活⾏为或停⽌⾏为;提供了条件如if-else,case等循环程序结构;提供了可带参数且⾮零延续时间的任务程序结构;提供了可定义新的操作符的函数结构;提供了⽤于建⽴表达式的算术运算符,逻辑运算符,位运算符;Verilog HDL语⾔作为⼀种结构化的语⾔⾮常适⽤于门级和开关级的模型设计;提供了⼀套完整的表⽰组合逻辑的基本元件的原话;提供了双向通路和电阻器件的原话;可建⽴MOS器件的电荷分享和电荷衰减动态模型;Verilog HDL的构造性语句可以精确地建⽴信号的模型;2.构成模块的关键词是什么?module,endmodule。

3.为什么说可以⽤Verilog构成⾮常复杂的电路结构?因为Verilog可描述顺序执⾏和并⾏执⾏的程序结构;⽤延迟表达式或事件表达式来明确的控制过程的启动时间;通过命名的事件来触发其它过程⾥的激活⾏为或停⽌⾏为;提供了条件如if-else,case等循环程序结构;提供了可带参数且⾮零延续时间的任务程序结构;提供了可定义新的操作符的函数结构;提供了⽤于建⽴表达式的算术运算符,逻辑运算符,位运算符;Verilog HDL语⾔作为⼀种结构化的语⾔⾮常适⽤于门级和开关级的模型设计;提供了⼀套完整的表⽰组合逻辑的基本元件的原话;提供了双向通路和电阻器件的原话;可建⽴MOS器件的电荷分享和电荷衰减动态模型Verilog HDL的构造性语句可以精确地建⽴信号的模型;4.为什么可以⽤⽐较抽象的描述来设计具体的电路结构?因为有可以⽤⽐较抽象描述设计电路结构的语⾔,⽽这种语⾔是适合数字系统设计的语⾔。

5.是否任意抽象的符合语法的Verilog模块都可以通过综合⼯具转变为电路结构?不能。

verilog代码练习题

verilog代码练习题Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。

在学习和掌握Verilog代码编写的过程中,练习题是非常重要的一环。

通过多做一些练习题,可以提高对Verilog语言的理解和运用能力,进而更好地应对实际的电路设计和开发项目。

本文将介绍一些常见的Verilog代码练习题,帮助读者提升自己的编程能力。

具体的练习题如下:练习题一:整数加法器设计一个4位整数加法器,输入两个4位的二进制整数A和B,输出它们的和。

请使用Verilog代码描述该加法器,并给出仿真结果和波形图。

练习题二:时钟分频器设计一个时钟分频器,将输入时钟信号分频为两个输出时钟信号。

其中,输出时钟信号A频率为输入时钟信号的一半,输出时钟信号B 频率为输入时钟信号的四分之一。

请使用Verilog代码描述该时钟分频器,并给出仿真结果和波形图。

练习题三:数字比较器设计一个4位数字比较器,输入两个4位的二进制整数A和B,输出A是否大于B的结果(1表示大于,0表示不大于)。

请使用Verilog代码描述该数字比较器,并给出仿真结果和波形图。

练习题四:有限状态机设计一个简单的有限状态机,实现一个计数器的功能。

输入信号CLK表示时钟信号,每个上升沿计数器加1,输出信号OUT表示计数器的值,初始值为0,最大值为9,超出后回到0。

请使用Verilog代码描述该有限状态机,并给出仿真结果和波形图。

练习题五:位宽可调的加法器设计一个位宽可调的加法器,输入为两个任意位宽的二进制整数A和B,输出为它们的和。

请使用Verilog代码描述该位宽可调的加法器,并给出仿真结果和波形图。

以上是几个常见的Verilog代码练习题,通过多做这些练习题,可以提高对Verilog语言的掌握和运用能力。

在实际的电路设计和开发中,良好的Verilog编程能力是非常重要的。

希望本文对你有所帮助,加油!。

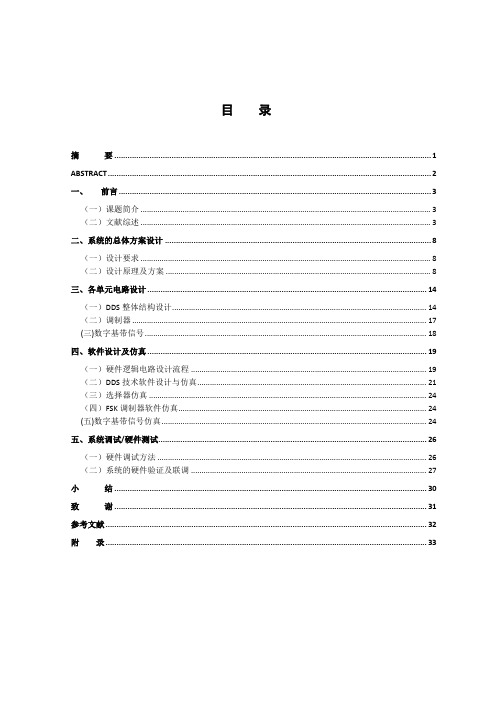

基于Verilog的FSK调制器的设计与实现

目录摘要 (1)ABSTRACT (2)一、前言 (3)(一)课题简介 (3)(二)文献综述 (3)二、系统的总体方案设计 (8)(一)设计要求 (8)(二)设计原理及方案 (8)三、各单元电路设计 (14)(一)DDS整体结构设计 (14)(二)调制器 (17)(三)数字基带信号 (18)四、软件设计及仿真 (19)(一)硬件逻辑电路设计流程 (19)(二)DDS技术软件设计与仿真 (21)(三)选择器仿真 (24)(四)FSK调制器软件仿真 (24)(五)数字基带信号仿真 (24)五、系统调试/硬件测试 (26)(一)硬件调试方法 (26)(二)系统的硬件验证及联调 (27)小结 (30)致谢 (31)参考文献 (32)附录 (33)摘要FSK(Frequency-shift keying)是信息传输中使用得较早的一种调制方式,它实现起来较容易,抗噪声与抗衰减的性能较好,在中低速数据传输中得到了广泛的应用。

而DDS(Direct Digital Synthesizer)是直接数字式频率合成器的英文缩写,和DSP(digital signal processor)——数字信号处理一样,DDS是一种很重要的数字化技术。

与传统的频率合成器相比,DDS的优点有低成本、低功耗、高分辨率和快速转换时间,它广泛地运用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

而本课题设计的基于Verilog的FSK调制器,就是采用EDA技术,以FPGA 为核心,在DDS技术的基础上实现FSK调制器的设计。

设计中用FPGA芯片完成各种时序逻辑控制、计数功能。

在Quartus Ⅱ平台上,用Verilog HDL语言编程完成了FPGA的软件设计、编译、调试、仿真和下载,在FPGA 上进行硬件的测试。

关键词: FSK调制器 DDS FPGA Quartus ⅡABSTRACTFSK (Frequency-shift keying) may be used for transmission of information of a modulation earlier, it is easier to implement, preferably anti-anti-noise and attenuation properties, has been widely used in low-speed data transmission. And a DSP (digital signal processor) - as digital signal processing, DDS is a very important digital technology. DDS (Direct Digital Synthesizer) yes yes direct digital frequency synthesizer abbreviation. Compared with the conventional frequency synthesizer, DDS has the advantage of low-cost, low-power, high resolution and fast conversion time, it is widely used in the field of telecommunications and electronic equipment, is to achieve full digital equipment is a key technology. The design of this project Verilog-based FSK modulator, is the use of EDA technology to FPGA as the core, FSK modulator based on DDS technology design.Complete a variety of designs using FPGA chip timing control logic, counting function. On the Quartus Ⅱ platform with Verilog HDL language programming complete FPGA design software, compiling, debugging, simulation and downloading, after the FPGA hardware tests.Keywords: FSK modulator DDS FPGA Quartus Ⅱ一、前言(一)课题简介1.设计目标直接数字式频率合成DDS技术是近年来发展起来的一种新的频率合成技术。

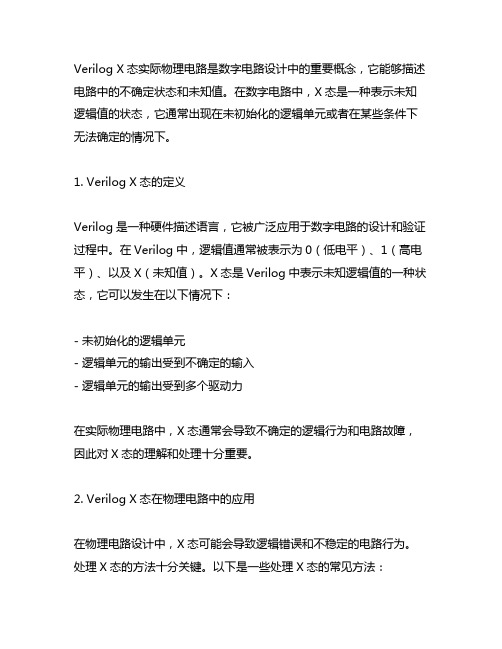

verilog x态 实际物理电路

Verilog X态实际物理电路是数字电路设计中的重要概念,它能够描述电路中的不确定状态和未知值。

在数字电路中,X态是一种表示未知逻辑值的状态,它通常出现在未初始化的逻辑单元或者在某些条件下无法确定的情况下。

1. Verilog X态的定义Verilog是一种硬件描述语言,它被广泛应用于数字电路的设计和验证过程中。

在Verilog中,逻辑值通常被表示为0(低电平)、1(高电平)、以及X(未知值)。

X态是Verilog中表示未知逻辑值的一种状态,它可以发生在以下情况下:- 未初始化的逻辑单元- 逻辑单元的输出受到不确定的输入- 逻辑单元的输出受到多个驱动力在实际物理电路中,X态通常会导致不确定的逻辑行为和电路故障,因此对X态的理解和处理十分重要。

2. Verilog X态在物理电路中的应用在物理电路设计中,X态可能会导致逻辑错误和不稳定的电路行为。

处理X态的方法十分关键。

以下是一些处理X态的常见方法:- 初始化在数字电路设计中,一种常见的方法是对逻辑单元进行初始化。

通过在设计中为逻辑单元赋初值,可以避免X态的出现。

对于寄存器或者存储单元,可以通过将其初始化为0或者1的方法来避免X态的出现。

- 严格的逻辑规划在设计物理电路时,可以采取严格的逻辑规划措施来避免X态的出现。

通过合理的逻辑规划和电路设计,可以最大程度地避免X态对电路的不确定影响。

- 逻辑层次仿真在数字电路设计的验证过程中,可以使用仿真工具对电路进行逻辑层次的仿真,以检测和排除X态对电路行为的不确定影响。

3. Verilog X态的处理挑战虽然Verilog语言提供了对X态的描述和处理机制,但是在实际物理电路中,处理X态依然是一个挑战。

由于X态往往会导致不确定的电路行为,因此在物理电路设计和验证中,需要特别注意处理X态的挑战。

- 不确定性X态往往会导致电路的不确定性,这对电路设计和验证带来了挑战。

在面对X态时,设计人员需要思考如何在逻辑上处理X态,并且在物理电路中采取相应的措施来避免X态对电路行为的影响。

《verilog_数字系统设计课程》(第二版)思考题答案

《verilog_数字系统设计课程》(第⼆版)思考题答案绪论1.什么是信号处理电路?它通常由哪两⼤部分组成?信号处理电路是进⾏⼀些复杂的数字运算和数据处理,并且⼜有实时响应要求的电路。

它通常有⾼速数据通道接⼝和⾼速算法电路两⼤部分组成。

2.为什么要设计专⽤的信号处理电路?因为有的数字信号处理对时间的要求⾮常苛刻,以⾄于⽤⾼速的通⽤处理器也⽆法在规定的时间内完成必要的运算。

通⽤微处理器芯⽚是为⼀般⽬的⽽设计的,运算的步骤必须通过程序编译后⽣成的机器码指令加载到存储器中,然后在微处理器芯⽚控制下,按时钟的节拍,逐条取出指令分析指令和执⾏指令,直到程序的结束。

微处理器芯⽚中的内部总线和运算部件也是为通⽤⽬的⽽设计,即使是专为信号处理⽽设计的通⽤微处理器,因为它的通⽤性也不可能为某⼀特殊的算法来设计⼀系列的专⽤的运算电路⽽且其内部总线的宽度也不能随便的改变,只有通过改变程序,才能实现这个特殊的算法,因⽽其算法速度也受到限制所以要设计专⽤的信号处理电路。

3.什么是实时处理系统?实时处理系统是具有实时响应的处理系统。

4.为什么要⽤硬件描述语⾔来设计复杂的算法逻辑电路?因为现代复杂数字逻辑系统的设计都是借助于EDA⼯具完成的,⽆论电路系统的仿真和综合都需要掌握硬件描述语⾔。

5.能不能完全⽤C语⾔来代替硬件描述语⾔进⾏算法逻辑电路的设计?不能,因为基础算法的描述和验证通常⽤C语⾔来做。

如果要设计⼀个专⽤的电路来进⾏这种对速度有要求的实时数据处理,除了以上C语⾔外,还须编写硬件描述语⾔程序进⾏仿真以便从电路结构上保证算法能在规定的时间内完成,并能通过与前端和后端的设备接⼝正确⽆误地交换数据。

6.为什么在算法逻辑电路的设计中需要⽤C语⾔和硬件描述语⾔配合使⽤来提⾼设计效率?⾸先C语⾔很灵活,查错功能强,还可以通过PLI编写⾃⼰的系统任务,并直接与硬件仿真器结合使⽤。

C语⾔是⽬前世界上应⽤最为⼴泛的⼀种编程语⾔,因⽽C程序的设计环境⽐Verilog HDL更完整,此外,C语⾔有可靠地编译环境,语法完备,缺陷缺少,应⽤于许多的领域。

Verilog 实验报告

Verilog 实验报告一、实验目的本次 Verilog 实验的主要目的是通过实际编写代码和进行仿真,深入理解 Verilog 语言的基本语法、逻辑结构和时序特性,掌握数字电路的设计方法和实现过程,并能够运用Verilog 实现简单的数字逻辑功能。

二、实验环境本次实验使用的软件工具是 Xilinx Vivado 20192,硬件平台是Xilinx Artix-7 开发板。

三、实验内容(一)基本逻辑门的实现1、与门(AND Gate)使用 Verilog 语言实现一个两输入的与门。

代码如下:```verilogmodule and_gate(input a, input b, output out);assign out = a & b;endmodule```通过编写测试激励文件对该模块进行仿真,验证其逻辑功能的正确性。

2、或门(OR Gate)同样实现一个两输入的或门,代码如下:```verilogmodule or_gate(input a, input b, output out);assign out = a | b;endmodule```3、非门(NOT Gate)实现一个单输入的非门:```verilogmodule not_gate(input a, output out);assign out =~a;endmodule```(二)组合逻辑电路的实现1、加法器(Adder)设计一个 4 位的加法器,代码如下:```verilogmodule adder_4bit(input 3:0 a, input 3:0 b, output 4:0 sum);assign sum = a + b;endmodule```2、减法器(Subtractor)实现一个 4 位的减法器:```verilogmodule subtractor_4bit(input 3:0 a, input 3:0 b, output 4:0 diff);assign diff = a b;endmodule```(三)时序逻辑电路的实现1、计数器(Counter)设计一个 4 位的计数器,能够在时钟上升沿进行计数,代码如下:```verilogmodule counter_4bit(input clk, output 3:0 count);reg 3:0 count_reg;always @(posedge clk) begincount_reg <= count_reg + 1;endassign count = count_reg;endmodule```2、移位寄存器(Shift Register)实现一个 4 位的移位寄存器,能够在时钟上升沿进行左移操作:```verilogmodule shift_register_4bit(input clk, input rst, output 3:0 data_out);reg 3:0 data_reg;always @(posedge clk or posedge rst) beginif (rst)data_reg <= 4'b0000;elsedata_reg <={data_reg2:0, 1'b0};endassign data_out = data_reg;endmodule```四、实验结果与分析(一)基本逻辑门的结果通过仿真,与门、或门和非门的输出结果与预期的逻辑功能完全一致,验证了代码的正确性。

verilog语言期末试题及答案

verilog语言期末试题及答案一、填空题1. Verilog语言是一种_硬件描述语言_。

2. Verilog语言适用于_数字电路设计_和_验证_。

3. Verilog的编译和仿真工具主要有_Synopsys Design Compiler_和_ModelSim_。

4. Verilog中的组合逻辑使用_always_关键字实现。

5. 时钟的上升沿触发使用_posedge_关键字实现。

6. Verilog的层次化模块定义使用_和号_(&)和_连接符_实现。

7. Verilog语言的数据类型包括_bit_、_reg_、_wire_和_logic_。

8. Verilog中用来控制模拟时间的关键字是_#_。

9. 顺序逻辑使用的关键字是_always_ff_。

10. Verilog的条件语句包括_if_、_else_和_case_。

二、选择题1. Verilog中的关键字always @(posedge clk)表示:A. 在时钟上升沿触发B. 在时钟下降沿触发C. 在时钟上升沿或下降沿触发D. 无关键字触发答案:A2. Verilog中用来定义模块的关键字是:A. alwaysB. moduleC. caseD. reg答案:B3. 下列哪个关键字用于在连续赋值中实现多路选择:A. ifB. elseC. caseD. always_ff答案:C4. Verilog中用来延时模拟时间的关键字是:A. #B. @C. $D. %答案:A5. Verilog中的数据类型wire和reg的区别在于:A. wire用于内部信号连接,reg用于存储数据B. wire只能传输数字信号,reg可以传输任意信号C. wire用于组合逻辑,reg用于时序逻辑D. wire在连续赋值中使用,reg在时序赋值中使用答案:A三、编程题请使用Verilog语言描述一个4位全加器模块,并画出其电路原理图。

```verilogmodule full_adder(input a, b, cin, output sum, cout);assign sum = a ^ b ^ cin;assign cout = (a & b) | (a & cin) | (b & cin);endmodule```四、简答题1. 请简述Verilog语言的优点及应用领域。

eda试题及答案verilog

eda试题及答案verilog1. 请解释Verilog中的阻塞赋值和非阻塞赋值的区别。

答案:在Verilog中,阻塞赋值使用`=`操作符,表示在赋值时会立即执行,并且赋值操作会阻塞后续语句的执行,直到当前赋值完成。

而非阻塞赋值使用`<=`操作符,表示赋值操作会在当前时间单位的末尾执行,不会阻塞后续语句的执行,允许并行执行。

2. 描述Verilog中模块的实例化过程。

答案:在Verilog中,模块的实例化是通过使用模块名后跟实例名和连接端口的列表来完成的。

实例化过程包括指定模块名、实例名以及将端口连接到适当的信号或参数上。

例如:```verilogmodule my_module(a, b, c);output a, c;input b;// ...endmodule// 实例化my_module instance_name(.out1(a), .out2(c), .in(b));```3. 列出Verilog中的基本数据类型。

答案:Verilog中的基本数据类型包括:- 线网类型(wire)- 寄存器类型(reg)- 实数类型(real)- 整型(integer)- 时间类型(time)- 字符串类型(string)4. 说明Verilog中如何使用条件语句。

答案:在Verilog中,可以使用`if`、`case`和`if-else`等条件语句来实现条件控制。

例如,使用`if`语句:```verilogif (condition) begin// 条件为真时执行的代码end else begin// 条件为假时执行的代码end```5. 解释Verilog中的always块的作用。

答案:Verilog中的always块用于描述硬件的时序逻辑和组合逻辑。

always块可以是时序的(使用时钟信号触发),也可以是非时序的(不依赖于时钟信号)。

时序always块通常用于描述寄存器行为,而非时序always块用于描述组合逻辑。

用Verilog实现题示电路实现四位二进制无符号数乘法计算(a3a2a1a0Xb3b2b1b0)

(二) 设计电路

该运算可由如下电路实现:

运算电路

-6-

(三)程序编写

根据电路,编写如下程序: module yunsuan(A,B,D); input [4:1] A,B; output[2*4:1] D; reg [2*4:1] D; integer i; always @(*) begin D=0; for(i=1;i<=4;i=i+1) if(B[i]) D=D+(A<<(i-1)); end endmodule

-8-

得到如下实验结果:

经过测试, 程序能够顺利执行四位二进制数的乘法, 计算结果与实际值符合。

三.设计总结

我们采用了分工合作, 互补互助的方式完成了此次设计。我们每人先设计其 中一道题目,然后交换彼此的设计与仿真结果,进行检查改进,最终顺利完成了 设计任务。 通过本次课程设计,基本掌握了由要求设计电路、由电路编写 VERILOG 语 言、 调试程序并解决问题的方式方法,使我们对于硬件描述语言有了一个基本的 了解,加深了对数电理论知识及其运用的理解能力。 本次设计最大的收获应该是学会了如何在设计中发现问题并解决问题, 然后 是学会了 Multisim 软件的基本使用方法。

-7-

.D(D) ); initial begin // Initialize Inputs A = 0; B = 0; // Wait 100 ns for global reset to finish #100; // Add stimulus here A=4'b1011; B=4'b1100; #100; A=4'b1000; B=4'b1111; #100; A=4'b1010; B=4'b0101; #100; end endmodule

verilog课程设计实验报告

verilog课程设计实验报告一、教学目标本课程旨在通过Verilog硬件描述语言的学习,让学生掌握数字电路设计的自动化工具,理解并实践硬件描述语言在数字系统设计中的应用。

通过本课程的学习,学生应达到以下目标:1.知识目标:–理解Verilog的基本语法和结构。

–掌握Verilog中的模块化设计方法。

–学习常用的Verilog描述技巧,包括逻辑门级建模、行为级建模和结构级建模。

2.技能目标:–能够运用Verilog语言进行简单的数字电路设计。

–学会使用至少一种Verilog仿真工具进行电路功能验证。

–能够阅读和理解Verilog代码,进行简单的代码优化。

3.情感态度价值观目标:–培养学生的团队合作意识,在实验报告中能够体现分工合作的精神。

–培养学生的问题解决能力,鼓励学生在遇到问题时积极寻找解决方案。

–培养学生对新技术的好奇心和学习兴趣,激发他们对电子工程领域的热爱。

二、教学内容依据教学目标,本课程的教学内容将围绕Verilog语言的基础知识、实践应用和项目设计展开。

教学大纲安排如下:1.第一部分:Verilog基础知识(2周)–介绍Verilog的背景和基本概念。

–详细讲解Verilog的数据类型、运算符和语句。

2.第二部分:模块化设计(2周)–讲解模块的定义和封装。

–实践模块的端口声明和模块实例化。

3.第三部分:数字电路的Verilog描述(2周)–通过实例教学,掌握逻辑门、触发器等基本组件的Verilog建模。

–学习组合逻辑和时序逻辑的设计方法。

4.第四部分:仿真与测试(1周)–学习使用仿真工具进行电路功能验证。

–理解并实践测试台(testbench)的编写。

5.第五部分:项目设计(3周)–小组合作完成一个较为复杂的数字系统设计项目。

–包括系统模块的划分、编码、仿真和测试。

三、教学方法为了提高学生的学习效果,将采用多种教学方法相结合的方式进行授课:1.讲授法:用于讲解Verilog的基本概念和语法。

CRC校验课程设计verilog

CRC校验课程设计verilog一、教学目标本课程的目标是让学生掌握CRC校验的基本原理,并能够使用Verilog进行CRC校验器的设计和仿真。

通过本课程的学习,学生应能够:1.描述CRC校验的基本原理和流程。

2.理解CRC校验码的生成方法和步骤。

3.使用Verilog编写CRC校验器的模块代码。

4.进行CRC校验器的仿真测试,验证其正确性。

二、教学内容本课程的教学内容主要包括以下几个部分:1.CRC校验的基本原理:介绍CRC校验的定义、原理和流程,以及CRC校验码的生成方法和步骤。

2.Verilog的基本语法:回顾Verilog的基本语法和编程技巧,为后续的CRC校验器设计打下基础。

3.CRC校验器的设计:讲解如何使用Verilog编写CRC校验器的模块代码,包括CRC校验码的生成和检查。

4.CRC校验器的仿真:介绍如何使用仿真工具进行CRC校验器的仿真测试,验证其正确性。

三、教学方法为了激发学生的学习兴趣和主动性,本课程将采用多种教学方法相结合的方式进行教学。

包括:1.讲授法:讲解CRC校验的基本原理和Verilog的基本语法。

2.案例分析法:通过分析实际案例,让学生理解CRC校验器的设计方法和步骤。

3.实验法:让学生动手编写Verilog代码,进行CRC校验器的仿真测试。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将准备以下教学资源:1.教材:选用《数字逻辑与计算机设计》作为主要教材,介绍CRC校验的基本原理和Verilog的语法。

2.参考书:提供《Verilog HDL权威指南》等参考书籍,供学生深入学习Verilog编程。

3.多媒体资料:制作PPT课件,生动展示CRC校验的基本原理和设计方法。

4.实验设备:提供计算机和仿真工具,让学生进行CRC校验器的仿真测试。

五、教学评估本课程的教学评估将采用多元化的评估方式,以全面、客观、公正地评价学生的学习成果。

评估方式包括:1.平时表现:通过课堂参与、提问、讨论等方式评估学生的学习态度和积极性。

verilog设计

Verilog 程序设计报告一、课题概述:任务:本实验主要完成8位比较器、分频器、阻塞赋值和非阻塞赋值的区别、8路的数据选择器、有限状态机的设计。

目的:通过实验掌握基本组合逻辑电路、时序逻辑电路的实现流程;条件语句及case语句的用法;在实验中认识阻塞赋值和非阻塞赋值的区别;能够设计出简单的有限状态机。

要求:熟练掌握verilog的基本语法知识和一些基本语句的用法。

二、设计思路及采取方案思路:(1)8位比较器可以用数据流描述方法(assign赋值语句)或行为描述方法(always语句)或结构描述方法(元件例化)实现。

(2)分频器可以采用if…else语句或case语句实现。

(3)阻塞赋值和非阻塞赋值的区别可以通过观察波形图及分析综合出的电路图来得到。

(4)8位数据选择器可以采用assign赋值语句及always语句实现。

(5)有限状态机可以采用case语句实现。

方案:(1)8位的比较器采用assign赋值语句实现。

(2)用if…else条件语句实现分频器的设计。

(3)通过观察波形图,得出利用阻塞赋值和非阻塞赋值设计电路的特点和区别。

(4)利用always语句实现8位数据选择器。

(5)利用case语句完成有限状态机的设计。

三、实验结果结果:我基本完成以上的5个任务,并且通过这些任务的完成,巩固了已经学过的知识,提高了自己的动手操作能力,坚定了继续学习的信心。

四、实验体会体会:第一次接触学习硬件编程语言,感受到verilog与软件编程语言有着许多显著的差别,最重要的是用verilog可以编出并行执行的程序,通过不断的学习和实践,习惯了用硬件结构思路编程,由于一些细节把握不到位,在设计中出现了许多错误;像进程赋值语句声明寄存器变量时格式出错、begin-end声明语句没有注意相互匹配、在声明语句的末尾忘了写上分号等等。

编译不成功时,我会不厌其烦的去查找错误,直至编译成功、满足题目的要求。

通过实验不仅巩固了已经学过的知识而且加强了自己的动手操作能力,为以后的考研及工作打下了基础。

verilog按键与led基础实验 实验小结

verilog按键与led基础实验实验小结在Verilog按键与LED基础实验中,我们主要学习了如何使用Verilog语言编写一个简单的数字电路,实现按键控制LED灯的亮灭。

以下是实验的主要内容和小结:1. 实验目的:通过本实验,我们旨在掌握Verilog的基本语法和结构,了解按键与LED灯的工作原理,学会使用Verilog编写简单的数字电路。

2. 实验原理:按键与LED灯的工作原理是:当按下按键时,按键产生一个低电平信号,这个信号经过电路处理后,驱动LED灯亮起;当松开按键时,按键产生的信号恢复为高电平,LED灯熄灭。

3. 实验步骤:a. 设计电路原理图:首先,我们需要设计一个简单的电路原理图,包括按键、LED灯、电阻等元件。

b. 编写Verilog代码:根据电路原理图,我们可以编写如下Verilog代码:verilogmodule key_led_test(input wire clk, // 时钟信号input wire rst, // 复位信号input wire btn, // 按键信号output wire led // LED灯信号);always @(posedge clk or posedge rst) beginif (rst) beginled <= 1'b0; // 复位时,LED灯熄灭end else beginif (btn) beginled <= 1'b1; // 按下按键时,LED灯亮起 end else beginled <= 1'b0; // 松开按键时,LED灯熄灭 endendendendmodulec. 仿真测试:将编写好的Verilog代码输入到仿真软件中,添加时钟、复位信号等输入信号,观察输出的LED灯状态是否符合预期。

4. 实验小结:通过本实验,我们学会了如何使用Verilog编写一个简单的数字电路,实现按键控制LED灯的亮灭。

verilog期末试题及答案

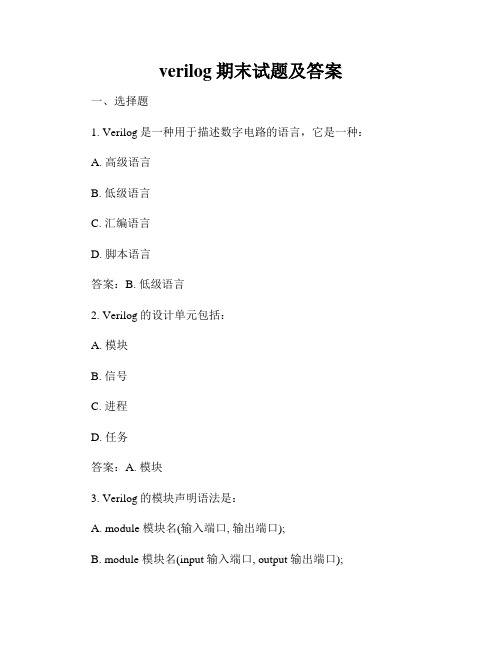

verilog期末试题及答案一、选择题1. Verilog是一种用于描述数字电路的语言,它是一种:A. 高级语言B. 低级语言C. 汇编语言D. 脚本语言答案:B. 低级语言2. Verilog的设计单元包括:A. 模块B. 信号C. 进程D. 任务答案:A. 模块3. Verilog的模块声明语法是:A. module 模块名(输入端口, 输出端口);B. module 模块名(input 输入端口, output 输出端口);C. 定义变量和信号D. 使用时调用模块答案:B. module 模块名(input 输入端口, output 输出端口);4. Verilog的赋值语句中,"="表示:A. 非阻塞赋值B. 阻塞赋值C. 非条件赋值D. 条件赋值答案:B. 阻塞赋值5. Verilog中的always块用于:A. 声明变量和信号B. 定义模块C. 并行执行代码块D. 顺序执行代码块答案:C. 并行执行代码块二、填空题1. Verilog的基本数据类型有______、______、______、______。

答案:wire, reg, integer, real2. Verilog中用于实现多路选择的关键字是______。

答案:case3. Verilog中用于实现循环的关键字是______。

答案:for4. Verilog中用于延迟执行的关键字是______。

答案:#(井号)5. Verilog中用于表示逻辑非的关键字是______。

答案:!三、简答题1. 请简要说明Verilog的模块和例化的概念。

答案:Verilog的模块是用于描述数字电路的基本单元,一个模块可以包含多个输入端口和输出端口,以及内部的逻辑代码。

模块可以被实例化(例化),即在其他模块中调用并使用。

例化时需要指定模块的名称,并连接相应的输入和输出端口。

2. 请简要说明Verilog中的阻塞赋值和非阻塞赋值的区别。

verilog hdl 习题答案

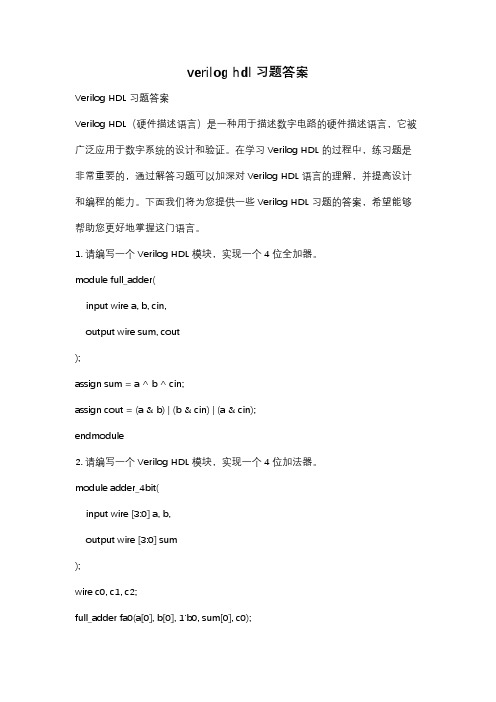

verilog hdl 习题答案Verilog HDL 习题答案Verilog HDL(硬件描述语言)是一种用于描述数字电路的硬件描述语言,它被广泛应用于数字系统的设计和验证。

在学习Verilog HDL的过程中,练习题是非常重要的,通过解答习题可以加深对Verilog HDL语言的理解,并提高设计和编程的能力。

下面我们将为您提供一些Verilog HDL习题的答案,希望能够帮助您更好地掌握这门语言。

1. 请编写一个Verilog HDL模块,实现一个4位全加器。

module full_adder(input wire a, b, cin,output wire sum, cout);assign sum = a ^ b ^ cin;assign cout = (a & b) | (b & cin) | (a & cin);endmodule2. 请编写一个Verilog HDL模块,实现一个4位加法器。

module adder_4bit(input wire [3:0] a, b,output wire [3:0] sum);wire c0, c1, c2;full_adder fa0(a[0], b[0], 1'b0, sum[0], c0);full_adder fa1(a[1], b[1], c0, sum[1], c1);full_adder fa2(a[2], b[2], c1, sum[2], c2);full_adder fa3(a[3], b[3], c2, sum[3], );endmodule3. 请编写一个Verilog HDL模块,实现一个4位移位寄存器。

module shift_register(input wire clk, rst, shift,input wire [3:0] in,output wire [3:0] out);reg [3:0] reg_data;always @(posedge clk or posedge rst) beginif(rst)reg_data <= 4'b0;else if(shift)reg_data <= {reg_data[2:0], in[0]};elsereg_data <= in;endassign out = reg_data;endmodule以上是一些常见的Verilog HDL习题的答案,通过这些习题的练习,相信您对Verilog HDL语言的掌握会更加深入。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

信号发生器设计仕样书

Rev. 1 2005-06-22 K.Ueno

1.适用

该仕样书适用于,Verilog-HDL 研修「信号发生器设计」.

2.名称

信号发生器

3.机能

Up Freq SW (SW3) : 输出频率步长100Hz

频率上升到9900Hz时停止工作

Down Freq SW (SW4) : 输出频率下降至100Hz

频率下降到0100Hz时停止工作

复位: 输出频率设定为1000Hz

4.性能

显示装置: 7 segment LED 4位 (共阴)

显示范围: 0100Hz ~ 9900Hz

最小显示: 100Hz

显示方式: 动态刷新模式

输出形式: TTL 水平 1bit 输出

5.工作模式

复位: 1000Hz 输出

频率up : 复位→1000Hz显示・输出

→Up Freq SW (SW3)→1100Hz显示・输出

频率down : 复位→1000Hz显示・输出

→Down Freq SW (SW4) →0900Hz显示・输出

上止点: 9800Hz显示・输出

→Up Freq SW (SW3)→9900Hz显示・输出

→Up Freq SW (SW3)→9900Hz显示・输出

下止点: 0200Hz显示・输出

→Down Freq SW (SW4)→0100Hz显示・输出

→Down Freq SW (SW4)→0100Hz显示・输出

6.其它

输入模块 76.8kHz

LED显示模块 150Hz

使用Verilog-HDL研修基板

概略模块图

DIV : 分频器

FG : 频率发生器, 根据FVAL 发生频率 RPT : 测出开关的上升沿

CNT : 计数步, FVAL 为BCD 8bit SEL : 从8bit 中选择4bit

DEC : 从BCD 向7段LED 的译码 DRV : 7段动态驱动

Clock Drive

(4 signals)。