Verilog 复习考试总结

Verilog学习总结

顺序块和并行块

语句是顺序执行的 parameter d=50; reg[7:0] r; begin #d r='h35; #d r='hE2; #d r='h00; #d r='hF7; #d ->end_wave; end 用顺序块和延时控制组合来产生一个时序波形 并行块是语句同时执行的

起始时间和结束时间

在并行块和顺序块中都有一个起始时间和结 束时间的概念。对于顺序块,起始时间就是 第一条语句开始被执行的时间,结束时间就 是最后一条语句执行结束的时间。而对于并 行块来说,起始时间对于块内所有的语句是 相同的,即程序植程控制进入该块的时间, 其结束时间是按时间排序在最后的语句执行 结束的时间。

条件语句

数字

整数 有二、八、十、十六进制 <位宽>’<进制><数字>,这是一种全面的描述方式 缺省的位宽由具体的机器系统决定,至少是32位 缺省的进制为十进制 x表示不定值,z代表高阻值,z还可以用?代替 4'b10x0 //位宽为4的二进制数从低位数起第二位为不定值 4'b101z //位宽为4的二进制数从低位数起第一位为高阻值 12'dz //位宽为12的十进制数,其值为高阻值 12'd? //同上 8'h4x //位宽为8的十六进制数,其低4位值为不定值 要表示负数的话只需在位宽表达式前加一个减号 两个不同数据宽度的变量操作时,自动右对齐操作。特别是赋 值操作。

数据类型

Verilog HDL中总共有19种数据类型 4 个最基本的数据类型:integer型、parameter 型、reg型和wire型。其他的类型有large型、 medium型、scalared型、 time型、small型、 tri型、trio型、tril型、triand型、trior型、 trireg型、vectored型、wand型和wor 型。

Verilog 复习考试总结

3Verilog1.Verilog HDL是一种硬件描述语言,用于从算法级、RTL级、门级到开关级的多种抽象设计层次的数字系统建模。

令行为级描述:数据结构和过程类似C;用于描述算法级和RTL级的Verilog模型。

令结构级描述:用于描述门级和开关级电路;特点:支持门级延时信息和驱动能力等的描述。

VHDL侧重于系统级描述,从而更多的为系统级设计人员所采用;Verilog侧重于电路级描述,从而更多的为电路级设计人员所采用。

2. Verilog HDL设计入门模块(module)模块是Verilog 的基本描述单位模块的定义从关键词module开始,到关键词endmodule结束每条Verilog HDL语句以分号“;”作为结束模块的基本结构(1)、模块定义行以module开头接着给出所定义模块的;模块名括号内给出端口名列表(端口名等价于硬件中的外接引脚,模块通过这些端口与外界发生联系)以分号结束(2)、端口类型说明端口类型只有input、output、inout三种(3)、数据类型说明支持的数据类型有连线类(wire)和寄存器(reg)类两个大类一位宽的wire类可被缺省外,其它凡将在在后面的描述中出现的变量都应给出相应的数据类型说明(4)、描述体部具体)展开对模块的描述(5)、结束行用关键词endmodule标志模块定义的结束它的后面没有分号令行为描述(Behavior)描述行为或功能特性令结构描述(Structure)描述通过什么样的结构方式将不同的实体连接起来用以实现所要求的行为或功能。

测试与仿真令测试平台(Test Bench):在输入端口加入测试信号,从输出端口检测其输出结果是否正确。

令通常将需要测试的对象称之为DUT (Device Under Test)。

令测试模块:要调用DUT;包含用于测试的激励信号源;能够实施对输出信号的检测,并报告检测的结果。

过程语句令Initial:只顺序地执行一次;没有触发条件。

verilog课程期末总结

verilog课程期末总结一、引言Verilog(硬件描述语言)是一种用于描述电子系统的硬件结构和行为的语言,它广泛用于设计和验证数字电路,尤其是在集成电路和FPGA设计中。

在本学期的Verilog课程中,我们学习并实践了Verilog语言的基本概念和设计技巧,通过实验和项目开发,我们对Verilog语言的使用和应用有了更深入的了解。

本文将对这门课程进行总结,包括所学内容、实践经验以及未来的发展方向。

二、课程内容回顾本学期的Verilog课程共包含以下几个部分的内容:1. Verilog的基本语法和数据类型:在这个部分,我们学习了Verilog的基本语法,如模块定义、端口声明、数据类型定义等。

我们了解了如何使用Verilog语言进行模块化设计,利用不同的数据类型来描述数字电路中的信号和寄存器。

2. Verilog建模:这个部分教授了如何使用Verilog语言来建模和设计数字电路。

我们学习了组合逻辑和时序逻辑的建模方法,掌握了常用的门级建模和行为级建模技巧。

3. Verilog仿真:通过仿真可以验证我们设计的电路是否符合功能和时序的要求。

在这个部分,我们学习了如何使用Verilog语言进行仿真,以及如何编写仿真测试平台、编写仿真测试用例等。

通过仿真,我们可以对设计进行调试和验证,同时也方便了我们对电路性能和时序约束的分析。

4. Verilog项目开发:最后一个部分是课程的项目开发,通过一个实际项目的设计和实现,我们将所学的Verilog知识应用到实践中。

这个项目的设计还涉及模块间的通信和数据处理等方面,对我们综合运用所学知识的能力提出了更高的要求。

三、实践经验总结在学习和实践Verilog语言的过程中,我积累了一些宝贵的经验。

以下是我总结的几点实践经验:1. 充分理解和熟练掌握语法规则:Verilog语言的语法规则对于我们正确理解和使用这门语言非常重要。

通过不断的练习和实践,我渐渐熟练掌握了Verilog的语法规则,如模块的定义、端口的声明、数据类型的使用等。

VerilogHDL期末考试复习题

VerilogHDL期末考试复习题【第一章】1、FPGA 芯片的发展主要体现在哪几个方面?未来的发展趋势是什么?答:新型芯片的规模越来越大,成本越来越低,低端的FPGA已逐步取代了传统的数字元件。

先进的ASIC生产工艺已经被用于FPGA的生产,越来越丰富的处理器内核被嵌入到高端的FPGA芯片中,基于FPGA的开发成为一项系统级设计工程。

随着半导体制造工艺的不同提高,FPGA的集成度将不断提高,制造成本将不断降低,其作为替代ASIC来实现电子系统的前景将日趋光明。

2、EDA 技术的优势是什么?答:1.用HDL对数字系统进行抽象的行为与功能描述以及具体的内部线路结构描述,从而可以在电子设计的各个阶段、各个层次进行计算机模拟验证,保证设计过程的正确性,可以大大降低设计成本,缩短设计周期。

2.EDA工具之所以能够完成各种自动设计过程,关键是有各类库的支持。

3.某些HDL也是文档型的语言,极大地简化了设计文档的管理。

4.EDA具有日益强大的逻辑设计仿真测试技术,极大地提高了大规模系统电子设计的自动化程度。

5.基于EDA技术的设计,由于用HDL表达的成功的专用功能设计在实现目标方面有很大的可选性,它既可以用不同来源的通用FPGA/CPLD实现,也可以直接以ASIC来实现,设计者拥有完全的自主权。

6.EDA技术的设计语言是标准化的,不会由于设计对象的不同而改变;它的开发工具是规范化的,EDA软件平台支持任何标准化的设计语言;它的设计成果是通用性的,IP核具有规范的接口协议。

良好的可移植与可测试性,为系统开发提供了可靠的保证。

7.EDA技术能将所有设计环节纳入统一的自顶向下的设计方案中。

8.EDA不但在整个设计流程上充分利用计算机的自动设计能力,在各个设计层次上利用计算机完成不同内容的仿真模拟,而且在系统板设计结束后仍可利用计算机对硬件系统进行完整全面的测试。

3、EDA 的设计流程包括哪几个环节?ANS: ①设计输入(原理图/HDL 文本编辑)②综合③FPGA/CPLD 适配④时序仿真与功能门级仿真⑤FPGA/CPLD 编程下载⑥FPGA/CPLD 器件电路硬件检测。

verilog期末知识点总结

verilog期末知识点总结Verilog是一种硬件描述语言(HDL),用于描述数字电路。

它适用于设计和验证数字电路,以及编写仿真测试程序。

本文将总结Verilog的一些重要知识点,包括语法结构、模块化设计、时钟和同步电路、测试和调试等内容。

1. 语法结构Verilog的语法结构类似于C语言,包括模块声明、信号声明、组合逻辑和时序逻辑描述等。

模块声明以module关键字开始,用于定义一个模块,并使用endmodule结束。

信号声明包括输入、输出和内部信号,可以使用wire或reg关键字定义。

组合逻辑描述使用assign关键字和逻辑运算符描述输出信号与输入信号的关系。

时序逻辑描述使用always块和@关键字描述时钟触发事件,以及使用去块开始描述触发事件发生时的行为。

2. 模块化设计Verilog支持模块化设计,可以通过实例化和连接模块来完成整个电路的设计。

模块包括顶层模块和子模块,通过端口连接来进行通信。

顶层模块可以实例化多个子模块,并且可以在端口上进行信号连接,以及进行层次化的设计。

模块化设计可以提高代码的可读性和维护性,以及方便进行功能调试和验证。

3. 时钟和同步电路Verilog中的时序逻辑是通过时钟触发事件来控制的,常用的时钟触发事件是posedge和negedge,用于描述信号的上升沿和下降沿。

时序逻辑通常包括寄存器、时钟、复位和延迟等内容。

同步电路是一种使用时钟控制的电路,用于避免因异步时序引起的问题,如时序冲突和信号竞争等。

Verilog中可以使用always块和@关键字,以及使用posedge和negedge关键字来描述同步电路的行为。

4. 测试和调试Verilog支持使用仿真工具来进行电路的测试和调试。

常用的仿真工具包括ModelSim、VCS、NCVerilog等,可以对Verilog代码进行仿真、波形查看和时序约束验证等。

在进行测试和调试时,可以使用testbench来模拟输入信号,以及使用检验器来验证输出信号。

Verilog语法知识点总结(转)

Verilog语法知识点总结(转)1.1 概述条⽬说明分类1>> ⾯向设计的语句; // 可综合。

2>> ⾯向测试的语句; //testbench ,不可综合。

特点设计语句 assign , always ,模块例化,都对应实际电路,并⾏执⾏。

构造1.2 模块 Module条⽬说明模块名(端⼝列表)整个电路的外特性,抽象为⿊盒⼦;端⼝⽅向input , output ; inout ;端⼝类型wire , reg ;端⼝类型是 wire 时可以省略。

例: input a ; // 端⼝⽅向为输⼊,类型默认为 wire ;1.3 数据类型1.3.1 wire/reg 线⽹wire 和 reg 都是线类型,⼯程上没区别;只是 always/initial 模块中输出定义需要为 reg 型;注意:不要将 reg 类型与 D 触发器混淆, reg 理解为因为代码所产⽣的。

例如:wire [7:0] a; // 定义了 8 位的 wire 型数据wireb; // 定义了 1 位的 wire 型数据reg [3:0]sum ; // 定义了⼀个 4 位的 reg 型数据1.3.2 常量类型格式说明parameter parameter 数据名 = 表达式parameterMSB = 7 ;// 定义参数 MSB 为常量 7 ;推荐⼤写;常量< 位宽 >< 进制 >< 数字 >⼆进制: B 或 b ;⼗进制: D 或 d ;⼋进制: O 或 o ;⼗六进制: H 或 h ;8’b1010_1100 (‘b 表⽰⼆进制 )下画线“ _”, 提⾼阅读性。

< 数字 >默认⼗进制;4 值逻辑0 : Logic Low低电平;1 : Logic High⾼电平;x : Unknow ;不确定;z : High Impedance ;⾼阻态; // 三态门1.4 运算符1.4.1 概述运算符说明算术运算符+ ( 加 ) , - (减), * (乘), / (除), % (取模);每个运算符在电路中都是个模块,如加法器,减法器;!注意:除法,除 2^n ,是移位运算,浮点运算就复杂了,因此浮点运算要专⽤除法器;关系运算符>, <, >=, <= , == (相等),! = (不相等);逻辑运算符&& (逻辑与) . || (逻辑或) , ! (逻辑⾮);条件判断语句中,为避免歧义,逻辑运算符⼆边推荐为 1bit ;位运算符& (与), | (或), ~ (⾮) , ^ (异或) ; ~^ (同或);移位运算符<< (左移), >> (右移);归约操作& , ~& , | , ~| , ^, ~^;//unary reduction ;条件运算符?:拼接运算符{}//{3{a[0]}}: 代表 3 根同样的 a[0] 线, {a[0],a[0],a[0]} 1.5 设计语句1.5.1 assign (连续赋值)实例说明assigny = ~ b ;assign out = a==1 && c==1 ;assign f =sel ? a : b ;>> 实现可以⽤布尔函数描述的组合逻辑电路;>>“=” 后⾯可以是任何布尔函数;>> 并⾏执⾏;典型错误 1 :assigna = b + a;避免出现反馈电路:变为了不可知时序逻辑电路;1.5.2 always (过程块)a、赋值赋值⽅式说明= ,阻塞赋值always @ ( a or b or C or … )begin语句块( = , if 语句, case 语句)end实现:组合逻辑电路;(注意!禁⽌⽤于时序逻辑电路)always 块内,阻塞赋值:是顺序执⾏(类似 C );敏感表: @ ( * ) //“*” ⾃动添加相关输⼊信号;敏感表: @ ( * ) //“*” ⾃动添加相关输⼊信号;避免出现 Latch (锁存器)分⽀语句( if 语句, case 语句)条件不满时,会在电路中⾃动⽣成锁存器来保存不满⾜条件的值,因此要补全 if-else ,和 case 的 defalut 语句;<= ,⾮阻塞赋值always @ ( posedge clk or negedge rst_n )begin语句块( <= , if 语句, case 语句)end实现:时序逻辑电路;(注意!禁⽌⽤于组合逻辑电路)always 块内,阻塞赋值:并⾏执⾏;b、if 语句条⽬说明格式 1if( 条件 )begin 语句 1;语句 2 ;endelse begin语句 1 ;语句 2 ;end格式 2if( 条件 )begin 语句 1;语句 2 ;endelse if begin 语句 1 ;语句 2 ;endelse begin语句 1 ;语句 2end特点分⽀语句,各个分⽀条件不同;顺序执⾏判断;注意if-else 成对使⽤;c、case 语句条⽬说明格式case( 表达式 )常量表达式 1:begin 语句;end常量表达式 2:begin 语句;end常量表达式 3:begin 语句;enddefault :语句;endcase特点分⽀语句,各个分⽀条件相同;并⾏执⾏判断;注意default 语句不可省略;d、代码 & 硬件条⽬说明映射赋值语句 -> 逻辑函数; // 加法器,减法器等;边沿型条件分⽀ -> D 触发器;条件分⽀ -> 多路选择器;⽰例1.5.3 模块例化a、作⽤系统设计时,建议遵循以下设计原则:b、常见的典型错误如下所⽰:1.5.4 全加器全加器顶层: w1 , w2 , w3 :模块之间连线;半加强: 2 种描述⽅法,如下:描述⽅式描述⽅式说明位置关联AND u1(a, b, and_out);名字关联AND u1(.a(a), .b(b), .o ( and_out ) ); // 推荐使⽤1.6 测试语句1.6.1 结构Testbench1.6.2 特殊符号语句说明`< 标识符 >表⽰:编译引导语,⽤于指导仿真编译器在编译时采取⼀些特殊处理;编译引导语句⼀直保持有效,直到被取消或重写;`timescale `timescale < 时间单位 >/< 时间精度 >例 1 :`timescale 1ns/1ns // 时间单位 1ns ;时间精度 1ns ;#2 // 延时 2 ×1=2ns ;#2.1// 延时 2.1 × 1 = 2.1ns, 精确到 1ns ,为 2ns ;例 2 :`timescale 1ns/100ps // 时间单位 1ns ;时间精度 100ps ;#2 // 延时 2 ×1= 2ns ;#2.1// 延时 2.1 × 1 = 2.1ns, 精确到 100s ,为 2.1ns ;`define`include`include “global.v”包含另⼀个⽂件,完整拷贝过来;`restall把所有设置的编译引导恢复到缺省状态;#<num>;#10; // 延迟 10 个时间单位1.6.3 语句语句说明initial 块语句:只执⾏⼀次, always 循环执⾏;不可综合;作⽤:initial产⽣激励信号;检查输出波形;赋初值;forever // 产⽣周期信号:intial beginclk = 0 ;forever#10 clk = ~clk; // 时钟信号end1.6.4 系统任务和函数条⽬说明$< 标识符 >表⽰ Verilg 的系统任务和函数$time当前的仿真时间$display 显⽰信号值变化:只执⾏⼀次,打印当前时刻;$display($time, “b% %b %b” , rst,clk,dout);$monitor 监视信号值变化:所有过程时刻;$monitor($time, “b% %b %b” , rst,clk,dout);$stop暂停仿真$finish结束仿真,释放电脑资源;1.7 代码模板1.7.1 组合逻辑电路条⽬说明assign assign add_cnt = flag==1; // ⽤于简单的组合逻辑电路;always always @(*)begin// 统⼀采⽤“ *” 为敏感列表;( =,if,case )语句; // 只能使⽤“ =” 赋值end1.7.2 时序逻辑电路a、计数器模板 13 段式模板模板 1always @( posedge cllk or negedge rst_n) begin1计数段always @( posedge cllk or negedge rst_n) begin if (!rst_n)cnt <= 0; // 初值规定为 0else if (add_cnt)begin// 【位置 1 】if(end_cnt)cnt <= 0;elsecnt <= cnt + 1;endend2加 1 条件assingadd_cnt = d==1; //d==1 :什么时候开始数脉冲3结束条件assing end_cnt = add_cnt&& cnt == X-1; // X: 数多少个脉冲b、计数器模板 23 段式模板模板 11计数段always @( posedge cllk or negedge rst_n) begin if (!rst_n)cnt <= 0; // 初值规定为 0else if (add_cnt) begin// 【位置 1 】if(end_cnt)cnt <= 0;elsecnt <= cnt + 1;endelsecnt <= 0; // 不连续,需要清 0 时,使⽤模板 2 ;end2加 1 条件assingadd_cnt = d==1; //d==1 :什么时候开始数脉冲3结束条件assing end_cnt = add_cnt&& cnt == X-1; // X: 数多少个脉冲c、 4 段式状态机模板段号代码// 初始化,次态赋值给现态,明确当前状态;1always @(posedge clk or negedge rst_n) begin if(!rst_n)state_c <= S00;// 初始状态elsestate_c <= state_n;end2always @( * ) begin // 组合逻辑,描述状态转换⽬标case(state_c)S00: beginif(s00_s20_start) // 条件名 S00->S20state_n = S20;elsestate_n = state_c; // ⽅便拷贝endS20: beginif(s20_s21_start)state_n = S21;elsestate_n = state_c;endS21: beginif(s21_s00_start)state_n = S00;elsestate_n = state_c;enddefault: beginstate_n = S00;endendcaseend3// 具体的转换条件内容assign s00_s20_start = state_c==S00&& ( 条件 ) ;assign s20_s21_start = state_c==S20&& ( 条件 ); assign s21_s20_start = state_c==S21&& ( 条件 );4根据转态设计输出:1 个 always 设计 1 个输出信号;1.7.3 Testbencha、框架条⽬内容模块名`timescale 1 ns/1 nsmodule testbench_name();信号定义reg clk ; // 时钟reg rst_n; // 复位reg[3:0] din0 ; //uut 的输⼊信号,定义为 reg 型,在 initial 中reg din1 ;wire dout0;//uut 的输出信号,定义为 wire 型wire[4:0] dout1;parameter CYCLE = 20; // 参数定义,⽅便修改;parameter RST_TIME = 3 ;待测模块例化module_name uut( // 统⼀采⽤名字关联.clk ( clk ),.rst_n ( rst_n ),.din0 ( din0 ),.din1 ( din1 ),.dout0 ( dout0 ),.dout1 ( dout1 ));激励产⽣// 复位,时钟,等显⽰输出结果$display // 类似 printf ;b、复位复位initial beginrst_n = 1;#2;rst_n = 0;#(CYCLE*RST_TIME);rst_n = 1;endc、仿真时钟仿真时钟initial beginclk = 0;forever#(CYCLE/2)clk=~clk;endd、激励信号激励信号initial begin#1;// ⽅便观测din1 = 0; // 赋初值#(10*CYCLE);// 开始赋值end以上就是总结的 Verilog 语法相关知识点,转⾃明德扬论坛。

EDA-Verilog HDL期末复习题总结必过

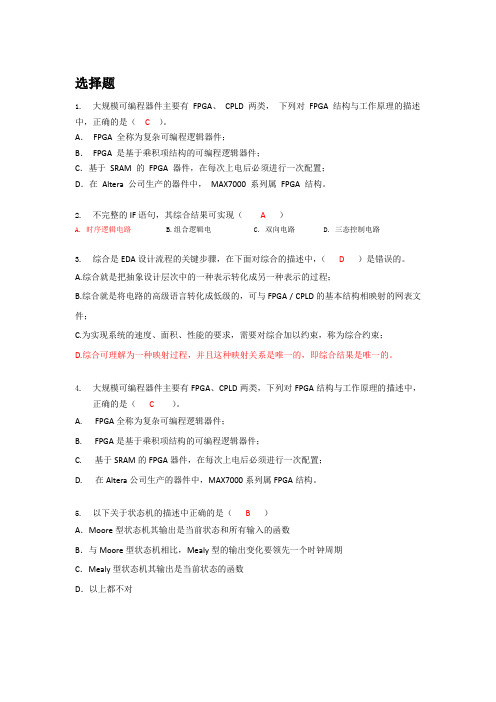

选择题1.大规模可编程器件主要有FPGA、CPLD 两类,下列对FPGA 结构与工作原理的描述中,正确的是(C)。

A.FPGA 全称为复杂可编程逻辑器件;B.FPGA 是基于乘积项结构的可编程逻辑器件;C.基于SRAM 的FPGA 器件,在每次上电后必须进行一次配置;D.在Altera 公司生产的器件中,MAX7000 系列属FPGA 结构。

2.不完整的IF语句,其综合结果可实现(A)A. 时序逻辑电路B.组合逻辑电C. 双向电路D. 三态控制电路3.综合是EDA设计流程的关键步骤,在下面对综合的描述中,(D)是错误的。

A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

4.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是( C )。

A.FPGA全称为复杂可编程逻辑器件;B.FPGA是基于乘积项结构的可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

5.以下关于状态机的描述中正确的是(B)A.Moore型状态机其输出是当前状态和所有输入的函数B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期C.Mealy型状态机其输出是当前状态的函数D.以上都不对6.目前应用最广泛的硬件描述语言是(B)。

A. VHDLB. Verilog HDLC. 汇编语言D. C语言7.一模块的I/O 端口说明:“input [7:0] a;”,则关于该端口说法正确的是( A )。

A. 输入端口,位宽为8B. 输出端口,位宽为8C. 输入端口,位宽为7D. 输出端口,位宽为78.基于EDA 软件的FPGA / CPLD 设计流程为:原理图/HDL 文本输入→综合→___ __→→适配→编程下载→硬件测试。

Verilog总结复习题 副本

Verilog复习题一、填空题1. 用 EDA 技术进行电子系统设计的目标是最后完成2. 可编程器件分为_CPLD_ 和 __FPGA__ 。

3. 随着 EDA 技术的不断完满与成熟,_自顶向下_ ASIC的设计与实现。

_的设计方法更多的被应用于Verilog HDL设计中间。

4.当前国际上较大的 PLD 器件制造公司有 _ALtera_ 和 _Xilinx_ 公司。

5.完满的条件语句将产生 _组合 _电路,不完满的条件语句将产生_时序 _电路。

6.拥塞性赋值符号为___=____ ,非拥塞性赋值符号为 ____<=_______ 。

7.有限状态机分为 __Moore__ 和 _Mealy_ 两各种类。

8、 EDA 缩写的含义为电子设计自动化 (Electronic Design Automation)_ _9.状态机常用状态编码有_二进制 _、_格雷码 _和 _独热码 _。

10. Verilog HDL中任务能够调用_其他任务 _和__函数 __。

11.系统函数和任务函数的首字符标志为_$_,预编译指令首字符标志为__#__。

12.可编程逻辑器件的优化过程主若是对___速度 ___和 __资源 __的办理过程。

13、大型数字逻辑电路设计采用的IP 核有 __软 IP__、__固 IP___和 __硬 IP__。

二、选择题1、已知“a =1b’ 1; b=3b'001;”那么{a,b}=(C)(A) 4b'0011 (B) 3b'001 (C) 4b'1001 (D) 3b'1012、在 verilog中,以下语句哪个不是分支语句?(D)(A) if-else (B) case (C) casez (D) repeat3、 Verilog HDL语言进行电路设计方法有哪几种(①自上而下的设计方法(Top-Down )②自下而上的设计方法(Bottom-Up )8 分)③综合设计的方法4、在 verilog 语言中, a=4b'1011,那么&a= ( D)(A) 4b'1011 (B) 4b'1111 (C) 1b'1 (D) 1b'05、在 verilog 语言中整型数据与( C )位寄存器数据在实质意义上是相同的。

VerilogHDL复习题与答案

VerilogHDL硬件描述语言复习一、1. Verilog HDL 是在哪一年首次被I E E E标准化的?答:Verilog HDL是在1995年首次被IEEE标准化的。

2. Verilog HDL支持哪三种根本描述方式?答:Verilog HDL可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;构造化方式—使用门和模块实例语句描述建模3. Verilog HDL 是由哪个公司最先开发的?答:Verilog HDL是由Gateway Design Automation公司最先开发的4. Verilog HDL中的两类主要数据类型什么?答:线网数据类型和存放器数据类型。

线网类型表示构件间的物理连线,而存放器类型表示抽象的数据存储元件。

5. U D P代表什么?答:UDP代表用户定义原语6. 写出两个开关级根本门的名称。

答:pmos nmos7.写出两个根本逻辑门的名称。

答:and or8.在数据流描述方式中使用什么语句描述一个设计?答:设计的数据流行为使用连续赋值语句进展描述9. 采用构造描述方式描述1位全加器。

答:module full_add(a,b,cin,s,co);input a,b,cin;output s,co;wire S1,T1,T2,T3;xorX1(S1,a,b),X2(s,S1,cin);andA1(T3,a,b),A2(T2,b,cin),A3(T1,a,cin);orO1(co,T1,T2,T3);endmodule10. i n i t i a l语句与always 语句的关键区别是什么?答: 1) initial语句:此语句只执行一次。

2) always语句:此语句总是循环执行, 或者说此语句重复执行。

11.采用数据流方式描述2 - 4译码器。

答:'timescale 1ns/nsmodule Decoder2×4(A,B,EN,Z);input A,B,EN;output [0:3]Z;wire abar,Bbar;assign #1 Abar=~A;assign #1 Bbar=~B;assign #2 Z[0]=~(Abar&Bbar&EN);assign #2 Z[1]=~(Abar&B&EN);assign #2 Z[2]=~(A&Bbar&EN);assign #2 Z[3]=~(A&B&EN);endmodule1 2. 找出下面连续赋值语句的错误。

VerilogHDL复习题与答案

VerilogHDL硬件描述语言复习一、1. Verilog HDL 是在哪一年首次被I E E E标准化的?答:Verilog HDL是在1995年首次被IEEE标准化的。

2. Verilog HDL支持哪三种基本描述方式?答:Verilog HDL可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3. Verilog HDL 是由哪个公司最先开发的?答:Verilog HDL是由Gateway Design Automation公司最先开发的4. Verilog HDL中的两类主要数据类型什么?答:线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

5. U D P代表什么?答:UDP代表用户定义原语6. 写出两个开关级基本门的名称。

答:pmos nmos7.写出两个基本逻辑门的名称。

答:and or8.在数据流描述方式中使用什么语句描述一个设计?答:设计的数据流行为使用连续赋值语句进行描述9. 采用结构描述方式描述1位全加器。

答:module full_add(a,b,cin,s,co);input a,b,cin;output s,co;wire S1,T1,T2,T3;xorX1(S1,a,b),X2(s,S1,cin);andA1(T3,a,b),A2(T2,b,cin),A3(T1,a,cin);orO1(co,T1,T2,T3);endmodule10. i n i t i a l语句与always 语句的关键区别是什么?答: 1) initial语句:此语句只执行一次。

2) always语句:此语句总是循环执行, 或者说此语句重复执行。

11.采用数据流方式描述2 - 4译码器。

答:'timescale 1ns/nsmodule Decoder2×4(A,B,EN,Z);input A,B,EN;output [0:3]Z;wire abar,Bbar;assign #1 Abar=~A;assign #1 Bbar=~B;assign #2 Z[0]=~(Abar&Bbar&EN);assign #2 Z[1]=~(Abar&B&EN);assign #2 Z[2]=~(A&Bbar&EN);assign #2 Z[3]=~(A&B&EN);endmodule1 2. 找出下面连续赋值语句的错误。

verilog知识点总结

verilog知识点总结Verilog知识点总结Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统。

在数字电路设计中,Verilog是一种重要的工具,它可以描述组合逻辑和时序逻辑,以及设计和验证硬件。

本文将总结Verilog的一些重要知识点,包括模块化设计、数据类型、运算符、时序建模和测试基础等。

一、模块化设计在Verilog中,模块是设计的基本单元。

模块化设计可以使复杂的电路设计更加可管理和可重用。

在Verilog中,模块由模块声明和模块体组成。

模块声明定义了模块的接口,包括输入、输出和内部信号。

模块体定义了模块的功能,包括组合逻辑和时序逻辑。

二、数据类型Verilog支持多种数据类型,包括位、字、整数和实数。

位是最基本的数据类型,用于表示二进制数。

字是一组连续的位,用于表示整数或实数。

整数是有符号或无符号的整数,用于表示整数值。

实数是浮点数,用于表示小数值。

三、运算符Verilog支持多种运算符,包括算术运算符、逻辑运算符、位运算符和关系运算符。

算术运算符包括加法、减法、乘法和除法。

逻辑运算符包括与、或、非和异或。

位运算符包括位与、位或、位非和位异或。

关系运算符包括等于、不等于、大于、小于、大于等于和小于等于。

四、时序建模时序建模是描述时序电路行为的重要方面。

在Verilog中,可以使用时钟信号和时钟边沿来定义时序行为。

时钟信号用于同步电路的操作,时钟边沿用于触发电路的操作。

常用的时序建模语句包括时钟边沿敏感的always语句和延迟语句。

五、测试基础测试是硬件设计过程中的重要环节。

Verilog提供了多种测试方法,包括模拟仿真、自动测试生成和形式验证。

模拟仿真是通过模拟输入信号并观察输出信号来验证电路的功能。

自动测试生成是通过生成测试向量来覆盖电路的所有可能输入组合。

形式验证是通过数学证明来验证电路的正确性。

六、常用编码风格在Verilog中,编码风格是编写可读性高且易于理解的代码的重要因素。

(完整word版)EDA-VerilogHDL期末复习题总结必过

(完整word版)EDA-VerilogHDL期末复习题总结必过选择题1.大规模可编程器件主要有FPGA、CPLD 两类,下列对FPGA 结构与工作原理的描述中,正确的是(C)。

A.FPGA 全称为复杂可编程逻辑器件;B.FPGA 是基于乘积项结构的可编程逻辑器件;C.基于SRAM 的FPGA 器件,在每次上电后必须进行一次配置;D.在Altera 公司生产的器件中,MAX7000 系列属FPGA 结构。

2.不完整的IF语句,其综合结果可实现(A)A. 时序逻辑电路B.组合逻辑电C. 双向电路D. 三态控制电路3.综合是EDA设计流程的关键步骤,在下面对综合的描述中,(D)是错误的。

A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD 的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

4.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是( C )。

A.FPGA全称为复杂可编程逻辑器件;B.FPGA是基于乘积项结构的可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

5.以下关于状态机的描述中正确的是(B)A.Moore型状态机其输出是当前状态和所有输入的函数B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期C.Mealy型状态机其输出是当前状态的函数D.以上都不对6.目前应用最广泛的硬件描述语言是(B)。

A. VHDLB. Verilog HDLC. 汇编语言D. C语言7.一模块的I/O 端口说明:“input [7:0] a;”,则关于该端口说法正确的是( A )。

verilog知识点总结

verilog知识点总结Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统,它广泛应用于数字系统设计和仿真领域。

本文将总结一些Verilog 的重要知识点,以帮助读者更好地理解和应用Verilog。

一、Verilog的基本语法Verilog的基本语法包括模块声明、端口声明、信号声明、数据类型、运算符等。

Verilog中的模块是设计的基本单元,模块声明包括模块名和端口声明。

端口可以是输入、输出或双向的。

信号声明用于定义内部信号,可以是寄存器或线网类型。

Verilog支持多种数据类型,包括整数、浮点数、向量、数组等。

Verilog还提供了丰富的运算符,包括算术运算符、逻辑运算符、位运算符等。

二、组合逻辑电路描述Verilog可以用来描述各种组合逻辑电路,如与门、或门、非门等。

通过使用逻辑运算符和条件语句,可以很方便地描述组合逻辑电路的功能。

Verilog还提供了多种语法结构,如if语句、case语句等,用于描述复杂的逻辑功能。

三、时序逻辑电路描述时序逻辑电路是一种带有状态的电路,Verilog可以用来描述各种时序逻辑电路,如触发器、计数器、状态机等。

通过使用时钟信号和触发器,可以实现电路的时序行为。

Verilog提供了多种触发器类型,如D触发器、JK触发器、T触发器等,可以根据实际需求选择合适的触发器类型。

四、模块实例化和层次化设计Verilog支持模块的实例化和层次化设计,可以将一个模块实例化为另一个模块的一部分。

通过模块实例化,可以方便地实现模块的复用和层次化设计。

层次化设计可以使整个系统更加清晰和模块化,方便调试和维护。

五、仿真和验证Verilog可以用于对设计进行仿真和验证,以确保设计的正确性。

Verilog提供了仿真器,可以对设计进行时序仿真和波形查看。

通过仿真,可以验证设计的功能和时序行为是否符合要求。

Verilog 还支持测试向量的生成和自动验证,可以自动生成测试向量并进行自动验证。

verilog报告总结

张威工作总结在完成本次verilog大作业的过程中,我不仅学到了很多只靠读书学不到的知识,而且体会到了团队协作的力量,以下做一简要总结:在这次作业中,我们首先进行分工合作,我和徐建龙负责bmp图像方面的工作,首先我们通过在网上和图书馆查阅资料,了解了bmp格式图像的基本知识,以便编写具体算法实现图像的翻转。

在对bmp格式文件有了一定掌握后,我们首先尝试用c++语言将其转换为txt 文件的格式,但是在查阅了相关资料后,发现这种方法过于复杂,因此最终放弃了这个思路。

随后我们查阅资料发现可以直接利用verilog的系统任务$fread即可对bmp文件进行操作,再结合文件输出任务$fopen\$fdisplay\$fclose将bmp文件打开并通过翻转算法转换后再写入txt文件,最后用软件WinHex将其转换为2进制文件并另存为bmp格式,即完成了翻转工作。

在这个过程中,我对课上学到的语句有了更深的理解,并将其应用到了实际工程中,使自己的运用能力得到了很好的锻炼,并且,我对Modelsim仿真软件也有了一定的了解,其基本操作已经较熟练的掌握,对其中一些细节问题,如仿真时间的选取等也有了自己的理解。

实践出真知,通过在软件上反复改程序、跑程序我也学会了很多只看书本发现不了的问题,锻炼了自己的解决问题能力。

最后,我还想感谢我的队友们,这次作业的完成使我们共同努力的结果,我真正感受到了团队的力量,也体会到了老师为什么一定要求必须结对完成的良苦用心。

在做工程的过程中,我们曾经对算法,流程等诸多问题产生过分歧,在屡次失败后,我们也曾想过放弃,但是我们最终团结一致,共同努力完成了作业,在图片成功翻转的那一霎那,所有的辛苦都有了回报,我们真正明白了什么叫teamwork!刘欢verilog大作业工作报告在团队成员的合作下,经历了许多困难,终于完成了verilog的大作业,虽然过程并不是和想象中的一样,而且作业也与老师要求的有所差距,但是在紧张的考试复习中,还是努力把这个作业完成了,并且从中学习到了许多关于verilog的使用与仿真的知识,这对于今后的学习是有很大的帮助的。

verilogHDL语言复习归纳

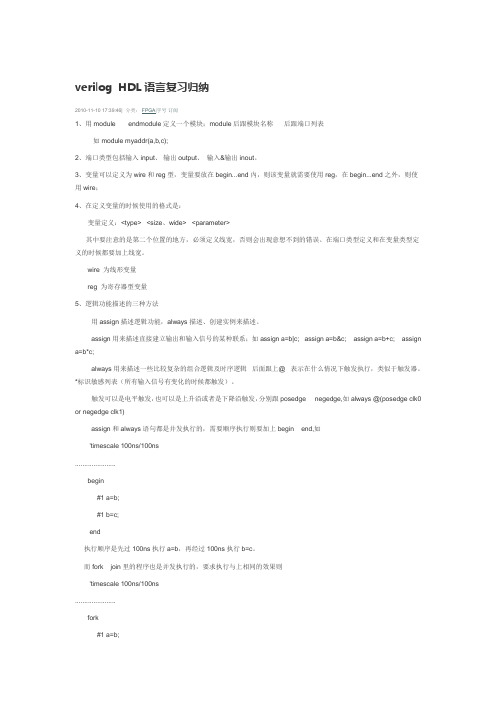

verilog HDL语言复习归纳2010-11-10 17:39:46| 分类:FPGA|字号订阅1、用module endmodule定义一个模块;module后跟模块名称后跟端口列表如module myaddr(a,b,c);2、端口类型包括输入input、输出output、输入&输出inout。

3、变量可以定义为wire和reg型,变量要放在begin...end內,则该变量就需要使用reg,在begin...end之外,则使用wire;4、在定义变量的时候使用的格式是:变量定义:<type> <size、wide> <parameter>其中要注意的是第二个位置的地方,必须定义线宽,否则会出现意想不到的错误。

在端口类型定义和在变量类型定义的时候都要加上线宽。

wire 为线形变量reg 为寄存器型变量5、逻辑功能描述的三种方法用assign描述逻辑功能,always描述、创建实例来描述。

assign用来描述直接建立输出和输入信号的某种联系;如assign a=b|c; assign a=b&c; assign a=b+c; assign a=b*c;always用来描述一些比较复杂的组合逻辑及时序逻辑后面跟上@ 表示在什么情况下触发执行,类似于触发器。

*标识敏感列表(所有输入信号有变化的时候都触发)。

触发可以是电平触发,也可以是上升沿或者是下降沿触发,分别跟posedge negedge,如always @(posedge clk0 or negedge clk1)assign和always语句都是并发执行的,需要顺序执行则要加上begin end,如'timescale 100ns/100ns......................begin#1 a=b;#1 b=c;end执行顺序是先过100ns执行a=b,再经过100ns执行b=c。

verilog总复习

verilog总复习1.Verilog的主要应用包括:a)ASIC和FPGA工程师编写可综合的RTL代码b)使用高抽象级描述仿真系统,进行系统结构开发c)测试工程师用于编写各种层次的测试程序d)用于ASIC和FPGA单元或更高层次的模块的模型开发2.Verilog模型可以是实际电路的不同级别的抽象,这些抽象的级别包括:(a)行为级(系统说明)-设计文档/算法描述(b)RTL/功能级,Verilog(c)门级/结构级, Verilog(d)版图/物理级, 几何图形Verilog既是一种行为描述的语言也是一种结构描述语言。

行为综合综合前仿真逻辑综合综合后仿真版图3.Verilog可以在三种抽象级上进行描述:a.行为级(Behavioral level)1. 用功能块之间的数据流对系统进行描述2. 在需要时在函数块之间进行调度赋值。

b.RTL级/功能级(RTL level or Functional level)1. 用功能块内部或功能块之间的数据流和控制信号描2.基于一个已定义的时钟的周期来定义系统模型c.结构级/门级(Structural level or Gate level)1. 用基本单元(primitive)或低层元件(component)的连接来描述系统以得到更高的精确性,特别是时序方面。

2. 在综合时用特定工艺和低层元件将RTL描述映射到门级网表4.二选一多路选择器用RTL和门级电路分别来描述。

5.基本词法:空白符、注释、常量、字符串、标识符编译指令基本语法:-模块结构- 端口定义(input、output、inout)- 数据类型(net、register、parameter)- 功能描述(assign语句、always语句)6. 基本构件module(Verilog程序包含:端口定义,I/O说明,内部信号声明,功能定义)module DFF (// 端口说明Output reg q,wire qb,input wire d, // input dataclk, /*input clock */clr);7.模块实例化的实现:引用现成元件和模块的方法。

Verilog学习总结

verlog语法要点

同步状态机: 包括moore和mealy型两种,及其反馈模型(是一种反 馈控制系统,当前状态就是其内部状态变量) 状态机的开发步骤: 根据实际问题列出输入输出变量和状态数 画出状态图并化简 写出状态转移真值表得到逻辑表达式 用D触发器或JK触发器构建电路(目前用D触发器多) verilog描述时只需要得到简化的状态图就可以描述 状态编码方式: 独热码 格雷码 状态机主体程序有单always描述方式和多always描述方式 采用case/casez/casex建立模型最好,因为x是无关态, 生成的电路最简单 default: state='bx与实际情况更一致,效果等同于 default: state<=idle 只有同步状态机才能被目前的综合

生成语句:生成快的本质是使用循环内的一条语句代替多 条重复的verilog语句,简化了用户的编程。 genvar用于声 明生成变量,生成变量只能用在生成快之间 仿真时,仿 真器会将生成块中的代码展平,在确立后的方针代码中, 生成变量是不存在的。最好是先想象出来循环生成语句被 展平后的电路样子,再写相关的描述语句

verlog语法要点

常量格式: <二进制位宽><‘><进制><该进制的数值>: 默认进制为10进制 默认位宽为32位 位宽是从二进制宽度角度而言的 由位宽决定从低位截取二进制数2’hFF=2‘b11, 通常由被赋值的reg变量位宽决定 parameter常用于定义延迟和变量位宽,可用常量或常 量表达式定义

verlog语法要点

for语句会将所有变量的情况展开,占用巨量逻辑资源,替代 办法是用计数器和case语句说明所有情况 有优先级的if else结构会消耗更多资源,建议用无优先级的 case替代 模块的复用往往比代码上修改节省的资源多 PLL的分频、倍频、移相操作会增加设计精度 同步时序电路的延时:#x通常用于仿真测试,实际硬件延 时是:长延迟用计数器,小延迟用D触发器,此方法用来 取代延迟链 同步电路中,稳定的数据采用必须满足采样寄存器的建立 和保持时间 reg类型在always中不一定综合成时序电路,也可能是组合 逻辑电路 乒乓操作与作用 异步时钟域同步问题 延迟包括门延迟和线延迟 组合逻辑产生的时钟仅能应用在时钟频率较低、精度要求 不高的情况下增减敏感信号得到的结果一样

湖南工业大学EDA——Verilog考试重点

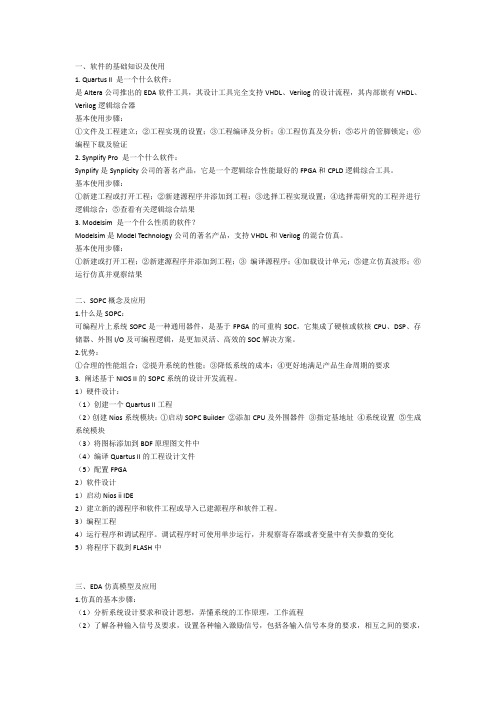

一、软件的基础知识及使用1. Quartus II 是一个什么软件:是Altera公司推出的EDA软件工具,其设计工具完全支持VHDL、Verilog的设计流程,其内部嵌有VHDL、Verilog逻辑综合器基本使用步骤:①文件及工程建立;②工程实现的设置;③工程编译及分析;④工程仿真及分析;⑤芯片的管脚锁定;⑥编程下载及验证2. Synplify Pro 是一个什么软件:Synplify是Synplicity公司的著名产品,它是一个逻辑综合性能最好的FPGA和CPLD逻辑综合工具。

基本使用步骤:①新建工程或打开工程;②新建源程序并添加到工程;③选择工程实现设置;④选择需研究的工程并进行逻辑综合;⑤查看有关逻辑综合结果3. Modelsim是一个什么性质的软件?Modelsim是Model Technology公司的著名产品,支持VHDL和Verilog的混合仿真。

基本使用步骤:①新建或打开工程;②新建源程序并添加到工程;③编译源程序;④加载设计单元;⑤建立仿真波形;⑥运行仿真并观察结果二、SOPC概念及应用1.什么是SOPC:可编程片上系统SOPC是一种通用器件,是基于FPGA的可重构SOC,它集成了硬核或软核CPU、DSP、存储器、外围I/O及可编程逻辑,是更加灵活、高效的SOC解决方案。

2.优势:①合理的性能组合;②提升系统的性能;③降低系统的成本;④更好地满足产品生命周期的要求3.阐述基于NIOS II的SOPC系统的设计开发流程。

1)硬件设计:(1)创建一个Quartus II工程(2)创建Nios系统模块:①启动SOPC Builder ②添加CPU及外围器件③指定基地址④系统设置⑤生成系统模块(3)将图标添加到BDF原理图文件中(4)编译Quartus II的工程设计文件(5)配置FPGA2)软件设计1)启动Nios ii IDE2)建立新的源程序和软件工程或导入已建源程序和软件工程。

Verilog复习重点

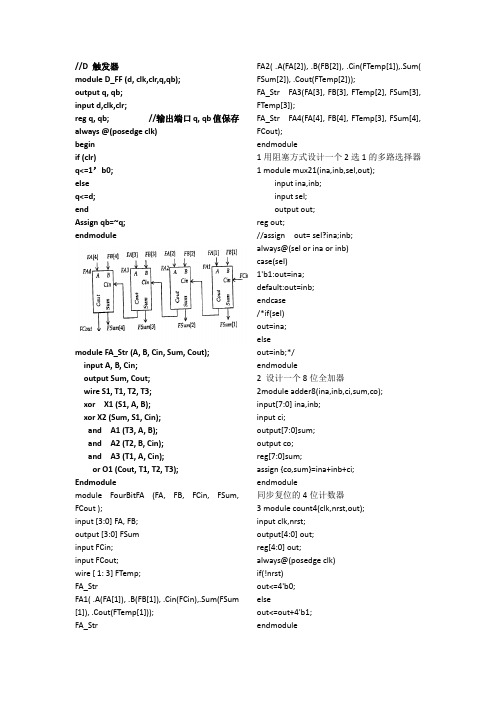

//D 触发器module D_FF (d, clk,clr,q,qb);output q, qb;input d,clk,clr;reg q, qb; //输出端口q, qb值保存always @(posedge clk)beginif (clr)q<=1’b0;elseq<=d;endAssign qb=~q;endmodulemodule FA_Str (A, B, Cin, Sum, Cout);input A, B, Cin;output Sum, Cout;wire S1, T1, T2, T3;xor X1 (S1, A, B);xor X2 (Sum, S1, Cin);and A1 (T3, A, B);and A2 (T2, B, Cin);and A3 (T1, A, Cin);or O1 (Cout, T1, T2, T3);Endmodulemodule FourBitFA (FA, FB, FCin, FSum, FCout );input [3:0] FA, FB;output [3:0] FSuminput FCin;input FCout;wire [ 1: 3] FTemp;FA_StrFA1( .A(FA[1]), .B(FB[1]), .Cin(FCin),.Sum(FSum [1]), .Cout(FTemp[1]));FA_Str FA2( .A(FA[2]), .B(FB[2]), .Cin(FTemp[1]),.Sum( FSum[2]), .Cout(FTemp[2]));FA_Str FA3(FA[3], FB[3], FTemp[2], FSum[3], FTemp[3]);FA_Str FA4(FA[4], FB[4], FTemp[3], FSum[4], FCout);endmodule1用阻塞方式设计一个2选1的多路选择器1 module mux21(ina,inb,sel,out);input ina,inb;input sel;output out;reg out;//assign out= sel?ina;inb;always@(sel or ina or inb)case(sel)1'b1:out=ina;default:out=inb;endcase/*if(sel)out=ina;elseout=inb;*/endmodule2 设计一个8位全加器2module adder8(ina,inb,ci,sum,co);input[7:0] ina,inb;input ci;output[7:0]sum;output co;reg[7:0]sum;assign {co,sum}=ina+inb+ci;endmodule同步复位的4位计数器3 module count4(clk,nrst,out);input clk,nrst;output[4:0] out;reg[4:0] out;always@(posedge clk)if(!nrst)out<=4'b0;elseout<=out+4'b1;endmodule设计一个8-3优先编码器5 module encoder83(in,outcode);output[2:0] outcode;input [7:0] in;reg[2:0] outcode;function[2:0] code;input[7:0] ina;if(ina[0]) code=3'b000;else if(ina[1]) code=3'b001;else if(ina[2]) code=3'b010;else if(ina[3]) code=3'b011;else if(ina[4]) code=3'b100;else if(ina[5]) code=3'b101;else if(ina[6]) code=3'b110;else if(ina[7]) code=3'b111;else code=3'bx;endfunctionassign outcode=code(in);endmodule6.设计八功能的算术运算单元(ALU),其输入信号a和b均为4位,功能选择信号select 为3位.输出信号out为8位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

算术运算符: 1、加法运算符; +,实现加法运算 4、除法运算符; /, 实现除法运算 2、减法运算符; -,实现减法运算 5、取模运算符; %,实现取模运算 3、乘法运算符; ×,实现乘法运算 在算术运算操作中,操作数是作为一个整体参与运算的,因而,如果某个操作数的某一位为 不定态(x 值) ,则整个表达式的运算结果也为不定态。 位运算符: 按位取反运算符:~ 按位异或运算符:^ 按位与运算符:& 按位同或运算符:^~或~^ 按位或运算符:| 缩位运算符: 单目运算符,按位进行逻辑运算,最后结果为一位的二进制数 缩位运算符包括: & ~| ^ (异或) | ~& ~^ or ^~ (同或) 逻辑运算符: 逻辑与运算符:&&(双目运算符) A = 6; A && B 1 && 0 0 逻辑或运算符: || (双目运算符) B = 0; A || !B 1 || 1 1 逻辑非运算符: ! (单目运算符) C = x; x 关系运算符: 1、小于:< 2、大于:> 3、小于等于:<= 4、大于等于:>= 结果是一位值:0,1 或 x 相等与全等运算符:

3 Verilog

1. Verilog HDL 是一种硬件描述语言,用于从算法级、RTL 级、门级到开关级的多种抽象设计层次的数字系统建模。 行为级描述:数据结构和过程类似 C;用于描述算法级和 RTL 级的 Verilog 模型。 结构级描述:用于描述门级和开关级电路;特点:支持门级延时信息和驱动能力等的描述。 VHDL 侧重于系统级描述,从而更多的为系统级设计人员所采用; Verilog 侧重于电路级描述,从而更多的为电路级设计人员所采用。 Verilog HDL 设计入门 模块(module) 模块是 Verilog 的基本描述单位 模块的定义从关键词 module 开始,到关键词 endmodule 结束 每条 Verilog HDL 语句以分号“; ”作为结束 模块的基本结构 ⑴、模块定义行 以 module 开头 接着给出所定义模块的模块名 括号内给出端口名列表(端口名等价于硬件中的外接引脚,模块通过这些端口与外界发生联系) 以分号结束 ⑵、端口类型说明 端口类型只有 input、output、inout 三种 ⑶、数据类型说明 支持的数据类型有连线类(wire)和寄存器(reg)类两个大类 一位宽的 wire 类可被缺省外,其它凡将在后面的描述中出现的变量都应给出相应的数据类型说明 ⑷、描述体部 具体展开对模块的描述 ⑸、结束行 用关键词 endmodule 标志模块定义的结束 它的后面没有分号 行为描述与结构描述 行为描述(Behavior)描述行为或功能特性 结构描述(Structure)描述通过什么样的结构方式将不同的实体连接起来用以实现所要求的行为或功能。 测试与仿真 测试平台(Test Bench) :在输入端口加入测试信号,从输出端口检测其输出结果是否正确。 通常将需要测试的对象称之为 DUT(Device Under Test) 。 测试模块:要调用 DUT;包含用于测试的激励信号源;能够实施对输出信号的检测,并报告检测的结果。 过程语句 Initial:只顺序地执行一次;没有触发条件。 Always: 当顺序执行到最后一条语句后,会自动返回到第一条语句重新开始执行,是一条没有穷尽的循环语句 往往带有触发条件 Verilog HDL 基础知识 基本词法定义 空白符 空白符是以下几种字符与控制符的总称:①空格、②TAB 键、③换行符、④换页符。 空白符起分隔符的作用:允许在一行内写多条 Verilog HDL 语句 注释行 单行注释:以“//”开始到行末结束,不允许续行 多行注释:以“/*” 开始,到“*/”结束,可以跨越多行,但不允许嵌套

实数及其表示 实数可以用十进制数表示,也可用指数表示。 在 verilog HDL 中, 实数可以参与的运算是受限制 的。 当实数被转换为整数时,是按四舍五入的方式进 行的。 字符串 定义:为两个双引号“”之间的字符;字符串不 允许跨行。 可通过前导的控制键(反斜杠及百分号)引入一些特殊字符 取名规则 必须是由字母(a~z, A~Z)或下划线开头,长度小于 1024 字符的一串字符序列 后续部分可以是字母( a~z, A~Z ) 、数字(0~9) 、下划线、$ 还可以是反斜杠“\”开头,并以空白符结尾的任何字符序列。但反斜杠本身及空白符都不属标识符 组成部分 系统命令行中的内容只是为了便于阅读理解 在必要的地方增加适当的注释说明,在 HDL 编程中尤为重要 有些操作控制命令以注释行的方式出现在 HDL 描述中,它不影响 HDL 的仿真,但其它工具可以识 别这些控制命令 四种逻辑状态 Verilog HDL 需要用数字或字符去表达在数字电路中存储与传送的逻辑状态。 0 1 逻辑零、逻辑非、低电平 逻辑 1、逻辑真、高电平 x或X z或Z 不确定的逻辑状态 高阻态

宏替换定义本身以及用到宏替换的地方必须有撇号“`”作开头 模拟时间定标 对模拟器的时间单位及时间计算的精度进行定标 定义:`timescale<计时单位>/<计时精度> 计时单位与计时精度都由整数及相应的时间单位两部分组成 时间单位:S、ms(毫秒) 、us(微秒) 、Ns(纳秒) 、 ps(微微秒) 、Fs(毫微微秒) 时间精度:延迟时间的最小分辨率 计时单位必须大于等于精度单位 对 timescale 的定义必须在模块描述的外部进行 模拟器允许对不同模块定义不同的时标,但以最小的精度进行模拟计算 运算符 运算符的分类 单目运算符:只有一个操作数,且运算符位于操作数的左边 双目运算符:有两个操作数,各位于运算符的两边 三目运算符:属于这一类的只有条件运算符(? :)一个 运算符的优先级顺序

共有四种: 1、相等 运算符:== 4’b 1z0x == 4’b 1z0x x 2、不等 运算符:!= 4’b 1z0x != 4’b 1z0x x 3、全等 运算符:=== 4’b 1z0x === 4’b 1z0x 1 4、不全等运算符:!== 4’b 1z0x !== 4’b 1z0x 0 都是双目运算符,得到的结果是 1 位的逻辑值 相等算符: 逐位比较两个操作数相应位的值是否相等, 只有当每一位都相等时,相等关系才满足。如果任何 一个操作数中的某一位存在不定态或高阻态,则将得 到一个不定态的结果。 全等算符:将不定态或高阻态看作是逻辑状态的一种 而参与比较 逻辑移位运算符: 1、逻辑左移:<< 2、逻辑右移:>> Result is same size as first operand, always zero filled 例:a = 4’b1010; d = a >> 2; // d = 0010 c = a << 1; // c = 0100 连接运算符: 将两组或两组以上的信号用大括号括起来,拼接成一组新的信号。 对于一些重复信号的连接,可以用它的简化表示方法{n{a}},表示将信号 a 重复连接 n 次。 Operands must be sized !!(数的进制相同) 条件运算符: <条件运算符>?<条件为真时的表达式>:<条件为假时的表达式>:Assign out = (sel == 0) ? a :b 允许实型量参与的运算符 不允许实型量参与的运算符

斜体表示的是可缺省的部分 过程语句是指 Initial 或 always 事件控制敏感表只在 always 过程语句中出现,用于激活过程语句的执行 块语句标识符分 begin-end(串行块)与 fork-join(并行块)两类 块名和块内局部变量说明均为可选项 过程语句 Initial 与 always 1、 都是从模拟的 0 时刻开始执行,但 initial 过程语句后面的块语句沿时间轴只执行一次,而 always 则 循环地重复执行其后的块语句。 2、 initial 过程语句不带触发条件,因而必定从模拟的 0 时刻开始执行它后面的块语句;always 过程语句 则通常带有触发(激活)条件,只有当触发条件被满足时,其后的块语句才真正开始执行。如果触发 条件被缺省,则认为触发条件始终被满足。 3、 一个模块的行为描述中可以有多个 initial 与 always 语句,代表多个过程块的存在,它们之间相互独 立,并行运行。 Initial 过程语句 在实际的描述过程中,最经常地应用于测试模块中对激励向量的描述。 在对硬件功能模块的行为描述中,仅在必要时给寄存器变量赋以初值。 是一条主要面向模拟的过程语句,通常不为逻辑综合工具接受。 Always 过程语句 在测试模块中一般用于对时钟的描述,但更多地用于对硬件功能模块的行为描述。 功能模块的行为描述是由过程块构成的,每个过程块都要由过程语句所引导,因而每个功能模块 的行为描述中,至少存在一个 always 过程语句。 块语句 由块标识符 begin-end 或 fork-join 界定的一组行为描述语言。 过程块所要完成的具体操作内容,都是通过块语句中所包含的描述语句的执行而得以实现的。 串行块 begin-end 位于串行块中的各条语句按串行方式顺序执行 特点: 1、 串行块中的每条语句依据块中的排列次序,先后逐条顺序执行。块中每条语句给出的延时都是相 对于前一条语句执行结束的相对时间。 2、 串行块的起始执行时间就是串行块中第一条语句开始执行的时间。串行块的结束时间就是块中最 后一条语句执行结束的时间。 3、 串行块的行为描述可以形象地理解为硬件电路中,数据在时钟及控制信号作用下,沿数据通道的 各级寄存器之间的传送过程。 并行块 fork-join 位于并行块中的各条语句按并行方式同时执行 特点: 1、 并行块中的每条语句都是同时开始并行执行的,各条语句的执行过程与语句在块中的先后排列顺 序无关。块中每条语句给出的延时都是相对于并行块开始执行时的绝对时间。 2、 并行块的起始执行时间就是流程控制转入并行块的时间,并行块中的每条语句都是相对于这一时 间同时开始执行的。 并行块的结束时间就是并行块中按执行时间排序最后执行的一条语句结束的 时间。 3、 并行块的行为描述可以形象的理解为硬件电路上电后,各电路模块同时开始工作的过程。 有名块 Named-block 块是可以取名的,方法是在块语句开始标识符后面加上一个冒号,之后给出一个名字。 作用:①、便于实现对块语句执行过程的有效控制; ②、允许在块语句内部引入局部变量。 赋值语句 位于过程块中的赋值语句称之为过程赋值语句 过程赋值语句只能对寄存器类的量进行赋值