集成电路设计实验1

《集成电路设计实践》第一讲_A

课程进度安排(续二)

第9周:Cell-based设计方法及工具 3.1 Cell-based设计流程介绍 3.2 Verilog简介 第10周: 3.3 电路综合 第11周: 3.4 布局布线 3.5 DRC与LVS

课程进度安排(续三)

第12周:项目设计——CYCLIC ADC的设计 4.1 CYCLIC ADC原理 4.2 CYCLIC ADC电路设计 4.3 版图设计考虑 4.4 ADC性能仿真 4.5 设计报告要求 第13周:深亚微米工艺下的集成电路设计方法 5.1 按比例缩小原理 5.2 短沟道效应 5.3 深亚微米工艺下的设计讨论 5.4 SOC设计 第14~16周:项目设计与辅导

课程进度安排(续一)

第5周:Full-custom设计方法及工具 2.1 Full-custom设计流程介绍 2.2 原理图输入与电路网表导出 第6周: 2.3 HSPICE电路仿真 第7周: 2.4 版图编辑 第8周: 2.5 设计规则检查(DRC)与版图电路比对(LVS) 2.6 版图参数提取和后仿真 2.7 分层设计讨论

一. 集成电路设计基础

1.2 版图的基本概念

版图结构

集成电路加工的平面工艺

制 版 加 工

芯片的剖面结构

从平面工艺到立体结 构,需多层掩膜版,故 构,需多层掩膜版,故 版图是分层次的,由多 层图形叠加而成!

一个简单的例子

Vdd 版 图 in metal1

N+ 剖 N-阱 面 N-阱 图 P-substrate N+ P+

逆向电路提取 逆向电路提取

解剖照相 拼图 电路提取 分析与仿真

集成电路分类

集 成 电 路 按用途 数 字 集 成 电 路 模 拟 集 成 电 路 数 模 混 合 集 成 电 路 按集成规模 ULSI ULSI GLSI GLSI 大 规 模 超 大 规 模 集 成 电 路 按制作工艺 GaAs GaAs MOS MOS Bipolar Bipolar 集 成 电 路 集 成 电 路 按生产形式 标 专 准 用 通 集 用 成 集 电 成 路 电 路 ASIC ASIC

福州大学集成电路应用实验一

《集成电路应用》课程实验实验一 4053门电路综合实验学院:物理与信息工程学院专业: 电子信息工程年级: 2015级姓名:张桢学号:指导老师:许志猛实验一 4053门电路综合实验一、实验目的:1.掌握当前广泛使用的74/HC/HCT系列CMOS集成电路、包括门电路、反相器、施密特触发器与非门等电路在振荡、整形、逻辑等方向的应用。

2.掌握4053的逻辑功能,并学会如何用4053设计门电路。

3.掌握多谐振荡器的设计原理,设计和实现一个多谐振荡器,学会选取和计算元件参数。

二、元件和仪器:1.CD4053三2通道数字控制模拟开关2.万用表3.示波器4.电阻、电容三、实验原理:1.CD4053三2通道数字控制模拟开关CD4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。

CD4053的管脚图和功能表如下所示CD4053真值表输入状态接通通道根据CD4053的逻辑功能,可以由CD4053由4053电路构成如下图所示8种逻辑门(反相器与非门或非门、反相器、三态门、RS触发器、——RS触发器、异或门等)。

])2)(()(ln[T DD T DD T DD T V V V V V V V RC T -+--=2.多谐振荡器的设计非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。

电路的基本工作原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT 时,门的输出状态即发生变化。

因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。

可以利用反相器设计出如下图所示的多谐振荡器这样的多谐振荡器输出的信号周期计算公式为:当R S ≈2R 时,若:VT=0.5VDD ,对于HC 和HCU 型器件,有T ≈2.2RC对于HCT 型器件,有T ≈2.4RC四、实验内容:1. 验证CD4053的逻辑功能,用4053设计门电路,并验证其逻辑功能:(1)根据实验原理设计如下的反相器电路图:(2(3)验证逻辑功能:测试结果:0为低电平,1为高电平2.设计多谐振荡器:(1)根据实验原理设计如下的电路图:4053构成的RC振荡器(2)在面包板上连接电路。

实验一集成门电路逻辑功能测试实验报告

实验一集成门电路逻辑功能测试实验报告一、实验目的1、了解与掌握集成门电路的基本理论知识;2、了解和掌握使用示波器测量数字电路信号的原理;3、熟悉、掌握操作一个典型的集成门电路,能够完成输入、输出的测试;4、进一步学习实验技巧,提高操作及实际分析判断能力。

二、实验形式本实验采用实验班课题集成门电路逻辑功能测试的框架,使用典型的集成门电路元件,输入不同的控制信号,观察、量测集成门电路的输入输出行为,评价各个输入输出状态下系统的功能,分析和记录结果,探讨系统特性。

三、实验基础1、集成门电路:集成门电路是大规模集成电路中的一类电路,也称为数字逻辑电路。

它的基本功能就是进行逻辑运算,它通过特殊的电路结构,使多个信号输入后,经过基本的逻辑运算,呈现出几种功能或状态,对信号输入和输出做出反应,人们可以使用它来控制一系列的电子电路。

2、数字电路测试:数字电路测试技术是电子工程师经常采用的测量技术,是实现数字逻辑电路各种功能、参数的检测、测量技术,它是基于电路的特性、电路内外参数的变化,对具有规律数字变化的信号的变化情况进行观察与测量的技术。

3、示波器:示波器是一种常用的电子设备,它可以实时显示不同频率的电子信号的振幅及波形,是电子工程师的必备测量仪器。

示波器的采样速度必须高于测量信号最快变化率的2倍以上,以精确地记录信号振幅趋势,测量准确,结果真实可靠。

四、实验过程1、实验准备:根据实验要求准备相应的实验室、工装、测试电路,并根据实验要求搭建样板。

2、实验操作:(1)使用示波器观察不同输入情况下集成门电路输出信号的输出情况。

(2)重复进行输入信号的改变,记录示波器输出的曲线,比较输入信号的变化规律与输出信号的变化规律,得出系统的逻辑功能。

3、结果分析:根据测试结果,分析并记录系统及其输入输出信号的变化规律,分析系统的功能特性,探讨逻辑电路的应用和发展。

五、实验结果根据本次实验,我们对数字电路的操作和记录的结果,结果 depicted that the integrated gate circuit produced different output results when different input signals were applied. For example, when the input signal1 ‘A’was high andthe input signal2 ‘B’was low, the output was high; and when the inputsignal1 ‘A’was low and the input signal2 ‘B’was high, the output was low.充分表明了集成门电路的基本原理并且运用到实际的工程中。

实验一TTL门电路的逻辑功能测试

实验一TTL门电路的逻辑功能测试一、实验目的:1.了解TTL门电路的基本原理和逻辑功能;2.掌握TTL门电路的实验方法;3.学会使用逻辑分析仪测试TTL门电路的逻辑功能。

二、实验原理:TTL(Transistor-Transistor Logic)是一种基于晶体管的数字集成电路。

TTL门电路由NPN型和PNP型晶体管构成,通过输入端的电平状态控制输出端的电平状态。

常用的TTL门电路有与门、或门、非门、与非门、或非门等。

1. 与门(AND gate):只有当所有输入端都为高电平(逻辑1)时,输出端才为高电平;否则输出端为低电平(逻辑0);2. 或门(OR gate):只要有任意一个输入端为高电平,输出端就为高电平;否则输出端为低电平;3. 非门(NOT gate):输出端与输入端的电平相反;4. 异或门(XOR gate):当输入端的逻辑状态不同时,输出端为高电平;否则输出端为低电平;5. 与非门(NAND gate):当所有输入端都为高电平时,输出端为低电平;否则输出端为高电平;6. 或非门(NOR gate):只要有任意一个输入端为高电平,输出端为低电平。

三、实验仪器和器件:1.实验仪器:逻辑分析仪、示波器、直流电源、万用表;2.实验器件:TTL芯片(具体选用与门、或门、非门、与非门、或非门等)。

四、实验步骤:1.确定使用的TTL芯片,并查阅该芯片的技术手册,了解其引脚的功能和使用要求;2.将TTL芯片插入到实验面包板或焊接板上,根据技术手册连接相应的电源、输入端和输出端;3.打开逻辑分析仪,并将TTL芯片的输出端连接到逻辑分析仪的输入端,将TTL芯片的输入端连接到逻辑分析仪的输出端;4.打开逻辑分析仪的电源,并设置逻辑分析仪的采样频率和采样时间;5.根据TTL芯片的引脚定义和逻辑功能,设计特定的输入信号,并观察逻辑分析仪输出的波形;6.根据逻辑功能的定义,验证TTL芯片的输出是否与预期一致;7.记录实验数据,并分析实验结果。

实验1 逻辑门电路功能测试-实验报告

实验1 逻辑门电路功能测试实验报告一、实验目的1.熟悉常用逻辑门电路的功能。

2.了解集成电路引脚排列的规律及其使用方法。

二、实验仪器与设备1.数字电路实验箱。

2.数字万用表。

3.集成电路芯片74LS08、74LS32、74LS04、74LS00及74LS86各一片。

三、实验原理1. 三种基本逻辑运算(1)与运算与运算逻辑表达式可以写成Y = A·B、Y= A·B·C、……,与运算的逻辑关系也就是与逻辑。

与逻辑可以用图1-1所示开关电路来理解,它的状态组合见表1-1。

(2)或运算或运算逻辑表达式可以写成Y = A+B、Y = A+B+C、……,或运算的逻辑关系也就是或逻辑。

或逻辑可以用图1-3所示开关电路来理解,它的状态组合见表1-3。

同样,或逻辑开关电路的几种状态组合也可以用真值表来表示其逻辑关系。

在数字电路中,或逻辑的电路符号见图1-4所示。

(3)非运算逻辑表达式是Y=A,非运算的逻辑关系也就是非逻辑。

非逻辑开关电路只有表1-5所示两种状态组合。

同样,非逻辑的真值表和逻辑电路符号如表1-6和图1-6所示。

2. 常用复合逻辑运算几种常用的复合逻辑运算见表1-7所示。

表1-7 常用复合逻辑运算及其电路符号四、实验内容与步骤1.与逻辑功能测试图1-7所示芯片74LS08为四2输入与门。

图中管脚7为接地端,管脚14为电源端,管脚1、2为两个与输入端,它的输出端是管脚3,同样管脚4、5为输入端,管脚6为它的输出端,以此类推。

图1-7 74LS08管脚图(1)打开数字电路试验箱,选择芯片74LS08并按图1-7所示接线,将其中任一门电路的输入端接逻辑开关,它的输出端接发光二极管。

(2)按表1-8要求完成实验,每改变一次输入开关状态,观察并记录输出端的状态。

注意:芯片输入引脚悬空时,输入端为高电平。

输入状态输出状态U A U B Y0 0 00 1 01 0 01 1 10 悬空01 悬空 1悬空0 0悬空 1 1悬空悬空 1表1-8 74LS08功能测试图1-8所示芯片74LS32为四2输入或门。

数电实验报告:实验1-门电路的测试

广东海洋大学学生实验报告书(学生用表)实验名称课程名称 课程号 学院(系)专业 班级 学生姓名 学号 实验地点 实验日期实验1:集成逻辑门电路的测试一、实验目的:1. 学会检测常用集成门电路的好坏的简易方法;2. 掌握TTL 与非门逻辑功能和主要参数的测试方法;二、实验仪器与器件:3. 元器件:74LS20、74LS00(TTL 门电路)电阻、电位器若干;4. 稳压电源、万用表、数字逻辑箱。

三、实验原理:5.集成逻辑门电路的管脚排列:(1)74LS20(4输入端双与非门):ABCD Y =V CC 2A 2B N C 2C 2D 2Y1A 1B N C 1C 1D 1Y GNDV CC :表示电源正极、GND :表示电源负极、N C :表示空脚。

(2) 74LS00(2输入端4与非门):AB Y =V CC 4A 4B 4Y 3A 3B 3Y1A 1B 1Y 2A 2B 2Y GNDGDOU-B-11-112(3)4011(2输入端4与非门):ABYV CC4A 4B 4Y 3Y 3B 3A1A 1B 1Y 2Y 2B 2A GND集成门电路管脚的识别方法:将集成门电路的文字标注正对着自己,左下角为1,然后逆时针方向数管脚。

A)T TL与非门的主要参数有:导通电源电流I CCL、低电平输入电流I IL、高电平输入电流I IH、输出高电平V OH、输出低电平V OL。

注意:不同型号的集成门电路其测试条件及规范值是不同的。

B)检测集成门电路的好坏的简易方法:1)在未加电源时,利用万用表的电阻档检查各管脚之间是否有短路现象;2)加电源:利用万用表的电压档首先检查集成电路上是否有电,然后再利用门电路的逻辑功能检查电路。

例如:“与非”门逻辑功能是:“有低出高,全高出低”。

对于TTL与非门:若将全部输入端悬空测得输出电压为0.1V左右,将任一输入端接地测得输出电压为3V左右,则说明该门是好的。

四、实验内容和步骤:(1)测试芯片的与非功能;(2)TTL与非门的主要参数测试:1导通电源电流I CCL= 。

数字逻辑电路实验报告

数字逻辑电路实验报告指导老师:班级:学号:姓名:时间:第一次试验一、实验名称:组合逻辑电路设计1二、试验目的:掌握组合逻辑电路的功能测试。

1、验证半加器和全加器的逻辑功能。

2、、学会二进制数的运算规律。

3、试验所用的器件和组件:三、74LS00 3片,型号二输入四“与非”门组件74LS20 1片,型号四输入二“与非”门组件74LS86 1片,型号二输入四“异或”门组件实验设计方案及逻辑图:四、/全减法器,如图所示:1、设计一位全加时做减法运时做加法运算,当M=1M决定的,当M=0 电路做加法还是做减法是由SCin分别为加数、被加数和低位来的进位,、B和算。

当作为全加法器时输入信号A分别为被减数,减数Cin、B和为和数,Co为向上的进位;当作为全减法时输入信号A 为向上位的借位。

S为差,Co和低位来的借位,1)输入/(输出观察表如下:(2)求逻辑函数的最简表达式函数S的卡诺图如下:函数Co的卡诺如下:化简后函数S的最简表达式为:Co的最简表达式为:2(3)逻辑电路图如下所示:、舍入与检测电路的设计:2F1码,用所给定的集成电路组件设计一个多输出逻辑电路,该电路的输入为8421为奇偶检测输出信号。

当电路检测到输入的代码大于或F2为“四舍五入”输出信号,的个数为奇数时,电路。

当输入代码中含1F1=1;等于5是,电路的输出其他情况F1=0 F2=0。

该电路的框图如图所示:的输出F2=1,其他情况输出观察表如下:(输入/0 1 0 0 1 01 0 1 0 0 11 1 1 0 0 01 0 1 1 1 11 0 0 1 0 11 0 1 0 0 11 0 0 1 1 01 1 1 0 1 11 0 1 1 0 011111求逻辑函数的最简表达式(2)的卡诺如下:函数F1 F2函数的卡诺图如下:的最简表达式为:化简后函数F2 的最简表达式为:F1)逻辑电路图如下所示;(3课后思考题五、化简包含无关条件的逻辑函数时应注意什么?1、答:当采用最小项之和表达式描述一个包含无关条件的逻辑问题时,函数表达式中,并不影响函数的实际逻辑功能。

作业1——EDA与集成电路设计

作业1:MOS管的传输特性注:请统一用A4大小纸上交作业,作业有效期为一周。

1.1判断在下列条件下NMOS所工作的区域。

已知V tn=0.7V,且衬底端接GND。

(1)V GS=3.3V,V DS=3.3V;(2)V GS=0V,V DS=3.3V;(3)V GS=1.5V,V DS=0.5V;(4)V GS=2V,V DS=−0.5V;1.2已知一个CMOS半导体工艺中,L min=0.8μm,t ox=15nm,μn=550cm2/Vs,V tn=0.7V,(1)计算出C ox和k n; (C ox=εox/t ox,εox为氧化物的介电常数=3.9x8.85x10−14F/cm) (2)用此工艺制作一个NMOS管,W/L=16μm/0.8μm,若此时工作电流I D=100μA,并且工作在饱和区,那么此时的过驱动电压V ov,V GS,以及能工作在饱和区的最小V DS(min)为多少?(3)同样的NMOS,若此时电压V DS非常小导致NMOS以一个1000Ω的电阻工作,请问此时的V ov,V GS为多少?1.3画出MOS晶体管的ID~VGS曲线,以以下两个参数为变量:(a)以VDS为参数,VDS1<VDS2<VDS3;(b)以VBS为参数,VBS=0与VBS>0。

并在特性曲线中标出饱和区与线性区的夹断点。

1.4一个NMOS管的参数为W=10um,L=1um, k n=194uA/V2,λ=0.024V−1,t ox=80Å,ϕf=0.3V,V t0=0.6V,N A=5x1015atoms/cm3,忽略速率饱和效应,假定V SB=0,试分别绘出V GS=0.5V,1.5V,3V时的I D−V DS特性曲线。

V DS取0到3V;1.5W/L=50/0.5,|ID|=0.5mA,计算NMOS和PMOS饱和区的跨导和输出阻抗,以及本征增益。

规定本征增益为g m r0。

表1:MOS管的一级SPICE模型。

实验1-门电路逻辑功能及测试

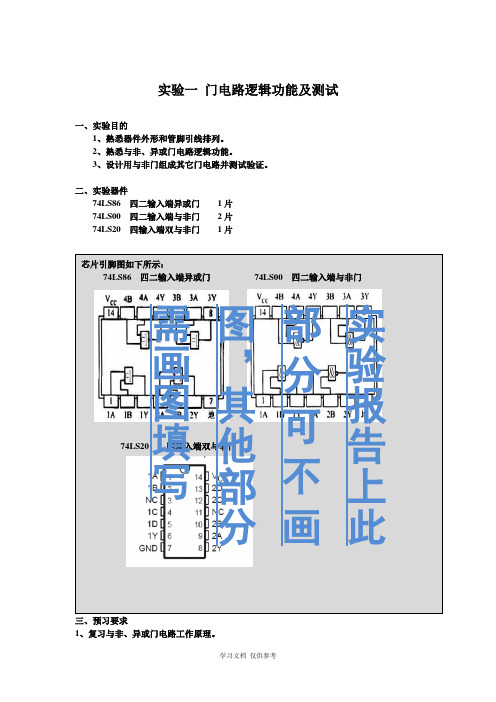

实验一 门电路逻辑功能及测试一、实验目的1、熟悉器件外形和管脚引线排列。

2、熟悉与非、异或门电路逻辑功能。

3、设计用与非门组成其它门电路并测试验证。

二、实验器件74LS86 四二输入端异或门 1片 74LS00 四二输入端与非门 2片 74LS20 四输入端双与非门 1片三、预习要求1、复习与非、异或门电路工作原理。

芯片引脚图如下所示:74LS86 四二输入端异或门 74LS00 四二输入端与非门74LS20 四输入端双与非门实验报告上此部分可不画图,其他部分需画图填写2、熟悉所用集成电路的引线位置及各引线用途。

四、实验内容及步骤实验前先检查实验箱电源是否正常。

然后对所选实验用的集成电路进行连线,特别注意Vcc及地线不能接错。

实验中改动接线须先断开电源,接好线后再通电源。

1、测试门电路逻辑功能〔1〕选用四输入端双非门74LS20一只,插入设计板,按图1接线,输入端a、b、c、d接S1—S4(电平开关输出插口),输出端L接电平显示发光二极管〔D1—D8任意一个〕。

(2) 将电平开关按表1置位,分别测出输出逻辑状态。

将输出结果填入表1中。

输入输出a b c d L1 1 1 1 00 1 1 1 10 0 1 1 10 0 0 1 10 0 0 0 12、异或门逻辑功能测试〔1〕选四二输入端异或门74LS86,按图2接线,输入端a、b、c、d接电平开关,输出端A、B、Y接电平显示发光二极管。

〔2〕将电平开关按表2置位拨动,将输出结果填入表2中。

图2表2输入输出a b c d A B Y0 0 0 0 0 0 01 0 0 0 1 0 11 1 0 0 0 0 01 1 1 0 0 1 11 1 1 1 0 0 00 1 0 1 1 1 03、分析并验证逻辑电路的逻辑关系〔1〕用74LS00按图3、图4接线,将输入输出关系分别填入表3、表4中。

〔2〕写出上面两个电路的逻辑表达式。

图3图4输入输出A B Y0 0 00 1 11 0 11 1 1输入输出A B Y Z0 0 0 00 1 1 01 0 1 01 1 0 14、组成或非门: 用一片二输入端四与非门74LS00组成或非门。

集成电路设计实践1_187401985

课程简介

成绩评定:

• 平时成绩: 20%

– 中期检查,安排在选题及方案设计、电路设计、 版图设计等阶段

• 答辩及总结报告: 80%

– 课程项目的完成质量 – 答辩情况 – 总结报告的书写质量

• 选题, 设计, 流片, 答辩, 总结报告等缺一不 可, 否则不给成绩

课程简介

• 总结报告要求

第一部分: 摘要 (中、英文) 300字 包括设计的内容、预期目的、主要电路结构、测试

课程历史

开课时间:2000年~ 开课单位:电子系 微电子所 授课对象:工学硕士 工程硕士 加工工艺:0.8um 0.6um 0.5um 授课老师:李冬梅 黄亚东 李福乐 授课方式:设计实践为主 设计实践/课堂教学 并重 选题范围:自由选题 单一命题 自由选题 教学效果:(IC设计)课程学习课题研究的桥梁

第11~18周

流水加工

答辩会

测试

秋季学期

课程报告

课程项目:

课程简介

• 结合本人的论文课题方向自行设计题目 • 结合实验室的科研任务设计题目 • 鼓励做有创新的、有用的设计 • 参考题目:

– Bandgap+LDO, 温漂<50ppm – LDO/Charge pump buck – On-Chip Temp. Sensor – 传感器接口电路(电容/电阻) – DAC/DDS信号合成电路 – ADC:Flash, SAR, Cyclic, Pipeline, sigma-delta, … – Low-pass Active-RC or Switched-capacitor filter – Oscillator (Crystal, RC) – PLL时钟倍频电路,Fi = 8MHz, Fo = 64MHz – SRAM • 自由组队,合作完成,1~2人/题目 • 每组推选一个组长,负责任务的协调分配,每组交一个设计报告,在 报告最后需说明组内个人的工作内容

实验一_QuartusII的使用

实验一_QuartusII的使用引言:Quartus II是一款由美国Intel公司开发的FPGA设计软件,广泛应用于数字集成电路设计和原型验证。

本实验将介绍Quartus II的基本使用方法,包括项目创建、设计输入、约束设置、编译与仿真等。

一、环境准备二、项目创建1.启动Quartus II软件,选择"File" -> "New Project Wizard"创建新项目。

在弹出的对话框中,选择项目的存储位置和名称,并选择合适的目标设备和设计流程。

点击"Next"进入下一步。

2.在第二步中,选择项目的项目类型和是否要添加预定义的IP (Intellectual Property)核。

IP核是现成的、可重用的模块,可以简化设计。

根据自己的需求进行选择,点击"Next"。

3.在第三步中,选择顶层设计文件的命名,并点击"Next"。

5.在第五步中,对项目的设置进行回顾,并点击"Finish"完成项目创建。

三、设计输入1.双击项目中的顶层设计文件,打开Design Entry工具。

在Design Entry工具中,可以通过图形界面或者Verilog/VHDL语言进行设计输入。

a.如果选择使用图形界面,可以在左侧工具栏中选择需要的元件,然后在设计区域中拖拽放置,最终形成需要的电路结构。

b.如果选择使用Verilog/VHDL语言,可以在设计区域中输入相应的代码,然后进行语法检查。

2.在设计完成后,可以使用编译按钮对设计进行编译。

编译过程中,Quartus II会对设计进行分析、优化和进行布线等操作,生成逻辑网表。

四、约束设置1.双击项目中的顶层设计文件,打开Design Constraints工具。

在Design Constraints工具中,可以设置时钟频率、信号约束、引脚约束等。

实验一集成门电路逻辑功能测试实验报告

数字电子技术实验报告实验名称:集成门电路逻辑功能测试一、实验目的:1、验证常用集成门电路的逻辑功能;2、熟悉各种逻辑门电路的逻辑符号;3、熟悉TTL集成电路的特点、使用规则和使用方法。

二、实验设备及器件:1、数字电路实验箱2、74LS00四2输入与非门1片74LS86四2输入异或门1片74LS11三3输入与门1片74LS32四2输入异或门1片74LS04反相器1片三、实验原理:集成逻辑门电路是最简单、最基本的数字集成元件,目前已有种类齐全集成门电路。

TTL集成电路由于工作速度高、输出幅度大、种类多、不易损坏等特点而广泛使用,特别对学生进行实验论证,选用TTL电路较适合,因此这里使用了74LS系列的TTL电路,它的电源电压为5V+10%,逻辑电平“1”时>2.4V,低电平“0”时<0.4V。

实验使用的集成电路都采用的是双列直插式封装形式,其管脚的识别方法为:将集成块的正面(印有集成电路型号标记面)对着使用者,集成电路上的标识凹口朝左,右下角第一脚为一脚,按逆时针方向顺序排布其管脚。

四、实验步骤:(一)、根据接线图连接,测试各门电路逻辑功能1、与门逻辑功能测试被测试器件为74LS11三3输入与门,其引脚图见实验教材P6。

(1)按图1-1(见实验教材P6)接线,门的三输入端节逻辑开关输出插口,以供“0”与“1”电平信号,开关向上,输出逻辑“1”,先下输出逻辑“0”。

门的输入端接LED发光二极管。

(实验时,利用DSWPK开关其电路图如下)(2)按表1-1要求用开关改变输入端A、B、C的状态,借助指示灯观测个相应输出端F的状态,当电平指示灯亮时记为“1”,灭时记为“0”,把测试结果填入表1-1中。

表1-1 74LS11逻辑功能表2、或门逻辑功能测试(1)按图1-2接线(见实验教材P6),按表1-2要求用开关改变输入端A、B的状态,借助指示灯各相应输出端F的状态,把测试结果填入表1-2中。

(其实验电路图如下)表1-2 74LS32逻辑功能表3、非门逻辑功能测试(1) 按图1-3接线(见实验教材P 7),按表1-3要求用开关改变输入端A 的状态,借助指示灯各相应输出端F 的状态,把测试结果填入表1-3中。

模拟集成电路实验1

一、实验目的1.熟练掌握使用Cadence Virtuoso ADE5.1.41软件进行原理图的编辑2.使用器件设计参数表格的数据进行电路设计3.掌握基本差分对电路的设计方法二、实验软件:Cadence IC Virtuoso ADE 5.1.41第一部分 基本差分对设计独立完成实验设计指标: 已知:VDD=3.3V , Iss=300uA要求:Av>40dB ,共模输入范围1.2 2.5inCM V ≤≤,最大共模输入电压下,输出摆幅1V >,共模抑制比85CMRR dB ≥1.1 基本差分对设计分析及参数估算一、参数估算1.根据共模输入范围inCM V 和输出摆幅的要求,各个MOS 管的过驱动电压并估算偏置电压VB 和输出Vout (也即VA )的静态值,电路如图1所示,min 131 1.2inCM GSN B TN on B V V V V V V =+-≈+≤B N30.2, 1.00.8,0.80.540.26on V V V V V ⇒=≤==-=onN1B 可以取V V 取max 121212|| 2.5inCM A TN GSP TN onP TN TP V V V VDD V V VDD V V V =+=-+=-+-≥即2 3.3 2.50.540.750.59onP V ≤-+-=指标要求最大共模输入电压,输出摆幅要求大于1Vmin max 1 2.50.54 2.06out inCM Tn V V V =-=-=故max 2.061 3.06out V ≥+=,由此可得2max 3.3 3.060.24onP out V VDD V ≤-=-=该值要和通过共模输入范围要求得到的2 3.3 2.50.540.750.59onP V ≤-+-=求交集,取20.2onP V V =,于是估算输出点的静态电压223.3(||) 3.3(0.20.75) 2.35out A onP TP V V V V ==-+=-+=2.确定输入的静态共模电平值。

2 Cadence IC实验一、二、三

2、输入特性

三极管的输入特性是指当集电极电压Vce为常数时,基极与发射极间电压Veb与基极电流ib之间的关系。

如同前一个实验介绍的方法,打开仿真窗口,先设置好model路径,模型文件依然选择/cad/smic018_tech/Process_technology/Mixed-Signal/SPICE_Model/ms018_v1p6_spe.lib,注意section设为bjt_tt。然后添加变量vbe和vce。再按图2.3对话框设置好DC分析。其中DC分析是对vbe进行扫描,扫描范围从0到1.8V。vce的初始值设为1.5V。最后设置输出,这里我们要看的是基极电流,所以点击三极管的基极pin脚。

然后点“Netlist and Run”进行仿真。得到的输入特性曲线如图2.4所示。横坐标是基极-射极电压vbe的变化,纵坐标是基极电流ib的变化。

3、输出特性

三极管的输出特性是指以iB为参变量的共射极电流iC与UCE之间的关系。

先设置好Analog Design Enviroment对话框,注意这次DC分析所扫描的变量是vce,扫描范围为-0.3到1.8V。如图2.5所示:

如同前面的方法,打开仿真窗口,先设置好model路径,库文件与上面的相同,但工艺角(section)填入tt。然后添加变量vds和vgs。接着设置DC分析。其中DC分析是对vds进行扫描,扫描范围从0到1.8V。vgs的初始值设为0V。最后设置输出,这里我们要观察的是MOS管的漏电流,所以点击MOS管的漏极。设置好后的仿真窗口如图2.11所示。

电压源的参数设置图1.3所示,在DC voltage处填入vin(填入变量是为了要做直流扫描)

实验1 集成门电路的逻辑功能与参数测试

实验一TTL集成门电路的逻辑功能与参数测试一、实验目的1、掌握TTL集成与非门的逻辑功能和主要参数的测试方法2、掌握TTL器件的使用规则3、进一步熟悉数字电路实验装置的结构,基本功能和使用方法二、实验原理本实验采用四输入双与非门74LS20,即在一块集成块内含有两个互相独立的与非门,每个与非门有四个输入端。

其逻辑框图、符号及引脚排列如图1-1(a)、(b)、(c)所示。

(b)(a) (c)图1-1 74LS20逻辑框图、逻辑符号及引脚排列1、与非门的逻辑功能与非门的逻辑功能是:当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全部为高电平时,输出端才是低电平(即有“0”得“1”,全“1”得“0”。

)其逻辑表达式为 Y=2、TTL与非门的主要参数(1)低电平输出电源电流ICCL 和高电平输出电源电流ICCH与非门处于不同的工作状态,电源提供的电流是不同的。

ICCL是指所有输入端悬空,输出端空载时,电源提供器件的电流。

ICCH是指输出端空截,每个门各有一个以上的输入端接地,其余输入端悬空,电源提供给器件的电流。

通常ICCL >ICCH,它们的大小标志着器件静态功耗的大小。

器件的最大功耗为PCCL =VCCICCL。

手册中提供的电源电流和功耗值是指整个器件总的电源电流和总的功耗。

ICCL 和ICCH测试电路如图1-2(a)、(b)所示。

[注意]:TTL电路对电源电压要求较严,电源电压VCC只允许在+5V±10%的范围内工作,超过5.5V将损坏器件;低于4.5V器件的逻辑功能将不正常。

(a) (b) (c) (d)图1-2 TTL与非门静态参数测试电路图(2)低电平输入电流IiL 和高电平输入电流IiH。

IiL是指被测输入端接地,其余输入端悬空,输出端空载时,由被测输入端流出的电流值。

在多级门电路中,IiL相当于前级门输出低电平时,后级向前级门灌入的电流,因此它关系到前级门的灌电流负载能力,即直接影响前级门电路带负载的个数,因此希望IiL小些。

verilog hdl数字集成电路设计与原理(一)

verilog hdl数字集成电路设计与原理(一)Verilog HDL数字集成电路设计与原理1. 引言•Verilog HDL是一种硬件描述语言,用于描述数字集成电路的行为和结构。

•本文将从基础开始,详细介绍Verilog HDL的设计与原理。

2. Verilog HDL基础知识•Verilog HDL是一种高级硬件描述语言,它允许我们使用模块化的方式来描述数字集成电路。

•通过Verilog HDL,我们可以描述电路的输入、输出以及内部逻辑。

•Verilog HDL使用模块化的形式,将电路划分为多个模块,每个模块负责完成特定的功能。

3. Verilog HDL模块•在Verilog HDL中,一个模块可以包含多个输入端口和输出端口。

•输入端口用于接收外部信号,输出端口用于输出内部计算结果。

•通过模块之间的互连,可以构建出复杂的电路结构。

4. Verilog HDL信号•在Verilog HDL中,信号是电路中的基本元素,可以是任何数据类型。

•信号可以通过赋值语句进行操作,例如逻辑运算、赋值操作等。

•信号的值可以在时钟的上升沿或下降沿进行更新。

5. Verilog HDL运算符•Verilog HDL提供了各种运算符,用于实现数字集成电路的运算功能。

•运算符包括逻辑运算符、位运算符、算术运算符等。

•运算符的选择和使用需要根据电路的需求进行灵活调整。

6. Verilog HDL过程•在Verilog HDL中,过程用于描述电路的行为和时序逻辑。

•过程包括组合逻辑过程和时序逻辑过程。

•组合逻辑过程是对输入进行组合运算得到输出,时序逻辑过程则需要考虑时钟和状态的变化。

7. Verilog HDL测试与调试•在实际设计中,测试与调试是非常重要的环节。

•可以通过自动生成测试向量、仿真、波形查看等方式进行测试与调试。

•通过不断优化和调试,可以确保电路设计的正确性和可靠性。

8. 总结•Verilog HDL是数字集成电路设计与原理中的重要工具和技术。

清华大学 集成电路设计实践 ic1-background

集成电路的进展内容简介 集成电路的应用领域 集成电路的制造过程 制 从CPU的发展看IC的进展 从行业的发展看IC C的进展 从ISSCC SSCC看IC C的发展方向2010-3-2清华大学微电子学研究所2集成电路的应用领域Communications Computer & Storage gWireless Cellular Basestations Wireless LANNetworking Switches RoutersWireline Optical Metro AccessComputer Servers Mainframe WorkstationsStorage RAID SANOffice AutomationCopiers Printers MFPConsumerIndustrialEntertainment Broadband Audio/Video Video DisplayBroadcast Studio Satellite BroadcastingInstrumentation st u e tat o Medical Test Equipment ManufacturingSecurity/ Energy M E Mgmt. tAuto Navigation EntertainmentMilitary ta y Secure Comm. Radar Guidance & ControlCard Readers Control Systems ATM3中国大陆地区2008 年集成电路设计产 业的有关情况根据商务部统计信息: 2007年集成电路及微电子组件进口金 额高达1277亿美元;是原油进口额的1.6 倍2008年1-10月 集成电路进口:1119亿美元 集成电路进 成品油:278亿美元 原油:1167亿美元 特殊时间:石油价格飞涨2008年大陆地区集成电路设计全行 业销售总额为345亿元,同比增长 23.5%需求大、本地企业小、不断发展集成电路的制造过程-晶圆Single dieWafer6” (15cm) 17000 mm2 8” (20cm) 31000 mm2 12” (30cm) 70000 mm2From 2010-3-2 清华大学微电子学研究所 5集成电路的制造过程-封装Wire BondingSubstrate Die PadLead Frame2010-3-2清华大学微电子学研究所6集成电路的制造过程-芯片2010-3-2清华大学微电子学研究所7集成电路的制造过程-成本 NRE(NonRecurring Engineering) Cost is Increasing0.35um 40k$ 0.25um 80k$ 0.18um 160K$ 0.13um 250K$ 90nm 900K$2010-3-2 清华大学微电子学研究所 8内容简介 集成电路的应用领域 集成电路的制造过程 从CPU的发展看IC的进展 从行业的发展看IC的进展 从ISSCC看IC的发展方向2010-3-2清华大学微电子学研究所9摩尔定律Intel的创始人戈登摩尔(Gordon Moore) •“集成电路所包含的晶体管每18个月就会翻一番” 个月就会翻 番”2010-3-2清华大学微电子学研究所10PDP1(1960)PDP-1(1960)The PDP-1 sold for $120,000.MIT wrote the firstvideo game, Spaceg pWar! for it.A total of 50 wereA total of50werebuilt.INTEL CPUINTEL CPU的发展i4004 1971年11月15日,成立3年的Intel公司推出了世界上第一个微处理器(4004CPU),4位微处理器,10微米的工艺,16针DIP封装,尺寸为3*4mm,共有2300个晶体工艺封装尺寸为3*4共有管,工作频率为108KHz,每秒运算6万次。

集成电路分析与设计1

N+

N+

P N阱

N+- BL

1.4 BiCMOS工艺简介

双极工艺为基础 的BiCMOS工艺(1)

(1)以CMOS工艺为基础的BiCMOS工艺中,影响 BiCMOS电路性能的主要是双极型器件。显然, 若以双极工艺为基础,对提高双极型器件的性 能是有利的

(2)这种结构克服了以P阱CMOS工艺为基础的 BiCMOS结构的缺点,而且还可以用此工艺获得 对高压、大电流很有用的纵向PNP管和LDMOS及 VDMOS结构

C

EB

PMOS

NMOS

N+

P

N 阱 N+

N+

P+ P阱 P+

N 阱 P+ N+ N+

P阱 N+ 外 延 层

P+

P- SUB

1.4

BiCMOS工艺简介

双极工艺为基础 的BiCMOS工艺(4)

这种结构的特点是采用N+及P+双埋层双阱结构, 采用薄外延层来实现双极器件的高截止频率和 窄隔离宽度。

此外,利用CMOS工艺的第二层多晶硅做双极器 件的多晶硅发射极,不必增加工艺就能形成浅 结和小尺寸发射极。

这种结构的缺点是: (1)由于NPN晶体管的基区在P阱中,所以基 区的厚度太大,使得电流增益变小 (2)集电极的串联电阻很大,影响器件性能 (3)NPN管和PMOS管共衬底,使得NPN管只 能接固定电位,从而限制了NPN管的使用

1.4

BiCMOS工艺简介

N阱CMOS工艺为基础 的BiCMOS工艺(1)

(d)硅片刻蚀 (e)场氧生长 (f)表面去除氮化物或氧化物

1.2 CMOS工艺流程 基本流程(3)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成电路设计实验报告

院别:电信学院专业:电子科学与技术

班级:电子姓名:学号:组序:

实验(一)题目名称:熟悉L-EDIT软件工具

成绩:教师签名:批改时间:

一、实验目的:

学会使用集成电路版图设计L-EDIT软件工具,熟练画电路版图的操作指令和各种快捷命令,并熟悉应用特定工艺库即工艺文件来实现电路。

通过该实验,使学生掌握L-EDIT的设计方法,加深对课程知识的感性认识,增强学生的设计与综合分析能力,为将来成为优秀的后端工程师做准备。

二、实验要求:

如将设计好的电路制成实际使用的集成块,就必须利用版图工具将设计的电路采用标准工艺文件转换成可以制造的版图。

然后再将版图提交给集成电路制造厂家(foundry),完成最后的集成块制造,所以画版图的本质就是画电路原理图。

在画版图时,首先要明白工艺文件的含义,每一种工艺文件代表一条工艺线所采用的光刻尺寸,以及前后各个工序等等;其次要懂得所使用的工具步骤及各个菜单及菜单栏的内容,以便熟练使用该软件;最后对所画版图进行验证,确保不发生错误。

此外,还必须了解所使用的版图设计法则,对于不同的工艺尺寸其法则有所不同,这就要求设计者在应用该软件时,必须熟悉相应的设计法则,为完成正确的版图做准备。

该实验原理是画常用的NMOS管,画图时要求熟悉NMOS的工艺过程及设计法则。

三、实验方法:

熟悉L-EDIT版图软件工具及工艺库相关内容,熟练该软件工具菜单功能及使用方法。

以PMOS器件为例,在调用相应的工艺文件基础上,画元器件的物理实现版图(如选用几微米的工艺线、设计法则等),设计完成后运用该软件的设计规则对所画的版图进行DRC验证,并修改不正确的部分,直至设计无错误。

四、实验内容:

1.安装L-EDIT仿真软件:先点击Daemon.exe文件,用虚拟光驱将.ISO文件

载入,并点击L-EDIT的Setup.exe文件即可。

2.按照Crack方式注册该软件,并运行。

3.以MOSIS提供的morbn20.tdb工艺库为例,从ReadMe中可以了解许多信息:

工艺提供制造商、工艺尺寸、设计规则及器件剖面图等。

4.以morbn20.tdb工艺库为例,画NMOS版图。

File→New→Copy TDB setup

from。

5. 点击Browse选择根目录Tanner→LEDIT83。

6. 点击LEDIT83→Samples。

7. 点击Samples→tech。

8. 点击tech→mosis。

9. 在mosis文件夹下,选择工艺库文件morbn20.tdb。

10. 版图的详细设计规则:Setup→Design,也可在file→open→morbn20.tdb。

包含有工艺线大小、设计规则、工艺流程等。

11. 画N Well掩模板,其中宽度W = 32µm 高度H = 20µm。

如果对需要对图

形进行修改,先将光标箭头放在该图形的边缘,点击鼠标中键即可完成拉长或缩短。

12. 画P select掩模板,其中宽度W = 18µm 高度H = 15µm。

13. 画Active有源区掩模板,其中宽度W = 14µm 高度H = 6µm。

该有源区与左边、右边和下边的间距都为2µm。

14. 画N select掩模板,其中宽度W = 9.5µm 高度H = 15µm。

15. 画Active有源区掩模板,其中宽度W = 5.5µm 高度H = 6µm。

16.画Poly多晶硅,其中宽度W = 2µm;高度H = 10µm及宽度W = 6µm;

高度H = 6µm两图形。

17.画Active contact有源区接触孔及Ploy contact接触孔,宽度W = 2µm;

高度H = 2µm。

18 画Metal1,宽度W = 4µm;高度H = 4µm。

18.进行设计规则检查,Tools→DRC即可。

19.检查没有错误,表示所画版图正确。

21. 如果不能通过DRC,则点击此叉图来查找问题,并改正。

五、实验中遇到的问题和解决办法

六、实验体会:

1.通过本次实验,初步了解了集成电路版图设计L-EDIT软件工具栏的菜单功能及使用方法,还有一些操作指令和快捷命令。

2.掌握了L-EDIT的设计方法,知道了NMOS管的版图设计,熟悉了NMOS的工艺过程及设计法则,加深了对课程知识的感性认识。