SOC design process_1

ASIC第八章-SOC(1)

SoC Design: system architecture+ IC

Motivation of SoC

Application perspective

More complicated system Low cost of computation Higher reliability

Engineering design perspective

SOC设计面临的挑战 可制造性设计(DFM)

对设计人员来说,需要在版图完成以后进行 DFM设计规则检查。 DMA设计规则通常包括金属密度、间距、线宽、 通孔、转角、电流密度等。 DFM设计规则本质上与普通设计规则相互补充 但事实上由于DFM的修正,会对布局布线造成 影响,进而改变原有的一些时序特性,增加了 设计的复杂性。

Design Object Shift

Design Complexity

Density

0.25µm 2000

Timing Closure

SI

Low Power

DFM/Y

0.18µm 2002

0.13µm

90nm 2004

65nm 2006

SOC设计面临的挑战 (1) 集成密度(复杂性)

包含多种功能模块:处理器核、DSP核、数字逻 辑核、存储器核等。IP核的多样性造成了验证 的复杂性。 芯片规模增大,I/O管脚增多,使测试难度增 加。 混合电路设计,要求在高密度下实现数字电路 和模拟电路的集成与信号交互,复杂性增加。

RISC architecture ARM7, ARM9, ARM10, ARM11 MIPS (Microprocessor without interlocked piped stages) RISC architecture MIPS 32, MIPS 64 PowerPC (Developed by IBM、Motorola、 Apple)

Soc设计

Focus shifted from individual products to product "platforms" Many IPs: hardware and software Application or architecture related platform Short develop time

System on Programmable Chip -SoPC

•

Many IPs + FPGA/CPLD on a chip Customizable: Chip was fabricated most of the way Only last few metal layers waiting for your custom part Field-programmable: Chip bought as it, customized by customer like FPGA Allowed to change the functionality of the chip according to the application

Motivation of SoC

• Application perspective

• Engineering design perspective

More complicated system Low cost of computation Higher reliability

What is SoC?

• SoC: System-on-Chip

• SoC Design: system architecture+ IC

Complex integrated circuit (IC) that integrates the major functional elements of a complete end-product into a single chip using silicon intellectual property (IP) blocks. Dataquest 1995: Contains at lest one of MPU or DSP core and memory and more than 100k gates

SoC设计方法和实现第十一章 低功耗-文档资料

Leakage vs. Process

• What will be the dominated leakage

current?

Long Channel(L>1um) Very small leakage Short channel (L>180nm,tox>30A) Subthreshold leakage

• Power limits to the wall

Challenge of Design as Process Scaling

Outline

• Why low power • Sources of power consumption • Low power design methodology • Low power techniques • Power analysis and tools • Trends in the future

Why Low Power

• Potable system - Battery lifetime • Desktops: high power consumption

Example: mobile phone, PDA, Digital camera Reliability and performance Need expensive chip package, cooling system Decreased reliability and performance Increased cost: packaging cost and cooling system Exceed power limits of the chip & system

Source of Power Consumption

Soc 设计 课件

• Fault Model Derived

Why Model Faults?

• Fault model identifies target faults • Fault model makes analysis possible • Effectiveness measurable by

experiments

Package • BGA • QFP • PGA • TAB • CSP • SIP • MCM • ...

Coverage • DC • AC • Digital • Analog • Speed • Temp • Power • ...

Qualification • Burn-in • Temp-Cycle • HVST • ESD • Latch-up • ...

Defect & Fault Modeling Definition

• Defect: Physical abnormally fabricated die • Fault: behavior difference due to a defect • Error: machine failure due to a fault

Test Challenges

• Reduce the cost of test

• Increase the defect coverage

Reduce Reduce Reduce Reduce

the the the the

vector data size tester sequencing complexity cost of test equipment test time

0 0

SoC-Encounter设计流程ppt

SMIC 65nm process

2024/8/14

2011-10-24

主要内容

1. Initial_design 2. Floorplan 3. Pre_place 4. Place_opt 5. Clock_syn 6. Clock_opt 7. Nano_route

命令:

loadCPF $cpf_file

commitCPF

2024/8/14

1.Initial_design

MMMC:

MMMC=multi-mode and multi-corner 即多角多模分析法

一般情况下有以下几种分析方法:

Full MMMC(完全方法)

分析所有工作模式下的最好最坏角点。

#### scan trace and generate original scan def

:输出扫描链

另外还有specifyScanCell(指定扫描单元)和specifyScanChain(指定名称和输入输出端 口)命令等。

2024/8/14

1.Initial_design

Load CPF file:

normal_setup2_max_dcw_view normal_setup1_max_dcw_view} \

-hold { normal_func2_min_dcb_view }

#### set analysis mode

:设置时序分析模式

setAnalysisMode -analysisType onChipVariation \

根据上面产生的模式组合和角点组合,结合时间的情况及方法,生成能够切实代表时序分析情况的 view组合。一般情况下,每次进行时序分析和优化时,只激活部分的view进行操作,使用的命令为: set_analysis_view。下次再进行分析和优化时再激活别的部分view进行操作。

Synopsys SoC 架构设计指南说明书

IP加速DesignWare IP,针对您的SoC进行调整从一开始就保证正确的 SoC 架构每一个复杂的 SoC 设计都是在巨大的上市时间压力下创建出来的。

随着软件内容的增加以及更多IP (以及更复杂IP)被集成,设计人员面临着在不过度设计 SoC 的情况下性能、功耗和面积目标等诸多挑战。

作为您的设计团队的一员,Synopsys 的 SoC 架构设计顾问将帮助您的 SoC 在正确的起点开始。

顾问们已经准备好将他们多年的设计手机、汽车、网络和物联网 SoC 的专业技能应用到您独特的设计中。

这些顾问将在以下方面应用并分享他们的深厚知识:• CPU、DSP和 ASIP 功能• 制定低功耗策略• 关键模块的设计(RTL,ASIP)• PPA 估算• 内存架构,总线带宽/延迟• 验证和基于 FPGA 的原型设计与您的 SoC 一样独特的 IP在为您的快节奏的市场打造 SoC 时,如果能够把针对您的设计调整的 IP 整合到一起,这将会为您带来竞争力上的优势。

然而现成的 IP 已经不足以应对您的设计挑战。

我们期待 IP 供应商能提供更多解决方案,包括简化 IP 配置和集成以及加速软件开发等。

Synopsys的“ IP 加速”计划将重新定义您对 IP 供应商的期望,它能帮助您以更少的功夫、更低的风险和更快的上市速度成功地将IP集成到您的 SoC 中。

“Synopsys团队提出了详细的建议来测试并构建我们 AI SoC的复杂接口,帮助确保我们按时启动项目。

”〜 一家领先的人工智能计算公司的研发总监预先验证的 IP 子系统,可由您或我们的团队 进行定制随着硬件和软件复杂性的增加,您需要更先进的集成 IP 解决方案来满足您快速的项目进度,同时还不能影响质量。

无论您需要单个控制器和 PHY 集成、多种协议的组合或者是需要具有处理器及软件堆栈的完整子系统,Synopsys 专家都能够交付针对您的 SoC 进行优化的 IP 子系统。

SOC设计实验报告

Operating Conditions: cb13fs120_tsmc_max Library: cb13fs120_tsmc_max

Wire Load Model Mode: Inactive.

Startpoint: state_reg[0]

begin

state<=st1;

end

end

end

st2:

begin

if(five==1)

begin

state<=st3;

end

else

begin

if(ten==1)

begin

state<=st3;

end

else

begin

state<=st2;

end

end

end

st3:

begin

state<=st0;

reg five_cents,ten_cents;

wire soda_out;

always #1 clk=~clk;

initial

begin

clk=0;

five_cents=0;

ten_cents=0;

rst_n=1;

#10 rst_n=0;

#10 rst_n=1;

rtl/

#读文件

Link

#连接到目标库

如果通过了偶校验则进入evenblank状态来使pcm30空缺248位,此时进入帧校验的奇校验;

帧校验的奇校验使用三个状态来完成,分别为:oddhold0,oddhold1,oddhold2来校验奇帧的1、2、3位;

电子信息行业集成电路设计方案

电子信息行业集成电路设计方案第1章集成电路设计概述 (3)1.1 背景与意义 (3)1.2 发展历程与现状 (4)1.3 设计流程与规范 (4)第2章集成电路设计基础 (5)2.1 半导体物理基础 (5)2.1.1 半导体的性质与分类 (5)2.1.2 半导体的能带理论 (5)2.1.3 半导体的掺杂 (5)2.2 半导体器件原理 (5)2.2.1PN结原理 (5)2.2.2 二极管 (6)2.2.3 晶体管 (6)2.3 集成电路制造工艺 (6)2.3.1 光刻技术 (6)2.3.2 蚀刻技术 (6)2.3.3 掺杂技术 (6)2.3.4 化学气相沉积 (6)2.3.5 封装技术 (6)第3章集成电路设计方法 (6)3.1 数字集成电路设计 (6)3.1.1 逻辑设计 (7)3.1.2 逻辑综合 (7)3.1.3 布局与布线 (7)3.1.4 版图设计 (7)3.2 模拟集成电路设计 (7)3.2.1 电路拓扑选择 (7)3.2.2 元器件参数设计 (7)3.2.3 电路仿真与优化 (7)3.2.4 版图设计 (7)3.3 混合信号集成电路设计 (8)3.3.1 数字与模拟分离设计 (8)3.3.2 模块集成与接口设计 (8)3.3.3 供电与隔离 (8)3.3.4 仿真与验证 (8)3.3.5 版图设计 (8)第4章集成电路设计工具 (8)4.1 电子设计自动化(EDA)工具 (8)4.1.1 EDA工具的作用 (8)4.1.2 EDA工具的分类 (9)4.2 仿真与验证工具 (9)4.2.1 仿真工具 (9)4.2.2 验证工具 (9)4.3 版图设计工具 (9)4.3.1 版图设计流程 (9)4.3.2 版图设计工具 (10)第5章集成电路设计中的电路分析 (10)5.1 电路分析方法 (10)5.1.1 等效电路法 (10)5.1.2 节点分析法 (10)5.1.3 回路分析法 (10)5.1.4 频域分析法 (10)5.2 瞬态分析与稳态分析 (11)5.2.1 瞬态分析 (11)5.2.2 稳态分析 (11)5.3 频率特性分析 (11)5.3.1幅频特性分析 (11)5.3.2 相频特性分析 (11)5.3.3 带宽分析 (11)第6章集成电路设计中的可靠性分析 (11)6.1 可靠性指标与评估方法 (11)6.1.1 可靠性指标 (11)6.1.2 评估方法 (12)6.2 热分析与热设计 (12)6.2.1 热分析 (12)6.2.2 热设计 (12)6.3 抗干扰与电磁兼容性设计 (12)6.3.1 抗干扰设计 (12)6.3.2 电磁兼容性设计 (12)第7章集成电路设计中的功率管理 (13)7.1 电源完整性分析 (13)7.1.1 电源网络建模 (13)7.1.2 电源噪声分析 (13)7.1.3 电源完整性仿真与优化 (13)7.2 电压调节与电源设计 (13)7.2.1 电压调节技术 (13)7.2.2 电源设计方法 (13)7.2.3 电源管理集成电路(PMIC)的应用 (13)7.3 功耗优化与低功耗设计 (13)7.3.1 功耗优化策略 (13)7.3.2 低功耗设计技术 (13)7.3.3 低功耗设计方法的应用 (13)第8章集成电路封装与测试 (14)8.1 封装技术概述 (14)8.1.1 封装形式的分类 (14)8.1.2 封装技术的发展趋势 (14)8.2 封装工艺与材料 (14)8.2.1 封装工艺 (14)8.2.2 封装材料 (14)8.3 测试方法与测试技术 (15)8.3.1 测试方法 (15)8.3.2 测试技术 (15)第9章集成电路应用案例 (15)9.1 微处理器设计 (15)9.1.1 案例概述 (15)9.1.2 设计原理 (15)9.1.3 设计实现 (16)9.2 存储器设计 (16)9.2.1 案例概述 (16)9.2.2 设计原理 (16)9.2.3 设计实现 (16)9.3 通信芯片设计 (17)9.3.1 案例概述 (17)9.3.2 设计原理 (17)9.3.3 设计实现 (17)第10章集成电路产业发展与展望 (17)10.1 产业现状与发展趋势 (17)10.1.1 全球集成电路产业现状 (17)10.1.2 我国集成电路产业现状 (18)10.1.3 集成电路产业发展趋势 (18)10.2 技术创新与市场应用 (18)10.2.1 技术创新 (18)10.2.2 市场应用 (18)10.3 我国集成电路产业发展策略与建议 (18)10.3.1 政策支持与引导 (18)10.3.2 技术创新与人才培养 (18)10.3.3 产业链协同发展 (18)10.3.4 国际合作与竞争 (18)10.3.5 市场拓展与规范 (19)第1章集成电路设计概述1.1 背景与意义集成电路(Integrated Circuit,IC)作为现代电子信息行业的核心组成部分,其技术的不断创新与发展,推动了电子设备的微型化、智能化和高效化。

soc设计方法学

soc设计方法学SOC设计方法学是指系统级芯片(System-on-Chip,SOC)的设计方法和技术。

SOC是将多种功能模块集成在一个芯片上的设计理念,可以实现复杂功能的集成和高性能的应用。

SOC设计方法学是指在SOC设计过程中所采用的一系列规范和方法,以确保设计的正确性、可靠性和高效性。

SOC设计方法学强调系统级设计。

在SOC设计中,设计师需要从整体上考虑系统的需求和功能,确定各个功能模块的划分和接口定义。

这要求设计师具备全面的系统级视野和分析能力,能够将系统需求转化为硬件设计的具体实现。

SOC设计方法学注重模块化设计。

在SOC设计中,各个功能模块可以独立设计和验证,然后通过标准接口进行连接。

这种模块化设计的好处是可以提高设计的复用性和可维护性,减少设计的风险和工作量。

SOC设计方法学还强调设计的可靠性和可测试性。

在SOC设计中,设计师需要考虑到芯片的制造和测试过程,确保设计的可靠性和可测试性。

这包括对设计进行可靠性分析和故障注入等技术手段,以及设计测试模式和测试方法等。

SOC设计方法学还注重功耗和性能的平衡。

在SOC设计中,功耗和性能是两个重要的指标。

设计师需要在满足性能需求的同时,尽量减少功耗,以提高芯片的使用时间和效率。

这需要设计师熟悉功耗分析和优化的方法和技术,对设计进行功耗估计和优化。

SOC设计方法学还强调验证和验证方法的重要性。

在SOC设计中,验证是一个重要的环节,用于验证设计的正确性和功能的完整性。

验证方法可以包括仿真、验证台和硬件验证等手段,以确保设计的正确性和稳定性。

SOC设计方法学还强调设计工具和流程的规范化和自动化。

设计工具和流程的规范化和自动化可以提高设计的效率和质量,减少设计的错误和风险。

这包括使用标准化的设计语言和工具,以及建立完善的设计规范和流程。

SOC设计方法学是一种系统级芯片设计的方法和技术,它强调系统级设计、模块化设计、可靠性和可测试性、功耗和性能平衡、验证和验证方法、设计工具和流程的规范化和自动化。

SoC设计与EDA工具第3章-SoC设计与EDA工具(1)

版图电路图同一性比较(LVS,Layout Versus Schematic)

用于比较版图和原理图在晶体管级的连接是否正确。

ECO步骤之后需要进行 逻辑等效性检查

P&R

Phy. V.

ECO

Equivalence Checking

静态时序分析(Static Timing Analysis)

静态时序分析工具通过计算路径上延迟的总和,并比较相对于预定义时钟的延迟, 来检查是否满足时序要求。它仅关注时序间的相对关系而不是评估逻辑功能。 不需要测试激励,检查所有路径的时序。 常用工具,如Synopsys公司的Primetime。

快速搭建虚拟原型机

电子系统级(ESL)设计

Electronic System Level(ESL)设计指系统级的设计方法,是从算 法建模演变而来,已经演变为嵌入式系统软硬件设计、验证、调试的 一种补充方法学。

ESL设计以抽象方式来描述SoC硬件系统,给软硬件工程师提供一 个虚拟的硬件原型平台,用以进行硬件系统结构的探测和软件程序的 开发。

设计约束

综合工具按照什么样的原则来综合电路,该电路所要达到的指标是什么。

主要包括时序、面积、功耗、可测性等。

逻辑综合的流程

工艺无关

工艺相关

逻辑综合的举例

RTL描述:

module magnitude_comparator(A, B, clk, rst_b, A_gt_B, A_lt_B, A_eq_B);

BIST的基本结构

边界扫描测试

边界扫描的原理是在核心逻辑电路的I/O都增加一个寄存器,通 过将这些I/O上的寄存器连接起来,可以将数据串行输入被测单 元,并且从相应端口串行读出。也可以并行输入,并行输出。

SoCDesign

¥ ¤ ¤ ¡ £¢ ¡

Through TE7720 Directly to FPGA

¡ ¡

¥ ¤ ¤ ¡ £¢ ¡

¡

Suzaku MicorBlaze Memory MAP

Start Address 0x0000 0000 0x0000 1000 0x8000 0000 0x8100 0000 0xFF00 0000 0xFF80 0000 0xFFE0 0000 0xFFF0 0000 0xFFFF 1000 0xFFFF 1100 0xFFFF 2000 0xFFFF 2100 0xFFFF 3000 0xFFFF 3100 0xFFFF A000 End Address 0x0000 1FFF 0x7FFF FFFF 0x80FF FFFF 0xFEFF FFFF 0xFF7F FFFF 0xFFCF FFFF 0xFFEF FFFF 0xFFFF 0FFF 0xFFFF 10FF 0xFFFF 1FFF 0xFFFF 20FF 0xFFFF 2FFF 0xFFFF 30FF 0xFFFF 9FFF 0xFFFF A0FF Peripheral BRAM Reserved OPB-SDRAM Controller Free OPB-EMC Free OPB-EMC Free OPB-Timer Free OPB-UART Lite Free OPB-Interrupt Controller Free OPB-GPIO Boot Mode Jumper LED Software Reset RS232C LAN Controller FLASH Memory 4MByte SDRAM 16MByte Device

0xFFFF A100

0xFFFF FFFF

SoC设计与EDA工具第2章SoC设计流程(1)

集成了由FPGA厂商提供的预先设计好、经过严格测试过的处理器等 IP软核或硬核。

基于FPGA的设计流程

电路功能设计 设计输入 (HDL) 综合

实现与布局布线

器件编程

SoC设计

方法与实现

SoC设计方法与实现

第பைடு நூலகம்章

SoC设计

流程(1)

SoC设计特点及软硬件协同设 计

内容大纲

SoC设计的特点

软硬件协同设计

基于标准单元的SoC芯 片设计流程

SoPC设计流程

内容大纲

SoC设计的特点 软硬件协同设计

SoC设计特点

SoC设计与传统的ASIC设计最大的不同在于以下两方面:

在完成布局布线后,需要对整个版图的布局进行动态功耗分析和静态功耗分 析。

除了对版图进行功耗分析以外,还应通过仿真工具快速计算动态功耗,找出 主要的功耗模块或单元。

基于标准单元的SoC芯片设计流程

单元布局和优化(Placement & Optimization)

单元布局和优化主要定义每个标准单元的摆放位置并根据摆放的位 置进行优化。

静态时序分析(STA,Static Timing Analysis)

通过对提取电路中所有路径上的延迟等信息的分析,计算出信号 在时序路径上的延迟,检查是否满足要求。

基于标准单元的SoC芯片设计流程

形式验证(Formal Verification)

形式验证也是一种静态验证方法。 在整个设计流程中会多次引入形式验证用于比较RTL代码之间、门级网表 与RTL代码之间,以及门级网表之间在修改之前与修改之后功能的一致性。

SOC软件设计流程和方法

SOC软件设计流程和方法SOC(System-on-a-Chip)软件设计流程和方法指的是在一个芯片上集成多种功能模块的软件开发流程和方法。

本文将详细介绍SOC软件设计流程和方法,并探讨其优势和挑战。

一、设计流程1.确定需求:明确芯片上集成的功能和性能要求。

这需要与系统设计人员紧密合作,以确保软件设计与硬件设计相互匹配。

2.系统划分:将整个功能划分为多个模块,并确定它们之间的通信方式和接口标准。

3. 开发模块:选择适当的编程语言和开发工具(如C/C++、Python 等),分别开发不同功能模块的软件。

4.软件集成:将所有的软件模块集成到一个整体中,并进行功能和性能测试。

5.调试和优化:通过对整体系统的调试和优化,确保系统的稳定性和高效性能。

6.验证和认证:对整个系统进行验证和认证,以确保符合规定的标准和规范。

二、设计方法1.模块化设计:将整个系统划分为多个模块,每个模块独立开发、调试和测试,降低了系统的复杂性。

2.面向对象设计:使用面向对象的设计方法,将系统中的功能和数据进行封装,提高了系统的可维护性和扩展性。

3.异步通信:由于系统上存在多个功能模块,采用异步通信方式可以提高系统的并发性能和响应能力。

4.软硬件协同设计:与硬件设计团队密切合作,通过软硬件协同设计方法,提高系统的集成程度和性能效率。

三、优势1.简化系统设计:SOC软件设计将多个功能模块集成到一个芯片上,简化了系统设计和开发流程。

2.提高系统性能:通过整合多个功能模块,SOC软件设计可以提高系统的并发能力和运行效率。

3.降低功耗:SOC软件设计可以优化系统的功耗管理和资源利用,提高系统的能效比。

4.提高可维护性:SOC软件设计使用模块化和面向对象的设计方法,提高了系统的可维护性和代码重用性。

四、挑战1.复杂性管理:SOC软件设计需要处理多个功能模块之间的复杂关系,对开发人员的能力和经验要求较高。

2.软硬件协同:软硬件协同设计需要密切合作和沟通,对团队协同能力和沟通能力要求较高。

soc验证流程和方法

soc验证流程和方法SOC verification is a critical process in the development of modern integrated circuits, helping to ensure the functionality, performance, and reliability of complex System-on-Chip designs. SOC验证是现代集成电路发展过程中的关键步骤,有助于确保复杂片上系统设计的功能性,性能和可靠性。

One common method for SOC verification is simulation, where the behavior of the design is tested using software models before the physical chip is manufactured. Simulation allows engineers to identify and correct errors in the design early in the development process, reducing the chances of expensive rework later on. 一种常见的SOC验证方法是模拟,即在制造物理芯片之前,使用软件模型测试设计的行为。

模拟允许工程师在开发过程的早期识别和纠正设计中的错误,减少贵重的重做机会。

Another approach to SOC verification is formal verification, which involves mathematically proving that the design meets its specifications. Formal verification is particularly useful for verifying complex algorithms or properties that are difficult to test withsimulation alone. 另一种SOC验证的方法是形式验证,涉及数学上证明设计符合其规格。

soc设计方法与实现

soc设计方法与实现SOC设计方法与实现。

在当今数字化社会中,系统芯片(SOC)的设计和实现变得越来越重要。

SOC是一种集成了处理器、内存、外设和接口等功能的芯片,它在各种电子设备中发挥着关键作用,如智能手机、平板电脑、智能家居设备等。

本文将介绍SOC设计的一般方法和实现过程。

首先,SOC设计的方法包括需求分析、架构设计、功能验证和物理实现等步骤。

在需求分析阶段,设计团队需要与客户和市场部门合作,了解产品的功能需求和性能指标。

在架构设计阶段,设计团队需要确定系统的整体架构,包括处理器核心、内存子系统、外设接口等。

在功能验证阶段,设计团队需要使用仿真和验证工具,验证系统的功能和性能。

在物理实现阶段,设计团队需要进行逻辑综合、布局布线和时序分析等工作,最终生成芯片的物理设计文件。

其次,SOC的实现过程涉及到多个关键技术,如处理器设计、内存系统设计、外设接口设计等。

在处理器设计方面,设计团队需要选择合适的处理器核心,并进行指令集架构设计、流水线设计和性能优化。

在内存系统设计方面,设计团队需要选择合适的存储器类型,并进行存储器控制器设计和存储器接口设计。

在外设接口设计方面,设计团队需要与外设厂商合作,设计各种接口标准和接口电路。

此外,还需要考虑功耗管理、故障处理、安全性等方面的设计。

最后,SOC设计和实现过程中需要考虑多种约束条件,如性能、功耗、面积、成本和时间等。

设计团队需要在这些约束条件下进行权衡和优化,以满足产品的要求。

同时,设计团队还需要与制造厂商合作,进行芯片制造和测试,最终将芯片投入量产。

综上所述,SOC设计方法和实现过程是一个复杂而关键的工程,它涉及到多个方面的技术和约束条件。

设计团队需要具备丰富的经验和专业的知识,才能完成这一重要任务。

随着数字化社会的不断发展,SOC设计和实现将继续发挥着重要作用,推动各种电子设备的创新和发展。

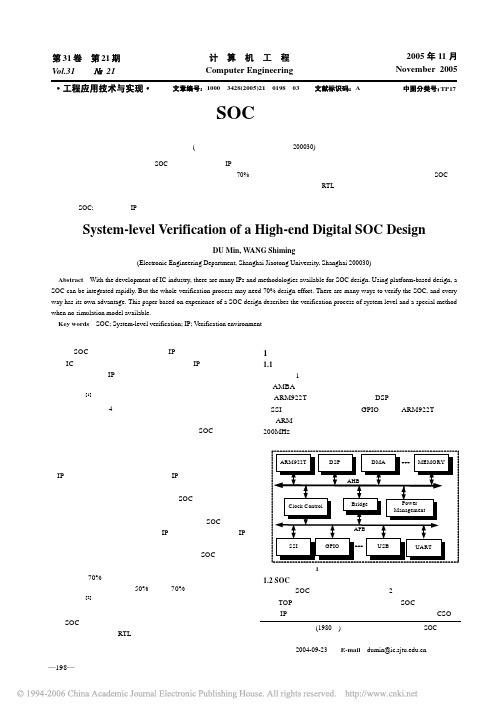

一款高端数字SOC设计的系统级验证

—198— 一款高端数字SOC 设计的系统级验证杜 敏, 王世明(上海交通大学电子工程系,上海 200030)摘 要:集成电路行业的发展,为SOC 设计积累了丰富的IP 库和设计方法。

采用系统设计常用的基于平台的方法,可以快速完成系统的集成。

但要完成对整个系统的验证,可能要占到整个设计周期70%以上的时间。

而验证的方法是具有多样性的。

该文以一款高端SOC 的设计经历,简单描述了系统级验证过程,并以同步串联接口模块为例详细介绍了在系统级对RTL 和门级网表的验证,以及验证所采用的特殊方法。

关键词:SOC; 系统验证;IP ;验证环境System-level Verification of a High-end Digital SOC DesignDU Min, WANG Shiming(Electronic Engineering Department, Shanghai Jiaotong University, Shanghai 200030)【Abstract 】With the development of IC industry, there are many IPs and methodologies available for SOC design. Using platform-based design, a SOC can be integrated rapidly. But the whole verification process may need 70% design effort. There are many ways to verify the SOC, and every way has its own advantage. This paper based on experience of a SOC design describes the verification process of system level and a special method when no simulation model available.【Key words 】SOC; System-level verification; IP; Verification environment计 算 机 工 程Computer Engineering 第31卷 第21期Vol.31 № 21 2005年11月November 2005·工程应用技术与实现·文章编号:1000—3428(2005)21—0198—03文献标识码:A中图分类号:TP17在SOC 的设计中,主要利用了IP 复用技术。

系统设计(SOC)入门

系统设计(系统设计(SOC 10.1系统数字结构的层次结构设计10.1.1 芯片的划分系统集成芯片(系统集成芯片(SOC 芯片系统的划分是SoC设计的第一步复杂大系统划分为若干小系统降低难度、利于并行工作、缩短开发周期34法,这对系统结构比较清楚的条件下才可以实现算法的选择决定了系统的的信息。

8255引脚图8 82558255内部结构框图内部结构框图98255的工作方式控制字118255的位操作控制字128255的C口位地址133.3. 芯片划分zzzzzzzzzz8255程序设计158255程序设计(续)16程序设计(续)1710.1.2 系统间互连的表示子系统之间或元件之间的互连关系实体通过端口语句,描述实体与外部系统的互连关系。

结构体规定了实体的功能,结构体内,通常采用进程和元件例化描述同一系统内的子系统。

2110.2系统集成芯片(系统集成芯片(SOC 10.2.110.2.1概念••1. 3.•••••••••••••••••Traditional design flowHWDesigned by independentgroups of experts••••••••1. 2. 3. 4. 5. 6.1.2.3.4.5.面临的问题Break the wall today!33••••软硬件协同设计流程35软硬件协同设计环境36典型的co-design 流程:37•••Software 程序(polling, interrupt handlers, ...)••••••••••••Company Name CoWareMentor Graphics Synopsys •••••大学:--POLIS: U.C.Berkeley--PTOLEMY: U.C.Berkeley--VULCAN: Stanford U.Verilog (Hardware C)to--CHINOOK:U. ofWashington (VHDL)--COSYMA: U. ofBraunschweig (C*)•••••••••••••••SystemC是由一些C++的类库组成54••••System C#include “systemc.h”SC_MODULE(dff) {sc_in<bool>sc_in<bool>sc_out<bool>void doit();void doit(); // Member functionSC_CTOR(dff) {to}};void dff::doit() { //Process bodydout = din;}11.111.1 引言ASIC(Application Specific Integrated全定制半定制可编程ASIC设计流程优点•••缺点•••••••••••••••••••••Channeled Gate Array Channelless Gate Array门海阵列Structured Gate Array标准单元设计••••标准单元设计的版图布置•••标准单元构成的行块•••标准单元的掩膜版图标准单元设计例子(1)1.0um 2层金属标准单元布线图标准单元设计例子(2)0.18um,6层金属标准单元布线图门阵列设计和标准单元设计比较••设计检验••设计规则检查(•••电学规则检查•••-版图与电路图一致性检查(LVS)••••••设计及生产的一些图片(1)设计及生产的一些图片(2)设计及生产的一些图片(3)5-1 介绍5-2 介绍国内和国外芯片设计公司(各。

一款深亚微米射频SoC芯片的后端设计与实现

一款深亚微米射频SoC芯片的后端设计与实现张志鹏;张超;刘铁锋【摘要】随着集成电路的发展,片上系统芯片(SoC)技术广泛应用于多种领域中,越来越多的射频、模拟、存储器模块集成到一块芯片中.SoC芯片后端设计面临尺寸特征小,芯片规模大,物理设计复杂程度高等问题.良好的芯片版图设计是集成电路实现和成功的基础之一.介绍了基于台积电0.18μmULL低功耗工艺设计的射频SoC 电路结构,在此基础上,详细说明了后端版图设计流程与布局规划,重点介绍了时钟模块设计,多时钟电路及复杂时序关系设计的后端布局处理,供电设计以及布线优化方法和技巧,对各类相关芯片的后端设计具有良好的借鉴意义.%With the development of integrated circuit, the system on chip (SoC) technology is widely used in many applications, as more and more RF modules, analog modules and memory modules are embedded into one chip. The SoC back-end design confronts more challenges such as smaller feature size, larger chip area and more complex physical design. A remarkable layout design is one of the elements of the integrated circuit implemention and success. RF SoC circuit structure based on TSMC 0.18μmULL low power consumption process design is introduced,and on this basis, back-end layout design process and layout planning are explained in detail,mainly focusing on the clock generation module design,back-end processing method of multi-clock circuit and complex timing relationshipdesign,power supply plan and layout optimization methods and techniques,that supplies a good reference to many relevant kinds of beck-end chip design.【期刊名称】《微处理机》【年(卷),期】2017(038)006【总页数】6页(P1-6)【关键词】片上系统芯片;后端布局;多时钟设计;时钟生成;后端流程;供电设计【作者】张志鹏;张超;刘铁锋【作者单位】中国科学院沈阳自动化研究所网络化控制系统重点实验室,沈阳110016;中国科学院沈阳自动化研究所网络化控制系统重点实验室,沈阳110016;中国科学院沈阳自动化研究所网络化控制系统重点实验室,沈阳110016【正文语种】中文【中图分类】TP277随着集成电路的发展,片上系统芯片(SoC)技术在超大规模集成电路设计的开发与市场角度已经非常成熟,广泛应用于工业控制、智能手机、平板电脑等各类芯片中。

Libero_SoC集成开发环境使用教程

© 2013 Microsemi Corporation.

Power Matters

6

Libero SoC 概述3

要生成供别的模块调用的子模块时候选择, 默认不选。

选择器件型号及封装等

如果不使用MSS,不需要选择此选项,此 选项是用于快速建立MSS实用的。单纯的 FPGA设计不要选。

© 2013 Microsemi Corporation.

© 2013 Microsemi Corporation.

Power Matters

27

Creat constraint: Timing(sdc)

时序约束反映了设计的性能目标.软件根据这个时序约束,指导

时序驱动的优化工具进行综合优化. 可以对全局或某个特定的路径进行时序约束. 可以设置的约束有:

Libero® SoC 集成开发环境使用教程 —— FPGA篇

Theo SoC Group

主要内容

Libero SoC 概览

Libero SoC 设计流程

Libero SoC 工程样例 Libero SoC License 管理

© 2013 Microsemi Corporation.

• • • • • •

指定要求的最小时钟周期. 设置输入输出端口时序信息. 定义指定路径的最大延迟. False路径分析. 多周期路径分析. 指定端口的外部附载.

© 2013 Microsemi Corporation.

Power Matters

28

Implement Design : Synthesize

© 2013 Microsemi Corporation.

Power Matters

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在SOC设计中,软件、硬件部分都需要设计规 范。设计规范必须全面的描述设计与环境之间的接 口,它们包括: 硬件

功能 与其它硬件的外部接口(如管脚、总线、如何使用等) 与软件接口(寄存器定义) 性能指标 物理设计问题,如面积、功耗等

软件

功能 时序 性能指标 与硬件接口 软件结构,内核

传统上,规范的书写使用自然语言,如英 语。但是,随之产生的问题很多,如表达不 清晰、不完全、包含有错误等等。许多公司 认识到了这个问题。所以,他们在系统设计 中使用部分或全部的可执行的规范描述语 言。

大多数项目开发中,软件的设计总是紧跟着 硬件设后就开始了的。但是,由于没有硬件 平台供软件进行调试,软件开发团队只有等 待。因此,软、硬件的开发总是顺序进行 的。

这种设计流程,在设计规模不超过100K门,制造 工艺大于0.5um时,还能够正常运行。这时通常 完成的设计能够保证一遍就正确。但是这种流程也 存在问题,因为项目在从一个团队交到另一个团队 时,很少有绝对不需要返工的。例如,因为算法根 本不可实现,RTL设计团队不得不将设计返回给系 统设计团队,以求重新设计;或者,因为设计不能 满足时序要求,RTL编码必须重新修改,综合团队 又必须将设计返回给RTL团队。

结论

软件、硬件开发团队一致发现,迭代是一个开发过程不可避免 的部分。在计划中考虑迭代的开销,具有重大意义。它有利于 找到一个方法,将设计时间缩短到最小。这通常意味着要将迭 代次数降低到最少,特别是要减少主循环的迭代次数。在一个 芯片设计布局布线完成后再返回到规范制定这一级,将付出昂 贵的费用。因此,我们希望迭代次数尽可能少,迭代返回尽可 能的提前。 我们宁可迭代发生的更紧密、更局部化。例如在编码、验证、 综合小模块的时候。这们做迭代就会更快、更有效率。我们可 以通过计划和规范我们所要的模块,使它们在创建时满足整个 设计的需要。如果有一个包含有众多已经设计好的核的库,显 然对设计是有帮助的。参数化的模块允许我们在功能、面积和 性能方面做出最佳的选择。

下面,我们将以流程图的方式描述设计过程。因为它是一种方 便的、用于表示设计步骤的方法。虽然迭代环路通常不能明显 的出对流图进行简化。但是,我们也不希望用瀑布式的方式, 因为它在上一阶段未完成之前,不允许下一阶段开始。通常在 规范制定完成之前,有必要对实现的细节进行核识。而不是在 上一阶段完成之后,才在迭代中再考虑全部细节。 我们的警告:迭代过程虽然不可避免,但不应该成为不认真制 定设计规范的借口。花费时间在详细、认真的做好设计规划 上,是一种减少迭代次数、减少迭代周期的最好的方法。

随着上市时间的压力增大,设计团队也在不断的寻找新方法, 从而谋求加速设计过程。功能不断提高的EDA工具,例如综合 和模拟工具,已经取得了重大进展。而对可重用核设计库的开 发,又将有助于极大的加速设计进程。 但是,像瀑布式的系统开发模式、自顶向下开发方式在理想状 态下也是一样的。自顶向下方法假定最底层的模块已经设计好 了。如果某一个模块不适合本次设计,则设计需要重新再反复 一次。正因为如此,事实上,设计团队通常选择混合使用自顶 向下和自底向上的方法。在构建关键的底层模块时,也同时进 行系统简化和模块设计规范的制定。在这一设计过程中,可重 用核库可以提供一些已经验证过的核,以满足部分的设计需 要。

SOC设计方法

第三讲 SOC设计过程 SOC design process

SOC设计范例 系统设计流程 设计规范 系统级设计过程

1 典型的SOC

微处理器和Memory 子系统 提供数据路径的片上总 线(高速和低速部分) 外部Memory控制器 通讯控制器 视频解码器 定时和中断控制器 通用I/O(输入/输 出)接口 UART(通用异步收发 器)接口

范例只是SOC设计最小化的一个版本。能够让我们集 中讲解如何使用可重用核进行设计,如何解决SOC设 计中遇到的问题。

2 系统设计流程

为了迎接SOC设计带来的挑战,芯片设计 师正在把他们的设计方法,转移到两种主要 设计方法上:

从瀑布模式转移到螺旋模式上 从自顶向下的方法转变为自顶向下和自底向上 混合的方法上。

瀑布模式和螺旋模式

传统的ASIC开发模式,通 常叫做瀑布模式。 项目开发是从一个阶段到另 一个阶段按步骤推进的,后 一个阶段完成后,不会再返 到前一个阶段去。 设计项目通常是由一个团队 移交到下一个团队,团队之 间没有交流。

这种方法始于专用ASIC芯片的开发时代。

对于一个含有复杂算法的ASIC芯片的设计,算法部分 先由图像处理专家完成,再交给设计团队去设计RTL编 码,最后形成SOC芯片。 功能验证后,由设计团队或某个独立的团队将设计综合 成一个门级网表。 时序验证部分验证设计是否满足时序要求。一但设计满 足了时序要求,相应的网表就会交到物理设计的团队手 上,进行布局、布线设计。最终芯片制成后进行测试。 原型芯片再送到软件开发团队那里,进行软件的调试和 开发。

边设计、边修改的方法

Sun公司的工程师在开发UltraSPARC 处 理器时,采用了一种叫做“边设计、边修改” 的方法。在这个项目中,一个团队完成了整 个项目的从构架定义到布局布线的全过程。 该项目的工程师必须掌握如何使用布局、布 线工具。然而,在过去,他们只需要依靠另 外一个专门做物理设计的团队就行了。在经 过这整个流程后,设计团队已经能够将最终 设计中的面积、功耗、性能等因素产生的影 响,在结构设计中就给于充分的考虑。

和综合的过 程并行。 规划和布局、布 线包含在综合过 程中。 只有在以前设计 的软、硬核工业 不可用时,才开 发新模块。 整个过程中有多 次迭代。

在许多大型项目中,工程师同时开发顶层系 统级规范、关键子模块算法、系统级验证方 案和时序分配方案。整个芯片设计的软件、 硬件同时进行功能、时序、物理设计和验 证。

UltraSPARC开发团队尽可能快的完成了 第一次的从结构到布局、布线流程,然后又 经过多次全过程的迭代。他们通过设计一个 组织和一个开发计划,使用一个开发小组, 通过多次的全过程迭代完成一个设计。这样 的作法,可以使他们看到自己的错误,然后 更正它。在芯片最终交付生产之前,这种过 程需要迭代多次。开发团队把这种优化、迭 代的过程叫做“边设计,边修改”。

3 规范的制定

设计过程的第一部分通常包括开发、验证、 细化一整套的设计规范,直至详细到了可以 开始RTL编码。快速完成一整套清晰、全 面、一致的设计规范是非常困难的问题。在 一个成功的设计中,规范设计阶段是最关 键、最具挑战性、最耗时的阶段。

项目进展中如果你知道什么是你所想实现 的,其中隐藏的错误就很容易被发现和消 除。如果你不是很清楚你所想实现的,那么 设计中的错误就很难发现,也许要到设计后 期或者直到生产时才能发现。

真正的SOC设计,更为复杂。

在真正的设计中可能包括几套的IP接口和多种数据传输方 法。 许多SOC设计中集成了多个处理器,或者是将处理器与 DSP处理器进行集成。 它们采用的Memory控制结构也非常复杂,有用多级 Cache和共享Memory的,还有在视频解码器中用特殊的 数据结构,来解决数据传输的模块。

设计规范的类型

当前,有两种主要技术有助于描述软件、硬 件规范,使软件、硬件更加具有鲁棒性和可 用性:形式化规范和可执行规范。

形式化规范

在形式化规范中,设计所需的特征被以一种与任何 实现都不相关的相形定义下来。一但某个设计是采 用形式化规范,那么就可以利用形式化方法,如利 用属性检查来证实某个实现方法是否满足规范的要 求。已经有许多形式化规范描述语言出现,其中包 括为VHDL开发的VSPEC。这些语言都提供了一 种机制,不仅能够描述行为功能,还能够描述时 序、功耗和面积需求。虽然直到今天,形式化规范 还没有被广泛的应用于商业设计中。但是,在将来 的很长一段时间里,它仍然是一个重要的研究方 向。

总而言之,在项目的早期制定完整的规范要 比项目完成后再书写规范,花费上要少的 多。例如,对接口定义进行特别的描述可能 揭示出接口中的错误或不一致之外。换句话 说,在项目完成后再整理文档,对开发人员 没有实际意义,也延误了项目的进度。

规范中的要求

Specification,规范 –制定设计规范是设计过程的第一部分 –制定规范是设计中最关键的阶段 功能规范 –Functional Specifications –描述从用户角度看到的系统或模块的接口 –引脚、总线、寄存器、数据操作 结构规范 –Architectural Specifications –描述各组件之间的接口 –以及,接口上的事务如何协调各模块的功能,以实现系统级行为

对于一个大型、深亚微米的设计,瀑布式设 计方法根本就无法工作。大型系统通常包含 有相当大的软件部分,要求开发过程中, 软、硬同步开发,以保证系统功能的正确 性。物理设计中的问题,也必须在设计的初 期给予足够的考虑,以便最终的设计能够满 足性能指标的要求。

随着复杂度增加、几何尺寸缩小、上市时间 压力增加,芯片设计师也正在转变设计流 程,以应对大规模SOC芯片设计的需要。 许多设计团队已经从旧的瀑布式设计方法转 变到螺旋式设计方法上。在螺旋式设计模式 中,设计团队是在多个层面上同时开始设计 的,增强了设计的竞争力。

哪些功能由软件中完成,哪些功能由硬件完成? 用什么样的处理器,用多少个? 选用什么样的总线结构,以达到系统要求的性能? 选用什么样的Memory 构架,从而在功耗、面积和速 度之间达到平衡?

该设计某种程度上讲是作者人为构造的。但是,它包含 着一个SOC设计完整的结构和必然要遇到的问题。

微处理器可能采用地是从8位的8051到64位的RISC处理器 中的任意一种。 存贮子系统采用地可能是单级或多级,可能包括SRAM或 DRAM。 外部Memory可能采用地是DRAM、SRAM或Flash形式 的。 I/O控制器可能包括PCI、PCI-X,Ethernet、USB、 IEEE1394、A/D、D/A或光电转换器等。 视频解码器可能采用MPEG,ASF或AVI标准。 GPIO接口可能使用LED或采样数据线。