数字系统设计2006~2007A

verilog数字系统设计教程习题答案

verilog 数字系统设计教程习题答案第二章HDL 既是一种行为描述语言,也是一种结构描述语言。

如果按照一定的规则和风格编写代码,就可以将功能行为模块通过工具自动转化为门级互联的结构模块。

这意味着利用Verilog 语言所提供的功能,就可以构造一个模块间的清晰结构来描述复杂的大型设计,并对所需的逻辑电路进行严格的设计。

2.模块的基本结构由关键词module和endmodule构成。

3.一个复杂电路系统的完整Verilog HDL 模型是由若干个VerilogHDL模块构成的,每一个模块又可以由若干个子模块构成。

其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块交互的现存电路或激励信号源。

利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计,并对所作设计的逻辑电路进行严格的验证。

HDL和VHDL乍为描述硬件电路设计的语言,其共同的特点在于:能形式化地抽象表示电路的结构和行为、支持逻辑设计中层次与领域的描述、可借用高级语言的精巧结构来简化电路的描述、具有电路仿真与验证机制以保证设计的正确性、支持电路描述由高层到低层的综合转换、硬件描述与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去)、便于文档管理、易于理解和设计重用。

5.不是6.将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

7.综合工具可以把HDL变成门级网表。

这方面Synopsys工具占有较大的优势,它的Design Compile 是作为一个综合的工业标准,它还有另外一个产品叫Behavior Compiler ,可以提供更高级的综合。

另外最近美国又出了一个软件叫Ambit ,据说比Synopsys 的软件更有效,可以综合50万门的电路,速度更快。

今年初Ambit 被Cadence 公司收购,为此Cade nee放弃了它原来的综合软件Syn ergy。

数字系统设计与veriloghdl课后答案

数字系统设计与veriloghdl课后答案【篇一:数字逻辑与数字系统设计习题参考答案】>第1章习题解答1.3 (1)86(2)219(3)106.25(4)0.6875 (4)0.1011.4 (1)101111(2)1001000(3)100001l.111.5 (1)(117)10=(165)8=(1110101)2=(75)16(2)(3452)10=(6574)8=(110101111100)2=(d7c)16(3)(23768.6875)10=(56330.54)8=(101110011011000.1011)2=(5cd 8.b)16 (4)(0.625)10=(0.5)8=(0.101)2=(0.a)16 1.6(1)(117)8=(1001111)2=(79)10(2)(7456)8=(111100101110)2=(3886)10(3)(23765.64)8=(10 0111 1111 0101.1101)2=(10229.8125)10(4)(0.746)8=(0.11111)2=(0.96875)10 1.7 (1)(9a)16=(10011010)2=(154)10(2) (3cf6)16=(11110011110110)2=(15606)10(3) (7ffe.6)16=(111111*********.011)2=(32766.375)10 (4)(0.c4)16=(0.110001)2=(0.765625)10 1-8(1)(125)10=(000100100101)8421bcd(2)(7342)10=(0111001101000010)8421bcd(3)(2018.49)10=(0010000000011000.01001001)8421bcd(4)(0.785)10=(0.011110000101)8421bcd1.9(1)(106)10=(1101010)2 原码=反码=补码=01101010 (2)(-98)10=(-1100010)2原码=11100010反码=10011101 补码=11100011(3)(-123)10=(-1111011)2 原码=11111011反码=10000101 补码=11111011(4)(-0.8125)10=(-0.1101)2 原码=1.1101000反码=1.0010111 补码=1.00110001.10(1)(104)10=(1101000)2 [1101000]补=01101000(-97)10=(-1100001)2 [-1100001]补=1001111101101000 + 10011111 0000011110000011 + 01001111 11010010[104-97]补=01101000+10011111=00000111, 104-97=(00000111)2=7 (2) (-125)10=(-1111101)2(79)10=(01001111)2[-1111101]补=10000011 [01001111]补=0100111101111000 [-125+79]补=10000011+01001111=11010010,-125+79=(-0101110)2=-46 (3) (120)10=(1111000)2[01111000]补=01111000(-67)10=(-1000011)2[-1000011]补=10111101[120-67]补=10000011+01001111=00110101,-125+79=(00110101)2=53 (4) (-87)10=(-1010111)2[-1010111]补=10101001(12)10=(1100)2[1100]补=00001100[-87+12]补=10101001+00001100=10110101,-125+79=(-1001011)2=-75+ 10111101 0011010110101001+ 00001100 10110101第2章习题解答2.3 解:根据逻辑图可直接写出逻辑表达式:(a) f=ab?bc;(b)f=abbcac解:设3个输入变量分别为a、b、c,输出为f,按题意,其中有奇数个为1,则输出f=1,因此可写出其逻辑表达式为f=abc?abc?abc?abc。

专科《硬件描述语言和数字系统设计》_试卷_答案

专科《硬件描述语言和数字系统设计》一、(共36题,共150分)1. reg类型的数组通常用于描述存储器,reg [15: 0] MEM [0:1023];定义存储器字的位数为(2分)A.1024B.16C.16384D.1040.标准答案:B2. 下列关于同步有限状态机的描述错误的是()(2分)A.状态变化只能发生在同一个时钟跳变沿;B.状态是否变化要根据输入信号,只要输入条件满足,就会立刻转入到下一个状态。

C.在时钟上升沿,根据输入信号的变化,确定电路状态D.利用同步状态机可以设计出极其复杂灵活的数字逻辑电路系统.标准答案:B3. 关于如下描述,正确的说法是( ) (2分)A.这种描述是错误的B.该电路不可综合C.该电路不可综合,但生成的不是纯组合逻辑D.以上说法都不对.标准答案:D4. 下列关于流水线的描述错误的是( ) (2分)A.流水线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插入寄存器,并暂存中间数据的方法;B.设计流水线目的是提高数据吞吐率C.流水线缩短了在一个时钟周期内给的那个信号必须通过的通路长度,从而可以提高时钟频率D.增加流水线长度可以节省更多延迟,流水线越长,首次延迟越大,系统频率就会降低。

.标准答案:D5. 以下关于Top-Down的设计方法不正确的描述是( ) (2分)A.Top-Down的设计方法首先从系统设计入手;B.Top-Down设计中的系统总体仿真与所选工艺有关C.Top-Down的设计方法从顶层进行功能划分和结构设计D.自顶向下的设计方法可以早期发现结构上的错误.标准答案:B6. 在verilog中,下列哪些操作一定是单bit?()(2分)A.==B.^C.>D.&& .标准答案:A,B,C,D7. 下面哪些是verilog的关键字()(2分)A.inputB.assignC.writeD.module.标准答案:A,B,D8. 全球主要的FPGA厂家有()(2分)A.XilinxB.AlteraC.Broadcomttice.标准答案:A,B,D9. 大规模数字逻辑设计原则,正确的说法有()(2分)A.异步设计原则B.组合时序电路分开原则C.面向RTL的原则D.先电路后代码的原则.标准答案:B,C10. 下面有关SRAM,DRAM的叙述,正确的有()(2分)A.DRAM存储单元的结构比SRAM简单B.DRAM比SRAM成本高C.DRAM比SRAM速度快D.DRAM要刷新,SRAM不刷新.标准答案:A,D11. 阻塞赋值与非阻塞赋值的差别及其各自的使用环境。

清华大学微电子系工硕课题介绍

课题介绍微电子与纳电子学系2013级工程硕士双选专用清华大学微电子与纳电子学系2013年12月有招生需求导师名单-------------------------------------------------------白国强(设计室)蔡坚、王谦(器件室)陈虹(设计室)陈炜(器件室)池保勇(设计室)邓宁(器件室)方华军(器件室)付军(集成室)姜汉钧(设计室)李福乐(设计室)李树国(设计室)李翔宇(设计室)李宇根(设计室)李兆麟(信研院)梁仁荣(集成室)刘雷波(CAD室)刘振宇(信研院)麦宋平(深研院)潘立阳(集成室)钱鹤(CAD室)任天令、杨轶(器件室)王敬(集成室)王晓红(器件室)王燕(CAD室)王喆垚(器件室)王志华、王自强(设计室)魏少军(CAD室)乌力吉(设计室)吴华强(工艺平台)伍冬(集成室)伍晓明(工艺平台)谢丹(器件室)谢翔(设计室)许军(集成室)叶佐昌(CAD室)尹首一(CAD室)岳瑞峰(器件室)张春(设计室)张进宇(CAD室)张雷(CAD室)刘泽文(器件室)何虎(设计室)北京朗波芯微技术有限公司课题介绍白国强一、招生老师联系信息E-mail: baigq@电话:62794391(O),136********办公室:主楼9区104二、招生人数:2-3名三、课题介绍课题一:(1)课题名称:面向低资源移动终端应用的新型公钥密码算法的集成电路实现技术研究。

(2)课题来源:国家自然科学基金重点项目“面向低资源移动终端的高效新型公钥密码芯片的理论与关键技术研究”。

(3)课题简介:受移动终端(如手机)硬件资源十分有限的限制,现有公钥密码算法,包括RSA算法和ECC算法很难直接应用于移动终端。

为解决这一问题,近年来多变量公钥密码学受到广泛关注,成为研究热点之一。

本课题研究内容是“面向低资源移动终端的高效新型公钥密码芯片的理论与关键技术研究”项目中的一部分内容,将以集成电路方式设计、实现基于多变量的新型公钥密码芯片。

数字电路与系统设计课后习题答案之欧阳科创编

1.1将下列各式写成按权展开式:(352.6)10=3×102+5×101+2×100+6×10-1(101.101)2=1×22+1×20+1×2-1+1×2-3(54.6)8=5×81+54×80+6×8-1(13A.4F)16=1×162+3×161+10×160+4×16-1+15×16-2 1.2按十进制0~17的次序,列表填写出相应的二进制、八进制、十六进制数。

解:略1.3二进制数00000000~11111111和0000000000~1111111111分别可以代表多少个数?解:分别代表28=256和210=1024个数。

1.4 将下列个数分别转换成十进制数:(1111101000)2,(1750)8,(3E8)16解:(1111101000)2=(1000)10(1750)8=(1000)10(3E8)16=(1000)101.5将下列各数分别转换为二进制数:(210)8,(136)10,(88)16解:结果都为:(10001000)21.6 将下列个数分别转换成八进制数:(111111)2,(63)10,(3F)16解:结果都为(77)81.7 将下列个数分别转换成十六进制数:(11111111)2,(377)8,(255)10解:结果都为(FF)161.8 转换下列各数,要求转换后保持原精度:解:(1.125)10=(1.0010000000)10——小数点后至少取10位(0010 1011 0010)2421BCD=(11111100)2(0110.1010)余3循环BCD码=(1.1110)21.9 用下列代码表示(123)10,(1011.01)2:解:(1)8421BCD码:(123)10=(0001 0010 0011)8421BCD(1011.01)2=(11.25)10=(0001 0001.0010 0101)8421BCD(2)余3 BCD码(123)10=(0100 0101 0110)余3BCD(1011.01)2=(11.25)10=(0100 0100.0101 1000)余3BCD1.10 已知A=(1011010)2,B=(101111)2,C=(1010100)2,D=(110)2(1)按二进制运算规律求A+B,A-B,C×D,C÷D,(2)将A、B、C、D转换成十进制数后,求A+B,A-B,C×D,C÷D,并将结果与(1)进行比较。

数字电子电路系统的设计、测量与调试

可控硅现象(又称门锁现象)是所有CMOS集 成电路在使用中都可能发生的固有特性,CMOS 工艺的A/D转换器也不例外。 其现象是在使用中,A/D转换器芯片电流骤增, 突然发热,时间一长,芯片就会烧坏。但这时只 要切断电源,然后重新打开,又会恢复。这种情 况通常发生在输入信号电平高于电源电压时,其

其原因是由于芯片衬底存在着寄生的横向PNP管和纵 向PNP管形成的可控硅结构。如果输入信号脉冲(如 较大的干扰脉冲)超过了额定值(如VSS-0.5V<VIN < VDD+0.5V),产生较大的输入电流时,就会使寄生 可控硅导通,使VDD与VSS或与地之间形成通路,产生 大的短路电流。为防止这种现象产生可采取以下措施:

1 1

数量级。在图(2)中R1、R2一般取值1K左右,C1、C2 取值100PF~100uF,输出频率为几兆赫至几十兆赫。

由于TTL门电路功耗大于CMOS门,并且最低频 率因受输入阻抗的影响,很难做到几赫,一般不适 宜低频段工作。 3)、用555定时器构成振荡器 用555定时器构成的振荡器可产生几赫至几兆 赫的矩形波信号。T=(R1+R2)Cln2+ R2Cln2 双极性定时器电源电压范围为3~16V,最 大负载电流可达200mA;CMOS定时器电源电 压范围为3~18V,最大负载电流在4mA以下。 频率稳定度最高能达到0.1%。

开始的。针对这些情况,A/D转换器提供了不同的引 脚,只有正确使用,才能保证转换精度。 ①变换量程的双模拟输入引脚和双极性偏置引脚的 正确使用 有的A/D转换器如AD574有两个模拟输入引脚,输 入电压分别为10V和20V,不同量程的输入电压应从不 同引脚输入。有的A/D转换器,如AD574,了双极性 编置控制引脚BOC,当此脚接地时,信号为单极性输 入方式。若将两种组合AD574具有4种输入量程,即 0~+10V,0~+20V,-5V~+5V,-10V~+10V。 ②双参考电压引脚的正确使用 有些A/D转换器,如ADC0809,有两个参考电压引 脚,一个为REF(+),另一个为REF(-),通常情 况下,REF(-)接地,REF(+)接+5V,输入电压范

数字系统

系统的方法得到了越来越广泛的应用。

14

.4.2 数字系统的描述方法

算法状态机图(ASM图)

ASM图(Algorithmic State Machine Chart)是硬件算

法的符号表示方法,可以方便地表示数字系统的时序操

作。ASM图 是一种时钟驱动 的流程图。ASM图不仅可 以用来描述控制器的控制过程(即控制器的状态转换、 转换条件以及控制器的输出等),还指明了在被控制的 数据处理器中应该实现的操作。在这个意义上,ASM图

数字系统

1

.1 数字系统的基本概念

所谓数字系统,系具有存储、 传输、处理数字信息功能的

逻辑系统

数据处理单元 存储部件 输入 部件 输出 部件

逻辑子系统的集合物。

数字系统的设计,涉及机、光、

电、化学、经济学等学科各

类工程技术问题,但从本质

上看,其核心问题仍是逻辑 设计问题。

处理部件

控制单元

数字系统结构框图

长,人工设计数字系统十分困难,必须依靠EDA技术。用EDA技术

设计数字系统的实质是一种自顶向下的分层设计方法。在每一层上, 都有描述、划分、综合和验证 四种类型的工作。

描述是电路与系统设计的输入方法,它可以采用图形输入、硬件

描述语言输入或二者混合使用的方法输入;也可以采用波形图输入法。

整个设计过程只有该部分由设计者完成。 划分、综合和验证 则采用EDA软件平台自动完成,这样

注意:条件输出框不是控制器的一个状态。

19

2. ASM 块

一个 ASM块表示一个时钟周期内的系统状态。每个 ASM 块必定包含一个状态框且只允许包含一个状态框,与此 状态框相连的若干个判断框和条件输出框也属于该 ASM 块.

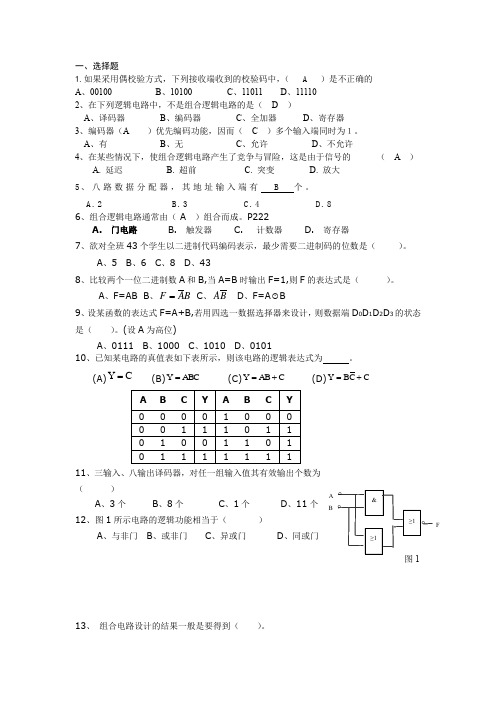

数字电子技术考试卷及答案 (5)

七、(本题12分)画出用74161的异步清零功能构成的80进制计数器的连线图。

八、(本题15分)用D触发器设计一个按自然态序进行计数的同步加法计数器。

要求当控制信号M=0时为5进制,M=1时为7进制(要求有设计过程)。

7《数字电子技术基础》期末考试A卷标准答案及评分标准8910北京航空航天大学2004-2005 学年第二学期期末《数字数字电子技术基础》考试A 卷班级______________学号_________姓名______________成绩_________2007年1月18日班号学号姓名成绩《数字电路》期末考试A卷注意事项:1、答案写在每个题目下面的空白处,如地方不够可写在上页背面对应位置;2、本卷共5页考卷纸,7道大题;((a)74LS85四、逻辑电路和各输入信号波形如图所示,画出各触发器Q 端的波形。

各触发器的初始状态为0。

(本题12分)五、由移位寄存器74LS194和3—8译码器组成的时序电路如图所示,分析该电路。

(1)画出74LS194的状态转换图;(2)说出Z 的输出序列。

(本题13分)CP CP六、已知某同步时序电路的状态转换图如图所示。

(1)作出该电路的状态转换表;(2)若用D触发器实现该电路时写出该电路的激励方程;(3)写出输出方程。

(本题15分)七、电路由74LS161和PROM组成。

(1)分析74LS161的计数长度;(2)写出W、X、Y、Z的函数表达式;(3)在CP作用下。

分析W、X、Y、Z端顺序输出的8421BCD码的状态(W为最高位,Z为最低位),说明电路的功能。

(本题16分)《数字电子技术基础》期末考试A卷标准答案及评分标准一、1、按照波形酌情给分。

北京航空航天大学2005-2006 学年第二学期期末《数字电子技术基础》考试A 卷班级______________学号_________姓名______________成绩_________2006年7月12日班号学号姓名成绩N图712Q Q Y(状态转换、设计过程和步骤对得10分,化简有误扣3-5分)七、MN=00时,是5进制,显示最大数字为4;MN=01时,是6进制。

数字系统设计期中试卷(09级)

A.数据分配器B.数据选择器C.编码器D.译码器

7.下面列出的选项中,()不是消除竞争-冒险的方法。

A.修改逻辑设计B.接入滤波电容C.引入选通脉冲D.进行时序仿真

8.设x是一个STD_LOGIC_VECTOR(7 DOWNTO 0)类型的信号,则信号赋值语句x<=’0’ & x(7 DOWNTO 1)的作用是将x()。

2.一个逻辑函数可有多种表达形式,下面几种形式中,()一定是唯一的。

A.最小项表达式B.最简或与式C.最简与或式

3.8位二进制补码能够表示的十进制有符号数的范围是()

A.0255B.-128+127C.-255+255D.-127+127

4.根据对偶规则可写出F=A+((BC)+B(A+C))的对偶式为FD=()。

6.可以将若干个TTL与非门的输出直接连接在一起,实现线与的功能。()

7.利用逻辑门实现某逻辑函数时,逻辑门的多余输入端可以悬空。()

8.在VHDL程序中,为了能够读取某输出信号的状态,应将它设置为BUFFER模式。()

9.在VHDL语法中,变量赋值是立即生效的,不允许出现附加延时。()

10.一个逻辑门可以有两个扇出系数,分别是输出高电平时和输出低电平时的扇出系数。()

3.(10分)试用一个8选1的数据选择器及反相器设计一个逻辑电路,完成下面的功能(A、B为数据输入端)。画出逻辑电路图,并写出设计过程。

S1S0

F

0 0

AB

0 1

A+B

1 0

A⊙B

1 1

AB

2.含2个逻辑变量的逻辑函数F=AB+AB的值恒等于1。()

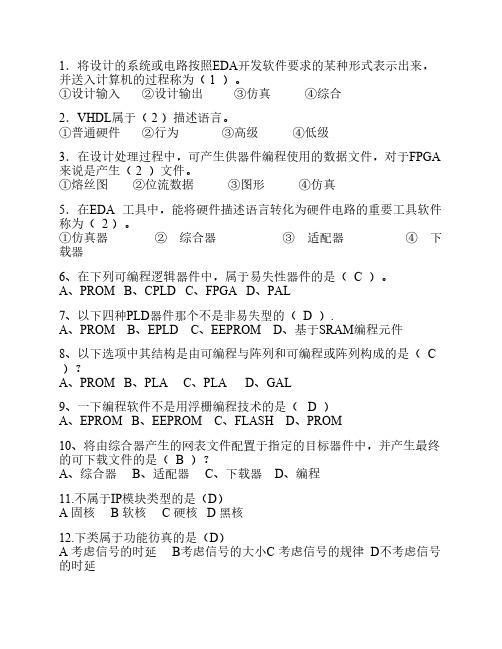

选择题 数字系统设计

1.将设计的系统或电路按照EDA开发软件要求的某种形式表示出来,并送入计算机的过程称为( 1 )。

①设计输入②设计输出③仿真④综合2.VHDL属于( 2 )描述语言。

①普通硬件②行为③高级④低级3.在设计处理过程中,可产生供器件编程使用的数据文件,对于FPGA 来说是产生( 2 )文件。

①熔丝图②位流数据③图形④仿真5.在EDA 工具中,能将硬件描述语言转化为硬件电路的重要工具软件称为( 2 )。

①仿真器 ② 综合器 ③ 适配器 ④ 下载器6、在下列可编程逻辑器件中,属于易失性器件的是( C )。

A、PROMB、CPLDC、FPGAD、PAL7、以下四种PLD器件那个不是非易失型的( D ).A、PROMB、EPLDC、EEPROMD、基于SRAM编程元件8、以下选项中其结构是由可编程与阵列和可编程或阵列构成的是( C )?A、PROMB、PLAC、PLAD、GAL9、一下编程软件不是用浮栅编程技术的是( D )A、EPROMB、EEPROMC、FLASHD、PROM10、将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件的是( B )?A、综合器B、适配器C、下载器D、编程11.不属于IP模块类型的是(D)A 固核B 软核C 硬核D 黑核12.下类属于功能彷真的是(D)A 考虑信号的时延 B考虑信号的大小C 考虑信号的规律 D不考虑信号的时延13.下类不属于简单PLD的是(B)A PLAB PROMC PALD GAL14、EDA技术发展的第二阶段是(B)A、CADB、CAEC、EDAD、PLD15、(B)指的是以版图形式实现的设计模块。

A、软核B、硬核C、固核D、散核16、可编程逻辑阵列是(C)A、PROMB、PALC、PLAD、GAL17、查找表的原理类似于ROM,其物理结构是静态存储器(SRAM),N个输入项的逻辑函数可以由一个(A)位容量的SRAM来实现。

A、2B、2C、2D、2-118、Quartus Ⅱ进行EDA设计开发过程中的综合、适配属于(D)步骤中。

第4-5章数字逻辑与数字系统设计复习题

29、当74LS148的输入端 按顺序输入11011101时,输出 为(C)。

A、101B、010C、001D、110

30、译码器的输入量是(A)。

A、二进制B、八进制C、十进制D、十六进制

31、编码器的输出量是(A)。

A、二进制B、八进制C、十进制D、十六进制

32、组合逻辑电路一般由(A)组合而成

根据上述最简式画出相应逻辑电路图如下:

课后练习题

5.16解:

F1= AB + BC + AC= =m7+m3+m6+m5

=∑(m3,m5,m6,m7)

F2=∑(m1,m2,m4,m7)

电路如习题5.16图所示

题5.16图

5.17解:

8选1多路选择器选用74HC151,根据其输出与输入的逻辑方程:

F1= =

A、5 B、6 C、8 D、43

8、比较两个一位二进制数A和B,当A=B时输出F=1,则F的表达式是()。

A、F=ABB、 C、 D、F=A⊙B

9、设某函数的表达式F=A+B,若用四选一数据选择器来设计,则数据端D0D1D2D3的状态是()。(设A为高位)

A、0111 B、1000 C、1010 D、0101

A、门电路B、触发器C、计数器D、寄存器

33、以下哪个编码不能是二-十进制译码器的输入编码(B)

A 0000B 1010C 1001 D 0011

34、8线—3线优先编码器的输入为I0—I7,当优先级别最高的I7有效时,其输出 的值是(C)。

A.111 B.010 C. 000 D. 101

35、十六路数据选择器的地址输入(选择控制)端有(C)个。

《数字电路与系统设计》课后答案

= A·BD·BC

(3) 画逻辑电路,如下图所示:

D

B

F

C

A

题4.4图

4.10电话室对3种电话编码控制,按紧急次序排列优先权高低是:火警电话、急救电话、普通电话,分别编码为11,10,01。试设计该编码电路。

解:设火警为A,急救为B,普通为C,列真值表为:

A

B

C

F

1

F2

1

1பைடு நூலகம்

1

0

1

1

0

0

0

1

0

1

0

0

0

= Y0Y4Y8Y12

F2(A,B,C,D)

m(0,1,2)

= m0m1m2

= Y0Y1Y2

F3(A,B,C,D)

m(8,9,10,11)

= m8m9m10m11

= Y8Y9Y10Y11

F4(A,B,C,D)m0

=Y0

数字电路与系统设计课后答案

4.1分析图P4.1电路的逻辑功能

数字电路与系统设计介绍

数字电路与系统设计介绍关于数字电路与系统设计介绍如下:一、数字电路基础数字电路是处理二进制数字信号的电路,其主要特点是将信号表示为离散的二进制形式。

数字信号具有抗干扰能力强、精度高等优点。

数字电路的基本单元是逻辑门电路,它们通过组合和时序逻辑设计,实现各种复杂的逻辑功能。

二、逻辑门电路逻辑门电路是数字电路的基本单元,它根据输入信号的逻辑值来决定输出信号的状态。

常见的逻辑门电路包括与门、或门、非门、与非门、或非门等。

这些逻辑门电路可以通过不同的组合和配置,实现复杂的逻辑运算。

三、组合逻辑电路组合逻辑电路是指只包含组合关系的逻辑电路。

在组合逻辑电路中,输出信号的状态仅取决于输入信号的当前状态,而不受时间的限制。

常见的组合逻辑电路包括加法器、比较器、多路选择器等。

四、时序逻辑电路时序逻辑电路是指包含时序关系的逻辑电路。

在时序逻辑电路中,输出信号不仅取决于当前的输入信号,还与前一时刻的输入信号有关。

常见的时序逻辑电路包括寄存器、计数器、移位器等。

五、数字系统设计方法数字系统设计是指将一组特定的功能需求转化为数字电路或数字系统的方法。

数字系统设计的方法主要包括自顶向下设计和自底向上设计两种。

自顶向下设计是指从高级抽象开始,逐步向低级抽象过渡的设计方法;自底向上设计是指从底层硬件开始,逐步构建更高层次抽象的设计方法。

六、可编程逻辑器件可编程逻辑器件是一种集成电路,其内部逻辑结构可以通过编程来配置。

可编程逻辑器件的出现,使得数字系统的设计和实现变得更加灵活和方便。

常见的可编程逻辑器件包括现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)等。

七、硬件描述语言硬件描述语言是一种用于描述数字系统硬件的语言。

它使用高级语言的形式来描述数字系统的结构和行为,使得数字系统的设计和实现更加方便和高效。

常见的硬件描述语言包括Verilog和VHDL等。

八、数字系统测试与验证数字系统测试与验证是确保数字系统正确性和可靠性的重要环节。

广东工业大学06与07数据库原理与设计A卷

广东工业大学考试试卷(A)参考答案及评分标准课程名称:数据库原理及应用(2006-2007年度第一学期)考试时间:第15周星期二(5月30日)一、选择填空题(每题1.5分,共30分)1、数据库系统阶段,数据______B_________。

A)具有物理独立性,没有逻辑独立性B)具有物理独立性和逻辑独立性C)独立性差D)具有逻辑独立性,没有物理独立性2、数据库系统的体系结构是C。

A)二级模式结构和一级映像B)三级模式结构和一级映像C)三级模式结构和二级映像D)三级模式结构和三级映像3、在数据库的三级模式结构中,描述数据库中全体数据的全局逻辑结构和特征的是D。

A)外模式B)内模式C)存储模式D)模式4、数据库的概念模型独立于A。

A)具体的计算机系统和DBMS B)E-R图C)信息世界D)现实世界5、需求分析阶段得到的结果是___A_____。

A)数据字典描述的数据需求B)E-R图表示的概念模型C)某个DBMS所支持的数据模型D)包括存储结构和存取方法的物理结构6、概念结构设计阶段得到的结果是___B_____。

A)数据字典描述的数据需求B)E-R图表示的概念模型C)某个DBMS所支持的数据模型D)包括存储结构和存取方法的物理广东工业大学试卷用纸,第1页共10页7、在下列关于关系的陈述中,错误的是BA)表中任意两行的值不能相同B)表中任意两列的值不能相同C)行在表中的顺序无关紧要D)列在表中的顺序无关紧要8、一个关系:DEPT(DNO,DNAME),如果要找出倒数第三个字母为W,并且至少包含4个字母的DNAME,则查询条件子句应写成WHERE DNAME LIKE____B_____A)‘__W_%’B)‘_%W__’C)‘_W__’D)‘_W_%’9、数据库中只存放视图的____C_______。

A)操作B)对应的数据C)定义D)限制10、有一个关系:学生(学号,姓名,系别),规定学号的值域是8个数字组成的字符串,这一规则属于_____C______。

数字逻辑电路与系统设计第6章习题及解答

第6章题解:6.1 试用4个带异步清零和置数输入端的负边沿触发型JK 触发器和门电路设计一个异步余3BCD 码计数器。

题6.1 解:余3BCD 码计数器计数规则为:0011→0100→…→1100→0011→…,由于采用异步清零和置数,故计数器应在1101时产生清零和置数信号,所设计的电路如图题解6.1所示。

CLK13图 题解6.1题6.2 试用中规模集成异步十进制计数器74290实现模48计数器。

题6.2 解:6.3 试用D 触发器和门电路设计一个同步4位格雷码计数器。

题6.3 解:根据格雷码计数规则,Q 3 Q 2Q 1 Q 0计数器的状态方程和驱动方程为:1333031210122202131011110320320100321321321321n n n n n n n nn n n n n n n n n n n n n n n n n n n n n n n n n n n n n n Q D Q Q Q Q Q Q Q Q D Q Q Q Q Q Q Q QD Q Q Q Q Q Q Q QQ D Q Q Q Q Q Q Q Q Q Q Q Q ++++==++==++==++==+++按方程画出电路图即可,图略。

题 6.4 解:反馈值为1010。

十一进制计数器6.5 试用4位同步二进制计数器74163实现十二进制计数器。

74163功能表如表6.4所示。

题 6.5 解:可采取同步清零法实现。

电路如图题解6.5所示。

题 6.6 解: 当M=1时:六进制计数器 当M=0时:八进制计数器图题解6.5图题解6.56.7 试用4位同步二进制计数器74163和门电路设计一个编码可控计数器,当输入控制变量M=0时,电路为8421BCD 码十进制计数器,M=1时电路为5421BCD 码十进制计数器,5421BCD 码计数器状态图如下图P6.7所示。

74163功能表如表6.4所示。

图 P 6.7Q 3Q 2Q 1Q 01010题6.7 解:实现8421BCD 码计数器,可采取同步清零法;5421BCD 码计数器可采取置数法实现,分析5421BCD 码计数规则可知,当21Q =时需置数,应置入的数为:32103000D D D D Q =。

数字系统设计与VerilogHDL课后习题

数字系统设计与VerilogHDL课后习题习题11.1现代EDA技术的特点有哪些?1.2什么是T op-down设计方式?1.3数字系统的实现方式有哪些?各有什么优缺点?1.4什么是IP复用技术? IP核对EDA技术的应用和发展有什么意义?1.5用硬件描述语言设计数字电路的优势是什么?1.6结合自己的使用情况谈谈对EDA工具的认识。

1.7基于FPGA/CPLD的数字系统设计流程包括哪些步骤?1.8什么是综合?常用的综合工具有哪些?1.9功能仿真与时序仿真有什么区别?1.10 FPGA与ASIC在概念上有什么区别?习题22.1 PLA和PAL在结构上有什么区别?2.2说明GAL的OLMC有什么特点,它怎样实现可编程组合电路和时序电路?2.3简述基于乘积项的可编程逻辑器件的结构特点。

2.4基于查找表的可编程逻辑结构的原理是什么?2.5基于乘积项和基于查找表的结构各有什么优点?2.6 CPLD和FPGA在结构上有什么明显的区别?各有什么特点?2.7 FPGA器件中的存储器块有何作用?2.8 Altera的MAX II器件是属于CPLD还是FPGA,请查阅有关资料并进行分析。

2.9边界扫描技术有什么优点?2.10说说JTAG接口都有哪些功能。

2.11 FPGA/CPLD器件未来的发展趋势有哪些?习题44.1 用Verilog设计一个8位加法器,进行综合和仿真,查看综合和仿真结果。

4.2 用Verilog设计一个8位二进制加法计数器,带异步复位端口,进行综合和仿真,查看综合和仿真结果。

4.3用Verilog设计一个模60的BCD码计数器,进行综合和仿真,查看综合和仿真结果。

习题66.1阻塞赋值和非阻塞赋值有什么本质的区别?6.2用持续赋值语句描述一个4选1数据选择器。

6.3用行为语句设计一个8位计数器,每次在时钟的上升沿,计数器加1,当计数器溢出时,自动从零开始重新计数。

计数器有同步复位端。

6.4设计一个4位移位寄存器。

数字系统设计

7.1.3 1. 数字系统的总体方案 数字系统的总体方案的优劣直接关系到整个数字系统的质量

与性能, 需要根据系统的功能要求、使用要求及性能价格比周密 思考后确定。 下面通过两个具体实例进行说明。

【例7-1】某数字系统用于统计串行输入的n位二元序列X中 “1”的个数,试确定其系统方案。

解 该数字系统的功能用软件实现最为方便, 但此处仅讨论 硬件实现问题。

st X

Q

CP2

位 数计 数 器

CP

控 制器

CLR

CP1

“ 1”数 计 数 器

do ne

“ 1”数 输 出

图 7 - 3 “1”数统计系统结构框图

该系统的大致工作过程如下: 系统加电时,系统处于等待状 态,即当st=0时,系统不工作;当st=1时,系统启动工作,控制器 输出CLR有效,将两个计数器清0,同时置输出状态信号done无效。

数字系统设计

7.1 数字系统设计概述 7.2 控制子系统的设计工具 7.3 控制子系统的实现方法 7.4 数字系统设计举例

7.1 数字系统设计概述

1. 什么是数字系统

在数字电子技术领域内,由各种逻辑器件构成的能够实现某 种单一特定功能的电路称为功能部件级电路,例如前面各章介绍 的加法器、 比较器、 译码器、数据选择器、计数器、移位寄存器、 存储器等就是典型的功能部件级电路, 它们只能完成加法运算、 数据比较、译码、数据选择、计数、移位寄存、数据存储等单一 功能。 而由若干数字电路和逻辑部件构成的、能够实现数据存储、 传送和处理等复杂功能的数字设备,则称为数字系统(Digital System)。电子计算机就是一个典型的复杂数字系统。

2 . 数字系统的逻辑划分

由于数据子系统和控制子系统的功能不同, 因此, 数字系 统的逻辑划分并不太困难。凡是有关存储、 处理功能的部分, 一律纳入数据子系统; 凡是有关控制功能的部分,一律纳入控 制子系统。逻辑划分后,就可以根据功能需要画出整个系统的结 构框图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

dout7-dout0

full empty

图 1 同步 FIFO 逻辑图

五、请写出 n 位(默认值为 8 位)三态缓冲器的 VHDL 描述: (10 分) 当控制端 en 为‘0’时,输出端 dout 为输入信号 din;当控制端 en 为‘1’时,输出端 dout 为高阻 态。 六、请画出下列 VHDL 描述的电路图: (12 分) ENTITY sh IS GENERIC(n:Integer := 4) ; PORT(clk,code_in:IN Bit;code_out:OUT Bit_Vector ( n DOWNTO 1)) ; END sh; * * * * * * * * * * * * * * * * * * * * *

* * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * 装 订 线 * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * * *

器。 数组。

数组,而 VHDL 综合器只支持 。 仿真和

9.属性 color’Left 表示 color 类型的 10.数字系统仿真主要有 11.VHDL 综合器只支持 12.VHDL 中的对象主要有 13.决断信号是 仿真、

仿真三个阶段。

模式的 LOOP 语句。 、 、 和 四类。 信号。 效应; 减小固有延迟的主要措施是

中 国 海 洋 大 学 命 题 专 用 纸(附页 B)

2006~2007 学年第 2 学期 试题名称 : 数字系统设计 A 共 3 页 第 3 页

ARCHITECTURE shift OF sh IS SIGNAL s:Bit_Vector(n DOWNTO 0) ; BEGIN s(0) <= code_in; FOR i IN 1 TO n GENERATE PROCESS(clk) BEGIN IF clk′ Event AND clk = ′1′ THEN s(i) <= s(i-1); END IF; END PROCESS; code_out(i) <= s(i); END GENERATE; END shift;

2.按照不同的生产工艺可以将数字集成电路划分为 3.按照不同的内部结构,可以将可编程逻辑器件划分为 器件;目前大量应用的可编程逻辑器件是 4.自顶向下的数字系统设计方法有 层次;在各个层次的设计中,主要有 5.行为综合是将 描述转换为 、 、 和

描述的过程。 电路和 电路划

6.为了保证时序逻辑电路的稳定性,应当将系统的 分在一个独立模块中。 7.并行信号赋值语句“x <= y;”的综合结果是一个 8.VHDL 仿真器支持

* * * * * *

* *

* * * *

中 国 海 洋 大 学 命 题 专 用 纸(附页 A)

2006~2007 学年第 2 学期 试题名称 : 数字系统设计 A 共 3 页 第 2 页

* * * *

* *

* * * *

* *

三、指出下列 VHDL 描述中的多处错误,并修改之: (12 分) ENTITY count IS PORT(reset,clk:IN Std_Logic; d_out:BUFFER Std_Logic_vector(7 DOWNTO 0) ; c_out:OUT Std_Logic) ; END; ARCHITECTURE cnt OF count IS BEGIN PROCESS(clk) VARIABLE d_var:Std_Logic_vector(7 DOWNTO 0) ; BEGIN d_var := d_out; IF reset = ′0′ THEN d_var := ″00000000″; c_out <= ′ 0′; ELSIF(clk′ Event AND clk = ′1′)THEN d_var := d_var+1; IF d_var = ″00000000″ THEN c_out <= ′1′; ELSE c_out <= ′0′; END IF; END IF; d_out <= d_var; END; din7-din0 END cnt; rd 四、图 1 是一个同步 FIFO 的逻辑图, 请写出它的实体说明。 (6 分) wr clk

中 国 海 洋 大 学 命 题 专 用 纸(首页)

2006~2007 学年第 2 学期 试题名称 : 数字系统设计 A

专业年级 学号 姓名 授课教师

共 3 页 第 1 页

分数

一、填空题(每空 1 分,共 42 分) 1.数字系统是使用数字技术 和 信息的电子系统。 工艺、 工艺和 结构器件和 。 、 、 和 和 四个设计 四种类型的工作。 工艺。 结构

信号;普通信号是

14.形成门电路固有延迟的物理机制是 减小 15.程序包体说明是对 16.IP 核分为 IP、 。 和 IP 和

的 分) 1.简述验证的三个主要目的。 2.简述“并行语句”与硬件电路之间的关系。 3.简述信号和变量这两种不同对象之间的根本区别。