74ls138引脚图-74ls138管脚图及功能真值表

74ls138功能介绍

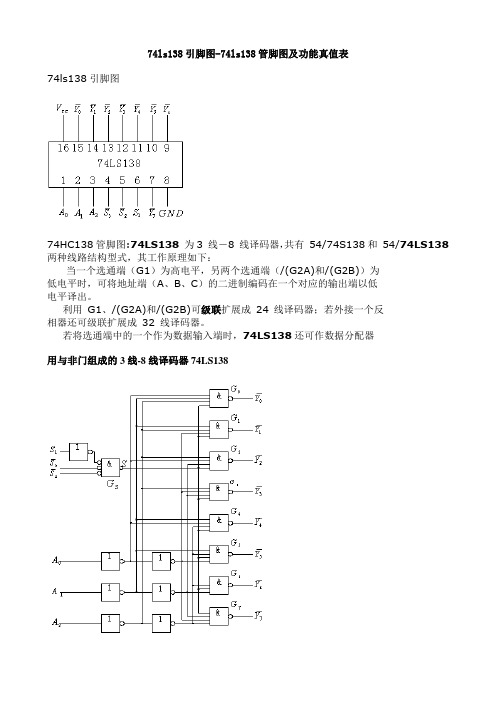

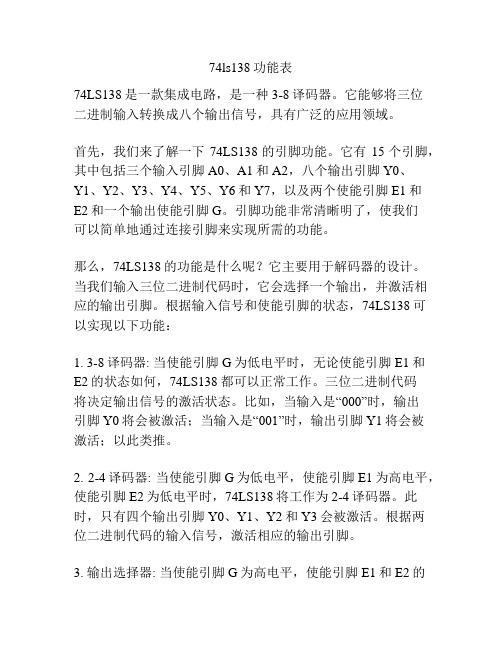

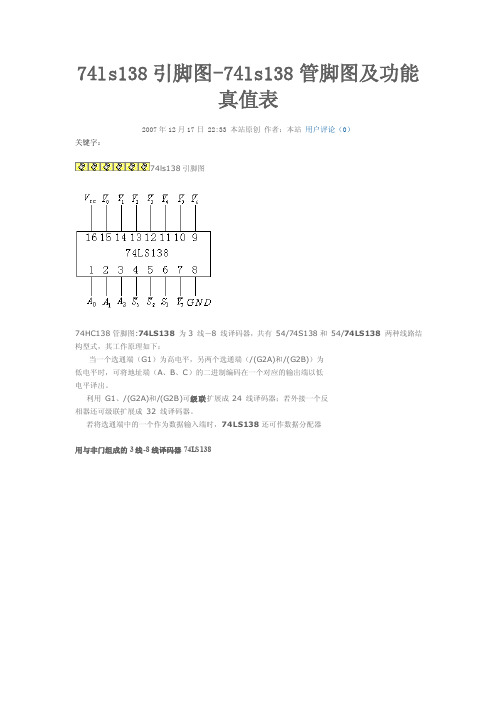

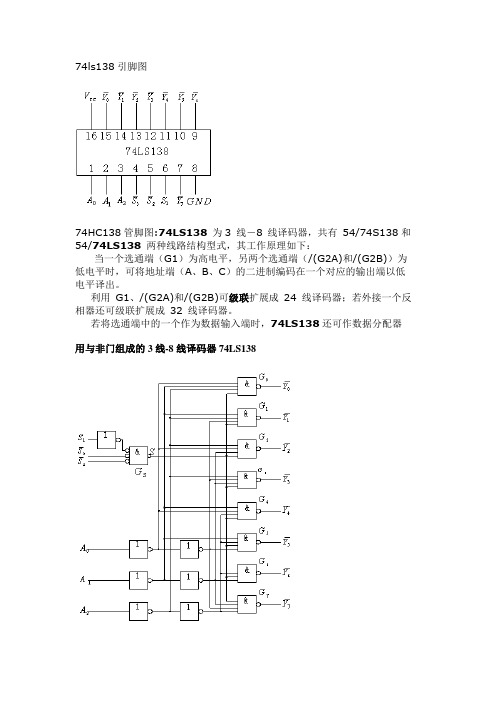

74ls138功能介绍74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74ls138管脚图及功能

74ls138引脚图-74ls138管脚图及功能真值表74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

三位二进制译码器-74LS138

H H H H L H H H H H H

H H H H H L H H H H H

H H H H H H L H H H H

H H H H H H H L H H H

H H H H H H H H L H H

H H H H H H H H H L H

H H H H H H H H H H L

3. 逻辑符号

D1

输

D2 D3 D4 D5

出

D6 D7

使能端 的作用

G1 G 2 A G2 B

× × L H H H H H H H H H × × L L L L L L L L × H × L L L L L L L L

译码 功能

× × × × × × L L L L L H L H H L H L H H H H

&

G=G 1⋅G 2A⋅ G 2B

3线/8线译码器

G 2B

输入 缓冲门

1 1

1 1

1 1

B2 B1 B0

1

G1 G 2A

3功能表

74LS138 的功能表

输 入 B2 B1 B0 D0 × × × L H L H L H L H H H H L H H H H H H H

三位二进制译码器—74LS138

——常用中规模集成译码电路 1. 内部结构 2. 功能表 3. 逻辑符号 4. 扩展 5. 应用—实现逻辑函数 6.管脚排列

1. 74LS138最小项译码器的电路结构

D7 D6 D5 D4 D3 D2 D1 D0

Di = G ⋅ mi

&

&

&

&

&

&

74LS系列主要芯片引脚及参数

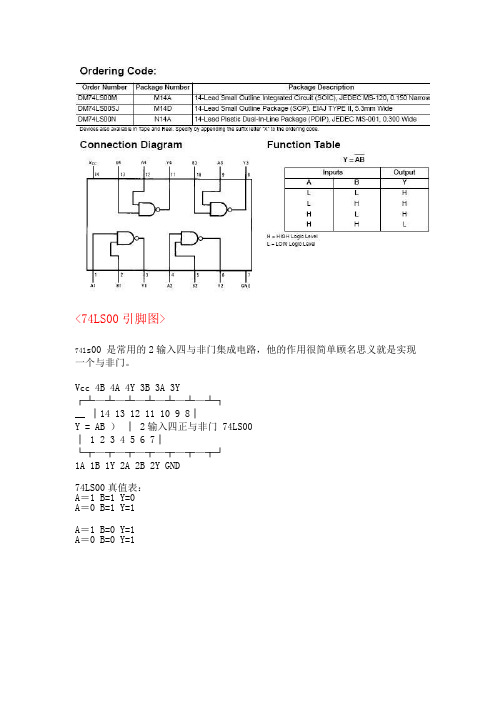

<74LS00引脚图>74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=174HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138图74ls138译码器内部电路3线-8线译码器74LS138的功能表备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。

<74ls138功能表>74LS138逻辑图无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出74ls138逻辑图由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

74ls138管脚图及功能真值表

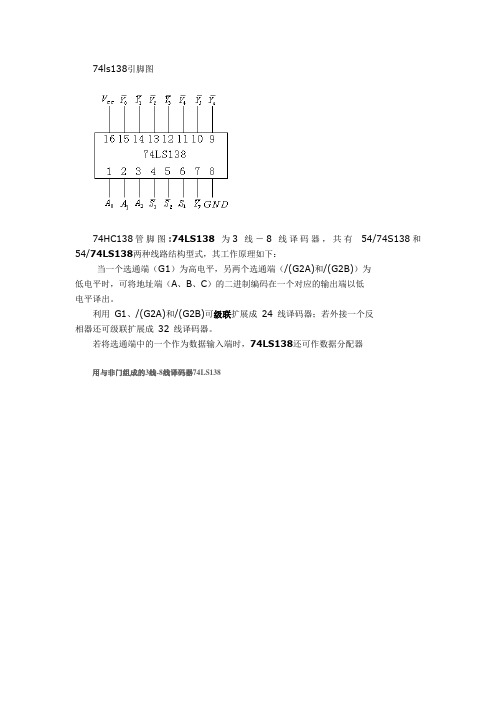

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74LS138中文资料P

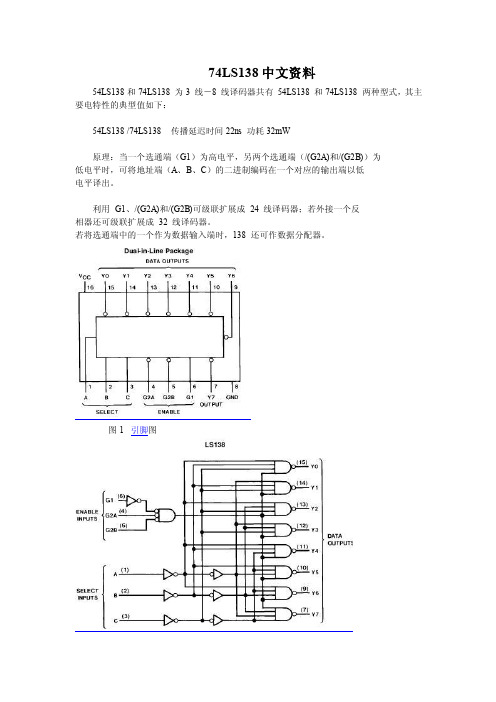

74LS138中文资料

54LS138和74LS138 为3 线-8 线译码器共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:

54LS138 /74LS138 传播延迟时间22ns 功耗32mW

原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为

低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低

电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反

相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

图1 引脚图

图2 内部逻辑管脚图

引脚功能:

A、B、C 译码地址输入端

G1 选通端/(G2A)、/(G2B) 选通端(低电平有效)Y0~Y7 译码输出端(低电平有效)

真值表:

建议操作条件:

电气参数:

动态特性表:。

74系列芯片引脚图及逻辑功能表

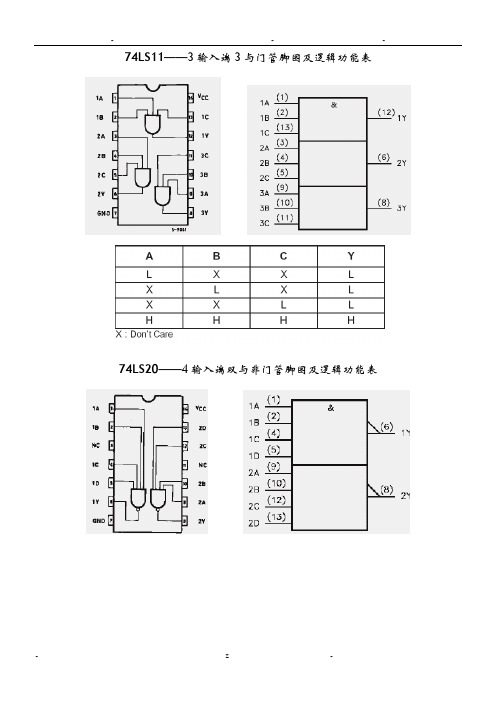

74LS11——3输入端3与门管脚图及逻辑功能表

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表

74LS138——3-8线译码器管脚图及逻辑功能表

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门

74LS54——4-2-3

与或非门

74LS08——2输入4与门。

74LS138中文资料P.pdf

74LS138中文资料54LS138和74LS138 为3 线-8 线译码器共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:54LS138 /74LS138 传播延迟时间22ns 功耗32mW原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

图1 引脚图图2 内部逻辑管脚图引脚功能:A、B、C 译码地址输入端G1 选通端/(G2A)、/(G2B) 选通端(低电平有效)Y0~Y7 译码输出端(低电平有效)真值表:建议操作条件:电气参数:符号参数测试条件最大值典型值最大值单位VI 输入钳位电压VCC = Min, II = -18 mA- - -1.5 VVOH 输出高电平电压VCC = Min, IOH = Max,VIL = Max, VIH = Min2.73.4 - VVOL 输出低电平电压VCC = Min, IOL = Max,VIL = Max, VIH = Min- 0.35 0.5V IOL = 4 mA, VCC = Min - 0.25 0.4II 最大输入电压时输入电流VCC = Max, VI = 7V - - 0.1 mAIIH 输入高电平电流VCC = Max, VI = 2.7V - - 20 mA IIL 输入低电平电流VCC = Max, VI = 0.4V - - -0.36 mA IOS 输出短路电流VCC = Max (Note 4) -20 - -100 mA ICC 电源电流VCC = Max (Note 5) - 6.3 10 mA 动态特性表:符号参数To (Output) 时滞RL = 2 kW单位CL = 15pF CL = 50 pF最大值最大值最大值最大值tPLH 低到高电平输出传递延迟时间Select to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 2 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Select to Output 3 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 3 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Enable to Output 2 - 24 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 3 - 18 - 27 nstPHL 传递延迟时间Enable to Output 3 - 28 - 40 ns。

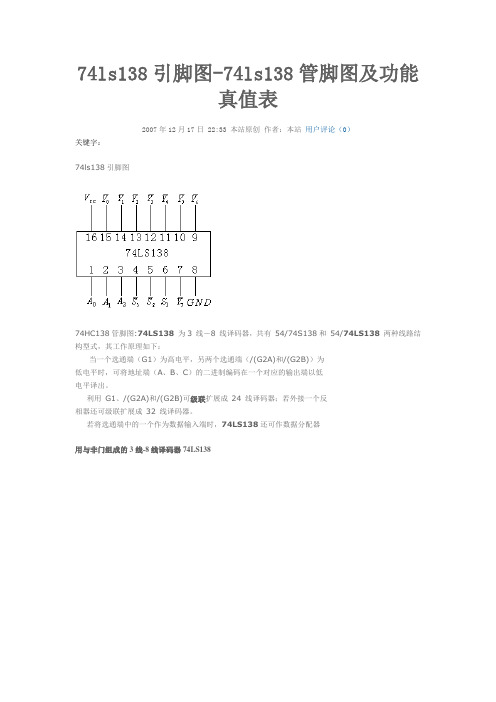

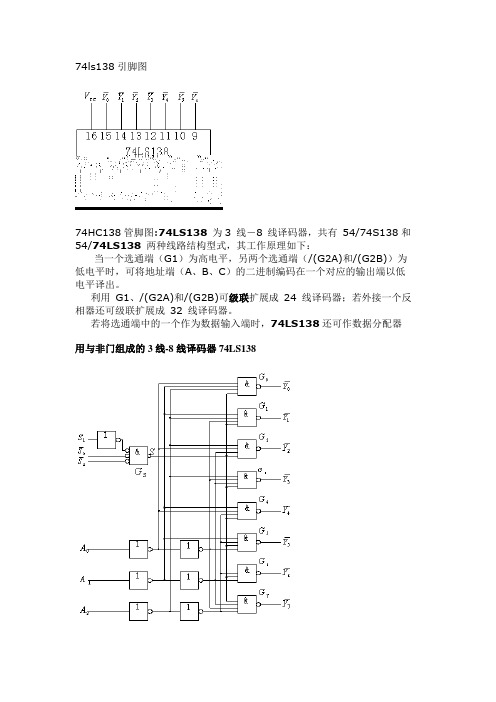

74ls138引脚图-74ls138管脚图及功能真值表

74ls138引脚图-74ls138管脚图及功能真值表2007年12月17日 22:33 本站原创作者:本站用户评论(0)关键字:74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

74LS138管脚功能的主要 介绍

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74ls138功能表

74ls138功能表74LS138是一款集成电路,是一种3-8译码器。

它能够将三位二进制输入转换成八个输出信号,具有广泛的应用领域。

首先,我们来了解一下74LS138的引脚功能。

它有15个引脚,其中包括三个输入引脚A0、A1和A2,八个输出引脚Y0、Y1、Y2、Y3、Y4、Y5、Y6和Y7,以及两个使能引脚E1和E2和一个输出使能引脚G。

引脚功能非常清晰明了,使我们可以简单地通过连接引脚来实现所需的功能。

那么,74LS138的功能是什么呢?它主要用于解码器的设计。

当我们输入三位二进制代码时,它会选择一个输出,并激活相应的输出引脚。

根据输入信号和使能引脚的状态,74LS138可以实现以下功能:1. 3-8译码器: 当使能引脚G为低电平时,无论使能引脚E1和E2的状态如何,74LS138都可以正常工作。

三位二进制代码将决定输出信号的激活状态。

比如,当输入是“000”时,输出引脚Y0将会被激活;当输入是“001”时,输出引脚Y1将会被激活;以此类推。

2. 2-4译码器: 当使能引脚G为低电平,使能引脚E1为高电平,使能引脚E2为低电平时,74LS138将工作为2-4译码器。

此时,只有四个输出引脚Y0、Y1、Y2和Y3会被激活。

根据两位二进制代码的输入信号,激活相应的输出引脚。

3. 输出选择器: 当使能引脚G为高电平,使能引脚E1和E2的状态无关紧要时,74LS138可以应用作为一个简单的八选一选择器。

在这种模式下,只有一个输出引脚被激活,输出引脚的选择由三位二进制代码确定。

值得一提的是,74LS138还具有连接能力,允许多个芯片级联,从而实现更大规模的译码和选择功能。

通过正确地连接多个74LS138芯片,我们可以构建出更为复杂的逻辑功能。

总结起来,74LS138是一款功能强大的集成电路,可以实现3-8译码器、2-4译码器和输出选择器等不同的工作模式。

它被广泛应用在数字电路设计、计算机接口、显示控制等领域。

74ls138引脚图-74ls138管脚图及功能真值表

74ls138引脚图-74ls138管脚图及功能真值表2007年12月17日 22:33 本站原创作者:本站用户评论(0)关键字:74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74L S1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

74LS138管脚功能

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。