74ls138引脚

74LS138部份38译码器部份实验

74LS138部份38译码器部份实验38译码器是通过3条线来达到控制8条线的状态,即2的3次方。

在电路中,起到扩展IO资源用。

74LS138引脚定义:74LS138逻辑表:相关原理:程序运行照片:以下实验通过P1.0,P1.1,P1.2三条数据线通过74LS138译码作一个8路跑马灯实验。

接线方法:1、用4PIN数据排线插入CPU部份的JP44的P1.0-P1.3 口.另一端插入74LS138部份的JP22作为数据输入。

2、用一条8PIN数据排线,连接78LS138的输出口JP25到 8路指示灯的JP32,运行可看到跑马灯。

程序流程图:汇编语言参考程序:org 0000hajmp mainorg 0080h ;;定义P1.0,P1.1,P1.2 分别为AA,BB,CC 以便在程序中描述AA EQU P1.0BB EQU P1.1CC EQU P1.2MAIN:CLR CC ;状态1 A,B,C为000CLR BBCLR AACALL DELAY ;调用延时CLR CC ;状态2 A,B,C 为100 CLR BBSETB AACALL DELAY ;调用延时CLR CC ;状态2 A,B,C 为010 SETB BBCLR AACALL DELAYCLR CCSETB BBSETB AACALL DELAYSETB CCCLR BBCLR AACALL DELAYSETB CCCLR BBSETB AACALL DELAYSETB CCSETB BBCLR AACALL DELAYSETB CCSETB BBSETB AACALL DELAYJMP MAIN ;重新开始DELAY: ;延时子程序MOV R5,#255D3:MOV R2,#255D4: DJNZ R2,D4 DJNZ R5,D3RETEND。

74ls138管脚图及功能

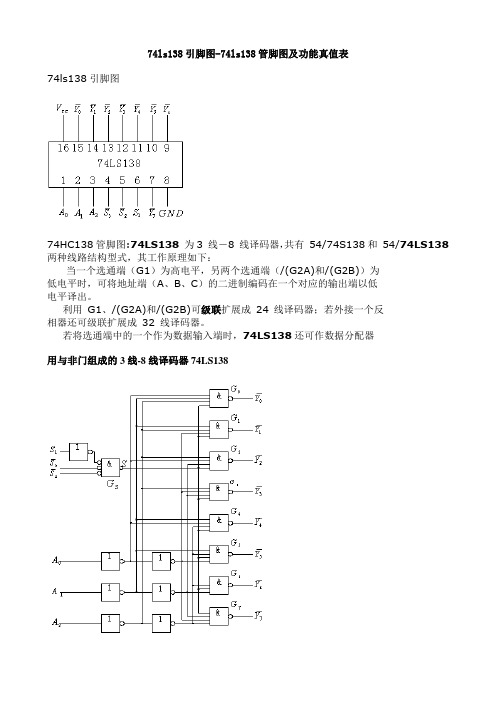

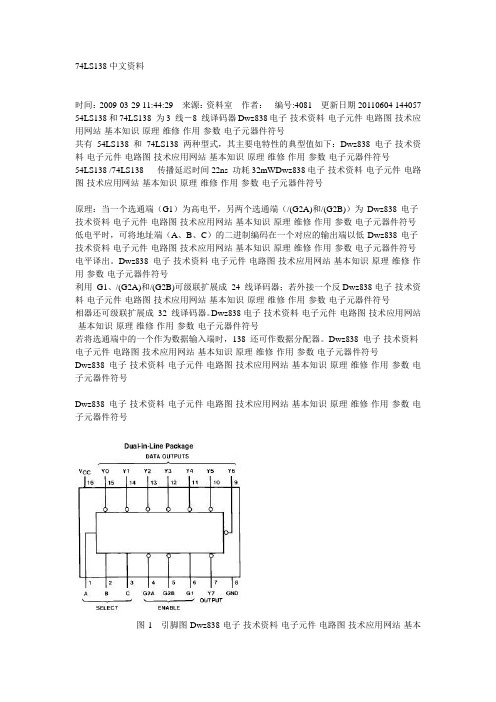

74ls138引脚图-74ls138管脚图及功能真值表74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

译码器引脚图

74LS138译码器引脚图,逻辑图及功能表74LS138与74HC的引脚图用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出功能介绍:就是38译码器,是TTL系列的,也就是74系列。

有三个输入端A0,A1,A2,其中A2是高位,输出是八个低电平输出Y0 ~ Y7,工作电压一般的5V就可以了,举个例子,你A0,A1,A2依次输入000,输出就是Y0,输入依次是001,输出就是Y1。

74ls381引脚图集成算术/逻辑运算单元(ALU)能够完成一系列算术运算和逻辑运算。

在这里我们介绍一种常用的集成算术/逻辑运算单元74LS381,它是四位算术/逻辑运算单元,管脚图如图3.3所示,A和B是预定的输入状态,根据输入信号S2~S0选择八种不同的功能。

图3.3 74LS381集成算术/逻辑运算单元(a)符号图(b)引脚图下面我们可以通过74LS381的功能表了解其功能。

表3.3 74LS381功能表由表3.3可知,74LS381能够进行六种算术和逻辑运算,并有清零和预置功能。

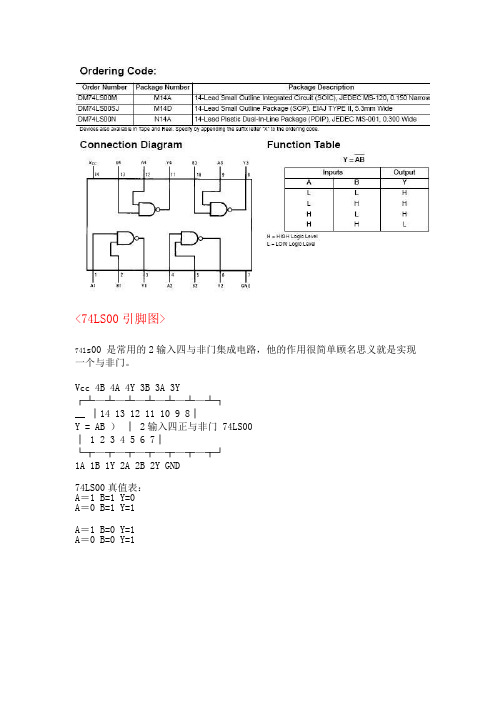

所谓清零是将各数据输出端的状态全为0;预置是使数据输出端输出预定的状态,进行预置操作时,预定的状态从A和B端输入.74ls00,74ls08引脚图[日期:2009-01-01 ] [来源:net 作者:佚名] [字体:大中小] (投递新闻)74ls00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND<74LS00引脚图>74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=1Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND<74LS08引脚图>是常用的2输入四正与门电路74LS08真值表:a b y0 0 00 1 01 0 01 1 1基本RS触发器原理基本RS触发器原理1 基本RS触发器的工作原理基本RS触发器的电路如图1(a)所示。

74LS系列主要芯片引脚及参数

<74LS00引脚图>74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=174HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138图74ls138译码器内部电路3线-8线译码器74LS138的功能表备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。

<74ls138功能表>74LS138逻辑图无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出74ls138逻辑图由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

74ls138管脚图及功能真值表

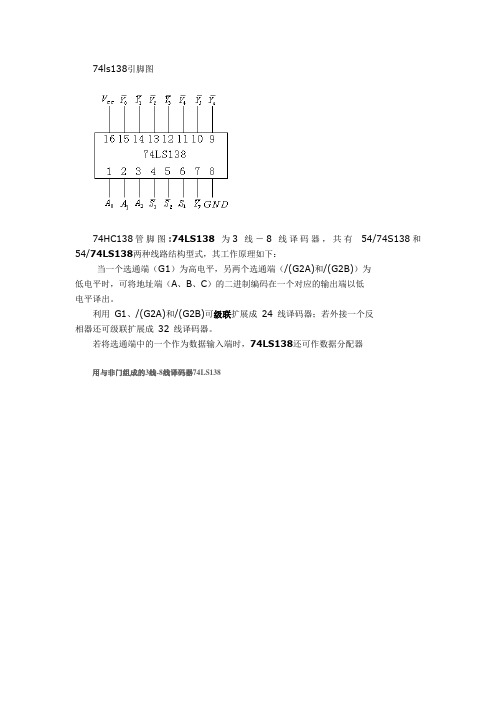

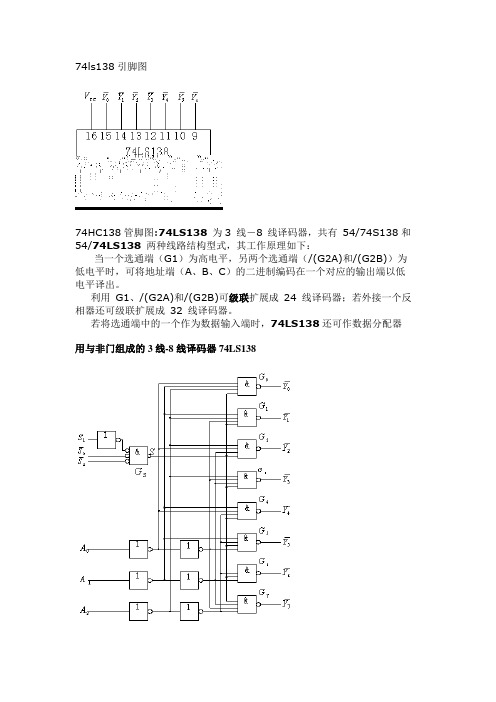

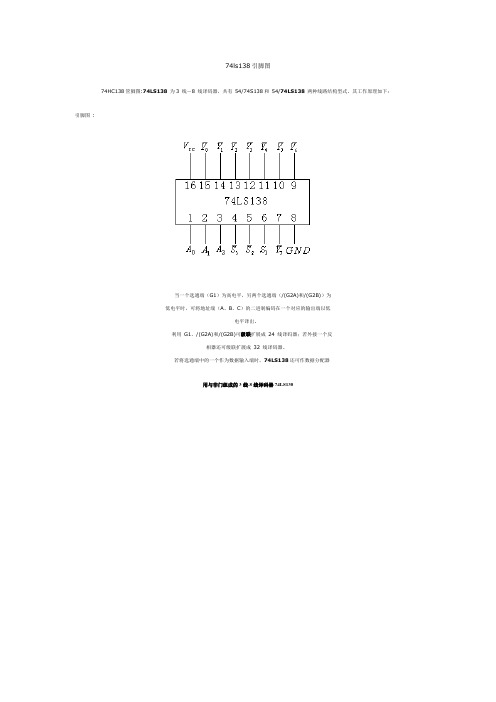

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

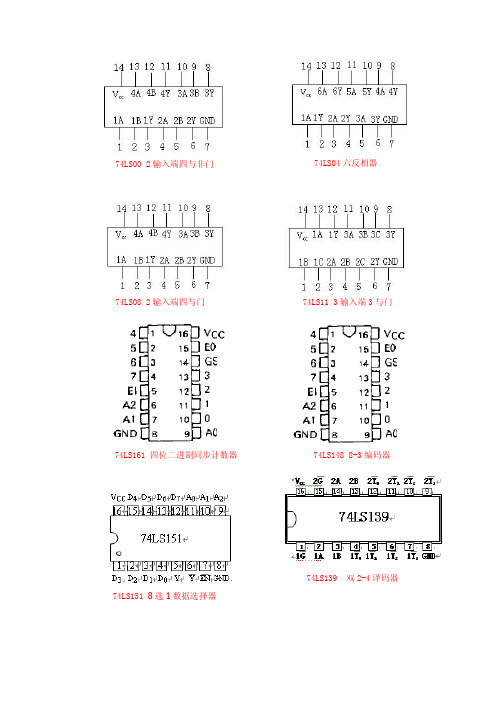

74系列芯片引脚图

类别 电路简称 四位比较器 74LS85

A3 B3

数据输入 A2 B2 A1 B1

真值表 A0 B0

级联输入

输出

A>B A<B A=B A>B A<B A=B

A3>B3 A3<B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3

GND 8

7744LLSS17124

16 Vcc 15 1CLR 14 2CLR 13 2CK 12 2K 11 2J 10 2PR 9 2Q

(a) JK 触发器 74112 引脚图

Y0 1

Y1 2

Y2 3 Y3 4 Y4 5 Y5 6 Y6 7 GND 8

7474LLSS7442

16 Vcc

15 A0 14 A1

13 A2 12 A3 11 Y9 10 Y8 9 Y7

图 3.2 74LS42 引脚图

74LS04

B1

C2

LT 3 BI/RBO 4

RBI 5 D6 A7

GND 8

747L4LSS7448

16 Vcc 15 f 14 g

13 a 12 b 11 c 10 d 9e

图 3.3 74LS48 引脚图

常用 74 系列 TTL 集成电路

真值表

时钟 CP J K

X

XX

X

XX

↓

00

↓

10

↓

01

↓

11

输出 清零(Q=0) 置 1(Q=1) 保持(Q=Qn)

Q=1 Q=0 翻转(Q=/Q)

电路引脚图

类别

电路简 称

译码器引应用图脚图

74LS138译码器引脚图,逻辑图及功能表74LS138与74HC的引脚图用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出功能介绍:74ls381引脚图集成算术/逻辑运算单元(ALU)能够完成一系列算术运算和逻辑运算。

在这里我们介绍一种常用的集成算术/逻辑运算单元74LS381,它是四位算术/逻辑运算单元,管脚图如图3.3所示,A和B是预定的输入状态,根据输入信号S2~S0选择八种不同的功能。

图3.3 74LS381集成算术/逻辑运算单元(a)符号图(b)引脚图下面我们可以通过74LS381的功能表了解其功能。

表3.3 74LS381功能表由表3.3可知,74LS381能够进行六种算术和逻辑运算,并有清零和预置功能。

所谓清零是将各数据输出端的状态全为0;预置是使数据输出端输出预定的状态,进行预置操作时,预定的状态从A和B端输入.74ls00,74ls08引脚图Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND<74LS00引脚图>74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=1Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND<74LS08引脚图>是常用的2输入四正与门电路74LS08真值表:a b y0 0 00 1 01 0 01 1 1基本RS触发器原理基本RS触发器原理1 基本RS触发器的工作原理基本RS触发器的电路如图1(a)所示。

74LS138中文资料P.pdf

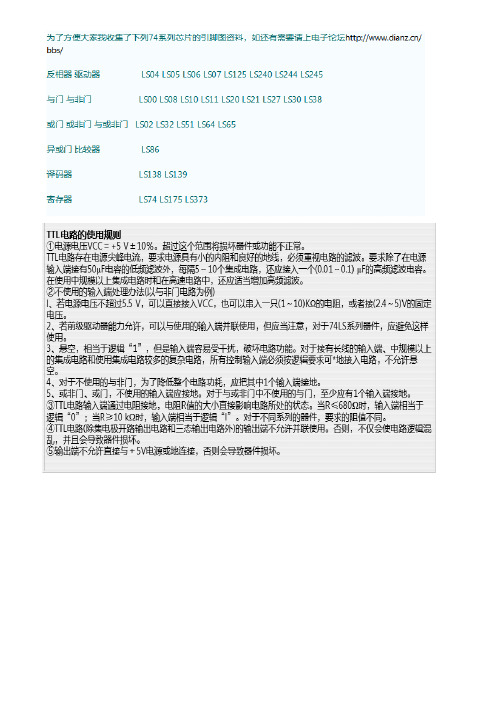

74LS138中文资料54LS138和74LS138 为3 线-8 线译码器共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:54LS138 /74LS138 传播延迟时间22ns 功耗32mW原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

图1 引脚图图2 内部逻辑管脚图引脚功能:A、B、C 译码地址输入端G1 选通端/(G2A)、/(G2B) 选通端(低电平有效)Y0~Y7 译码输出端(低电平有效)真值表:建议操作条件:电气参数:符号参数测试条件最大值典型值最大值单位VI 输入钳位电压VCC = Min, II = -18 mA- - -1.5 VVOH 输出高电平电压VCC = Min, IOH = Max,VIL = Max, VIH = Min2.73.4 - VVOL 输出低电平电压VCC = Min, IOL = Max,VIL = Max, VIH = Min- 0.35 0.5V IOL = 4 mA, VCC = Min - 0.25 0.4II 最大输入电压时输入电流VCC = Max, VI = 7V - - 0.1 mAIIH 输入高电平电流VCC = Max, VI = 2.7V - - 20 mA IIL 输入低电平电流VCC = Max, VI = 0.4V - - -0.36 mA IOS 输出短路电流VCC = Max (Note 4) -20 - -100 mA ICC 电源电流VCC = Max (Note 5) - 6.3 10 mA 动态特性表:符号参数To (Output) 时滞RL = 2 kW单位CL = 15pF CL = 50 pF最大值最大值最大值最大值tPLH 低到高电平输出传递延迟时间Select to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 2 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Select to Output 3 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 3 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Enable to Output 2 - 24 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 3 - 18 - 27 nstPHL 传递延迟时间Enable to Output 3 - 28 - 40 ns。

74LS138中文资料

74LS138中文资料时间:2009-03-29 11:44:29 来源:资料室作者:编号:4081 更新日期20110604 144057 54LS138和74LS138 为3 线-8 线译码器Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号54LS138 /74LS138 传播延迟时间22ns 功耗32mWDwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号电平译出。

Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号相器还可级联扩展成32 线译码器。

Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号图1 引脚图Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号图2 内部逻辑管脚图Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号引脚功能:Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号A、B、C 译码地址输入端Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号G1 选通端Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号/(G2A)、/(G2B) 选通端(低电平有效)Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Y0~Y7 译码输出端(低电平有效)Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号真值表:Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Dwz838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号本文来自【838电子】:/ad/PCB/1039.html本文来自【838电子】:/ad/PCB/1039.html本文来自【838电子】:/ad/PCB/1039.html本文来自【838电子】:/ad/PCB/1039.html。

74138的工作原理如下图所示

74138的工作原理如下图所示:从上图可看出,74138有三个输入端:A0、A1、A2和八个输出端Q0~Q7。

当输入端A0、A1、A2的编码为000时,译码器输出为Q0=0,而Q1~Q7=1。

即Q0对应于A0、A1、A2为000状态,低电平有效。

A0、A1、A2的另外7种组合见后面的真值表。

图中S1、S2、S3为使能控制端,起到控制译码器是否能进行译码的作用。

只有S1为高电平,S2、S3均为低电平时,才能进行译码,否则不论输入羰输入为何值,每个输出端均为1。

下图是输入端A0、A1、A2为000,控制端S1=1、S1=0、S2=0的电平示意图(红色数字为端口电平),大家可按下图进行分析,也可以分析输出端另外七种组合时的输出情况。

74138 三线-八线译码器真值表:一、译码器的定义及功能1. 定义:具有译码功能的逻辑电路称为译码器。

译码即编码的逆过程,将具有特定意义的二进制码进行辨别,并转换成控制信号。

2. 分类:3. 功能:二进制译码器一般原理图一个n→2n译码器结构如上图,n个输入端,2n个输出端。

它是一个多输出逻辑组合电路,对每种可能的输入条件,有且仅有一个输出信号为逻辑“1”,所以我们可以把它当作最小项产生器,一个输出就相应于提取一个最小项。

4. 译码器电路结构:首先我们先来分析两输入译码器结构,由于2输入变量A、B共有4种不同状态的组合,因而可以译出4个输出信号,所以简称为2/4线译码器。

2线-4线译码器逻辑图由图可以写出输出端逻辑表达式:根据输出逻辑表达式可以列出功能表。

由表可知,时无论A、B 为何种状态,输出全为1,译码器处于非工作状态。

而当时,对应于AB 的某种状态组合,其中只有一个输出量为0,其余各输出量均为1。

例如:AB=0时,输出Y0=0,Y1~Y3=1,由此可见,译码器是通过输出端的逻辑电平来识别不同的代码。

在我们讲述的这种结构中,输出0表示有效电平,所以就叫做低电平有效。

2线-4线译码器功能表输入输出EI A B Y0Y1Y2Y31 x X 1 1 10 0 0 0 1 1 10 0 1 1 0 1 10 1 0 1 1 0 10 1 1 1 1 0二、集成电路译码器1.74138集成译码器下图为常用的集成译码器74LS138的逻辑图和引脚图。

74LS138管脚功能的主要 介绍

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

IC74LS138引脚及说明

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:引脚图:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

基于2片74LS138的单片机I-O口扩展分析

输出站 Y0~Y7,端,用于提供芯片 AD9835 的片选信号(FSYNC)。 同样对于第二片 74LS138 芯片而言,使能输入端 G2a 和 G2b 加载低 电平,使能输入端 G1 由 AT89C51 单片机的 P1.3 端提供。当 P1.3 端提供高 电平时,74LS138 芯片处于工作的状态;当 P1.3 端提供低电平时,74LS138 芯 片处于不工作的状态。因此通过上述 2 片 74LS138 芯片的连接,可以实现 4 端输入一 16 端输出的扩展功能。其中,输出端 Y8~Y11 端用于提供芯片 AD9835 的片选信号(FSYNC)。

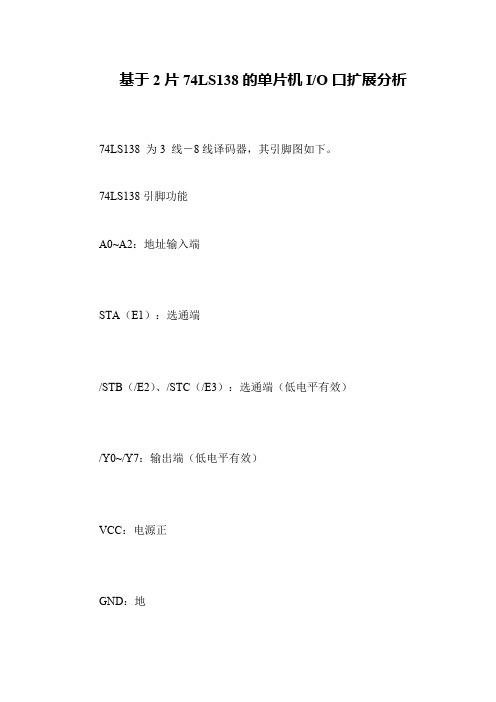

基于 2 片 74LS138 的单片机 I/O 口扩展分析

74LS138 为 3 线-8 线译码器,其引脚图如下。 74LS138 引脚功能 A0~A2:地址输入端 STA(E1):选通端 /STB(/E2)、/STC(/E3):选通端(低电平有效) /Y0~/Y7:输出端(低电平有效) VCC:电源正 GND:地

A0~A2 对应 Y0Y7; A0,A1,A2 以二进制形式输入,然后转换成十进制,对应相应 Y 的序号输出低电平,其他均为高电平; 基于 2 片 74LS138 的单片机 I/O 口扩展 将 2 片 74LS138 芯片采用如上图所示的连接方式,来实现对 AT89C51 芯片 I/O 口的扩展。其中,使能端 G1 选择高电平,G2b 选择低电 平。4 个输入口 A0~A3 分别与单片机 AT89C51 的 P1.0~P1.3 相连,实现对 AD9835 芯片的片选功能;Y0~Y15 端用于输出。根据上图所示,可以得到相 应的真值表,如下表所示。 根据上述 2 片 74LS138 芯片所组成的真值表,可以得到相应的逻辑 表达式: 相应的 Protel 电路连接图,如图所示。其中,第一片 74LS138 芯

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

秦驰74ls138引脚图

74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为

低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低

电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反

相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器

用与非门组成的3线-8线译码器74LS138

3线-8线译码器74LS138的功能表

无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出

由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.

5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以

反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

解:由图3.3.8可见,74LS138仅有3个地址输入端。

如果想对4位二进制代码,只能利用一个附加控制端(当中的一个)作为第四个地址输入端。

取第(1)片74LS138的和作为它的第四个地址输入端(同时令),取第(2)片的作为它的第四个地址输入端(同时令),取两片的、、,并将第(1)片的和接至,将第(2)片的接至,如图3.3.9所示,于是得到两片74LS138的输出分别为

图3.3.9 用两片74LS138接成的4线-16线译码器

式(3.3.8)表明时第(1)片74LS138工作而第(2)片74LS138禁止,将的0000~0111这8个代码译成8个低电平信号。

而式(3.3.9)表明时,第(2)片7 4LS138工作,第(1)片74LS138禁止,将的1000~1111这8个代码译成8个低电平信号。

这样就用两个3线-8线译码器扩展成一个4线-16线的译码器

了。

同理,也可一用两个带控制端的4线-16线译码器接成一个5线-32线译码器。

例2.74LS138 3-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。

试画出八个输出引脚的波形。

解:由74LS138的功能表知,当(A为低电平段)译码器不工作,8个输出引脚全为高电平,当(A为高电平段)译码器处于工作状态。

因所以其余7个引脚输出全为高电平,因此可知,在输入信号A的作用下,8个输出引脚的波形如下:

即与A反相;

其余各引脚的输出恒等于1(高电平)与A的波形无关。