74ls138功能介绍

74ls138功能介绍

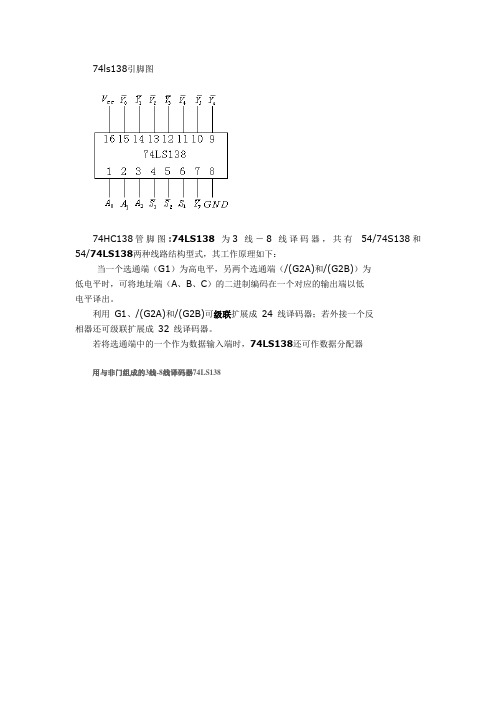

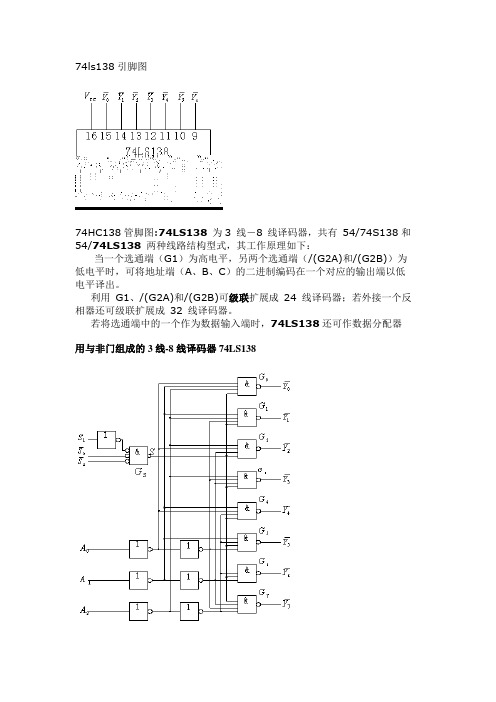

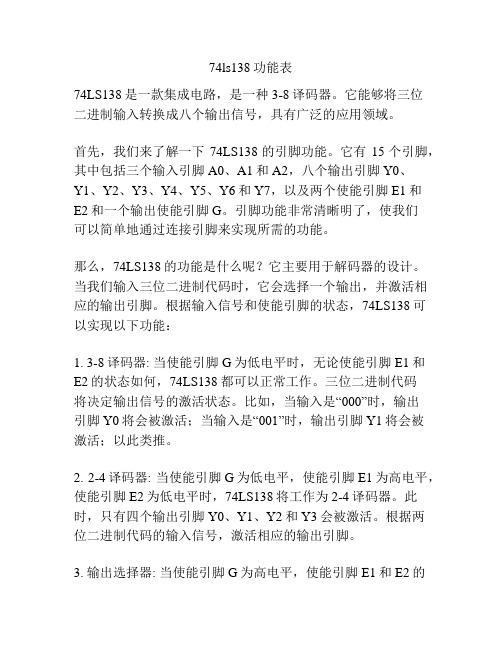

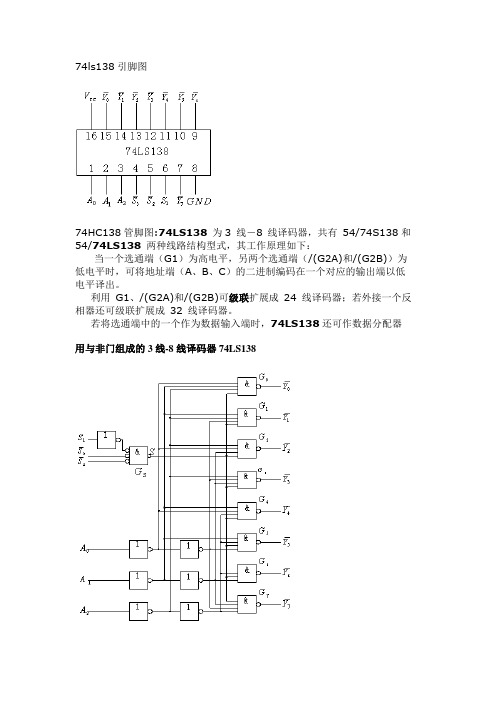

74ls138功能介绍74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

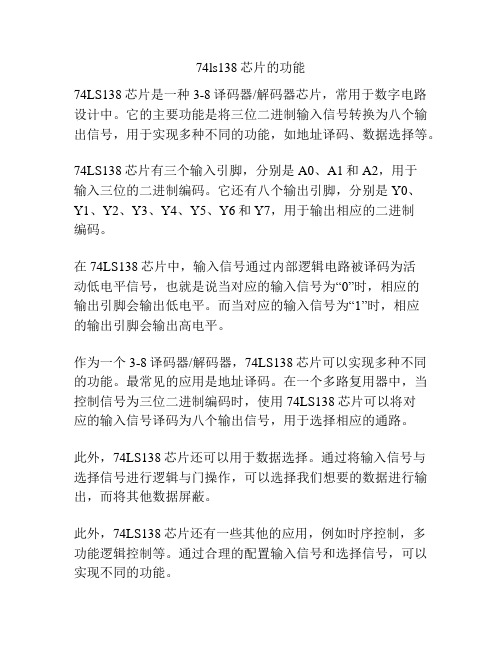

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74LS138译码器引脚图逻辑图及功能表

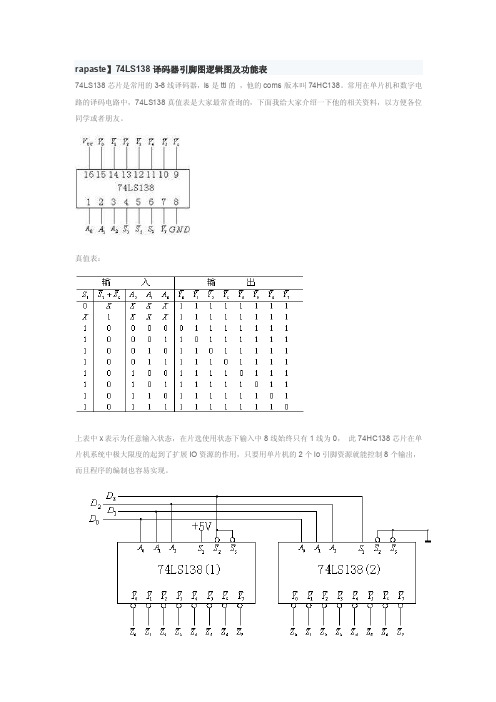

rapaste】74LS138译码器引脚图逻辑图及功能表

74LS138芯片是常用的3-8线译码器,ls是ttl的,他的coms版本叫74HC138。

常用在单片机和数字电路的译码电路中,74LS138真值表是大家最常查询的,下面我给大家介绍一下他的相关资料,以方便各位同学或者朋友。

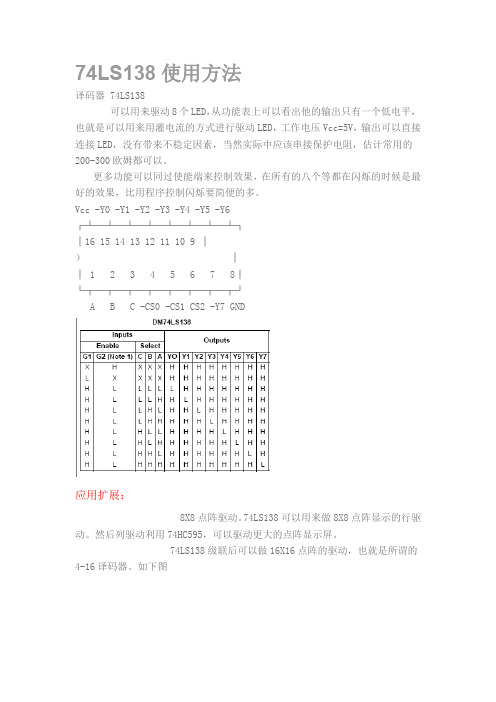

真值表:

上表中x表示为任意输入状态,在片选使用状态下输入中8线始终只有1线为0,此74HC138芯片在单片机系统中极大限度的起到了扩展IO资源的作用,只要用单片机的2个io引脚资源就能控制8个输出,而且程序的编制也容易实现。

拓展

式(3.3.8)表明时第(1)片74LS138工作而第(2)片74LS138禁止,将的0000~0111这8个代码译成8个低电平信号。

而式(3.3.9)表明时,第(2)片74LS138工作,第(1)片74LS138禁止,将的1000~1111这8个代码译成8个低电平信号。

这样就用两个3线-8线译码器扩展成一个4线-16线的译码器了。

同理,也可一用两个带控制端的4线-16线译码器接成一个5线-32线译码器。

例2.74LS138 3-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。

试画出八个输出引脚的波形

解:由74LS138的功能表知,当(A为低电平段)译码器不工作,8个输出引脚全为高电平,当(A为高电平段)译码器处于工作状态。

因所以其余7个引脚输出全为高电平,因此可知,在输入信号A的作用下,8个输出引脚的波形如下:

即与A反相;

其余各引脚的输出恒等于1(高电平)与A的波形无关。

74ls138芯片的功能

74ls138芯片的功能

74LS138芯片是一种3-8译码器/解码器芯片,常用于数字电路设计中。

它的主要功能是将三位二进制输入信号转换为八个输出信号,用于实现多种不同的功能,如地址译码、数据选择等。

74LS138芯片有三个输入引脚,分别是A0、A1和A2,用于

输入三位的二进制编码。

它还有八个输出引脚,分别是Y0、

Y1、Y2、Y3、Y4、Y5、Y6和Y7,用于输出相应的二进制

编码。

在74LS138芯片中,输入信号通过内部逻辑电路被译码为活

动低电平信号,也就是说当对应的输入信号为“0”时,相应的

输出引脚会输出低电平。

而当对应的输入信号为“1”时,相应

的输出引脚会输出高电平。

作为一个3-8译码器/解码器,74LS138芯片可以实现多种不同的功能。

最常见的应用是地址译码。

在一个多路复用器中,当控制信号为三位二进制编码时,使用74LS138芯片可以将对

应的输入信号译码为八个输出信号,用于选择相应的通路。

此外,74LS138芯片还可以用于数据选择。

通过将输入信号与

选择信号进行逻辑与门操作,可以选择我们想要的数据进行输出,而将其他数据屏蔽。

此外,74LS138芯片还有一些其他的应用,例如时序控制,多

功能逻辑控制等。

通过合理的配置输入信号和选择信号,可以实现不同的功能。

总结起来,74LS138芯片是一种常用的3-8译码器/解码器芯片,它能够将三位的二进制输入信号译码为八个输出信号,用于实现多种不同的功能。

它在数字电路设计中具有广泛的应用,如地址译码、数据选择、时序控制等。

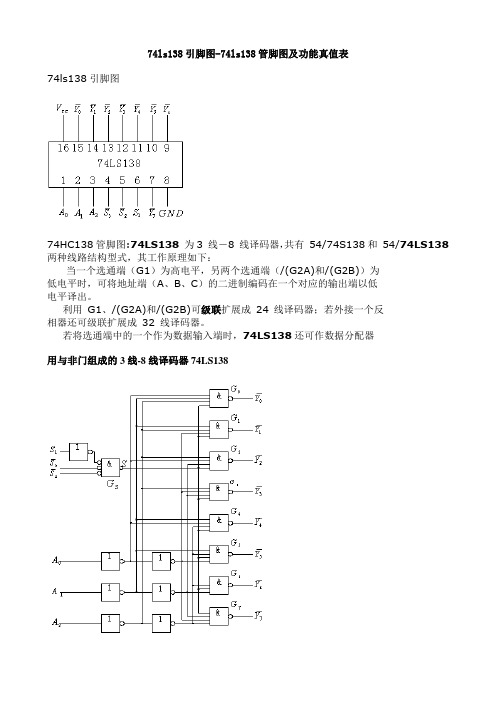

74ls138管脚图及功能

74ls138引脚图-74ls138管脚图及功能真值表74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74LS138中文资料[1]

![74LS138中文资料[1]](https://img.taocdn.com/s3/m/6ededed2d15abe23482f4d6d.png)

54138/741383线-8线译码器 简要说明: 138为3线-8线译码器,共有54/74S138和54/74LS138两种线路结构型式,其主要电特性的典型值如下:型号T pd (ABC->Y)(3级)P D CT54S138/CT74S1388ns 245mW CT54LS138/CT74LS13822ns32mW当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A 、B 、C )的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24线译码器;若外接一个反相器还可级联扩展成32线译码器。

若将选通端中的一个作为数据输入端时,138还可作数据分配器。

管脚图:引出端符号: A、B、C 译码地址输入端 G1 选通端 /(G2A)、/(G2B) 选通端(低电平有效) Y0~Y7 译码输出端(低电平有效)功能表:ww w.t a i -ya n.c o m/b b s/G2*=G2A+G2B H=高电平 L=低电平 X=任意 极限值 电源电压------------------------------------------------7V 输入电压54/74S138----------------------------------------5.5V 54/74LS138---------------------------------------7V 工作环境温度 54×××------------------------------ -55~125℃ 74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃推荐工作条件:CT54S138/CT74S138CT54LS138/CT74LS138最小额定最大最小额定最大单位 544.5 5 5.54.5 5 5.5电源电压Vcc744.75 5 5.254.75 5 5.25 V输入高电平电压V IH 2 2 V 54 0.8 0.7输入低电平电压V IL 740.8 0.8V输出高电平电流I OH -1000 -400 µA 54 20 4输出低电平电流I OL74208mA逻辑图ww w.t a i -ya n.c o m/b b s静态特性(T A 为工作环境温度范围)`S138 `LS138 参数 测试条件【1】 最小最大最小最大 单位 VIK 输入钳位电压Vcc 最小 IIK=-12mA-1.2 -1.5 V 54 2.52.5VOH 输出高电平电压 Vcc=最小,VIH=2V,VIL=最大,IOH=最大 74 2.7 2.7 V54 0.50.4 VOL 输出低电平电压 VCC=最小,VIH=2V,VIL=最大,IOL=最大 740.50.5 VVI=5.5V 1II 最大输入电压时输入电流 Vcc=5VVI=7V0.1 mA IH 输入高电平电流Vcc=5V,VIH=2.7V 50 20 μA VI=5.5V 1II 最大输入电压时输入电流 Vcc=最大VI=7V0.1 mA IIH 输入高电平电流 Vcc=最大 VIH=2.7V50 20 μA VIL=0.4V -0.4 VIL 输入低电平电流 Vcc=最大VIL=0.5V-2 mA 54-40 -100-6 -40 IOS 输出短路电流Vcc=最大 74-40-100-5 -42 mA Icc 电源电流Vcc=最大7410mA【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

三位二进制译码器-74LS138

H H H H L H H H H H H

H H H H H L H H H H H

H H H H H H L H H H H

H H H H H H H L H H H

H H H H H H H H L H H

H H H H H H H H H L H

H H H H H H H H H H L

3. 逻辑符号

D1

输

D2 D3 D4 D5

出

D6 D7

使能端 的作用

G1 G 2 A G2 B

× × L H H H H H H H H H × × L L L L L L L L × H × L L L L L L L L

译码 功能

× × × × × × L L L L L H L H H L H L H H H H

&

G=G 1⋅G 2A⋅ G 2B

3线/8线译码器

G 2B

输入 缓冲门

1 1

1 1

1 1

B2 B1 B0

1

G1 G 2A

3功能表

74LS138 的功能表

输 入 B2 B1 B0 D0 × × × L H L H L H L H H H H L H H H H H H H

三位二进制译码器—74LS138

——常用中规模集成译码电路 1. 内部结构 2. 功能表 3. 逻辑符号 4. 扩展 5. 应用—实现逻辑函数 6.管脚排列

1. 74LS138最小项译码器的电路结构

D7 D6 D5 D4 D3 D2 D1 D0

Di = G ⋅ mi

&

&

&

&

&

&

74ls138功能

74ls138功能74LS138是一种三线至八线译码器/多路复用器集成电路。

它的功能是将三个输入线(A, B, C)的组合编码转换成八个输出线之一(Y0-Y7)。

74LS138由两个部分组成:译码器和多路复用器。

译码器功能:它的主要功能是将输入的三位二进制代码(A, B, C)转化为对应的八个输出线之一(Y0-Y7)。

当输入的二进制代码与译码器的内部逻辑相匹配时,相应的输出线Y0-Y7被激活(置1),其余的输出线则被禁用(置0)。

译码器使用了多个与门和非门来实现这一功能。

多路复用器功能:多路复用器的功能是根据A, B, C三个输入线的状态,将输入的八个数据线(D0-D7)中的一个复制到输出线(Y)上。

由于译码器部分已经实现了对应关系,所以多路复用器只需要将对应的输入线连接到输出线即可。

74LS138的特点:1. 它是一种低功耗TTL(Transistor-Transistor Logic)电平集成电路。

2. 由于采用了多个与门和非门的组合,所以能够实现高速的编码和译码功能。

3. 使用了三输入线,八输出线的结构,适用于处理三位二进制的多路选择问题。

4. 输出线具有驱动能力,可以连接较高负载电器。

5. 内部结构简单,易于集成和使用。

应用领域:74LS138广泛应用于数字电子系统中的地址译码、信号切换和信号分发等方面。

例如,它可以被用作存储器的地址译码器,将不同的地址对应到存储器的不同单元,使得系统能够选择正确的存储器单元读取或写入数据。

另外,它还可以用于多路选择器或多路复用器,将多个输入信号中的一个选择输出。

总之,74LS138是一种功能强大、应用广泛的译码器/多路复用器集成电路,能够高效地处理二进制编码和多路选择问题。

74ls138管脚图及功能真值表

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74ls138功能介绍

74ls138功能介绍

74LS138是一个3-8位多路编码器,中文称作3-8位多路选择器,它是一种典型的电路集成设备,也就是集成电路,是美国贝尔实验室公司以Schottky技术设计生产的一款常用的低功耗数字电路。

74LS138用途多样,最常见的应用是用来做地址选择,或条件选择等功能的手段。

它的基本结构和功能有助于解决电子设备中比较复杂的运算路径问题。

74LS138由一个核心和两个要素组成,它有三个数据输入端:A0、A1、A2分别对应选择信号,不同的选择信号可以控制多个数据输出端Y0-Y7,有八位输出,每个输出都有一个单独的输出端。

74LS138剩余两个输入端有什么功能呢?它们是入端和修正端,输入端遵守电平小布局七段码规则,输入端可控制单路和多路输出,就是说一个输入端的电平可以引导8个输出端的电平,控制不同的输出端的电平,这样可以给数据结构赋值;而修正端CN1让其入端能够选择不同的某一个输出端,加快这8个输出端的工作速度。

74LS138可以用在许多应用场合中,它可以将3位二进制编码信号转换为8组不同的分离控制信号,对比较复杂的多路信号控制有非常好的用途,在数据处理中它也起着至关重要的作用,常常和过程计算机一起使用来负责程序的加载、编辑等工作。

总的来说,74LS138是一块非常有用的集成电路,它可以将一个三位二进制信号转换成八路不同的控制信号,同时具有非常优良的特性,它的功耗极低,运算特性也极好,作为一款常用的基础电路,被普遍应用于各类计算机、测控、汽车、村村电路等设备中。

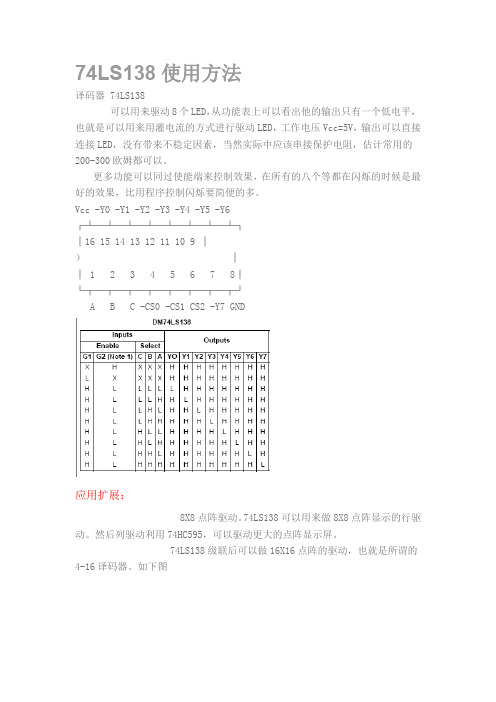

译码器使用

74LS138使用方法译码器 74LS138可以用来驱动8个LED,从功能表上可以看出他的输出只有一个低电平,也就是可以用来用灌电流的方式进行驱动LED,工作电压Vcc=5V,输出可以直接连接LED,没有带来不稳定因素,当然实际中应该串接保护电阻,估计常用的200-300欧姆都可以。

更多功能可以同过使能端来控制效果,在所有的八个等都在闪烁的时候是最好的效果,比用程序控制闪烁要简便的多。

Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6┌┴─┴─┴─┴─┴─┴─┴─┴┐│16 15 14 13 12 11 10 9 │)││ 1 2 3 4 5 6 7 8│└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND应用扩展:8X8点阵驱动。

74LS138可以用来做8X8点阵显示的行驱动。

然后列驱动利用74HC595,可以驱动更大的点阵显示屏。

74LS138级联后可以做16X16点阵的驱动,也就是所谓的4-16译码器。

如下图这样就可以驱动点阵了。

当然也可以使用74LS154,看自己的需要了。

^_^74HC595使用总结发表于2007/11/26 16:37:3074HC595外形图________QB --|1 16|--VccQC --|2 15|--QAQD --|3 14|--SIQE --|4 13|--/GQF --|5 12|--RCKQG --|6 11|--SCKQH --|7 10|--/SCLRGND-|8 9|--QH'|________|74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

QH': 级联输出端。

我将它接下一个595的SI端。

SI: 串行数据输入端。

74595的控制端说明:/SCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SCK(11脚):上升沿时数据寄存器的数据移位。

74LS138中文资料P.pdf

74LS138中文资料54LS138和74LS138 为3 线-8 线译码器共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:54LS138 /74LS138 传播延迟时间22ns 功耗32mW原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

图1 引脚图图2 内部逻辑管脚图引脚功能:A、B、C 译码地址输入端G1 选通端/(G2A)、/(G2B) 选通端(低电平有效)Y0~Y7 译码输出端(低电平有效)真值表:建议操作条件:电气参数:符号参数测试条件最大值典型值最大值单位VI 输入钳位电压VCC = Min, II = -18 mA- - -1.5 VVOH 输出高电平电压VCC = Min, IOH = Max,VIL = Max, VIH = Min2.73.4 - VVOL 输出低电平电压VCC = Min, IOL = Max,VIL = Max, VIH = Min- 0.35 0.5V IOL = 4 mA, VCC = Min - 0.25 0.4II 最大输入电压时输入电流VCC = Max, VI = 7V - - 0.1 mAIIH 输入高电平电流VCC = Max, VI = 2.7V - - 20 mA IIL 输入低电平电流VCC = Max, VI = 0.4V - - -0.36 mA IOS 输出短路电流VCC = Max (Note 4) -20 - -100 mA ICC 电源电流VCC = Max (Note 5) - 6.3 10 mA 动态特性表:符号参数To (Output) 时滞RL = 2 kW单位CL = 15pF CL = 50 pF最大值最大值最大值最大值tPLH 低到高电平输出传递延迟时间Select to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 2 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Select to Output 3 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 3 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Enable to Output 2 - 24 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 3 - 18 - 27 nstPHL 传递延迟时间Enable to Output 3 - 28 - 40 ns。

电子线路设计-74LS138译码器的介绍

图 3线-8线译码器逻辑图与引脚图

74LS138的功能表

输入

输出

G1

G2A

G2A

c

B

A

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

X

1

1

X

X

X

1

1

1

1

1

1

1

1

0

X

X

X

X

X

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

0

0

1

1

0

1

1

1

1

1

1

1

0

0

0

1

0

1

1

0

1

1

1

1

1

1

0

是CC4514译码输出为高电平有效,而CC4515译码输出为低电平有效。

74LS138译码器的识别与检测

1、识别

2、检测

Thanks

0

0

1

1

1

1

1

0

1

1

1

1

1

0

0

1

0

0

1

1

1

1

0

1

1

1

1

0

0

1

0

1

1

1

1

1

1

0

1

1

1

0

0

74LS138管脚功能的主要 介绍

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

译码器使用

74LS138使用方法译码器 74LS138可以用来驱动8个LED,从功能表上可以看出他的输出只有一个低电平,也就是可以用来用灌电流的方式进行驱动LED,工作电压Vcc=5V,输出可以直接连接LED,没有带来不稳定因素,当然实际中应该串接保护电阻,估计常用的200-300欧姆都可以。

更多功能可以同过使能端来控制效果,在所有的八个等都在闪烁的时候是最好的效果,比用程序控制闪烁要简便的多。

Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6┌┴─┴─┴─┴─┴─┴─┴─┴┐│16 15 14 13 12 11 10 9 │)││ 1 2 3 4 5 6 7 8│└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND应用扩展:8X8点阵驱动。

74LS138可以用来做8X8点阵显示的行驱动。

然后列驱动利用74HC595,可以驱动更大的点阵显示屏。

74LS138级联后可以做16X16点阵的驱动,也就是所谓的4-16译码器。

如下图这样就可以驱动点阵了。

当然也可以使用74LS154,看自己的需要了。

^_^74HC595使用总结发表于2007/11/26 16:37:3074HC595外形图________QB --|1 16|--VccQC --|2 15|--QAQD --|3 14|--SIQE --|4 13|--/GQF --|5 12|--RCKQG --|6 11|--SCKQH --|7 10|--/SCLRGND-|8 9|--QH'|________|74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

QH': 级联输出端。

我将它接下一个595的SI端。

SI: 串行数据输入端。

74595的控制端说明:/SCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SCK(11脚):上升沿时数据寄存器的数据移位。

74ls138功能表

74ls138功能表74LS138是一款集成电路,是一种3-8译码器。

它能够将三位二进制输入转换成八个输出信号,具有广泛的应用领域。

首先,我们来了解一下74LS138的引脚功能。

它有15个引脚,其中包括三个输入引脚A0、A1和A2,八个输出引脚Y0、Y1、Y2、Y3、Y4、Y5、Y6和Y7,以及两个使能引脚E1和E2和一个输出使能引脚G。

引脚功能非常清晰明了,使我们可以简单地通过连接引脚来实现所需的功能。

那么,74LS138的功能是什么呢?它主要用于解码器的设计。

当我们输入三位二进制代码时,它会选择一个输出,并激活相应的输出引脚。

根据输入信号和使能引脚的状态,74LS138可以实现以下功能:1. 3-8译码器: 当使能引脚G为低电平时,无论使能引脚E1和E2的状态如何,74LS138都可以正常工作。

三位二进制代码将决定输出信号的激活状态。

比如,当输入是“000”时,输出引脚Y0将会被激活;当输入是“001”时,输出引脚Y1将会被激活;以此类推。

2. 2-4译码器: 当使能引脚G为低电平,使能引脚E1为高电平,使能引脚E2为低电平时,74LS138将工作为2-4译码器。

此时,只有四个输出引脚Y0、Y1、Y2和Y3会被激活。

根据两位二进制代码的输入信号,激活相应的输出引脚。

3. 输出选择器: 当使能引脚G为高电平,使能引脚E1和E2的状态无关紧要时,74LS138可以应用作为一个简单的八选一选择器。

在这种模式下,只有一个输出引脚被激活,输出引脚的选择由三位二进制代码确定。

值得一提的是,74LS138还具有连接能力,允许多个芯片级联,从而实现更大规模的译码和选择功能。

通过正确地连接多个74LS138芯片,我们可以构建出更为复杂的逻辑功能。

总结起来,74LS138是一款功能强大的集成电路,可以实现3-8译码器、2-4译码器和输出选择器等不同的工作模式。

它被广泛应用在数字电路设计、计算机接口、显示控制等领域。

74LS138的工作原理

74LS138的工作原理

74LS138是一个3-8线译码器/解码器集成电路。

它有3个输入线A0,A1和A2,以及8个输出线Y0-Y7。

其工作原理如下:

1. 输入选择:根据输入线A2、A1和A0的逻辑电平,选择要

激活的输出线。

2. 译码功能:当输入线的逻辑电平满足特定条件时,将激活相应的输出线。

输出线上的逻辑电平取决于电路连接的方式,可以是高电平、低电平或三态(输出线不连接到任何电路)。

3. 解码功能:74LS138还可以作为解码器使用。

在解码模式下,输入线A2、A1和A0信号负逻辑,将会选择并激活一个输出线,其余输出线处于三态。

4. 输出端:输出线Y0-Y7的状态由输入线A2、A1和A0的逻

辑电平决定。

其中,只有一个输出线为低电平,其余输出线为高电平或三态(解码模式下)。

5. 使能端:除了输入线和输出线之外,74LS138还具有使能端(通常标记为G),通过对使能端进行控制,可以控制

74LS138的工作状态。

综上所述,74LS138通过输入选择和译码功能,根据输入信号

的逻辑电平激活特定的输出线,实现3-8线的译码器/解码器

功能。

74LS138管脚功能

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74ls138功能介绍

74ls138引脚图

74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为

低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低

电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反

相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器

用与非门组成的3线-8线译码器74LS138

3线-8线译码器74LS138的功能表

无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出

由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.

5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以

反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

解:由图3.3.8可见,74LS138仅有3个地址输入端。

如果想对4位二进制代码,只能利用一个附加控制端(当中的一个)作为第四个地址输入端。

取第(1)片74LS138的和作为它的第四个地址输入端(同时令),取第(2)片的作为它的第四个地址输入端(同时令),取两片的、、,并将第(1)片的和接至,将第(2)片的接至,如图3.3.9所示,于是得到两片74LS138的输出分别为

图3.3.9 用两片74LS138接成的4线-16线译码器

式(3.3.8)表明时第(1)片74LS138工作而第(2)片74LS138禁止,将的0000~0111这8个代码译成8个低电平信号。

而式(3.3.9)表明时,第(2)片7 4LS138工作,第(1)片74LS138禁止,将的1000~1111这8个代码译成8个低电平信号。

这样就用两个3线-8线译码器扩展成一个4线-16线的译码器

了。

同理,也可一用两个带控制端的4线-16线译码器接成一个5线-32线译码器。

例2.74LS138 3-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。

试画出八个输出引脚的波形。

解:由74LS138的功能表知,当(A为低电平段)译码器不工作,8个输出引脚全为高电平,当(A为高电平段)译码器处于工作状态。

因所以其余7个引脚输出全为高电平,因此可知,在输入信号A的作用下,8个输出引脚的波形如下:

即与A反相;

其余各引脚的输出恒等于1(高电平)与A的波形无关。

74LS138

引脚图

74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,

其工作原理如下:

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为

低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低

电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反

相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,7 4LS138还可作数据分配器。