74LS139及74LS138的应用

74LS139及74LS138的应用

高 位 片 (74LS1 51) E A2 A1 A0 D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D1 0D1 1D1 2D1 3D1 4D1 5 1

A3 A2 A1 A0

数据选择器位扩展的连接图

•

3. 利用数据选择器,当使能端有效时,可将地址输入、 数据输入代替逻辑函数中的变量实现逻辑函数的功能。 例: 试用八选一数据选择器74LS151产生逻辑函数

74LS151 (a) 符号图; (b) 管脚图

7 11 10 9 4 3 2 1 15 14 13 12 E W A0 A1 A2 D 0 74LS151 D 1 D 2 W D 3 D 4 D 5 D 6 D 7 (a) 5 1 16

16

D 3 D 2 D 1 D 0 W W E G N D

V CC

Y ( A B D A BD A B D ABD ) E 0 1 2 3

•

A1

A0

E

1

1

1 & ≥1 E A1 A0 D0

D0

D1

Y

四选一 Y

D2

D1

D2 D3

D3 (a ) (b )

(a) 逻辑图; (b) 符号图

四选一数据选择器的功能表

E

1. 集成数据选择器

74LS151是一种典型的集成数据选择器。74LS151有三个 地址端A2A1A0。可选择D0~D7八个数据,具有两个互补输出 端W 。 W和ຫໍສະໝຸດ Y9Y8 Y7 Y6

Y

5

Y 4 Y 3 Y2 Y1 Y 0

• 由功能表知,Y0输出为Y0= A ,当 A3A2A1A0=0000 3A 2A 1A 0 • 时, 输出Y0=0。它对应的十进制数为0。其余输出依次类推。

译码器的级联应用实验原理

译码器的级联应用实验原理实验目的掌握译码器的级联应用原理,了解其在数字电路中的作用和应用。

实验器材•逻辑设计教学套件•译码器(74LS138)•连线电缆•示波器实验介绍译码器是一种常见的数字逻辑电路元件,用于将输入的数字信号转换为对应的输出信号。

它可以实现逻辑功能的解码和译码,广泛应用于数字电路设计中。

在本实验中,我们将学习译码器的级联应用原理。

级联(Cascade)是指将一个逻辑电路的输出连接到另一个逻辑电路的输入,从而实现多级电路的功能扩展。

通过级联多个译码器,我们可以实现更复杂的逻辑功能和更高的位数解码。

实验步骤1.将74LS138译码器连接至逻辑设计教学套件上。

2.将74LS138的引脚与其他电路元件连接,实现级联应用。

3.使用连线电缆连接逻辑设计教学套件和示波器,以观察电路的输出信号情况。

4.开始输入不同的数字信号观察译码器的输出变化。

5.记录观察结果,并进行分析。

实验结果与分析通过实验观察和记录数据,我们可以得出以下结论: - 译码器的级联应用可以实现更复杂的逻辑功能和更高的位数解码。

- 输入不同的数字信号,译码器的输出信号也会不同,可以实现数字信号的解码。

- 通过示波器的观察,我们可以清楚地看到逻辑电路的输出情况,便于分析和判断。

实验注意事项1.实验时注意正确连接电路,确保电路有稳定的供电和接地。

2.小心操作实验器材,避免损坏。

3.记录实验数据时要详细和准确,便于后续分析和总结。

实验总结通过本实验,我们了解了译码器的级联应用原理,并进行了实际操作和观察。

通过级联多个译码器,我们可以实现更复杂的逻辑功能和更高的位数解码,提供了数字电路设计的灵活性和扩展性。

译码器在数字电路中的应用非常广泛,我们可以将其应用于数据解码、地址解码、显示控制等方面。

掌握了译码器的级联应用原理,对于理解数字电路的设计和工作原理有着重要的意义。

在今后的学习和实践中,我们需要进一步加深对译码器的理解,并结合其他逻辑电路元件进行组合,实现更多复杂的功能。

74ls138功能介绍

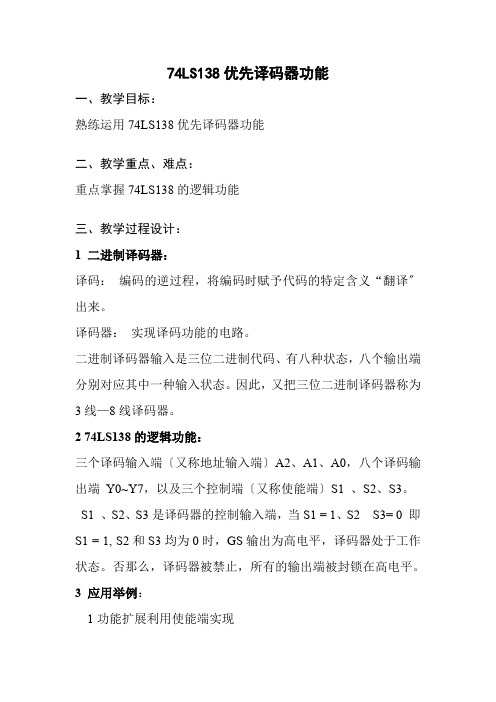

74ls138功能介绍74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

74LS138译码器引脚图逻辑图及功能表

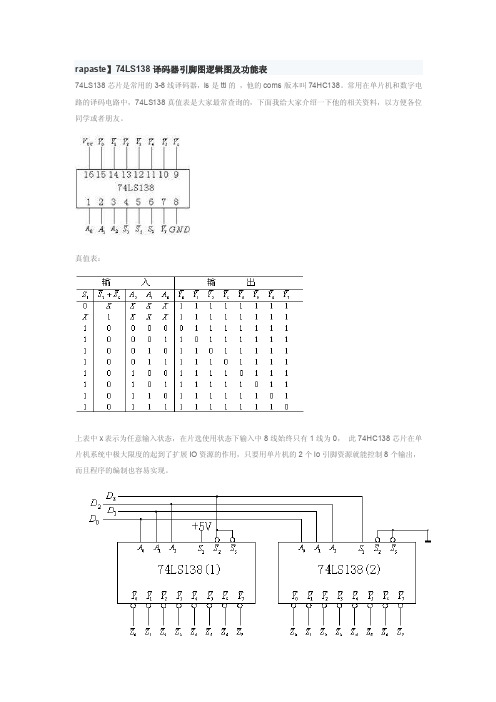

rapaste】74LS138译码器引脚图逻辑图及功能表

74LS138芯片是常用的3-8线译码器,ls是ttl的,他的coms版本叫74HC138。

常用在单片机和数字电路的译码电路中,74LS138真值表是大家最常查询的,下面我给大家介绍一下他的相关资料,以方便各位同学或者朋友。

真值表:

上表中x表示为任意输入状态,在片选使用状态下输入中8线始终只有1线为0,此74HC138芯片在单片机系统中极大限度的起到了扩展IO资源的作用,只要用单片机的2个io引脚资源就能控制8个输出,而且程序的编制也容易实现。

拓展

式(3.3.8)表明时第(1)片74LS138工作而第(2)片74LS138禁止,将的0000~0111这8个代码译成8个低电平信号。

而式(3.3.9)表明时,第(2)片74LS138工作,第(1)片74LS138禁止,将的1000~1111这8个代码译成8个低电平信号。

这样就用两个3线-8线译码器扩展成一个4线-16线的译码器了。

同理,也可一用两个带控制端的4线-16线译码器接成一个5线-32线译码器。

例2.74LS138 3-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。

试画出八个输出引脚的波形

解:由74LS138的功能表知,当(A为低电平段)译码器不工作,8个输出引脚全为高电平,当(A为高电平段)译码器处于工作状态。

因所以其余7个引脚输出全为高电平,因此可知,在输入信号A的作用下,8个输出引脚的波形如下:

即与A反相;

其余各引脚的输出恒等于1(高电平)与A的波形无关。

74LS139中文资料

0.4

II

最大输入电压时输入电流

VCC = Max, VI = 7V

-

-

0.1

mA

IIH

输入高电平电流

VCC = Max, VI = 2.7V

-

-

20

μA

IIL

输入低电平电流

VCC = Max, VI = 0.4V

-

-

-0.36

mA

IOS

输出短路电流

VCC = Max (Note 4)

-20

-

-100

mA

ICC

电源电流

VCC = Max (Note 5)

-

6号

参数

Fro (Input)

To (Output)

RL = 2 kW

单位

CL = 15 pF

CL = 50 pF

Min

Max

Min

Max

tPLH

低到高输出传递延迟时间

Select to Output

-

18

-

27

74LS139中文资料(功能,引脚,真值表及电气参数)

74LS139功能:

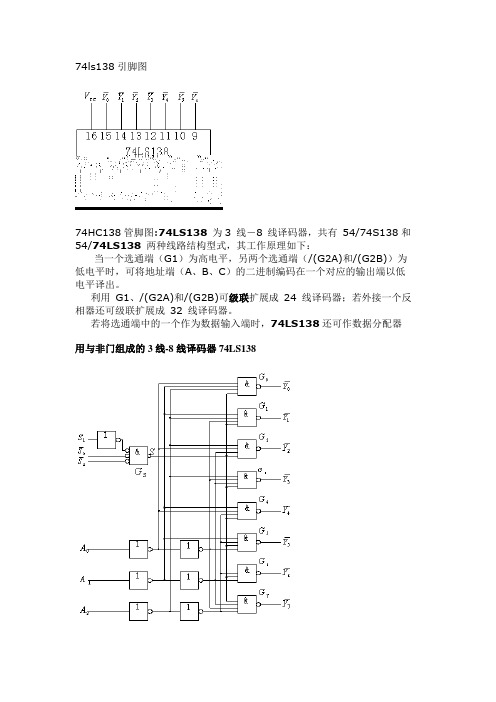

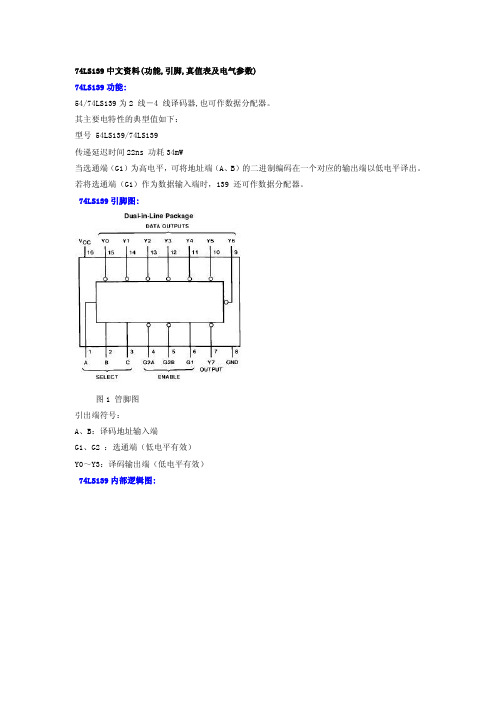

54/74LS139为2线-4线译码器,也可作数据分配器。

其主要电特性的典型值如下:

型号54LS139/74LS139

传递延迟时间22ns功耗34mW

当选通端(G1)为高电平,可将地址端(A、B)的二进制编码在一个对应的输出端以低电平译出。

ns

tPHL

高到低输出传递延迟时间

Select to Output

-

27

-

40

ns

tPLH

低到高输出传递延迟时间

74hc138的应用原理

74HC138的应用原理介绍74HC138是一种三到八线解码器,通常被用于数字电路设计中。

它具有识别三个输入信号,并将其映射到八个输出之一的功能。

本文将介绍74HC138的工作原理及其应用。

工作原理74HC138由三个二输入正逻辑门和一个三输入与非门组成。

它的三个输入(A0,A1和A2)可以表示八个不同的输入组合,输出由Y0到Y7表示。

通过设置三个输入信号中的不同组合,可以选择要激活的输出。

接下来,我们将详细介绍74HC138的应用原理。

使用示例以下是一个使用74HC138的示例电路图:python +—–+ +—–+ A0 —-| |————–| | | 74HC138 Y0 —- | A1 —-| |————–| | + +—–+ + +—–+ A2 —-| | | | | Decoder | | Register | | | | | E1 —-| | | | E2 —-| | | | E3 —-| | | | +————+ +————+ | | | | | 74LS138 | | 74LS175 | | | | | | | | | +————+ +————+ ```在上述电路中,输入A0,A1和A2信号用于选择要激活的输出。

74HC138芯片将输入信号和输出互相连接,并通过输出信号将电流传递到68LS175寄存器芯片。

功能以下是74HC138的功能:1.选择输出信号:通过设置输入A0,A1和A2的不同组合,可以选择激活的输出。

共有八个输出(Y0到Y7)。

2.输入信号:74HC138接收三个输入信号(A0,A1和A2)。

3.解码功能:74HC138将输入信号解码为对应的输出信号。

4.数字电路集成:74HC138是一个数字电路集成芯片,通过一片芯片就能实现数字信号的输入和输出。

应用领域74HC138广泛应用于以下领域:1.数字系统设计:74HC138用于基于数字信号的系统设计,如计算机、电子设备等。

ls138译码器内部电路逻辑图功能表简单应用

74ls138译码器内部电路逻辑图功能表简单应用74HC138:74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用 G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138<74ls138译码器内部电路>3线-8线译码器74LS138的功能表<74ls138功能表>无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出<74ls138逻辑图>由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

实验三 74ls139译码器实验

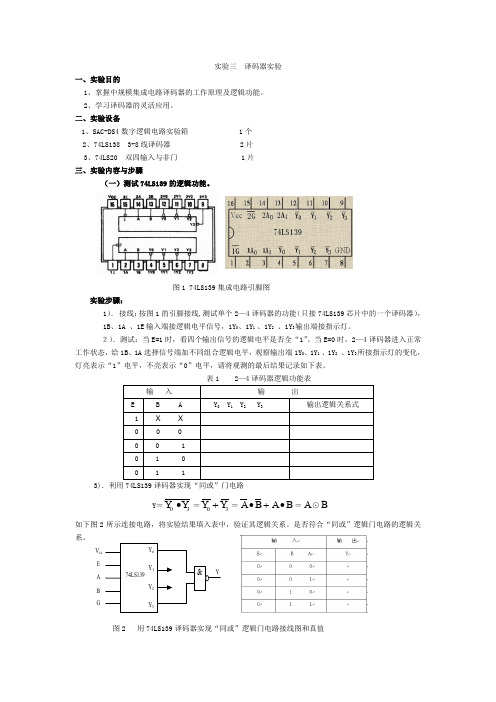

实验三 译码器实验一、实验目的1、掌握中规模集成电路译码器的工作原理及逻辑功能。

2、学习译码器的灵活应用。

二、实验设备1、SAC-DS4数字逻辑电路实验箱1个 2、74LS138 3-8线译码器 2片 3、74LS20 双四输入与非门 1片 三、实验内容与步骤(一)测试74LS139的逻辑功能。

图1 74LS139集成电路引脚图实验步骤:1). 接线:按图1的引脚接线,测试单个2—4译码器的功能(只接74LS139芯片中的一个译码器), 1B 、1A 、1E 输入端接逻辑电平信号,1Y 0、1Y 1 、1Y 2 、1Y 3输出端接指示灯。

2).测试:当E=1时,看四个输出信号的逻辑电平是否全“1”。

当E=0时,2—4译码器进入正常工作状态,给1B 、1A 选择信号端加不同组合逻辑电平,观察输出端1Y 0、1Y 1 、1Y 2 、1Y 3所接指示灯的变化,灯亮表示“1”电平,不亮表示“0”电平,请将观测的最后结果记录如下表。

表1 2—4译码器逻辑功能表3).利用74LS139译码器实现“同或”门电路Y =30Y Y ∙=30Y Y +=B A B A ∙+∙=A ⊙B如下图2所示连接电路,将实验结果填入表中,验证其逻辑关系。

是否符合“同或”逻辑门电路的逻辑关系。

图2 用74LS139译码器实现“同或”逻辑门电路接线图和真值V ccE A B G4).利用74LS139译码器实现“异或”门电路 Y =21Y Y ∙=21Y Y +=B A B A ∙+∙=A ⊕B如下图3所示连接电路,将实验结果填入表中,验证其逻辑关系。

是否符合“异或”逻辑门电路的逻辑关系。

图3 用74LS139译码器实现“异或”逻辑门电路接线图和真值二、用74LS139集成电路将2—4译码器扩展成3—8译码器。

1).接线:扩展的3—8译码器逻辑电路如图3—4所示。

按图3—4连线,A 、B 、C 输入端接实验板电平信号,Y 0 ~Y 72).测试:按真值表4给扩展的3—8译码器输入端送入不同组合的逻辑电平,将输出端显示的逻辑电平填入表中,灯亮表示“1”电平,灯灭表示“0”电平。

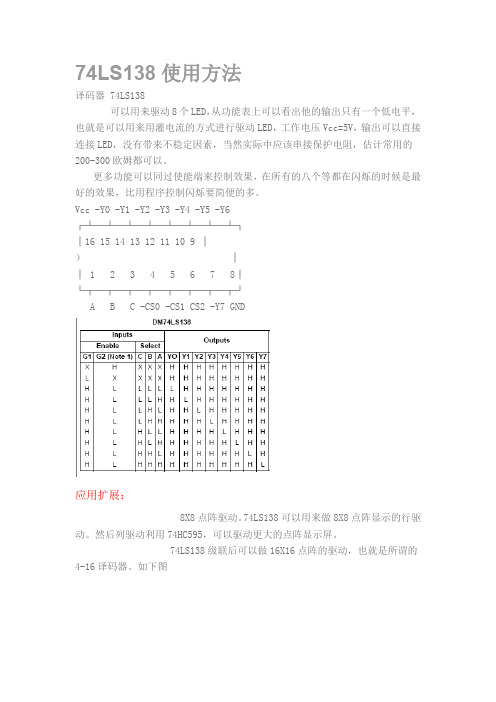

译码器使用

74LS138使用方法译码器 74LS138可以用来驱动8个LED,从功能表上可以看出他的输出只有一个低电平,也就是可以用来用灌电流的方式进行驱动LED,工作电压Vcc=5V,输出可以直接连接LED,没有带来不稳定因素,当然实际中应该串接保护电阻,估计常用的200-300欧姆都可以。

更多功能可以同过使能端来控制效果,在所有的八个等都在闪烁的时候是最好的效果,比用程序控制闪烁要简便的多。

Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6┌┴─┴─┴─┴─┴─┴─┴─┴┐│16 15 14 13 12 11 10 9 │)││ 1 2 3 4 5 6 7 8│└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND应用扩展:8X8点阵驱动。

74LS138可以用来做8X8点阵显示的行驱动。

然后列驱动利用74HC595,可以驱动更大的点阵显示屏。

74LS138级联后可以做16X16点阵的驱动,也就是所谓的4-16译码器。

如下图这样就可以驱动点阵了。

当然也可以使用74LS154,看自己的需要了。

^_^74HC595使用总结发表于2007/11/26 16:37:3074HC595外形图________QB --|1 16|--VccQC --|2 15|--QAQD --|3 14|--SIQE --|4 13|--/GQF --|5 12|--RCKQG --|6 11|--SCKQH --|7 10|--/SCLRGND-|8 9|--QH'|________|74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

QH': 级联输出端。

我将它接下一个595的SI端。

SI: 串行数据输入端。

74595的控制端说明:/SCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SCK(11脚):上升沿时数据寄存器的数据移位。

实验四 集成译码器及其应用

实验四 集成译码器及其应用一、实验目的1、掌握二进制译码器和7段显示译码器的逻辑功能。

2、了解各种译码器之间的差异,能正确选择译码器。

3、熟悉掌握集成译码器的应用方法。

4、掌握集成译码器的扩展方法。

二、实验原理集成译码器是一种具有特定逻辑功能的组合逻辑器件,本实验以3线-8线二进制译码器74LS138为主,通过实验进一步掌握集成译码器。

1.74LS138管脚及功能双排直立式集成3-8译码器74LS138各引脚功能及原理图中惯用画法如图4-1所示。

由功能表可知:(1) 三个使能端(EN EN EN EN 2B 2A 1==0)任何一个无效时,八个译码输出都是无效电平,即输出全为高电平“1”;(2) 三个使能端(EN EN EN EN 2B 2A 1==1)均有效时,译码器八个输出中仅与地址输入对应的一个输出端为有效低电平“0”,其余输出无效电平“1”;(3) 在使能条件下,每个输出都是地址变量的最小项,考虑到输出低电平有效,输出函数可写成最小项的反,即:i i m 2B 2A 1EN EN EN Y =。

2.用74LS138和门电路实现组合电路给定逻辑函数L 可写成最小项之和的标准式,对标准式两次取非即为最小项非的与非,即∏∏= =i iiim yL。

逻辑变量作为译码器地址变量,即可用74LS138和与非门实现逻辑函数L。

3.用译码器实现数据分配将需要传输的数据作为译码器的使能信号,地址变量作为数据输出通道的选择信号,译码器就能实现有选择的输出数据。

三、实验内容1.74LS138功能测试将74LS138输出Y7~Y0接LED0/1指示器,地址A2A1A0输入接0/1开关变量,使能端接固定电平(V CC或地)。

EN1EN2A EN2B≠100时,任意扳动0/1开关,观察LED显示状态,记录之。

EN1EN2A EN2B=100时,按二进制顺序扳动0/1开关,观察LED显示状态,并与功能表对照,记录之。

译码器及数据选择器的应用

译码器及数据选择器的应用一、实验目的1.掌握译码器(74LS138)的逻辑功能和使用方法。

2.掌握数据选择器(74LS151)的逻辑功能和使用方法。

二、实验原理译码器和数据选择器都属于中规模集成电路,中规模集成器件多数是专用的功能器件,具有某种特定的逻辑功能,采用这些功能器件实现组合逻辑函数,基本采用逻辑函数对比法。

在一般情况下,使用译码器和附加的门电路实现多输出逻辑函数较方便,而使用数据选择器实现单输出逻辑函数较方便。

1.译码器一个n 变量的译码器的输出包含了n 变量的所有最小项.例如,如图5.1.4-1是3线/8线译码器 (74LS138) ,有三个选通端1S 、2S 和3S ,只有当1S =1、2S +3S =0时,译码器才被选通,否则,译码器被禁止,所有的输出端被封锁在高电平。

利用选片作用也可以将多片连接起来以扩展译码器的功能。

8个输出包含3个变量的全部最小项的译码。

表5.1.4-1是3线/8线译码器的功能表。

用n 变量译码器加上输出与非门电路,就能获得任何形式的输入变量不大于n 的组合逻辑电路。

图1 74LS138(3线/8线译码器)2.数据选择器一个n 个地址端的数据选择器,具有对2 n 个数据选择的功能。

例如,八选一数据选择器(74LS151),如图2所示,n =3,可完成八选一的功能,见表2。

由真值表可写出:70126012501240123012201210120012D A A A D A A A D A A A D A A A D A A A D A A A D A A A D A A A Y +++++++=数据选择器又称多开路开关,其功能是在多路并行传输数据中选通一路送到输出线上。

图2 74LS151(八选一数据选择器)表5.1.4-2 74LS151功能表三、实验仪器及器材数字实验箱一台,集成芯片74LS00、74LS20、74LS138、74LS151各一块,导线若干。

通信工程设计与监理《74LS138优先译码器功能教案》

74LS138优先译码器功能

一、教学目标:

熟练运用74LS138优先译码器功能

二、教学重点、难点:

重点掌握74LS138的逻辑功能

三、教学过程设计:

1二进制译码器:

译码:编码的逆过程,将编码时赋予代码的特定含义“翻译〞出来。

译码器:实现译码功能的电路。

二进制译码器输入是三位二进制代码、有八种状态,八个输出端分别对应其中一种输入状态。

因此,又把三位二进制译码器称为3线—8线译码器。

274LS138的逻辑功能:

三个译码输入端〔又称地址输入端〕A2、A1、A0,八个译码输出端Y0~Y7,以及三个控制端〔又称使能端〕S1 、S2、S3。

S1 、S2、S3是译码器的控制输入端,当S1 = 1、S2 S3= 0 即S1 = 1, S2和S3均为0时,GS输出为高电平,译码器处于工作状态。

否那么,译码器被禁止,所有的输出端被封锁在高电平。

3应用举例:

1功能扩展利用使能端实现

五、本节小结:

对本节内容进行小结。

74LS138管脚功能的主要 介绍

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

中规模集成电路的应用实验报告

1. 74ls139功能验证基本功能验证:如右图2. 74ls148功能验证基本功能验证:如下图3.用74ls138以及74ls00实现全加器、全减器(1)实验分析:74ls138三个输入对应8个输出,意思就是一个3位的二进制输入对应一个10进制的一位例如ABC输入111那他那边的Y就会输出对应的一个位置如果ABC译码为8那Y里面就有一个位被弄为低电平。

74ls138就是38译码器,是TTL系列的,也就是74系列,有三个输入端A0,A1,A2,其中A2是高位,输出是八个低电平输出Y0 ~ Y7,工作电压一般的5V。

(2)用74ls138、74ls00实现全加器电路图如下:(4)全减器真值表:用74LS138、74LS00实现全减器电路图如下:74ls247验证如右图74ls248验证如下图74ls85验证如下图74ls283将8421码转为余3码(如右图)J1端为输入8421码端。

灯X1、X2、X3、X4分别代表余三循环码的四位高低电平,灯亮代表高电平1,灯灭代表低电平0.(如下图)输入为8421码制的0111时输出为相对应的余三码制的应为1111,结果如下图:1.74LS74加法器(左图)74LS74减法器(左图)74LS112加法器(下图) 74LS112减法器(下图)74ls160:1.用于快速计数的内部超前进位2.用于n 位级联的进位输出3.同步可编程序4.有置数控制线5.二极管箝位输入6.直接清零同步计数74ls160是十进制计数器,也就是说它只能记十个数从0000-1001(0-9)到9之后再来时钟就回到0,首先是clk,这是时钟。

之后是rco,这是输出,MR是复位低电频有效(图上接线前面花圈的都是低电平有效)load是置数信号,当他为低电平时,在始终作用下读入D0到D3。

为了使161正常工作ENP和ENT接1另外D0到D3是置数端Q0到Q3是输出端。

这种同步可预置十进计数器是由四个D型触发器和若干个门电路构成,内部有超前进位,具有计数、置数、禁止、直接(异步)清零等功能。

电子技术基础(数字部分)译码器74LS138功能验证实验[汇编]

![电子技术基础(数字部分)译码器74LS138功能验证实验[汇编]](https://img.taocdn.com/s3/m/2df4b11853ea551810a6f524ccbff121dc36c550.png)

实验二译码器74LS138功能验证实验实验目的:验证译码器74LS138功能;掌握74LS138作为数据分配器时的应用。

实验器材:数字逻辑实验箱一个;数字万用表一个;5V 电源一个;导线若干;(1)验证74LS138的功能:74LS138为3-8译码器,实验原理图如下图所示:实验过程:分别在74LS138的A2、A1、A0、E3、/E2和/E1加上高、低不同的电平,用万用表测量出输出Y 7-Y 0电平,记录下来,验证逻辑关系是否正确测量结果:3+74LS3L 2345678111111191///////V A A //E /G A 74LS+K 3+K 74LS3L输入输出E 3/E2/E1A2A1A/Y0/Y1/Y2/Y3/Y4/Y5/Y6/Y7×××××××××××××××实验结论:当E3输入非高电平时,无论其他输入如何,电路输出都为高电平,即译码器不处于工作状态;只有当E3输入为高电平,/E2和/E1同时为低电平时,译码器才处于工作状态,输出的低电平有效。

(2)验证74LS138作为数据分配器时的功能(设信号从/E1输入,从/Y5输出)。

电路原理如下:实验过程如下:先将K1闭合,测量/E1引脚的电平关态和/Y5引脚的电平状态;再将先将K1断开,测量/E1引脚的电平关态和/Y5引脚的电平状态,没量结果如下:结论: /E1引脚电平关态与/Y5引脚电平状态永远相同,说明接在/E1的信号被分配到/Y5输出。

/E1引脚电压/Y5引脚电压K1闭合时K1断开时74LS3L 2345678111111191///////V A A //E /GA 74LS +3+K +。

74LS139中文资料

图 1 管脚图 引出端符号: A、B:译码地址输入端 G1、G2 :选通端(低电平有效) Y0~Y3:译码输出端(低电平有效) 74LS139 内部逻辑图:

图 2 内部逻辑引脚功能 74LS139 电气参数: 建议操作条件: 符号 VCC VIH VIL IOH IOL TA 参数 电源电压 输入高电平电压 ViH 输入低电平电压 VIL 输出高电平电流 IOH 输出低电平电流 IOL 工作温度 最小值 4.75 2 0 典型值 5 最大值 5.25 0.8 -0.4 8 70 单位 V V V mA mA ℃

74LS139 中文资料(功能,引脚,真值表及电气参数) 74LS139 功能: 54/74LS139 为 2 线-4 线译码器,也可作数据分配器。 其主要电特性的典型值如下: 型号 54LS139/74LS139 传递延迟时间 22ns 功耗 34mW 当选通端(G1)为高电平,可将地址端(A、B)的二进制编码在一个对应的输出端以低电平译出。 若将选通端(G1)作为数据输入端时,139 还可作数据分配器。 74LS139 引脚图:

-

0.35 0.25 -

0.5 V 0.4 0.1 mA

IIH IIL IOS ICC

输入高电平电流 输入低电平电流 输出短路电流 电源电流

VCC = Max, VI = 2.7V VCC = Max, VI = 0.4V VCC = Max (Note 4) VCC = Max (Note 5)

-20 -

6.82Biblioteka -0.36 -100 11μA mA mA mA

动态特性: RL = 2 kW 符号 参数 Fro (Input) To (Output) CL = 15 pF Min tPLH tPHL tPLH tPHL 低到高输出传递延迟时间 高到低输出传递延迟时间 低到高输出传递延迟时间 高到低输出传递延迟时间 Select to Output Select to Output Enable to Output Enable to Output Max 18 27 18 24 CL = 50 pF Min Max 27 40 27 40 ns ns ns ns 单位