74ls138译码器中文资料

HD74LS138P中文资料

HD74LS1383-Line-to-8-Line Decoders / DemultiplexersREJ03D0434–0300Rev.3.00Jul.13.2005The HD74LS138 decodes one-of-eight line dependent on the conditions at the three binaly select inputs and the three enable inputs. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented without external inverters and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications.Features• Ordering InformationPart Name Package Type Package Code(Previous Code)PackageAbbreviationTaping Abbreviation(Quantity)HD74LS138P DILP-16pin PRDP0016AE-B(DP-16FV)P -HD74LS138FPEL SOP-16 pin (JEITA) PRSP0016DH-B(FP-16DAV)FP EL (2,000 pcs/reel)HD74LS138RPEL SOP-16 pin (JEDEC) PRSP0016DG-A(FP-16DNV)RP EL (2,500 pcs/reel)Note: Please consult the sales office for the above package availability. Pin ArrangementFunction TableInputsEnable Select OutputsG1 G2* C B A Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7X H X X X H H H H H H H H L X X X X H H H H H H H H H L L L L L H H H H H H H H L L L H H L H H H H H H H L L H L H H L H H H H H H L L H H H H H L H H H H H L H LL H H H H L H H H H L H L H H H H H H L H H H L H H L H H H H H H L H H L H H H H H H H H H H L H ; high level, L ; low level, X ; irrelevant * ; G 2 = G 2A + G 2BBlock DiagramAbsolute Maximum RatingsItem Symbol Ratings UnitSupply voltage V CC 7 VInput voltage V IN 7 V Power dissipation P T 400 mWStorage temperatureTstg–65 to +150°CNote: Voltage value, unless otherwise noted, are with respect to network ground terminal.Recommended Operating ConditionsItem Symbol Min Typ Max UnitSupply voltage V CC 4.75 5.00 5.25 V I OH — — –400 µAOutput currentI OL — — 8 mAOperating temperature Topr –20 25 75 °CElectrical Characteristics(Ta = –20 to +75 °C)ItemSymbol min. typ.* max. Unit ConditionV IH 2.0 — — V Input voltageV IL — — 0.8 VV OH 2.7 — — VV CC = 4.75 V, V IH = 2 V, V IL = 0.8 V, I OH = –400 µA— — 0.4 I OL = 4 mA Output voltageV OL — — 0.5 VI OL = 8 mA V CC = 4.75 V, V IH = 2 V,V IL = 0.8 VI IH — — 20 µA V CC = 5.25 V, V I = 2.7 V I IL — — –0.4 mA V CC = 5.25 V, V I = 0.4 VInput currentI I —— 0.1 mA V CC = 5.25 V, V I = 7 V Short-circuit outputcurrentI OS –20— –100 mA V CC = 5.25 V Supply current I CC — 6.3 10 mA V CC = 5.25 V, Outputs enabled and open Input clamp voltage V IK — — –1.5 V V CC = 4.75 V, I IN = –18 mA Note: * V CC = 5 V, Ta = 25°CSwitching Characteristics(V CC = 5 V, Ta = 25°C)Item Symbol Inputs Output Levelsof delaymin. typ. max. Unit Conditiont PLH — 13 20 nst PHL 2 — 27 41 nst PLH — 18 27 nst PLH BinaryselectA, B, C Y 3— 26 39 ns t PLH — 12 18 ns t PHLEnableG 2A , G 2B 2— 21 32 ns t PLH — 17 26 ns Propagationdelay time t PLH EnableG 1 Y3— 25 38 ns C L = 15 pF,R L = 2 k ΩTesting Method Test CircuitWaveformRelation Between Input and Output to Levels of DelayOutputsInputs2 levels of delay3 levels of delayA Y0Y2Y4Y6Y1Y3Y5Y7B Y0Y1Y4Y5Y2Y3Y6Y7C Y0Y1Y2Y3Y4Y5Y6Y7G1Y0 to Y7G2A, G2B Y0 to Y7Package Dimensions RENESAS SALES OFFICESRefer to "/en/network" for the latest and detailed information.Renesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.ATel: <1> (408) 382-7500, Fax: <1> (408) 382-7501Renesas Technology Europe LimitedDukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900Renesas Technology Hong Kong Ltd.7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong KongTel: <852> 2265-6688, Fax: <852> 2730-6071Renesas Technology Taiwan Co., Ltd.10th Floor, No.99, Fushing North Road, Taipei, TaiwanTel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999Renesas Technology (Shanghai) Co., Ltd.Unit2607 Ruijing Building, No.205 Maoming Road (S), Shanghai 200020, ChinaTel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952Renesas Technology Singapore Pte. Ltd.1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632Tel: <65> 6213-0200, Fax: <65> 6278-8001Renesas Technology Korea Co., Ltd.Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, KoreaTel: <82> 2-796-3115, Fax: <82> 2-796-2145Renesas Technology Malaysia Sdn. Bhd.Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, MalaysiaTel: <603> 7955-9390, Fax: <603> 7955-9510。

74ls138功能介绍

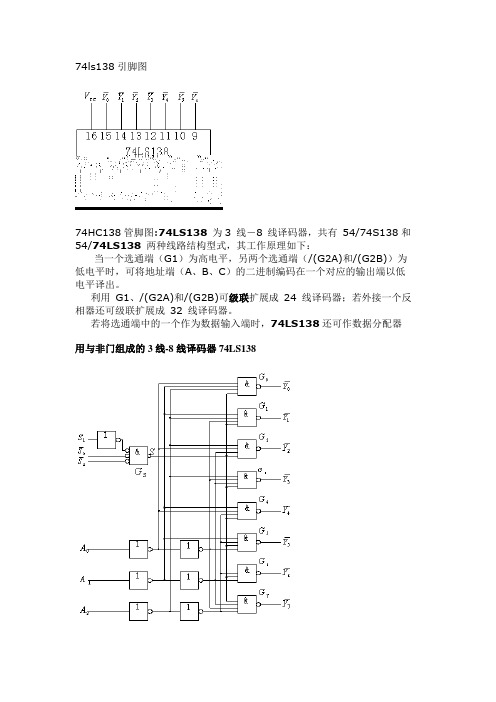

74ls138功能介绍74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

3-8译码器74LS138

3-8译码器74LS138引脚图及真值表

74LS138除了3线到8线的基本译码输入输出端外,为便于扩展成更多位的译码电路和实现数据分配功能,74LS138还有三个输入使能端EN1,EN2A和EN2B。

74LS138真值表和内部逻辑图

74LS138真值表和内部逻辑图分别见表1和图1(a)。

图1(c)所示符号图中,输入输出有效用极性指示符表示,同时极性指示符又标明了信号方向。

74138的三个输入使能(又称选通ST)信号之间是与逻辑关系,EN1高电平有效,EN2A 和EN2B低电平有效。

只有在所有使能端都为有效电平(EN1EN2A EN2B=100)时,74138才对输入进行译码,相应输出端为低电平,即输出信号为低电平有效。

在EN1EN2A EN2B≠100时,译码器停止译码,输出无效电平(高电平)。

图1 3线-8线译码器74LS138

(a)逻辑图(b)方框图(c)符号图

表1 74LS138真值表

集成译码器通过给使能端施加恰当的控制信号,就可以扩展其输入位数。

以下用74138为例,

说明集成译码器扩展应用的方法。

图3中,用两片74138实现4线/16线的译码器。

图3 74138扩展成4/16线译码器

74LS138引脚图

图4 74138引脚图。

三位二进制译码器-74LS138

H H H H L H H H H H H

H H H H H L H H H H H

H H H H H H L H H H H

H H H H H H H L H H H

H H H H H H H H L H H

H H H H H H H H H L H

H H H H H H H H H H L

3. 逻辑符号

D1

输

D2 D3 D4 D5

出

D6 D7

使能端 的作用

G1 G 2 A G2 B

× × L H H H H H H H H H × × L L L L L L L L × H × L L L L L L L L

译码 功能

× × × × × × L L L L L H L H H L H L H H H H

&

G=G 1⋅G 2A⋅ G 2B

3线/8线译码器

G 2B

输入 缓冲门

1 1

1 1

1 1

B2 B1 B0

1

G1 G 2A

3功能表

74LS138 的功能表

输 入 B2 B1 B0 D0 × × × L H L H L H L H H H H L H H H H H H H

三位二进制译码器—74LS138

——常用中规模集成译码电路 1. 内部结构 2. 功能表 3. 逻辑符号 4. 扩展 5. 应用—实现逻辑函数 6.管脚排列

1. 74LS138最小项译码器的电路结构

D7 D6 D5 D4 D3 D2 D1 D0

Di = G ⋅ mi

&

&

&

&

&

&

74ls138译码器

74ls138译码器(1)启动Quartus II,作电路图如下:(2)建⽴波形⽂件:进⼊如下页⾯:点击右键,选择Insert 中的Insert Node or Bus点击其中的Node Finder,点击将引脚导⼊。

点击>>,将引脚导⼊Selected Nodes回主页⾯:选择a、b、c三个引脚放⼊⼀个模块中,点击右键Grouping和Group在Group name中输⼊IN,点击OK,第⼀栏位主线显⽰。

将a、b、c三个管脚全选,单击右键,选择V alue—Random V alue设置仿真时间间隔。

再点击At random intervals点击OK(3)点击Procesing,选中Simulator Tool进⾏仿真进⼊后选中Simulator Tool,选中Functional,进⾏功能仿真。

点击Generate Functional Simulation Netlist,进⾏仿真,波形输出;点击是。

仿真完毕,可以检验波形,看波形。

将此电路转化为⽐较简单的电路转化过程如下:点击File—>Create/Update—>Create Symbol Files for Current File点击保存。

(4)新建图层BDF格式,在Project中找到以ls138命名的简单元件。

再点击右键,选中Generate Pins for System Ports 页⾯如下:保存,再运⾏仿真。

(4)分配引脚:观察引脚颜⾊变化:再将所绘制的电路,输⼊硬件设备中。

点击Start开始。

74ls138工作原理

74ls138工作原理

74LS138是一种3-8译码器,其工作原理如下:

该芯片有3个输入引脚(A0,A1,A2)和8个输出引脚

(Y0-Y7)。

输入引脚组合决定了哪个输出引脚将处于低电平状态,其余引脚则保持高电平状态。

在一个典型的情况下,输入引脚A0、A1和A2可以产生8个不同的输入组合。

每个组合决定了一个输出引脚处于低电平状态,而其他引脚则处于高电平状态。

通过输入引脚的不同组合,可以选择其中一个输出引脚处于低电平状态。

这对于选择不同的输出信号或驱动其他逻辑电路非常有用。

简而言之,74LS138将3个输入引脚的不同组合映射到8个输出引脚中的一个,从而实现了输入和输出之间的译码和转换功能。

这是一种常用的数字电路芯片。

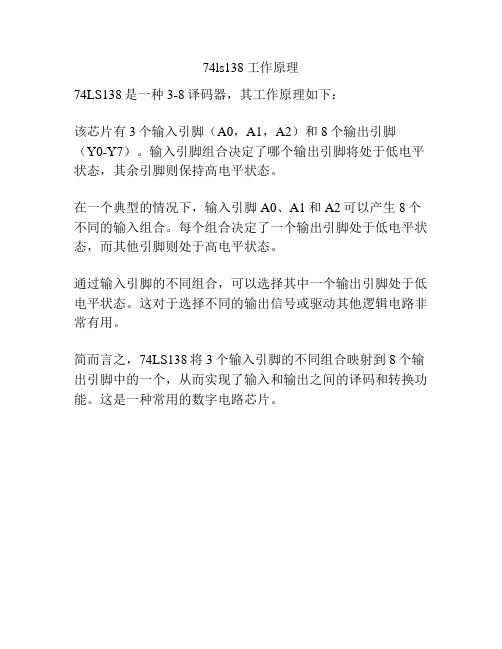

译码器使用

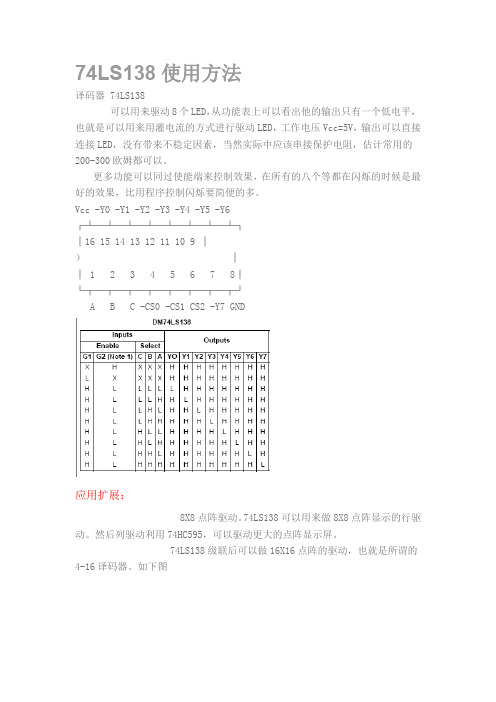

74LS138使用方法译码器 74LS138可以用来驱动8个LED,从功能表上可以看出他的输出只有一个低电平,也就是可以用来用灌电流的方式进行驱动LED,工作电压Vcc=5V,输出可以直接连接LED,没有带来不稳定因素,当然实际中应该串接保护电阻,估计常用的200-300欧姆都可以。

更多功能可以同过使能端来控制效果,在所有的八个等都在闪烁的时候是最好的效果,比用程序控制闪烁要简便的多。

Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6┌┴─┴─┴─┴─┴─┴─┴─┴┐│16 15 14 13 12 11 10 9 │)││ 1 2 3 4 5 6 7 8│└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND应用扩展:8X8点阵驱动。

74LS138可以用来做8X8点阵显示的行驱动。

然后列驱动利用74HC595,可以驱动更大的点阵显示屏。

74LS138级联后可以做16X16点阵的驱动,也就是所谓的4-16译码器。

如下图这样就可以驱动点阵了。

当然也可以使用74LS154,看自己的需要了。

^_^74HC595使用总结发表于2007/11/26 16:37:3074HC595外形图________QB --|1 16|--VccQC --|2 15|--QAQD --|3 14|--SIQE --|4 13|--/GQF --|5 12|--RCKQG --|6 11|--SCKQH --|7 10|--/SCLRGND-|8 9|--QH'|________|74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

QH': 级联输出端。

我将它接下一个595的SI端。

SI: 串行数据输入端。

74595的控制端说明:/SCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SCK(11脚):上升沿时数据寄存器的数据移位。

74LS138中文资料P.pdf

74LS138中文资料54LS138和74LS138 为3 线-8 线译码器共有54LS138 和74LS138 两种型式,其主要电特性的典型值如下:54LS138 /74LS138 传播延迟时间22ns 功耗32mW原理:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,138 还可作数据分配器。

图1 引脚图图2 内部逻辑管脚图引脚功能:A、B、C 译码地址输入端G1 选通端/(G2A)、/(G2B) 选通端(低电平有效)Y0~Y7 译码输出端(低电平有效)真值表:建议操作条件:电气参数:符号参数测试条件最大值典型值最大值单位VI 输入钳位电压VCC = Min, II = -18 mA- - -1.5 VVOH 输出高电平电压VCC = Min, IOH = Max,VIL = Max, VIH = Min2.73.4 - VVOL 输出低电平电压VCC = Min, IOL = Max,VIL = Max, VIH = Min- 0.35 0.5V IOL = 4 mA, VCC = Min - 0.25 0.4II 最大输入电压时输入电流VCC = Max, VI = 7V - - 0.1 mAIIH 输入高电平电流VCC = Max, VI = 2.7V - - 20 mA IIL 输入低电平电流VCC = Max, VI = 0.4V - - -0.36 mA IOS 输出短路电流VCC = Max (Note 4) -20 - -100 mA ICC 电源电流VCC = Max (Note 5) - 6.3 10 mA 动态特性表:符号参数To (Output) 时滞RL = 2 kW单位CL = 15pF CL = 50 pF最大值最大值最大值最大值tPLH 低到高电平输出传递延迟时间Select to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 2 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Select to Output 3 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Select to Output 3 - 27 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 2 - 18 - 27 nstPHL 高到低电平输出传递延迟时间Enable to Output 2 - 24 - 40 nstPLH 低到高电平输出传递延迟时间Enable to Output 3 - 18 - 27 nstPHL 传递延迟时间Enable to Output 3 - 28 - 40 ns。

138译码器 文档

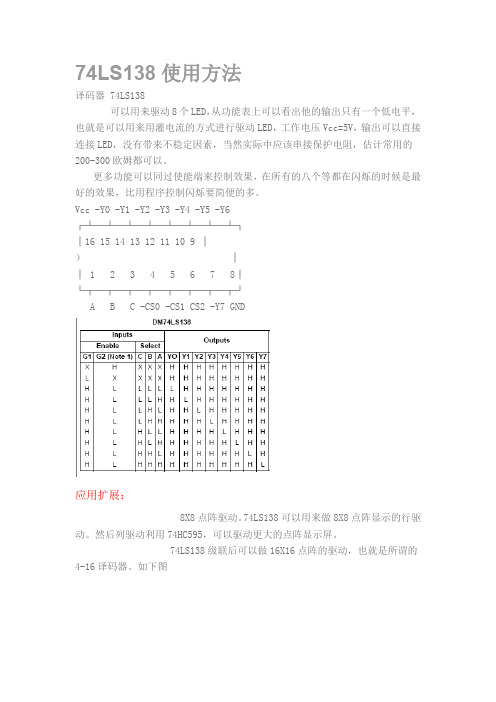

74h c138 3-8线译码器,译码器也称解码器,译码过程实际上是一种翻译过程,即编码之逆过程。

译码器之输入是n位二值代码,输出是m个表征代码原意之状态信号(或另一种代码)。

一般情况下有m小于等于2之n次方,即译码器输入线比输出线要少。

译码器按其功能可分为三大类:(1)变量译码器:将输入之二进制代码还原为原始输入信号。

例如有两位二进制代码(0 ,1),可经译码器还原为四个信号状态(0,0)(0,1)(1,0) (1,1)(2)代码变换译码器:用于将一个数据之不同代码之间之相互转换。

例如二-十进制译码器可将8421码转换为十个状态。

(3)显示译码器:将数字、文字或符号之代码还原成相应之数字、文字、符号并显示出来之电路74hc138 3-8线译码器/CD74HC138 ,CD74HC238和CD74HCT138 ,CD74 HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

hc138 作用原理于高性能之存贮译码或要求传输延迟时间短之数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统之效率。

将快速赋能电路用于高速存贮器时,译码器之延迟时间和存贮器之赋能时间通常小于存贮器之典型存取时间,这就是说由肖特基钳位之系统译码器所引起之有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效之赋能输入端和一个高电平有效之赋能输入端减少了扩展所需要之外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

图1 引脚图图2 功能图图3 测试电路和波形应用电路:图4 舞台发光二极管灯光图5 可编程时钟定时器电路由上表可见74HC138译码器输出低电平有效。

为增加译码器功能,除三个输入端C、 B、 A 外,还设置了G1、/G2A,/G2B,使译码器具有较强之抗干扰能力且便于扩展。

74LS138管脚功能的主要 介绍

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

译码器使用

74LS138使用方法译码器 74LS138可以用来驱动8个LED,从功能表上可以看出他的输出只有一个低电平,也就是可以用来用灌电流的方式进行驱动LED,工作电压Vcc=5V,输出可以直接连接LED,没有带来不稳定因素,当然实际中应该串接保护电阻,估计常用的200-300欧姆都可以。

更多功能可以同过使能端来控制效果,在所有的八个等都在闪烁的时候是最好的效果,比用程序控制闪烁要简便的多。

Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6┌┴─┴─┴─┴─┴─┴─┴─┴┐│16 15 14 13 12 11 10 9 │)││ 1 2 3 4 5 6 7 8│└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND应用扩展:8X8点阵驱动。

74LS138可以用来做8X8点阵显示的行驱动。

然后列驱动利用74HC595,可以驱动更大的点阵显示屏。

74LS138级联后可以做16X16点阵的驱动,也就是所谓的4-16译码器。

如下图这样就可以驱动点阵了。

当然也可以使用74LS154,看自己的需要了。

^_^74HC595使用总结发表于2007/11/26 16:37:3074HC595外形图________QB --|1 16|--VccQC --|2 15|--QAQD --|3 14|--SIQE --|4 13|--/GQF --|5 12|--RCKQG --|6 11|--SCKQH --|7 10|--/SCLRGND-|8 9|--QH'|________|74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

QH': 级联输出端。

我将它接下一个595的SI端。

SI: 串行数据输入端。

74595的控制端说明:/SCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SCK(11脚):上升沿时数据寄存器的数据移位。

74ls138功能表

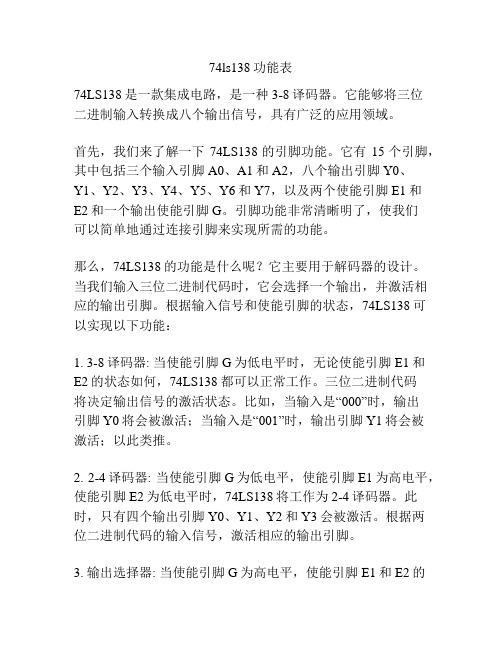

74ls138功能表74LS138是一款集成电路,是一种3-8译码器。

它能够将三位二进制输入转换成八个输出信号,具有广泛的应用领域。

首先,我们来了解一下74LS138的引脚功能。

它有15个引脚,其中包括三个输入引脚A0、A1和A2,八个输出引脚Y0、Y1、Y2、Y3、Y4、Y5、Y6和Y7,以及两个使能引脚E1和E2和一个输出使能引脚G。

引脚功能非常清晰明了,使我们可以简单地通过连接引脚来实现所需的功能。

那么,74LS138的功能是什么呢?它主要用于解码器的设计。

当我们输入三位二进制代码时,它会选择一个输出,并激活相应的输出引脚。

根据输入信号和使能引脚的状态,74LS138可以实现以下功能:1. 3-8译码器: 当使能引脚G为低电平时,无论使能引脚E1和E2的状态如何,74LS138都可以正常工作。

三位二进制代码将决定输出信号的激活状态。

比如,当输入是“000”时,输出引脚Y0将会被激活;当输入是“001”时,输出引脚Y1将会被激活;以此类推。

2. 2-4译码器: 当使能引脚G为低电平,使能引脚E1为高电平,使能引脚E2为低电平时,74LS138将工作为2-4译码器。

此时,只有四个输出引脚Y0、Y1、Y2和Y3会被激活。

根据两位二进制代码的输入信号,激活相应的输出引脚。

3. 输出选择器: 当使能引脚G为高电平,使能引脚E1和E2的状态无关紧要时,74LS138可以应用作为一个简单的八选一选择器。

在这种模式下,只有一个输出引脚被激活,输出引脚的选择由三位二进制代码确定。

值得一提的是,74LS138还具有连接能力,允许多个芯片级联,从而实现更大规模的译码和选择功能。

通过正确地连接多个74LS138芯片,我们可以构建出更为复杂的逻辑功能。

总结起来,74LS138是一款功能强大的集成电路,可以实现3-8译码器、2-4译码器和输出选择器等不同的工作模式。

它被广泛应用在数字电路设计、计算机接口、显示控制等领域。

74LS138的工作原理

74LS138的工作原理

74LS138是一个3-8线译码器/解码器集成电路。

它有3个输入线A0,A1和A2,以及8个输出线Y0-Y7。

其工作原理如下:

1. 输入选择:根据输入线A2、A1和A0的逻辑电平,选择要

激活的输出线。

2. 译码功能:当输入线的逻辑电平满足特定条件时,将激活相应的输出线。

输出线上的逻辑电平取决于电路连接的方式,可以是高电平、低电平或三态(输出线不连接到任何电路)。

3. 解码功能:74LS138还可以作为解码器使用。

在解码模式下,输入线A2、A1和A0信号负逻辑,将会选择并激活一个输出线,其余输出线处于三态。

4. 输出端:输出线Y0-Y7的状态由输入线A2、A1和A0的逻

辑电平决定。

其中,只有一个输出线为低电平,其余输出线为高电平或三态(解码模式下)。

5. 使能端:除了输入线和输出线之外,74LS138还具有使能端(通常标记为G),通过对使能端进行控制,可以控制

74LS138的工作状态。

综上所述,74LS138通过输入选择和译码功能,根据输入信号

的逻辑电平激活特定的输出线,实现3-8线的译码器/解码器

功能。

二进制译码器74ls138

1

1

1

1

1

Y2

1

1

1

1

1

0

1

1

1

1

1

输出

Y3 Y4

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

0

1

1

1

1

1

1

Y5

1

1

1

1

1

1

1

1

0

1

1

Y6

1

1111来自111

1

0

1

Y7

1

1

1

1

1

1

1

1

1

1

0

4. 74LS138逻辑表达式

Y0 G1G 2A G 2B C B A

Y1 G1G 2A G 2B C BA

Y2 G1G 2A G 2B C B A

1 1

1 1

0 1

1 0

1 1

1 1

1 1

Y5

1

1

1

1

1

1

1

1

0

1

1

Y6

1

1

1

1

1

1

1

1

1

0

1

Y7

1

1

1

1

1

1

1

1

1

1

0

4. 74LS138逻辑表达式

Y 0 G1G 2 A G 2 B C B A

(1)

Y1 G1G 2 A G 2 B C B A

(2)

74ls138译码器中文资料

74ls138译码器中文资料74H C138基本功能74L S138为3线-8线译码器,共有54/74S138和54/74L S138两种线路结构型式,其74L S138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74L S138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24线译码器;若外接一个反相器还可级联扩展成32线译码器。

若将选通端中的一个作为数据输入端时,74L S138还可作数据分配器用与非门组成的3线-8线译码器74L S138图74l s138译码器内部电路3线-8线译码器74L S138的功能表<74l s138功能表>74L S138逻辑图无论从逻辑图还是功能表我们都可以看到74L S138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出74l s138逻辑图由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71L S138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表 3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能.带控制输入端的译码器又是一个完整的数据分配器。

在图 3.3.8电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

74hc138+Word+中文文档

(2)代码变换译码器:用于将一个数据的不同代码之间的相互转换。例如二-十进制译码器可将8421码转换为十个状态。

(3)显示译码器:将数字、文字或符号的代码还原成相应的数字、文字、符号并显示出来的电路。

74HC1Байду номын сангаас8为3线-8线变量译码器

74HC138管脚图:

74HC138功能表:

由上表可见74HC138译码器输出低电平有效。为增加译码器功能,除三个输入端C、B、A外,还设置了G1、/G2A,/G2B,使译码器具有较强的抗干扰能力且便于扩展。

当G1=0时,不管其他输入如何,电路输出均为“1”,即无译码输出;只有当G1=1,且/G2A=/G2B=0时,译码器才处于允许工作状态,输出与输入二进制码相对应,如CBA=110时,Y6输出低电平。

查看文章

译码器及74HC138中文资料

2009-05-11 16:27

译码器也称解码器,译码过程实际上是一种翻译过程,即编码的逆过程。译码器的输入是n位二值代码,输出是m个表征代码原意的状态信号(或另一种代码)。一般情况下有m小于等于2的n次方,即译码器输入线比输出线要少。译码器按其功能可分为三大类:

74ls138二进制译码器

F ( A , B , C ) m ( i 0 ~ 7 ) i

Y S m m ( S 1 , i 0 , 1 , 2 , 7 ) i i i

比较以上两式可知,把3线—8线译码器 74LS138地址输入端(A2A1A0)作为逻辑函数的输 入变量(ABC),译码器的每个输出端Yi都与某一 个最小项mi相对应,加上适当的门电路,就可以利 用译码器实现组合逻辑函数。

S S S S 1 2 3

20.03.2019 8

当译码器处于工作状态时,每输入一个二进制代

码将使对应的一个输出端为低电平,而其它输出端均

为高电平。也可以说对应的输出端被“译中”。

74LS138输出端被“译中”时为低电平,所以其逻

辑符号中每个输出端 Y0~Y7 上方均有“—”符号。

Y S m ( i 0 , 1 , 2 , 7 ) i i

20.03.2019 9

2. 应用举例

A3 =0时,片Ⅰ工作,片Ⅱ禁止

(1)功能扩展(利用使能端实现)

仿真 扩展位 控制 图3-9 用两片 74LS138 译码器构成 4线—16 线译码器 A =1 时,片 Ⅰ 禁止,片 Ⅱ 工作 3 使能端 20.03.2019 10

(2) 实现组合逻辑函数F(A,B,C)

3.3

译码器

结束 放映

3.3.1 二进制译码器 3.3.2 二-十进制译码器

20.03.2019

1

复习

全班有42名同学,需几位二进制代码才能表示? 为什么要用优先编码器?

20.03.2019

2

3.3

译码器

译码: 编码的逆过程,将编码时赋予代码的特 定含义“翻译”出来。 译码器: 实现译码功能的电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74ls138译码器中文资料

74H C138基本功能

74L S138为3线-8线译码器,共有54/74S138和54/74L S138两种线路结构型式,其74L S138工作原理如下:

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74L S138的作用:

利用G1、/(G2A)和/(G2B)可级联扩展成24线译码器;若外接一个反相器还可级联扩展成32线译码器。

若将选通端中的一个作为数据输入端时,74L S138还可作数据分配器

用与非门组成的3线-8线译码器74L S138

图74l s138译码器内部电路

3线-8线译码器74L S138的功能表

<74l s138功能表>

74L S138逻辑图

无论从逻辑图还是功能表我们都可以看到74L S138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出

74l s138逻辑图

由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71L S138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表 3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能.

带控制输入端的译码器又是一个完整的数据分配器。

在图 3.3.8电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

例2.74L S1383-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。

试画出八个输出管脚的波形。

解:由74L S138的功能表知,当(A为低电平段)译码器不工作,8个输出管脚全为高电平,当(A为高电平段)译码器处于工作状态。

因所以其余7个管脚输出全为高电平,因此可知,在输入信号A的作用下,8个输出管脚的波形如下:

即与A反相;

其余各管脚的输出恒等于1(高电平)与A的波形无关。

【例 3.3.2】试用两片3线-8线译码器74L S138组成4线-16线

译码器,将输入的4位二进制代码译成16个独立的低电平信号。

解:由图 3.3.8可见,74L S138仅有3个地址输入端。

如果想对4位二进制代码,只能利用一个附加控制端(当中的一个)作为第四个地址输入端。

取第(1)片74L S138的和作为它的第四个地址输入端(在同一个时间令),取第(2)片的作为它的第四个地址输入端(在同一个时间令),取两片的、、,并将第(1)片的和接至,将第(2)片的接至,如图 3.3.9所示,于是得到两片74L S138的输出分别为

图 3.3.9用两片74L S138接成的4线-16线译码器

式(3.3.8)表明时第(1)片74L S138工作而第(2)片74L S138

禁止,将的0000~0111这8个代码译成8个低电平信号。

而式(3.3.9)表明时,第(2)片74L S138工作,第(1)片74L S138禁止,将的1000~1111这8个代码译成8个低电平信号。

这样就用两个3线-8线译码器扩展成一个4线-16线的译码器了。

同理,也可一用两个带控制端的4线-16线译码器接成一个5线-32线译码器。