P2020处理器的存储映射

华为存储RAID2.0技术细节

存储阵列

Pool 0

Pool 1 …..…

Pool N

离

Pool示意图

HUAWEI TECHNOLOGIES CO., LTD.

Huawei Confidential

Page 5

Huawei Enterprise A Better Way

Pool

Pool即存储池,由存储阵列中多 个硬盘组成,硬盘可选择SSD、 SAS、NL-SAS中的一种或者多种 。 存储系统可划分为多个Pool,每 个Pool分别服务于不同的应用, 整个存储系统也可只有一个Pool 不同Pool之间故障和管理相互隔

Page 14

HUAWEI TECHNOLOGIES CO., LTD.

Huawei Confidential

Huawei Enterprise A Better Way

Copyright© 2012 Huawei Technologies Co., Ltd. All Rights Reserved. The information in this document may contain predictive statements including, without limitation, statements regarding the future financial and operating results, future product portfolio, new technology, etc. There are a number of factors that could cause actual results and developments to differ materially from those expressed or implied in the predictive statements. Therefore, such information is provided for reference purpose only and constitutes neither an offer nor an acceptance. Huawei may change the information at any time without notice.

基于多核处理器P2020的综合数据处理模块设计及应用

核 心部 分。 reclP w rC 系列产品是一种广泛应用于工业 、 Fesae o e P 通信 、 军事领域 的处理 器。 本文研 究了 Fesa recl e P w rC新 多核处理 器 P 00的特点 ,主要 介绍 了基于此处理 器平 台的综合数据处理模块设计 ,研究其在 实际 o eP 22

A bsr c : I tg ae ib r edaa ta s s i n d vc sa v tlp r o e v o i y t m .I ro m sm a y t a t n e r td ar o t n miso e ie i i a tofm d m a i n c s se n r a tpef r n f ci n u h a ln e a al a i g b sd t e o d n ,a d o a d v d o c mp e s d d t e o dn n u y t m un to ss c spa n d d t o d n , u a ar c r i g u i n i e o r s e aar c r ig a d s bs se s fw a e la ig,ec I t g ae aa p o e sn o u e i h o e o e ie r e c l we P p o u t a e o t r o dn t . n e rt d d t r c si g m d l st e c r ft d v c .F e s ae Po r C r d csh v he wi e a pl ain i n u ty o m u iai n a d m i tr r c s o .Th spa e d n i e h h r ce it s o e d p i t n i d sr ,c m c o n c to n l ay p o e s r i i p ri e tf st e c a a trsi fn w i c F e s ae P we PC r e c l o r mul — o e p o e s rP 0 0 a d i to u e h e in ofi tg a e a ap o e sng m o u eb s d t c r r c so 2 2 n n d c ste d sg e i r n r td d t r c s i d l a e o i r c so lto m swela t p ia in i r cie nt sp o e s rp af r a l sisa pl t np a tc . h c o

华为p20

华为p20

华为P20是华为公司于2018年3月27日在法国巴黎发布的一

款手机。

该手机采用了后置双摄像头,由莱卡镜头提供支持,主摄像头为1200万像素,副摄像头为200万像素。

前置摄像

头为2400万像素,支持人脸识别解锁。

华为P20搭载了海思

麒麟970芯片,配备了6GB RAM和128GB的存储空间。

手

机采用了全新的3D玻璃机身设计,搭配纹理镀膜和镜面处理

工艺,提供了黑色、蓝色、粉红金、金色和翡翠绿等多种颜色可供选择。

华为P20的屏幕为5.8英寸FHD+全面屏,分辨率

为2244x1080像素。

手机搭载了3400mAh的电池,支持快充

技术。

华为P20还加入了智能语音助手HiVoice和语音识别技术。

手机操作系统为EMUI 8.1,基于Android 8.1版本。

此外,华为P20还支持人脸解锁和指纹解锁两种解锁方式,并拥有

IP53级防水和防尘功能。

飞思卡尔推出QorIQ通信平台 首款八核微处理器行业最高标准

产业技术I NDUSTRY TECH飞思卡尔推出Q o r I Q通信平台 首款八核微处理器行业最高标准■飞思卡尔半导体公司 飞思卡尔半导体推出Qo rIQ P4080多核处理器,一个旨在为嵌入式多核空间中的性能、功效和编程性设定新标准的非常先进的八核通信处理器。

P4080多核处理器是飞思卡尔新QorIQ平台的标志性成员,基于45nm处理技术。

它集成了增强的P o wer A rchit ect ure内核、三级缓存分层、创新C o reNet片上结构和数据路径加速,可在最大30W的功率电路内提供卓著性能。

Qor IQ P4080能够并行处理控制平面、数据平面和应用层的处理任务,它非常适合于联网、电信、工业、军事和航天领域的一些应用,如交换机、企业和服务提供商路由器、接入和媒体网关、基站控制器、无线网络控制器(RNC)和通用嵌入式计算系统。

实现卓越性能的架构要点P4080S o C内置8个增强型P o wer A rchit ect ure e500mc内核,目标直指1.5GHz的最高频率。

每个内核都有其自己的专用128KB L2后端缓存,并能够接入2MB共享前端L3缓存。

完全的处理器独立性(包括启动和重置各单个e500mc内核的能力)是该器件最显著的特征。

内核可以作为8个对称多处理(SMP)内核或8个完全不对称多处理(A MP)内核,也可以SMP和A MP组的组合且以不同程度的独立性进行运行。

此外,内核还能够运行不同操作系统(OS)或者在无OS情况下运行,为用户提供了在控制、数据路径和应用处理间进行分区的极大灵活性。

整体性能通过数据路径加速架构(D PA A)得以增强,而D PAA同时又提供高联网性能,降低了软件复杂性。

该加速架构与内核一起,管理分组路由、安全、服务质量和深度分组检测,让内核把注意力集中到增值服务和应用处理上来。

由于消除了其他多核方法中常见的一些与共享总线/共享存储器架构有关的总线争夺、瓶颈和延迟问题, C oreNet结构因此也提高了性能。

在P2020平台下使用串口更新Bootrom

在P2020平台下使用串口更新Bootrom周加谊;蒲永材;李中【摘要】针对传统情况下更新bootrom需要取下存储芯片编程,频繁操作会对主板底座造成伤害问题,论文提出了一种在P2020平台下启动vxWorks系统后使用串口在线更新bootrom的方法.定义了一套基于串口的通信传输协议,为保障数据在传输过程中完整性和正确性,在传输过程中采取了校验和重传机制.最后文章介绍了flash烧写的具体实现过程.测试结果显示,该方法具有可靠性高和成功率高的特性.【期刊名称】《机电产品开发与创新》【年(卷),期】2017(030)005【总页数】3页(P92-94)【关键词】P2020;串口;在线烧写;vxWorks;bootrom【作者】周加谊;蒲永材;李中【作者单位】中国兵器装备集团自动化研究所武器装备信息与控制研发中心,四川绵阳621000;中国兵器装备集团自动化研究所武器装备信息与控制研发中心,四川绵阳621000;中国兵器装备集团自动化研究所武器装备信息与控制研发中心,四川绵阳621000【正文语种】中文【中图分类】TN914;N随着嵌入式系统的快速发展,其中VxWorks系统凭借其良好的可持续性、高性能的内核等优点越来越受到人们的关注。

由于该系统的强实时性、高稳定性以及内核的可裁剪性已经使其广泛应用于通讯、船舶、航空等实时性要求特别高的领域中[1]。

Bootrom是基于vxWorks[2]定制的一套类似于uboot的bootloader[3],主要功能是初始化硬件和引导vxWorks操作系统。

P2020由飞思卡尔公司研发一款可实现单线程极高性能功耗比的处理器,适用于联网、电信、军事以及工业领域的各种应用[4]。

针对传统更新bootrom存在的这些问题,本文提出了使用串口的方式更新bootrom,该方法在启动vxWorks系统后使用串口在线更新,而不需要拆卸任何硬件装置。

本方案我们采用型号为am29f040的nor flash存放bootrom引导文件,容量为512KB。

P89LPC901_902_903中文数据完整手册

3. 定购信息......................................................................................................................................5 3.1 定购选择..............................................................................................................................5

4. 功能框图......................................................................................................................................6 5. 管脚信息......................................................................................................................................7 5.1 管脚配置................................................................................................................................7 5.2 管脚描述................................................................................................................................8 6. 逻辑符号.................................................................................................................................... 11 7. 特殊功能寄存器........................................................................................................................12 8.功能描述......................................................................................................................................20 8.1 增强型 CPU.........................................................................................................................20 8.2 时钟......................................................................................................................................20 8.2.1 时钟定义 .......................................................................................................................20 8.2.2 CPU 时钟(OSCCLK) .................................................................................................21 8.2.3 低频振荡器选项(P89LPC901) ...............................................................................21 8.2.4 中频振荡器选项(P89LPC901) ................................................................................21 8.2.5 高频振荡器选项(P89LPC901) ................................................................................21 8.2.6 时钟输出(P89LPC901) ...........................................................................................21 8.3 片内 RC 振荡器选项 ..........................................................................................................21 8.4 看门狗振荡器选项 ..............................................................................................................22 8.5 外部时钟输入选项(P89LPC901)........................................................................................22 8.6 CPU 时钟(CCLK)唤醒延迟 ...........................................................................................23 8.7 CPU 时钟(CCLK)调整:DIVM 寄存器 .....................................................................23 8.8 低功耗选择 ..........................................................................................................................23 8.9 存储器结构 ..........................................................................................................................23 8.10 数据 RAM 的分配...........................................................................................................23 8.11 中断 ....................................................................................................................................23 8.11.1 外部中断输入 .............................................................................................................24 8.12 I/O 口 ................................................................................................................................25 8.12.1 I/O 口配置 ................................................................................................................25 8.12.2 准双向口输出配置 .....................................................................................................25 8.12.3 开漏输出配置 .............................................................................................................26

基于P2020的嵌入式主控单元的硬件开发

基于P2020的嵌入式主控单元的硬件开发作者:牛利民来源:《科教导刊·电子版》2019年第17期摘要:本文提出了基于P2020的嵌入式主控单元的硬件设计方案,对主控单元的工作原理进行了说明并对主要模块进行了介绍。

该模块已经在实际项目中应用,结果表明该板卡能力突出,工作稳定。

关键词主控单元 P2020 启动配置嵌入式主控单元主要功能是承载Vxworks操作系统,主控软件,并负责对业务板卡、信道板卡、交换板卡等其他板卡进行配置、数据交换,以及人机接口,外部接口进行交互功能等。

该主控单元具有集成度高、处理能力强、功耗低、扩展性好、环境适应性强等优点,基本功能框图见图1,其中CPU以飞思卡尔的P2020NXE2KFC为核心处理器;内存选用4片256MB /片DDR3 SDRAM;Flash选用64MB Nor FLASH(存放boot程序、操作系统)和16GB Nand FLASH(存放应用程序);千兆以太网物理层控制芯选用两片88E1111,其中一路作为调试网口,一路经母板接交换板;显示控制部分由Xilinx Spartan6 FPGA 、显示控制芯片GPUS1D13513构成;外围接口部分包括串口扩展芯片、两路千兆以太网通过CPCI高速接插件经母板接其他板卡。

1 P2020简介P2020采用45nm工艺,适用于联网、电信、军事以及工业领域中的各种应用,最高可实现1.2 GHz双核工作主频。

P2020主要特点有:双核高性能Power Architecture e500核心,36位物理寻址,800 MHz至1.2 GHz时钟频率;三个10/100/1000 Mbps增強型三速以太网控制器,支持RGMII、SGMII接口;支持64位DDR2/DDR3 SDRAM存储器控制器。

2 P2020的Local Bus与外设互联Local Bus总线一般采用数据/地址线复用的形式,使用时需要将总线的数据和地址分离出来再分别接到目标器件的数据和地址端口,需要通过 Buffer 起来来进行驱动和隔离,通过用信号锁存器SN74ALVCH16373 来分离总线中的数据和地址。

华为p20pro参数

华为p20pro参数

华为P20 Pro作为华为旗下的旗舰手机,拥有一系列令人称赞的参数。

首先是其外观设计,P20 Pro采用了2.5D玻璃背板和金属中框的组合,给人一种高端、时尚的感觉。

配备了6.1英寸的OLED全面屏,分辨率为1080x2240像素,显示效果出色。

在性能方面,华为P20 Pro搭载了麒麟970处理器,采用了独有的神经网络处理单元(NPU)和双ISP图像信号处理器,提供强大的计算和图像处理能力。

它采用6GB的RAM和128GB 的存储空间,支持存储卡扩展。

P20 Pro的拍照能力是其最大的亮点之一。

它配备了一颗4000万像素的Leica三摄像头,包括一颗RGB彩色镜头、一颗单色镜头和一颗长焦镜头。

这些镜头的配合使得P20 Pro在照片质量方面表现出色,能够拍摄出细节丰富、色彩鲜艳的照片。

此外,P20 Pro还具备5倍混合变焦和具有光学防抖功能的引擎4.0,确保用户能够拍摄出稳定和清晰的照片。

在其他方面,华为P20 Pro支持IP67级别的防尘防水,配备了一颗光线传感器和颜色温度传感器,能够根据环境自动调整屏幕亮度和色温。

它还搭载了4000mAh的电池,支持华为SuperCharge快充技术,可以快速充电。

此外,P20 Pro还支持人脸识别和指纹识别等安全解锁方式,运行EMUI 8.1基于Android 8.1系统。

总之,华为P20 Pro以其出色的外观设计、强大的性能以及卓越的拍照能力吸引了众多消费者的目光。

它是一款令人满意的旗舰手机。

PowerPC QorIQ P2020处理器介绍v1.1

测试例程列表:

CAN 总线通讯测试 FlexRay 总线通讯测试 Norflash 文件系统读写测试 Nandflash 文件系统读写测试 SATA 硬盘文件系统读写测试 USB 读写测试 网络通讯测试 串口通讯测试 I2C 读写测试 SPI 读写测试 Localbus 读写、中断测试 GPIO 测试 RTC 时钟测试 温度监控

和更少的竞争;

P2020 处理器应用领域:

工业控制应用 以太网交换机 军工/航空/航天 医疗电子 测试测量仪器 单板计算机 机器人 电力监控

如何快速进行基于 PowerPC 平台的应用开发:

当用户需要快速进行应用系统开发时,核心板+底板的方式可以帮助用户节省开发时间 和费用。

所谓核心板是指一种集成了嵌入式系统核心功能的电路板,通常包括中央处理器、 存 储器、电源管理芯片、晶振等相关元器件。

10) 集成安全引擎,协议支持包括 SNOW、ARC4、3DES、AES、RSA/ECC、RNG、单通道 SSL/TLS、Kasumi、XOR 加速。

QorIQ P2020 处理器优势

Freescale 半导体的 PowerPC P2020 处理器是可靠性嵌入式应用的理想基础平台。

1、 P2020 处理器集成丰富 I/O 接口,这就使得需要更低系统级 BOM 成本,减少桥路 芯片使用,高集成度缩短研发周期,降低生产成本和功耗;

板载 1GB SLC Nand FLASH; 2 路 10/100/1000M 以太网接口; 2 路串口(RS232),3 线 TTL; 1 路 USB2.0 Host 接口; 2 路 2x I²C, max. 400 kHz; 1 路 SD 卡接口,支持 4 位/8 位数据宽度; 1 路 SPI 接口,支持 4 个片选; 高速总线接口(可配置): 3 路 PCIe1.0 接口,其中 2 路(x1) ,1 路(x2); 2 路 Serial Rapid I/O (SRIO) (仅 P20xx); 2 路光纤网络接口; 1 路增强型的 Local Bus, max. 66 MHz

实验2.13存储器重映射

第一个循环结束之后,继续点击单步运 行 ,进行第二个循环,将“55”改成了“AA”。

依次点击单步运行,可以清楚看到,观 察窗中表内数据“55”依次被更改为“AA”。

第二个循环结束后,进入MEMMAP=0(二进 制00)模式,即Boot Block(引导块)模式。如图 所示是观察窗Tab1中的数据。

如上图所示为Tab2中的数据,是0x7fffe000之后一段地 址的上的数据,对比Tab1中的数据,不难发现0x7FFFE000

~0x7FFFE030与0x00000000~0x00000030上的数据是相同

的。

对实验结果的分析

实验开始执行程序,首先进入的是用户片内RAM模式, 即MEMMAP=2(二进制10),此模式下,将存储器重映 射到片内RAM 上。 即将0x00000000~0x0000003F中的数

ARM比较复杂。ARM芯片与普通单片机在存储器地址方面的 不同在于:ARM芯片中有些物理存储单元的地址可以根据设置变换。 就是说一个物理存储单元现在对应一个地址,经过设置以后,这个存

储单元就对应了另外一个地址了。下图是随意举了个例子(不要与 ARM芯片对应),旨在说明地址重映射的过程。下图表示把 0x00000000地址上的存储单元映射到新的地址0x00000007上。 CPU存取0x00000007就是存取0x00000000上的物理存储单元。

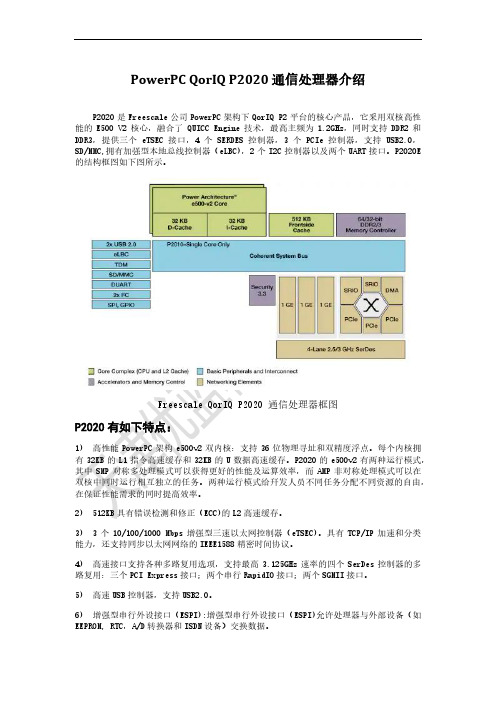

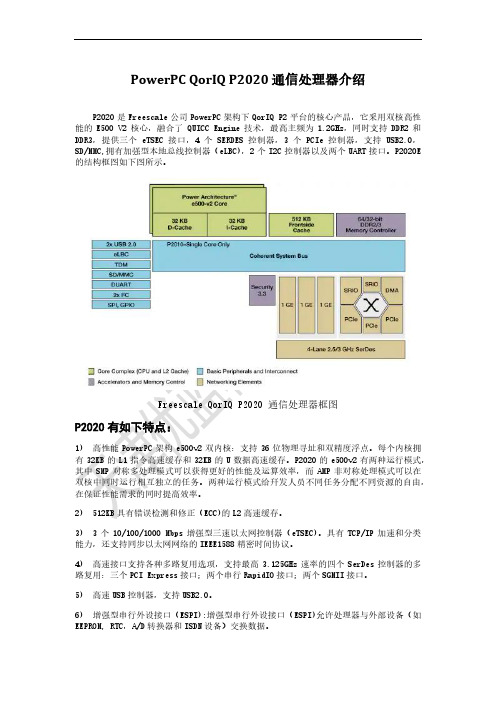

PowerPC QorIQ P2020处理器介绍v1.1

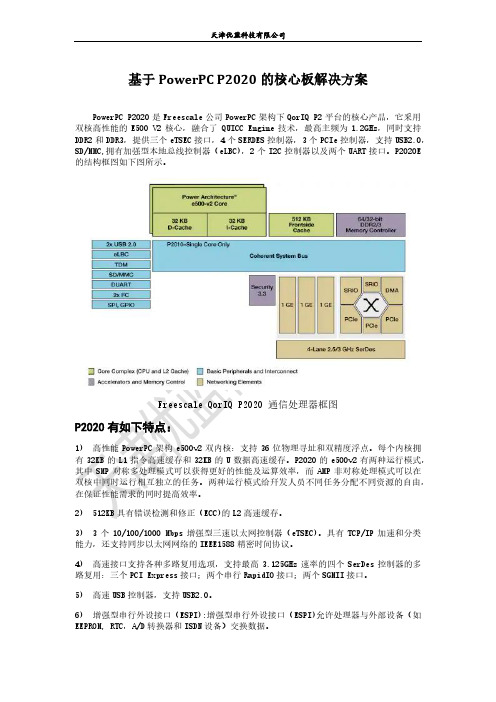

P2020 是 Freescale 公司 PowerPC 架构下 QorIQ P2 平台的核心产品,它釆用双核高性 能的 E500 V2 核心,融合了 QUICC Engine 技术,最高主频为 1.2GHz,同时支持 DDR2 和 DDR3,提供三个 eTSEC 接口,4 个 SERDES 控制器,3 个 PCIe 控制器,支持 USB2.0, SD/MMC,拥有加强型本地总线控制器(eLBC),2 个 I2C 控制器以及两个 UART 接口。P2020E 的结构框图如下图所示。

26 位地址,16 位数据,4 个片选,4 个外部中断 10 路 PPC GPIO,12 路灵活的扩展 GPIO; 支持 RTC,温度监控,看门狗,JTAG 接口; Uboot 引导 VxWorks/linux 操作系统镜像,调试过程更方便;

其他技术指标

供电指标: 电源输入:DC +5V(+/-5%) 功耗 <= 8W

Freescale QorIQ P2020 通信处理器框图

P2020 有如下特点:

1) 高性能 PowerPC 架构 e500v2 双内核:支持 36 位物理寻址和双精度浮点。每个内核拥 有 32KB 的 L1 指令高速缓存和 32KB 的 U 数据高速缓存。P2020 的 e500v2 有两种运行模式, 其中 SMP 对称多处理模式可以获得更好的性能及运算效率,而 AMP 非对称处理模式可以在 双核中同时运行相互独立的任务。两种运行模式给幵发人员不同任务分配不同资源的自由, 在保证性能需求的同时提高效率。 2) 512KB 具有错误检测和修正(ECC)的 L2 高速缓存。 3) 3 个 10/100/1000 Mbps 增强型三速以太网控制器(eTSEC)。具有 TCP/IP 加速和分类 能力,还支持同步以太网网络的 IEEE1588 精密时间协议。 4) 高速接口支持各种多路复用选项,支持最高 3.125GHz 速率的四个 SerDes 控制器的多 路复用:三个 PCI Express 接口;两个串行 RapidIO 接口;两个 SGMII 接口。 5) 高速 USB 控制器,支持 USB2.0。 6) 增强型串行外设接口(ESPI):增强型串行外设接口(ESPI)允许处理器与外部设备(如 EEPROM, RTC,A/D 转换器和 ISDN 设备)交换数据。

P2020与eMMC的机载嵌入式数据存储模块设计

2 硬件实现

嵌入式数据存储板安装在某型号机载电子设备 中,主 要完成两大功能:通过多种机载数据总线与其他机载 设 备 进行数据传输;完成各种机载数据的存储和读取。机 载 嵌 入式数据存 储 板 主 要 由 P2020 处 理 器、eMMC 芯 片、FPGA、多种机 载 数 据 总 线 接 口 电 路 (包 含 IEEE1394B 接 口 卡、ARINC429、MIL STD 1553B、RS422 总 线 接 口 电 路)组成,数据 存 储 板 总 体 框 图 如 图 2 所 示。P2020 作 为 板卡内的主控处理 器,负 责 控 制 管 理 其 他 功 能 电 路,并 实 现对eMMC 的读写访问;eMMC 芯片作为存储介 质,主 要 用于存储各种机载数据;机载数据总线接口电路主要 与 其 他机载设备进行数据传输;FPGA 负责完 成 数 据 处 理 和 接 口转换。

eSDHC 控制器 是 P2020 处 理 器 连 接 eMMC 芯 片 的 接 口控制器,支持 MMC4.2标准协议。eSDHC 控制器支 持全速/高速两种工作 模 式,高 速 模 式 下 接 口 时 钟 最 高 可 达 52 MHz,支 持 1/4/8 位 三 种 位 宽 的 数 据 传 输 模 式 。eS-

DHC 控制器接口电平支持3.3V、2.5V 和1.8V。

1.2 eMMC 芯片的特点

eMMC(embedded MultiMediaCard)即“嵌 入 式 多 媒 体存储 卡 ”,是 MMC 协 会 订 立 的 嵌 入 式 存 储 器 标 准 规 范[2]。eMMC 芯 片 在 一 个 小 型 BGA 封 装 里 集 成 了 MMC 接口、NANDFlash 控 制 器 以 及 NAND Flash 存 储 介 质。 eMMC 芯片架构如图1所示。

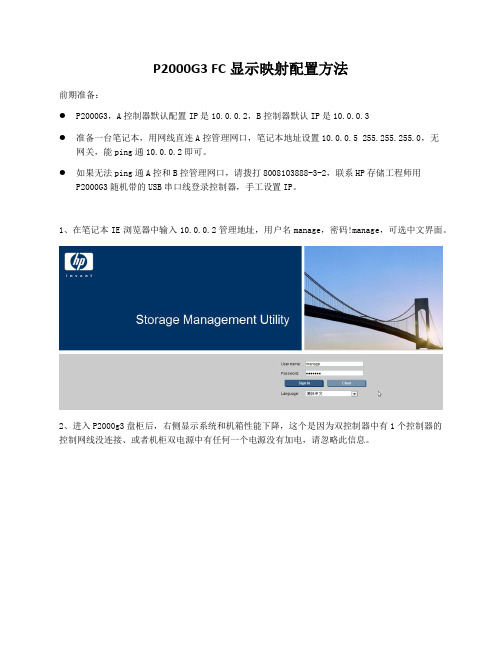

HPP2000G3 FC显示映射配置方法

P2000G3 FC显示映射配置方法前期准备:●P2000G3,A控制器默认配置IP是10.0.0.2,B控制器默认IP是10.0.0.3●准备一台笔记本,用网线直连A控管理网口,笔记本地址设置10.0.0.5 255.255.255.0,无网关,能ping通10.0.0.2即可。

●如果无法ping通A控和B控管理网口,请拨打8008103888-3-2,联系HP存储工程师用P2000G3随机带的USB串口线登录控制器,手工设置IP。

1、在笔记本IE浏览器中输入10.0.0.2管理地址,用户名manage,密码!manage,可选中文界面。

2、进入P2000g3盘柜后,右侧显示系统和机箱性能下降,这个是因为双控制器中有1个控制器的控制网线没连接、或者机柜双电源中有任何一个电源没有加电,请忽略此信息。

3、如果交换机和服务器都已经启动,那么在左侧主机中,可以看到所有在同一个zone中的服务器光纤卡的WWN号码。

(Qlogic卡按Ctrl+Q,Emulex卡用Alt+E键进入,确认卡的WWN号码)4、开始配置,左侧选择P2000G3 FC,右侧设置菜单中选择创建虚拟磁盘。

5、虚拟磁盘默认名字vd01,设置RAID级别(例如raid5),块大小默认,指定给自动。

6、界面往下拉,把所有硬盘都打勾选中,点“创建虚拟磁盘”。

7、创建虚拟磁盘成功。

8、点中创建好的虚拟磁盘vd01,右侧设置菜单中选择创建卷。

9、创建第一个卷的名字,指定卷大小,然后界面向下拉。

10、看到映射选项默认是打勾开启的,这里做的是默认映射,比较适合服务器和盘柜直连的情况,如果我们通过光纤交换机连接,这种映射方法不适合,因此去掉映射右侧的对勾。

11、去掉映射旁边的勾后,后面板视图消失,直接点应用。

12、同理点中vd01,右侧还是在设置中选择创建卷,来建立第二个卷。

13、同样,输入第二个卷的名字和大小。

14、同样,取消映射旁边的勾,点应用。

15、然后再同样创建第三个卷,输入卷名称和大小。

基于PowerPC P2020的核心板解决方案

天津优蓝科技有限公司

使用核心板的好处:

样机成型速度快,根据应用复杂度,一般 1~2 个月可以完成样机基本功能; 开发难度低, 无需开发 CPU 及其高速外围器件,只需关注底板电源及通信接口; 节省重新开发成本,同款核心板,可以多款产品使用;

和更少的竞争;

P2020 处理器应用领域:

工业控制应用 以太网交换机 军工/航空/航天 医疗电子 测试测量仪器 单板计算机 机器人 电力监控

如何快速进行基于 PowerPC 平台的应用开发:

当用户需要快速进行应用系统开发时,核心板+底板的方式可以帮助用户节省开发时间 和费用。

所谓核心板是指一种集成了嵌入式系统核心功能的电路板,通常包括中央处理器、 存 储器、电源管理芯片、晶振等相关元器件。

协助开发: • (*免费)底板原理图检查 • (*免费)底板协助调试 • (*免费)资料永久更新

增值服务:

主板定制设计 核心板定制设计 嵌入式软件开发 国产化器件设计 帮助客户实现快速样机试产

天津优蓝科技有限公司

优蓝科技有丰富的外设接口卡设计经验和技术积累,在以下多个方 面具有成熟技术储备,可配合 PowerPC 平台进行相关项目的一站式设 计:

Freescale QorIQ P2020 通信处理器框图

P2020 有如下特点:

1) 高性能 PowerPC 架构 e500v2 双内核:支持 36 位物理寻址和双精度浮点。每个内核拥 有 32KB 的 L1 指令高速缓存和 32KB 的 U 数据高速缓存。P2020 的 e500v2 有两种运行模式, 其中 SMP 对称多处理模式可以获得更好的性能及运算效率,而 AMP 非对称处理模式可以在 双核中同时运行相互独立的任务。两种运行模式给幵发人员不同任务分配不同资源的自由, 在保证性能需求的同时提高效率。 2) 512KB 具有错误检测和修正(ECC)的 L2 高速缓存。 3) 3 个 10/100/1000 Mbps 增强型三速以太网控制器(eTSEC)。具有 TCP/IP 加速和分类 能力,还支持同步以太网网络的 IEEE1588 精密时间协议。 4) 高速接口支持各种多路复用选项,支持最高 3.125GHz 速率的四个 SerDes 控制器的多 路复用:三个 PCI Express 接口;两个串行 RapidIO 接口;两个 SGMII 接口。 5) 高速 USB 控制器,支持 USB2.0。 6) 增强型串行外设接口(ESPI):增强型串行外设接口(ESPI)允许处理器与外部设备(如 EEPROM, RTC,A/D 转换器和 ISDN 设备)交换数据。

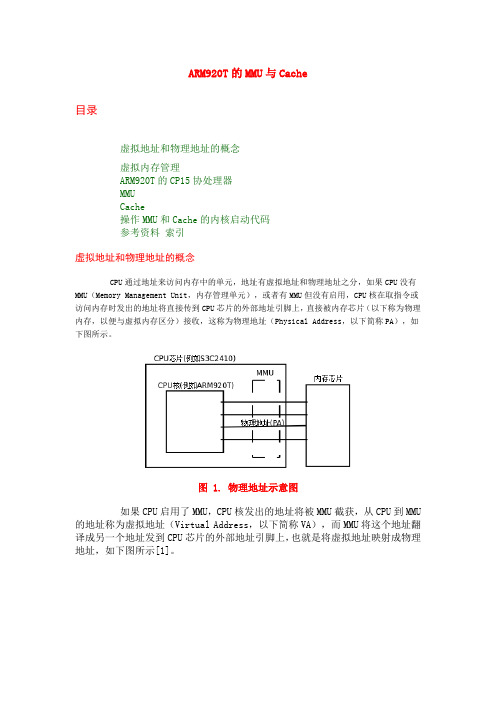

ARM处理器CACHE详解

ARM920T的MMU与Cache目录虚拟地址和物理地址的概念虚拟内存管理ARM920T的CP15协处理器MMUCache操作MMU和Cache的内核启动代码参考资料索引虚拟地址和物理地址的概念CPU通过地址来访问内存中的单元,地址有虚拟地址和物理地址之分,如果CPU没有MMU (Memory Management Unit,内存管理单元),或者有MMU但没有启用,CPU核在取指令或访问内存时发出的地址将直接传到CPU芯片的外部地址引脚上,直接被内存芯片(以下称为物理内存,以便与虚拟内存区分)接收,这称为物理地址(Physical Address,以下简称PA),如下图所示。

图 1. 物理地址示意图如果CPU启用了MMU,CPU核发出的地址将被MMU截获,从CPU到MMU的地址称为虚拟地址(Virtual Address,以下简称VA),而MMU将这个地址翻译成另一个地址发到CPU芯片的外部地址引脚上,也就是将虚拟地址映射成物理地址,如下图所示[1]。

图 2. 虚拟地址示意图MMU将虚拟地址映射到物理地址是以页(Page)为单位的,对于32位CPU 通常一页为4K。

例如,虚拟地址0xb700 1000~0xb700 1fff是一个页,可能被MMU映射到物理地址0x2000~0x2fff,物理内存中的一个物理页面也称为一个页框(Page Frame)。

虚拟内存管理现代操作系统充分利用MMU提供的VA到PA的映射机制来做内存管理,以下称为虚拟内存管理(Virtual Memory Management)。

首先看下面的例子:例 1. 进程的地址空间这是bash进程的虚拟地址空间,32位CPU的虚拟地址空间是4GB,也就是0x0000 0000-0xffff ffff,该进程占用的地址范围近似为0x0000 0000-0xbfff ffff,地址范围0xc000 0000-0xffff ffff由内核占用,用户进程不允许访问。

BR8220 芯片数据手册 v1.01

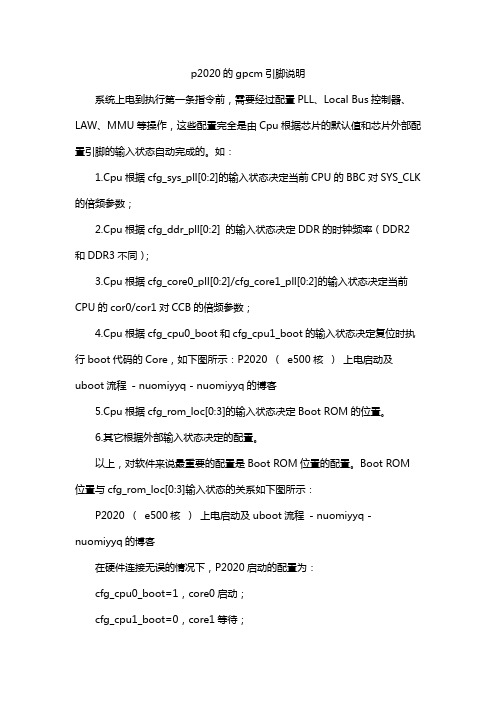

p2020的gpcm引脚说明

p2020的gpcm引脚说明系统上电到执行第一条指令前,需要经过配置PLL、Local Bus控制器、LAW、MMU等操作,这些配置完全是由Cpu根据芯片的默认值和芯片外部配置引脚的输入状态自动完成的。

如:1.Cpu根据cfg_sys_pll[0:2]的输入状态决定当前CPU的BBC对SYS_CLK 的倍频参数;2.Cpu根据cfg_ddr_pll[0:2] 的输入状态决定DDR的时钟频率(DDR2和DDR3不同);3.Cpu根据cfg_core0_pll[0:2]/cfg_core1_pll[0:2]的输入状态决定当前CPU的cor0/cor1对CCB的倍频参数;4.Cpu根据cfg_cpu0_boot和cfg_cpu1_boot的输入状态决定复位时执行boot代码的Core,如下图所示:P2020 (e500核)上电启动及uboot流程- nuomiyyq - nuomiyyq的博客5.Cpu根据cfg_rom_loc[0:3]的输入状态决定Boot ROM的位置。

6.其它根据外部输入状态决定的配置。

以上,对软件来说最重要的配置是Boot ROM位置的配置。

Boot ROM 位置与cfg_rom_loc[0:3]输入状态的关系如下图所示:P2020 (e500核)上电启动及uboot流程- nuomiyyq - nuomiyyq的博客在硬件连接无误的情况下,P2020启动的配置为:cfg_cpu0_boot=1,core0启动;cfg_cpu1_boot=0,core1等待;cfg_rom_loc[0:3] =1110,从Local bus GPCM—16-bit ROM启动;根据P2020的硬件手册,Cpu复位后执行的第一条指令的地址是0xFFFF,FFFC。

因此,Cpu要能正确执行U-boot代码,至少需要下面几个条件:Local Access Window能正确转换U-boot代码的物理地址空间Local Bus Control能正确转换U-boot代码的物理地址空间MMU能正确转换U-boot代码的有效地址空间(e500核的MMU无法关闭)首先,根据P2020手册,Local Access Window对Boot ROM的地址转换,不通过LAW寄存器配置。

基于VxWorks系统下P2020的PCIE转PCI接口设计

电子设计工程Electronic Design Engineering第29卷Vol.29第7期No.72021年4月Apr.2021收稿日期:2020-03-27稿件编号:202003206作者简介:王琪(1992—),男,江苏盐城人,助理工程师。

研究方向:嵌入式系统设计开发。

随着PCIE 总线技术的广泛应用,采用高速差分串行的方式进行数据传输,具有高带宽、高可靠性、高拓展性等优点[1],其很好地弥补了PCI 、PCI-X 总线的不足。

但许多应用场景依然需要适配原有的PCI 设备,尤其在航天航空系统中设备更新速度慢,兼容性要求高,该现象更为突出[2]。

为了兼容PCIE 总线与PCI 设备,推动了一系列PCIE 转PCI 桥芯片的发展[3-5]。

PowerPC 架构处理器在嵌入式系统上表现非常优秀,其具备良好的处理性能和丰富的通信接口,在航天航空系统中广泛应用。

该方案采用FreeScale 公司的P2020双核嵌入式处理器,该处理器内置两个最高频率可达1.2GHz 的e500v2内核,支持64KB 的L1Cache ,支持512KB 的L2Cache ,支持32/64-bit DDR2/DDR3,具有三路1000/100/10Mb/s 以太网控制器,三路高速PCIE 控制器,两路串行RapidIO 控制器。

PCIE-PCI 转换桥基于VxWorks 系统下P2020的PCIE 转PCI 接口设计王琪,邓佳伟,张梅娟(中国电子科技集团公司第五十八研究所,江苏无锡214062)摘要:基于VxWorks 嵌入式实时操作系统和PEX8112桥芯片,设计了一种应用于P2020处理器的PCIE 转PCI 的接口方案,有效解决了航天航空系统中P2020处理器的PCIE 控制器与PCI 设备的适配问题。

方案结合P2020处理器和PEX8112桥片的特点,详细阐述了P2020处理器的PCIE 转PCI 的接口方案硬件框架设计和基于VxWorks 嵌入式实时操作系统中VxBus 框架的软件开发设计。

当前待映射的扇区数

当前待映射的扇区数概述当前待映射的扇区数是指在存储设备中等待被映射的扇区的数量。

扇区是存储设备中最小的存储单位,通常为512字节。

当操作系统或应用程序需要读取或写入数据时,会使用扇区作为数据的最小单位,因此扇区的映射对于存储设备的性能和效率至关重要。

在存储设备中,扇区映射是通过文件系统或逻辑转换方式实现的。

文件系统负责将文件数据映射到实际的扇区上,并提供访问接口供操作系统或应用程序使用。

而逻辑转换方式则是通过磁盘控制器等硬件设备对扇区进行逻辑映射,使操作系统无需关心实际的物理扇区位置。

扇区映射的作用扇区映射对于存储设备的性能和数据完整性至关重要。

以下是扇区映射的主要作用:1. 数据访问效率通过扇区映射,存储设备可以将文件数据分散存储在不连续的扇区中。

这种分散存储的方式可以提高存储设备的数据利用率,避免了数据连续存储导致的大量空闲空间。

同时,存储设备可以根据实际读写需求,优化数据的物理位置,提高访问效率,减少寻道时间。

2. 数据保护和完整性扇区映射可以实现数据的冗余存储,提高数据的可靠性和完整性。

通过在存储设备中存储多个副本或奇偶校验信息,当某个扇区损坏或丢失时,可以通过其他副本或校验信息进行修复或恢复。

3. 空间管理和回收通过扇区映射,存储设备可以更好地管理空闲扇区,并进行回收和再利用。

当文件被删除或修改时,存储设备可以将相应的扇区标记为空闲状态,以便其他文件可以使用这些空闲扇区存储数据。

扇区映射算法扇区映射算法决定了文件数据在存储设备中的具体存储位置。

常见的扇区映射算法有以下几种:1. 直接映射直接映射是最简单的扇区映射算法,每个文件数据直接映射到存储设备的一个扇区。

这种映射方式简单高效,但可能导致存储设备中存在大量的空闲扇区。

2. 按块映射按块映射是将多个连续的扇区作为一个数据块,每个文件数据映射到一个或多个数据块。

这种映射方式可以减少存储设备中的空闲扇区数量,提高数据利用率和访问效率。

3. 链接映射链接映射是通过链表将文件数据映射到存储设备中的不连续扇区。

华为P20相机竟然还有这个隐藏神技能,速来学习!

华为P20相机竟然还有这个隐藏神技能,速来学习!华为P20系列主打拍照,超级优秀的夜拍、神级手持防抖、多种AI场景识别等等都是P20系列的招牌。

对于喜欢玩拍照的花粉来说,P20系列是不二之选,P20相机支持保存RAW格式文件,这个文件是什么,它又藏在什么地方呢?一、RAW格式文件是什么RAW图像是CMOS或者CCD图像感应器将捕捉到的光源信号转化为数字信号的原始数据。

RAW文件是一种记录了数码相机传感器的原始信息,同时记录了由相机拍摄所产生的一些元数据(Metadata,如ISO的设置、快门速度、光圈值、白平衡等)的文件。

RAW是未经处理、也未经压缩的格式,可以把RAW概念化为“原始图像编码数据”或更形象的称为“数字底片”。

二、RAW格式文件优势是什么★RAW格式是数码相机的专用格式,是真正意义上的“电子底片”。

RAW格式也是体现数码影像极致质量的唯一的格式。

★RAW文件并没有白平衡设置,但是真实的数据也没有被改变,就是说作者可以任意的调整色温和白平衡,并且是不会有图像质量损失的。

★颜色线性化和滤波器行列变换在具有微处理器的电脑上处理得更加迅速,这允许应用一些相机上所不允许采用的、较为复杂的运算法则。

★虽然RAW文件附有饱和度、对比度等标记信息,但是其真实的图像数据并没有改变。

用户可以自由地对某一张图片进行个性化的调整,而不必基于一、两种预先设定好的模式。

★RAW最大的优点就是可以将其转化为16位的图像。

也就是有65536个层次可以被调整,这对于JPG文件来说是一个很大的优势。

当编辑一个图像的时候,特别是当你需要对阴影区或高光区进行重要调整的时候,这一点非常重要。

三、P20要怎么样才能得到RAW文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本文简要表述P2020处理器的存储映射:

P2020处理器的存储空间映射关系总体如下:

...

其中E500V2内核的MMU单元负责将有效地址转换为虚拟地址,最终转换为物理地址,之后通过12个LAW寄存器来分配整个物理地址空间,在LAW寄存器中指定外设接口存储空间的类型和大小。

1、为什么要采用EA、VA、PA这种映射关系?

EA:在程序中能够直接使用的地址,E500内核的有效地址为32位,E500内核的EA由有效地址页表索引EPN和地址偏移Offset两部分组成。

在支持多进程的操作系统中,每个进程使用的虚拟空间独立,此时需要使用处理器提供的MMU将各个进程使用的地址空间进行有效隔离。

32位处理器能够访问的最大物理地址空间仅为4GB,然而在有些操作系统汇总,如Linux系统,每一个进程都拥有3GB虚拟地址空间。

因此一个多进程操作系统中使用的虚拟地址空间一般都大于4GB。

为此操作系统必须采取某种转换机制建立虚拟地址空间与实际物理空间的映射。

处理器的MMU为系统软件设立了转换查找表以支持虚实地址的映射。

在这些查找表中将规定虚实地址的对应关系及访问控制等一系列信息。

系统软件将利用处理器提供的查找表完成虚实地址的映射。