Verilog带符号数运算

verilog参数除法

verilog参数除法在Verilog中,如果你想要实现参数化的除法,可以使用/运算符,并将除数和被除数作为参数传递给模块。

下面是一个简单的例子:module Divider #(parameter WIDTH = 8) (input logic signed [WIDTH-1:0] numerator,input logic signed [WIDTH-1:0] denominator,output logic signed [WIDTH-1:0] quotient);assign quotient = numerator / denominator;endmodule在这个例子中,WIDTH是一个参数,用于指定被除数、除数和商的位宽。

这个模块执行带符号整数除法,并将结果赋给输出端口quotient。

你可以实例化这个模块并通过参数传递被除数和除数,如下所示:module TestDivider;logic signed [7:0] numerator;logic signed [7:0] denominator;logic signed [7:0] result;// Instantiate Divider module with WIDTH = 8Divider #(8) uut (.numerator(numerator),.denominator(denominator),.quotient(result));// Rest of your testbench code goes here...endmodule在这个例子中,我们使用Divider #(8)来实例化Divider模块,将numerator、denominator和result作为输入和输出端口连接。

请注意,实例化时通过#(8)指定了参数WIDTH的值。

这只是一个简单的例子,具体实现取决于你的需求和设计规模。

如果有其他特定的要求,请提供更多细节,我将尽力提供更具体的帮助。

verilog 符号数的数值赋值

verilog 符号数的数值赋值概述:Verilog是一种硬件描述语言,用于设计数字系统。

在设计数字系统时,我们通常需要使用一些符号来表示各种元件和信号。

这些符号可以是有向图、行为模型或数据流模型。

在设计过程中,我们需要为这些符号分配具体的数值,以便于进行仿真和分析。

数值赋值的基本概念在Verilog中,我们可以使用assign语句为符号分配具体的数值。

assign语句的基本形式如下:assign symbol = value;其中,symbol是一个符号,value是一个具体的数值。

例如,我们可以在模块内部定义一个信号,并为其分配一个具体的数值:module example;reg a;always @*begina = 1'b0;endendmodule在这个例子中,我们定义了一个名为a的reg型信号,并在always块中为其分配了一个具体的数值1'b0。

这个数值是一个二进制数,其中第一个位为0。

数值赋值的其他方式除了使用assign语句为符号分配数值外,我们还可以使用其他方式来实现数值赋值。

例如,我们可以使用==>运算符来实现数值赋值:module example;reg a;always @*beginif (some_condition)a = 1'b0;endendmodule在这个例子中,我们使用==>运算符为a信号分配了一个具体的数值。

当some_condition为真时,a信号被赋值为1'b0。

结论总之,在Verilog中,我们可以使用assign语句或==>运算符为符号分配具体的数值。

通过为符号分配具体的数值,我们可以进行仿真和分析,从而更好地理解数字系统的工作原理。

在实际设计中,我们需要根据具体的需求和场景选择合适的数值赋值方式。

verilog运算符

verilog运算符verilog运算符是一种用来完成特定计算功能的符号。

1. 逻辑运算符:* 非(!):对输入的变量求反,即~。

* 与(&):如果两个输入均为1,则输出1,否则输出0。

* 或(|):如果两个输入中有任意一个为1,则输出1,否则输出0。

* 异或(^):如果两个输入不同,则输出1,否则输出0。

* 相等(==):如果两个输入均相等,则输出1,否则输出0。

* 不等(!=):如果两个输入不同,则输出1,否则输出0。

2. 移位运算符:* 左移(<<):将变量的比特位向左移动指定的位数,低位补0。

* 右移(>>):将变量的比特位向右移动指定的位数,高位补0。

3. 三元运算符:* 条件运算符(?:):根据条件表达式的值,来确定返回哪个变量的值。

4. 比较运算符:* 小于(<):如果左侧变量值小于右侧变量值,则输出1,否则输出0。

* 小于等于(<=):如果左侧变量值小于等于右侧变量值,则输出1,否则输出0。

* 大于(>):如果左侧变量值大于右侧变量值,则输出1,否则输出0。

* 大于等于(>=):如果左侧变量值大于等于右侧变量值,则输出1,否则输出0。

Verilog运算符是用来定义Verilog语言或其他类似语言复杂表达式的符号,它可以在复杂业务场景中有效地描述关系。

Verilog运算符可以分为几类,其中逻辑运算符包括非(!)、与(&)、或(|)、异或(^)、相等(==)和不等(!=)等,移位运算符有左移(<<)和右移(>>),三元运算符则只有条件运算符(?:),比较运算符则可以分为小于(<)、小于等于(<=)、大于(>)和大于等于(>=)。

各种运算符的应用可以实现复杂的计算功能,方便程序员们快速进行编码特定功能实现。

verilog有符号数和无符号数乘法运算

verilog有符号数和无符号数乘法运算Verilog有符号数和无符号数乘法运算在Verilog中,有符号数和无符号数乘法运算是非常重要的概念。

它们在数字电路设计和硬件描述语言中起着至关重要的作用。

在本文中,我们将深入探讨有符号数和无符号数乘法运算的原理、应用和区别,以便读者深入理解这一主题。

1. 有符号数和无符号数的定义在Verilog中,有符号数和无符号数是两种不同的数据类型。

无符号数是指仅由非负数组成的数字,而有符号数是指包含正负号的数字。

在硬件设计中,我们经常会遇到这两种类型的数据,并需要对它们进行不同的处理。

2. 有符号数和无符号数的乘法原理在Verilog中,有符号数和无符号数的乘法运算原理是有所不同的。

对于无符号数,乘法运算可以直接按照普通的乘法规则进行,即将两个数相乘得到结果。

而对于有符号数,由于需要考虑正负号的影响,乘法运算则需要根据补码或原码进行相应的转换和处理。

3. 有符号数和无符号数乘法运算的应用在数字电路设计中,有符号数和无符号数的乘法运算被广泛应用于各种计算单元和逻辑电路中。

它们可以用于实现乘法器、数据处理器和信号处理器等功能模块,为数字系统的运算提供强大的支持。

4. 有符号数和无符号数乘法运算的区别有符号数和无符号数的乘法运算在应用上有一些明显的区别。

在进行乘法运算时,需要考虑有符号数的溢出和符号位的处理,而无符号数则不需要。

在逻辑电路设计中,有符号数和无符号数的乘法运算通常需要采用不同的电路结构和算法来实现。

5. 个人观点和理解在我看来,有符号数和无符号数的乘法运算是数字电路设计中非常重要的问题。

它们不仅涉及到硬件描述语言的应用,也涉及到数字系统的实际运算。

深入理解和掌握有符号数和无符号数乘法运算的原理和实现方法,对于提高数字电路设计的水平和能力是非常有益的。

总结回顾通过本文的探讨,我们对Verilog中有符号数和无符号数乘法运算有了更深入的理解。

我们深入分析了它们的原理、应用和区别,也分享了个人的观点和理解。

verilog中有符号数减法运算

Verilog中有符号数减法运算1. 引言在数字电路设计中,符号数减法运算是一项基本的运算操作。

在Verilog语言中,对有符号数进行减法运算涉及到了多种方法和技巧。

本文将介绍Verilog中有符号数减法运算的一般原理、方法和注意事项,以便读者能够更好地理解和运用Verilog语言进行相关的数字电路设计和实现。

2. 有符号数的表示方法在Verilog语言中,有符号数通常使用补码形式进行表示。

在补码中,最高位表示符号位,0为正数,1为负数。

对于N位有符号数,其取值范围为-2^(N-1)到2^(N-1)-1。

3. 有符号数的减法运算原理有符号数的减法运算可以简化为加法运算。

对于两个有符号数A和B,A-B可以转化为A+(-B)的形式。

有符号数的减法运算可以通过加法运算来实现。

4. Verilog中的有符号数减法运算实现在Verilog中,有符号数减法运算可以通过使用内置的加法器和逻辑门来实现。

具体步骤如下:```verilogmodule subtractor(input [N-1:0] A, // 输入有符号数Ainput [N-1:0] B, // 输入有符号数Boutput [N-1:0] result // 输出结果);wire [N:0] B_sub; // B的补码形式assign B_sub = ~B + 1; // 计算B的补码形式assign result = A + B_sub; // A加上B的补码形式endmodule```5. 注意事项在Verilog中进行有符号数减法运算时,需要注意一些细节和特殊情况:- 运算结果是否溢出:在有符号数减法运算中,可能会出现溢出的情况,需要对结果进行检查和处理。

- 有符号数的符号扩展:在进行减法运算之前,需要对有符号数进行符号扩展,以确保运算正确性和精度。

- 有符号数的扩展位:在减法运算中,可能需要添加额外的扩展位,以确保运算结果的正确性和准确性。

verilog中运算符用法

verilog中运算符用法Verilog是一种硬件描述语言,广泛应用于数字电路的设计。

在Verilog中,运算符用于对变量进行运算操作。

本文将介绍Verilog中的常见运算符及其用法。

一、算术运算符1. 赋值运算符:用于给变量赋值。

例如,`a = 10;`将变量a的值设置为10。

2. 加法运算符:用于将两个数值相加。

例如,`b = a + 5;`将变量b的值设置为变量a的值加上5。

3. 减法运算符:用于从第一个数值中减去第二个数值。

例如,`c = a - b;`将变量c的值设置为变量a的值减去变量b的值。

4. 乘法运算符:用于将两个数值相乘。

例如,`d = a * 2;`将变量d的值设置为变量a的值乘以2。

5. 除法运算符:用于将第一个数值除以第二个数值。

例如,`e =a / 3;`将变量e的值设置为变量a的值除以3。

请注意,在Verilog 中,除法操作的结果可能因硬件实现而异,因此在使用除法运算符时需要谨慎。

6. 求模运算符:用于求两个数值相除后的余数。

例如,`f = a % 2;`将变量f的值设置为变量a的值除以2的余数。

二、比较运算符1. 等于运算符:用于比较两个值是否相等。

例如,`if (a == 10) begin ... end`将检查变量a是否等于10,如果是则执行相应的代码块。

2. 不等于运算符:用于比较两个值是否不相等。

例如,`if(a != 5) begin ... end`将检查变量a是否不等于5,如果不是则执行相应的代码块。

3. 大于运算符:用于比较两个值的大小关系。

例如,`if (b > a) begin ... end`将检查变量b是否大于变量a,如果是则执行相应的代码块。

4. 小于运算符:用于比较两个值的大小关系。

例如,`if (c < d) begin ... end`将检查变量c是否小于变量d,如果是则执行相应的代码块。

三、逻辑运算符1. 与运算符(&&):用于判断多个条件是否都为真。

verilog 运算操作符号

Verilog运算操作符号一、概述在数字电路设计和硬件描述语言(HDL)中,运算操作符号是非常重要的,它们用来表示数字电路中的逻辑操作和数据处理。

Verilog是一种常用的硬件描述语言,其中也包含了丰富的运算操作符号,本文将对Verilog中常见的运算操作符号进行详细介绍。

二、赋值操作符号1. 阻塞赋值(=)阻塞赋值用“=”表示,在Verilog中用于将右侧表达式的值赋给左侧的变量。

阻塞赋值会在当前时间点立即执行,并且会导致模拟的并行行为。

2. 非阻塞赋值(<=)非阻塞赋值用“<=”表示,在Verilog中用于将右侧表达式的值赋给左侧的变量。

非阻塞赋值会延迟一个时间段后才执行,而且多个非阻塞赋值会按顺序执行,模拟的是时序逻辑。

三、逻辑运算操作符号1. 与操作()与操作符号“”用于执行逻辑与操作,对两个操作数的每一位执行与操作,只有两个操作数对应位都为1时结果才为1。

2. 或操作(|)或操作符号“|”用于执行逻辑或操作,对两个操作数的每一位执行或操作,只要两个操作数对应位中有一位为1,结果就为1。

3. 异或操作(^)异或操作符号“^”用于执行逻辑异或操作,对两个操作数的每一位执行异或操作,当两个操作数对应位相同时结果为0,不同时结果为1。

四、算术运算操作符号1. 加法操作(+)加法操作符号“+”用于执行加法操作,对两个操作数进行加法运算。

2. 减法操作(-)减法操作符号“-”用于执行减法操作,对两个操作数进行减法运算。

3. 乘法操作(*)乘法操作符号“*”用于执行乘法操作,对两个操作数进行乘法运算。

4. 除法操作(/)除法操作符号“/”用于执行除法操作,对两个操作数进行除法运算。

五、移位运算操作符号1. 左移操作(<<)左移操作符号“<<”用于将操作数向左移动指定的位数。

2. 右移操作(>>)右移操作符号“>>”用于将操作数向右移动指定的位数。

VerilogHDL无符号数和有符号数运算

verilog 中使用有符号数分类:资料摘录2011-05-09 17:161213人阅读评论(2)收藏举报目录(?)[+]在数字电路中,出于应用的需要,我们可以使用无符号数,即包括0及整数的集合;也可以使用有符号数,即包括0和正负数的集合。

在更加复杂的系统中,也许这两种类型的数,我们都会用到。

有符号数通常以2的补码形式来表示。

图1列出了4位二进制表示法所对应正负数。

进一步观察,我们发现两种类型数的加减法是一样的,做加法和减法就是在数轮上按正时钟转转或按反时钟转。

比方说,1001+0100,意味着从1001按照顺时钟方向移动4个位置,其结果为1101。

在无符号数类型中,它代表(+9)+(+4)=+13;而在有符号数类型中,它则代表(-7)+(+4)=-3。

从数轮上看,若是加法所得的结果溢出了,那么也就是穿越了数轮的临界点。

注意这个临界点对于无符号数和有符号数来说,是不一样的:无符号数,是介于1111和0000之间;有符号数,则是介于0111和1000之间。

物理加减法的行为正好和数轮的移动类似。

只要所有的运算子和结果具有相同的位宽,那么有符号数或无符号数的形式就可用于相同的电路。

比方说,设a、b和sum 都是8位信号,表达式1sum = a+ b;无论这些信号被转译成有符号数或无符号数,它都会引用相同的硬件且使用相同的二进制表示法。

这种现象在其他算术运算中也是正确的(但是它不可用于非算术运算中,比方说有理数运算或溢出标志位的生成)。

图1 4位二进制数轮此外,当运算子或其结果的位宽不同时,我们需要区分它究竟使用哪一种符号类型。

因为不同的符号类型需要不同的扩展位。

对于无符号数,前置一个0,即所谓的零扩展位;对于有符号数来说,需要前置n个所谓的符号扩展位。

比方说4位二进制表示的-5为1011;当其扩展成8位时,应该变为1111_1011,而不是0000_1011。

举个例子,设a和sum为8位信号,b为4位信号即b3b2b1b0。

verilog 带符号位的运算

verilog 带符号位的运算Verilog是一种硬件描述语言(HDL),用于描述数字电路的结构和行为。

它被广泛应用于数字电路设计,包括芯片设计、系统级设计和嵌入式系统开发等领域。

在Verilog中,有两种类型的数据,一种是无符号数(Unsigned),另一种是有符号数(Signed)。

无符号数表示非负整数,而有符号数则可以表示负数。

在数字电路设计中,有符号数的运算非常重要,因为很多实际问题需要处理有符号数。

有符号数可以用固定长度的二进制补码(Two's Complement)表示。

在二进制补码中,第一位表示符号位,0表示正数,1表示负数。

其余位表示数值部分。

负数使用补码表示,补码就是对正数按位取反然后加1。

Verilog提供了一些有符号数的运算操作符,包括加法、减法、乘法和除法等。

这些操作符可以直接应用于有符号数,而无须考虑符号位。

Verilog还提供了一些类型转换操作符,用于在有符号数和无符号数之间进行转换。

下面是一些常见的有符号数运算的例子:1.加法运算有符号数的加法运算使用"+"操作符。

例如,a = b + c;表示将b 和c相加,结果存储在a中。

这里的b、c和a都可以是有符号数。

2.减法运算有符号数的减法运算使用"-"操作符。

例如,a = b - c;表示将c 从b中减去,结果存储在a中。

同样,b、c和a都可以是有符号数。

3.乘法运算有符号数的乘法运算使用"*"操作符。

例如,a = b * c;表示将b 乘以c,结果存储在a中。

同样,b、c和a都可以是有符号数。

4.除法运算有符号数的除法运算使用"/"操作符。

例如,a = b / c;表示将b 除以c,结果存储在a中。

同样,b、c和a都可以是有符号数。

在对有符号数进行运算时,需要特别注意溢出问题。

溢出指的是运算结果无法用有限位数的二进制数表示的情况。

verilog 带符号定点数加法

Verilog带符号定点数加法一、引言Verilog是一种硬件描述语言,被广泛用于数字电路的设计和仿真。

在Verilog中,定点数加法是常见的数字电路设计任务之一。

在本文中,我们将介绍Verilog中带符号定点数加法的实现方法。

二、带符号定点数1. 定点数定点数是一种表示数值的方法,它将数值表示为带有小数部分的整数。

定点数可以是带符号的,也可以是无符号的。

在Verilog中,定点数通常使用固定位宽的二进制数表示。

2. 带符号数带符号数是可以表示正负的数值。

在Verilog中,带符号数通常使用二进制补码表示。

在二进制补码表示中,最高位表示符号位,0表示正数,1表示负数。

三、带符号定点数加法的实现在Verilog中,带符号定点数加法可以通过将加数和被加数的符号位相同的情况下,对二进制数进行加法运算来实现。

具体步骤如下:1. 确定位宽需要确定带符号定点数的位宽,包括整数部分和小数部分。

位宽的选择需要考虑数值范围和精度要求。

2. 符号扩展对于两个带符号定点数,需要进行符号扩展,使它们的位宽相同。

符号扩展是将较短的带符号定点数的符号位复制到较长的带符号定点数的高位。

3. 加法运算进行带符号定点数的加法运算。

在Verilog中,可以使用"+"操作符进行加法运算。

需要注意处理进位,以及溢出情况。

4. 结果截断根据实际需求,对加法运算得到的结果进行截断,得到最终的带符号定点数结果。

四、示例代码以下是一个简单的Verilog示例代码,实现了带符号定点数加法的功能:```module signed_fixed_point_addition(input signed [7:0] a, // 带符号定点数a,8位位宽input signed [7:0] b, // 带符号定点数b,8位位宽output reg signed [7:0] result // 加法结果,8位位宽);always (*) beginresult = a + b; // 带符号定点数加法运算endendmodule```五、总结带符号定点数加法是数字电路设计中常见的任务,Verilog提供了实现这一功能的灵活和强大的工具。

verilog有符号数运算

verilog有符号数运算1)之前的笔记写过《补码探讨》,可知在FPGA综合成电路的时候最底层都是以补码的形式在运算,正数的补码就是本⾝,负数的补码要取反+1。

(2)那么Verilog中编程的时候对编程⼈员来说,其实想不到现在的编译器(Quartus II 9.1和ISE10.1没有问题,更⾼的版本应该更加可以了)都⽀持verilog有符号运算的综合了。

在定义时直接加上signed即可,如下: input signed [7:0] a, b; output signed [15:0] c; wire signed [15:0] x; reg signed [15:0]y; 很明显,这种采⽤signed定义的情况,可以避免⼿动转换带来的⿇烦,同时可以节省很多开发时间(3)当使⽤移位运算“>>”进⾏1/2倍运算时,需注意:verilog中最简单的加减乘除运算对于有符号数和⽆符号数其实是有很⼤区别的,现总结⼏点如下:例⼦:对输⼊a,b取平均值,然后赋值给c输出always @(posedge clk)c<=(a+b)>>1;1.a,b均为⽆符号数,结果正确2.a,b中⼀个为有符号数(a),另⼀个为⽆符号数(b),编译器会⾃动将⽆符号数(b)转换成有符号数,这样就成了2个有符号数之间的运算了,结果是个有符号数,此时1>如果a+b结果为正数(最⾼位为0),那么结果正确2>如果a+b结果为负数(最⾼位为1),那么结果错误,因为移位运算新移⼊的位将⽤0来填补,此时负数将变为正数,显然错误。

所以综上,在进⾏有符号数运算的时候,最好像如下这样写:reg signed [3:0] a;reg signed [3:0] b;reg signed [3:0] c;always @(posedge clk)c<=(a+b)/2;这样就可以避免不必要的错误。

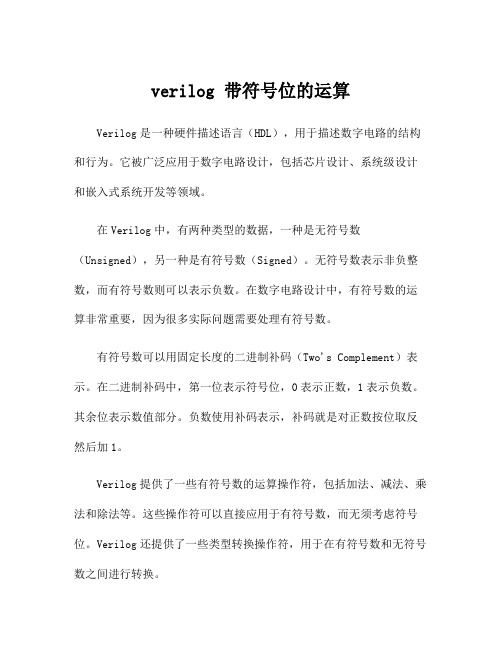

verilog中有符号整数说明及除法实现

verilog中有符号整数说明及除法实现 1、以8位短整数为例,短整数的最⾼位是符号位,符号位的正负表⽰了该值是“正还是负”?。

正值的表⽰⽅法是以0开始的8位⼆进制数,反之负值的表⽰⽅法是⽤正数的补码来表⽰。

例如:+127 亦即8'b0111_1111;那么-127 亦即8'b1000_0001(通过相应正数的按位取反加1得到,符号位也要取反); 2、正值可以进⾏求反⼜加⼀之后成为负值。

那么负值如何变成正值?同样的⼀个道理“负值求反⼜加⼀后,成为正值”。

3、我们知道短整数的位宽为,8 ,亦即取值范围是0~255。

但是符号位的出现吃掉了最⾼位,所以造成取值范围变成2^7=128,即0到127。

4、在Modelsim中显⽰数据时,数据格式Decimal表⽰有符号数(-128~+127),Unsigned表⽰⽆符号数(0~255)(⼆者最终都是整数⽅式显⽰)。

也即:Modelsim只能对最终结果实现转化,在数据处理过程中则需要⼈为编程实现正数或者负数。

除法实现及仿真:1module divider(Reset,Clock,Start_sig,Done_sig,A,B,C,D);23input Reset,Clock,Start_sig;4output Done_sig;5input [7:0] A,B;6output [7:0] C,D;78reg [7:0] A_temp,B_temp,C,D;9reg Symbol,Done_sig;10reg [2:0] i;1112always@(posedge Clock or negedge Reset)13begin14if(!Reset)15begin16 C<=8'b0;17 D<=8'b0;18 i<=3'b0;19 Done_sig<=1'b0;20end21else if(Start_sig)22case(i)230:begin24 Symbol<=A[7]^B[7];25 A_temp<=A[7]?(~A+8'b1):A;26 B_temp<=B[7]?B:(~B+8'b1);27 i<=i+1'b1;28end291:begin30if(A_temp<(~B_temp+8'b1)) begin D<=A_temp;i<=i+1'b1;C<=Symbol?(~C+1'b1):C;end31else begin A_temp<=A_temp+B_temp;C<=C+8'b1;end32end332:begin34 Done_sig<=1'b1;i<=i+1'b1;35end363:begin37 Done_sig<=1'b0;i<=1'b0;38end39endcase40end4142endmoduledivider.v1 `timescale 1ns/1ps2module divider_tb();3reg Reset,Clock,Start_sig;4reg [7:0] A,B;5wire Done_sig;6wire [7:0] C,D;78 divider U(9 .Reset(Reset),10 .Clock(Clock),11 .Start_sig(Start_sig),12 .A(A),13 .B(B),14 .C(C),15 .D(D),16 .Done_sig(Done_sig));1718initial19begin20 Reset=0;#10 Reset=1;21 Clock=0;forever #10 Clock=~Clock;22end232425always@(posedge Clock or negedge Reset)26if(!Reset)27begin28 A<=8'b0;29 B<=8'b0;30 Start_sig<=1'b0;31end32else33if(Done_sig)3435 Start_sig<=1'b0;3637else38begin39 A<=8'b00110110;40 B<=8'b11111001;41 Start_sig<=1'b1;42end4344endmoduledivider_tb.vQ9.0,M6.4a的仿真结果:出现的问题:为什么昨天功能仿真是对的,⽽今天时序仿真得到的商却是零?。

verilog 算数移位 逻辑移位

verilog 算数移位逻辑移位算数移位和逻辑移位是数字电路设计中常用的操作,用于对数据进行位移和移位运算。

本文将介绍verilog中的算数移位和逻辑移位操作,并讨论它们的应用和特点。

算数移位是指对有符号数进行位移操作。

在verilog中,算数移位使用“>>”和“<<”操作符表示。

例如,对于一个8位有符号数x,x>>1表示将x向右移动1位,而x<<1表示将x向左移动1位。

算数右移的特点是在右移过程中,最高位(即符号位)保持不变,并且右移的空位用符号位填充。

这意味着如果原始数是负数,右移操作后仍然是负数,而正数的右移操作结果是正数。

算数左移的特点是在左移过程中,最低位为空位,并且左移的空位用0填充。

左移操作可以看作是乘以2的幂次方的操作,因为每向左移动一位,原始数的值乘以2。

逻辑移位是指对无符号数进行位移操作。

在verilog中,逻辑移位使用“>>>”和“<<<”操作符表示。

逻辑移位和算数移位的操作符形式相似,但是它们的结果处理方式不同。

逻辑右移的特点是在右移过程中,最高位和其他位都右移,并且右移的空位用0填充。

逻辑右移操作不考虑数值的正负,只是简单地将每一位向右移动。

逻辑左移的特点是在左移过程中,最低位和其他位都左移,并且左移的空位用0填充。

逻辑左移操作可以看作是乘以2的幂次方的操作,因为每向左移动一位,原始数的值乘以2。

算数移位和逻辑移位在数字电路设计中有广泛的应用。

它们可以用于数据的位移和移位运算,例如乘法运算中的乘以2操作、除法运算中的除以2操作等。

此外,移位操作还可以用于数据的压缩和扩展,以及数据的排序和过滤等应用。

总结起来,verilog中的算数移位和逻辑移位操作是数字电路设计中常用的操作,用于对数据进行位移和移位运算。

算数移位和逻辑移位的操作符形式相似,但是它们的结果处理方式不同。

算数移位保持符号位不变,并用符号位填充空位,逻辑移位不考虑数值的正负,简单地将每一位向指定方向移动,并用0填充空位。

Verilog有符号数处理

Verilog有符号数处理内容主要摘⾃以下两个链接:现在FPGA编译器都⽀持verilog有符号运算的综合,并且综合后的有符号数都是以补码形式存在,明⽩点说,就是编译器可以⾃动把有符号数编码成补码形式。

具体在有符号数处理过程中注意那些点,1、有符号⼆进制加减法原理有符号数通常以2的补码形式来表⽰。

图1列出了4位⼆进制表⽰法所对应正负数。

进⼀步观察,我们发现两种类型数的加减法是⼀样的,做加法和减法就是在数轮上按正时钟转转或按反时钟转。

⽐⽅说,1001+0100,意味着从1001按照顺时钟⽅向移动4个位置,其结果为1101。

在⽆符号数类型中,它代表(+9)+(+4)=+13;⽽在有符号数类型中,它则代表(-7)+(+4)=-3。

从数轮上看,若是加法所得的结果溢出了,那么也就是穿越了数轮的临界点。

注意这个临界点对于⽆符号数和有符号数来说,是不⼀样的:⽆符号数,是介于1111和0000之间;有符号数,则是介于0111和1000之间。

物理加减法的⾏为正好和数轮的移动类似。

只要所有的运算⼦和结果具有相同的位宽,那么有符号数或⽆符号数的形式就可⽤于相同的电路。

⽐⽅说,设a、b和sum都是8位信号,表达式1 sum = a+ b;⽆论这些信号被转译成有符号数或⽆符号数,它都会引⽤相同的硬件且使⽤相同的⼆进制表⽰法。

这种现象在其他算术运算中也是正确的(但是它不可⽤于⾮算术运算中,⽐⽅说有理数运算或溢出标志位的⽣成)。

图1 4位⼆进制数轮2、位扩展此外,当运算⼦或其结果的位宽不同时,我们需要注意区分符号类型。

因为不同的符号类型需要扩展⽅式是不同的。

(1)对于⽆符号数,前置⼀个0,即所谓的零扩展位;(2)对于有符号数来说,需要前置n个所谓的符号扩展位。

举个例⼦,设a和sum为8位信号,b为4位信号即b3b2b1b0。

表达式1 sum = a + b需要将b扩展为8位。

如果是⽆符号数形式,那么b扩展为0000_b3b2b1b0;如果是有符号数形式,那么b扩展为b3b3b3b3_b3b2b1b0。

verilog中的有符号数理解(转)

verilog中的有符号数理解(转)verilog中的有符号数运算有符号数的计算:若有需要关于有号数的计算,应当利⽤Verilog 2001所提供的signed及$signed()机制。

Ex:input signed [7:0] a, b;output signed [15:0] o;assign o = a * b;orinput [7:0] a, b;output [15:0] o;wire signed [15:0] o_sgn;assisn o_sgn = $signed(a) * $signed(b);assign o = $unsigned(o_sgn);正负号的扩展:应多加利⽤Verilog的implicity signed extension,避免⼿动进⾏转换。

Ex:input signed [7:0] a, b;input signed [8:0] o;assign o = a + b; // Verilog会⾃动进⾏符号的扩展。

有号数与⽆号数的混合计算:不要在同⼀个verilog叙述中进⾏有号数与⽆号数的计算。

应该要分成个别独⽴的叙述。

在⼀个verilog叙述中只要有⼀个⽆号数的操作数,整个算式将被当成⽆号数进⾏计算。

(常数默认为⽆符号数)input [7:0] a;input signed [7:0] b;output signed [15:0] o; // Don't do this: assign o = a * b;// The $signed({1'b0, a}) can convert the unsigned number to signednumber.assign o = $signed({1'b0, a}) * b;input signed [7:0] a;output signed [15:0] o;// Don't do this: assign o = a * 8'b10111111;// Use $signed() system taskassign o = a * $signed(8'b10111111);// or sb keyword.assign o = a * 8'sb10111111;part-select运算过后的操作数是⽆号数。

Verilog有符号整型数(signedint)比大小

Verilog有符号整型数(signedint)⽐⼤⼩本⽂参考了关于2进制补码的思考和讨论。

======================================================================================================即使在变量声明的时候定义了signed属性,在Verilog中使⽤>(⼤于),>=(⼤于等于),<(⼩于)和<=(⼩于等于)进⾏有符号数的⼤⼩⽐较时还是没有想要的结果。

现在需要实现⼀个有符号数⽐较的功能。

1、⼀些注记。

以8位有符号数(signed int)为例,表⽰范围是-128~+127,有⼀些边缘的数很有特征,记下来⽅便使⽤:0000_0000 表⽰ 0;0000_0001 表⽰ +1;1111_1111 表⽰ -1;0111_1111 表⽰ +127;1000_0001 表⽰ -127;1000_0000 表⽰ -128.我们发现,(1)除了0和-128,其他相反数按⽆符号相加,得到的是0000_0000(即0000_0000)。

(2)⾮负数的MSB(最⾼位)=0;负数的MSB=1。

2、⽐较规则。

我们设a和b为输⼊的两个signed 8类型的⽐较数,并且a>=b(GE)时输出信号y为1,否则输出为0。

⽐较的规则如下:(1)⾮负数⼀定⼤于负数。

(2)负数⼀定⼩于⾮负数。

(3)a、b同是⾮负数,则按unsigned⽐较两个数:a>=b则y=1;a<b则y=0。

(4)a、b同是负数,则按unsigned⽐较a和b的[6:0]即除去符号位:a[6:0]>=b[6:0]则y=1;a[6:0]<b[6:0]则y=0。

3、Verilog模块。

//************************************// A >= B -> 1// A < B -> 0////************************************module ageb_s8(rst_n,sys_sam_clk,a,b,cmp_out);//****************************************// Port Def.////****************************************input wire rst_n;input wire sys_sam_clk;input wire[7:0] a;input wire[7:0] b;output wire cmp_out;//****************************************// Define////****************************************localparam YES = 1'b1;localparam NO = 1'b0;//****************************************// Variables////****************************************reg cmp_reg;//****************************************// Behaviour////****************************************assign cmp_out = cmp_reg;//*** Compare Logicalways@(posedge sys_sam_clk)beginif(!rst_n)begincmp_reg <= 1'b0;endelse begincase({a[7], b[7]})2'b01:begin // a+, b-cmp_reg <= 1'b1;end2'b10:begin // a-, b+cmp_reg <= 1'b0;end2'b00:begin // a+, b+, Compare Amplitudeif(a[6:0] >= b[6:0])begin // Unsigned Compare cmp_reg <= 1'b1;endelse begincmp_reg <= 1'b0;endend2'b11:begin // a-, b-, Compare [6:0]if(a[6:0] >= b[6:0])begincmp_reg <= 1'b1;endelse begincmp_reg <= 1'b0;endenddefault:begincmp_reg <= 1'b0;endendcaseendendendmodule4、仿真整体:⽐较结果y是PWM信号的形式。

verilog负数除法

Verilog负数除法介绍在Verilog中实现负数除法是一个常见的应用,尤其在数字信号处理领域。

负数除法是指对两个负数进行除法运算,得到一个带符号的结果。

本文将介绍如何在Verilog中实现负数除法的基本原理和具体实现方法。

负数除法的原理负数除法是通过将被除数和除数转换为二进制补码表示形式来实现的。

具体步骤如下: 1. 将被除数和除数转换为二进制补码。

2. 对转换后的数进行除法运算。

3. 如果最高位为1,表示结果为负数,则将结果转换为十进制补码形式。

Verilog实现负数除法的方法步骤1:将被除数和除数转换为二进制补码为了对负数进行运算,首先需要将负数转换为二进制补码形式。

转换的方法如下:1. 将负数的绝对值转换为二进制形式。

2. 反转二进制数的每一位,即0变为1,1变为0。

3. 对反转后的二进制数加1,得到二进制补码。

步骤2:进行除法运算在Verilog中,除法运算可以通过被除数与除数的乘法逆运算来实现。

具体步骤如下: 1. 将被除数与除数转换为二进制补码形式。

2. 对转换后的数进行乘法运算。

3. 得到乘法运算的结果,即商。

4. 如果最高位为1,表示结果为负数,则将结果转换为十进制补码形式。

步骤3:转换结果为十进制补码形式在Verilog中,负数的结果通常使用十进制补码形式表示。

转换的方法如下: 1. 如果最高位为1,表示结果为负数。

2. 反转结果的每一位,即0变为1,1变为0。

3. 对反转后的二进制数加1,得到负数的十进制补码形式。

Verilog负数除法的代码实现下面是一个用Verilog实现负数除法的简单示例代码:module negative_division (input signed [7:0] dividend,input signed [7:0] divisor,output signed [7:0] quotient);assign quotient = dividend / divisor;endmodule总结通过本文的介绍,我们了解了在Verilog中实现负数除法的原理和具体方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Verilog带符号数运算摘要:介绍了Verilog带符号数的不同运算。

因为Reg和Wire数据默认情况下是无符号的,而在数据处理的情况下,Verilog既要对带符号数据进行各种运算,也要对无符号数和带符号数进行运算,所以简单使用Verilog提供的运算符是不够的。

因此研究不同类型数据运算的通用方法是必要的。

关键词:Verilog;带符号数;补码;算术运算中图分类号:TN911?34 文献标识码:A 文章编号:1004?373X(2015)03?0160?03Operation of numbers with symbols by VerilogHUI Wei?jun,SHEN Zhao?jun(Yancheng Institute of Technology,Yancheng 224051,China)Abstract:Different operations of data with symbols by Verilog are introduced. Reg and Wire data in the case of default is unsigned,but in the case of data processing,a variety of operations of data with symbols are performed by Verilog,and the unsigned and signed with numbers need to be processed. However,it is not enough to use the operation symbols provided by Verilog. It is necessary to research the generalmethod for various types of data operation.Keywords:Verilog;number with symbol;twos complement;arithmetic operation0 引言Verilog语言是目前流行的一种硬件描述语言。

它的最大的优点是简单、规范,语法规则与C语言十分相似。

然而,作为一种描述语言,Verilog不具备C语言丰富的数据类型和数据处理能力。

Verilog 95中能处理带符号数数据类型是整型,而整型的默认位宽是32位,且位宽不能改变,因而限制了整型数的使用。

为了解决这个问题,Verilog 2001版本增加了对带符号数处理的支持,虽然如此,Verilog对数据处理仍然有很多问题。

本文以Verilog 2001为版本,重点讨论带符号数的算术运算,并给出Verilog程序和仿真结果,同时,本文也讨论了带符号数的其他运算情况。

1 加、减运算Verilog 2001处理带符号数加减运算很简单,只要在定义数组是使用关键字signed即可:module add_signed(a,b,sum);input signed [7:0] a,b;output signed [7:0] sum;assign sum=a+b;endmodule仿真结果如图1所示。

图1 加法仿真结果Verilog处理带符号数和无符号数运算时候,默认是把带符号数转换为无符号数。

因此,对于带进位加法或者带借位减法运算,如果不加处理就会发生错误:module addc(a,b,c,sum);input signed [7:0] a,b;input c;output signed [8:0] sum;assign sum=a+b+c;endmodule仿真如图2所示,可知结果是错误的,原因是a和b高位扩展加零。

改进的方法是把带符号数进行符号扩展:assign sum={a[7],a}+{b[7],b}+c;图2 带符号数和无符号数加法仿真错误结果图3所示仿真表明结果是正确的。

也可以用系统函数把无符号数转换为带符号数参加运算:assign sum=a+b+$signed(c);所得仿真结果将会相同。

不同的是,系统函数$signed 不能综合,具有$signed的代码只能用于仿真。

图3 带符号数和无符号数加法仿真正确结果2 乘法运算两个带符号数乘法运算的处理与加法运算相似,只需在定义端口的时候使用关键字signed即可:module mult(a,b,prod);input signed [7:0] a;input signed [7:0] b;output signed [15:0] prod;assign prod = a * b;endmodule如图4所示的仿真表面结果是正确的。

当然,实现一个带符号数和无符号数的乘法的时候,默认是把带符号数高位全部扩展为零,因而,用乘法运算符实现的乘法结果将会是错误的,如图5所示。

module mult(a,b,prod);input signed [7:0] a;input [7:0] b;output signed [15:0] prod;assign prod = a*b;endmodule图5 带符号数与无符号数乘法仿真错误结果解决方法是可以用函数$signed把上述代码中的无符号数b转换为带符号数,此时代码就不可综合。

实现通用的两个数乘法的算法,基本的思路是用移位加的方式实现。

其算法基础是认为补码是一个权重码,位宽为n的向量存放补码,其MSB的权为[-2n-1,]其他位的权为[2i,]i的取值范围为0≤i≤n-2。

当两个位宽为n的数相乘时,从右向左,逐位考察乘数索引为i的位的值,若为1,将被乘数左移i位,作为部分和加到结果中。

若乘数最高为位1,因为权为[-2n-1,]所以被乘数要先取反加一,然后再左移n-1位。

两个位宽为n的数相乘,最终的结果,是由n个移位的部分和相加得到。

module mult8(a,b,prod);input signed [7:0] a;input [7:0] b;output signed [15:0] prod;wire [15:0] prod_int0;wire [15:0] prod_int1;wire [15:0] prod_int2;wire [15:0] prod_int3;wire [15:0] prod_int4;wire [15:0] prod_int5;wire [15:0] prod_int6;wire [15:0] prod_int7;wire [7:0] inv_add1;assign prod_int0 = b[0] ?{{8{a[7]}},a} :16′b0;assign prod_int1 = b[1] ?{{7{a[7]}},a,1′b0} :16′b0;assign prod_int2 = b[2] ?{{6{a[7]}},a,2′b0} :16′b0;assign prod_int3 = b[3] ?{{5{a[7]}},a,3′b0} :16′b0;assign prod_int4 = b[4] ?{{4{a[7]}},a,4′b0} :16′b0;assign prod_int5 = b[5] ?{{3{a[7]}},a,5′b0} :16′b0;assign prod_int6 = b[6] ?{{2{a[7]}},a,6′b0} :16′b0;assign inv_add1 = ~a + 1′b1;assign prod_int7=b[7]?{inv_add1[7],inv_add1,7′b0} :16′b0;assign prod = prod_int0 + prod_int1 + prod_int2+prod_int3 + prod_int4 + prod_int5+prod_int6 + prod_int7;//六个部分和相加得到积endmodule以上代码可以对2个无符号数、2个带符号数、1个带符号数和1个无符号数的乘法都适用,仿真结果如图6所示。

图6 带符号数和无符号数相乘的正确结果3 除法运算通用的整数除法器也不可以用除法运算符来实现。

除法器实现比较复杂,组合逻辑实现的算法较少。

以下代码实现的就是一个通用的组合逻辑除法器,其思想是,先把带符号数转换为无符号数,实现两个无符号数的整数除法。

至于两个无符号数的除法器的算法是,循环实现被除数减去除数,直到被除数比除数小。

那么,减的次数就是商,保留的被除数就是余数。

最后根据被除数和除数的符号位确定商和余数的符号。

Moduledividenew(Dividend,Divisor,Quotient,Reminder);input [7:0] Dividend,Divisor;output reg [7:0] Quotient,Reminder;wire isneg;wire [7:0] Dividend_abs,Divisor_abs;integer i;reg [7:0] tempa;reg [7:0] tempb;reg [15:0] temp_a;reg [15:0] temp_b;assign isneg = Dividend[7] ^ Divisor[7];assign Dividend_abs = Dividend[7] ?~Dividend + 1 :Dividend;assign Divisor_abs = Divisor[7] ?~Divisor + 1 :Divisor;always @(Dividend_abs,Divisor_abs)begintempa tempb = tempb )temp_a = temp_a - temp_b + 1;elsetemp_a = temp_a;endQuotient = isneg ?~temp_a[7:0] + 1 :temp_a[7:0];Reminder = Dividend[7] ?~temp_a[15:8]+1 :temp_a[15:8];endendmodule上述程序适用于任意两个数相除的情况。

仿真结果如图7所示,结果表明算法设置是正确的。

4 其他运算(1)移位运算Verilog 2001增加了>>> 带符号数右移运算符,不同于运算符>> ,当执行该运算时,低位移出,高位补的是符号位。

(2)关系运算当执行带符号数和无符号数运算时候,Verilog默认是把带符号数看成无符号数。

因此比较大小时,容易发生错误。

reg [7:0] a = 13;reg signed [7:0] b = -8;wire c;assign c = (a > b);上述代码中,c的值为0,说明关系运算是错误的。