数字系统设计课件(自制)第4章

数字系统设计.ppt

智能

逻辑运算

系统

存

输入

储 器

控制 电路

控制信号 数据 条件信号 处理

输出 接口

2019/12/31

GUET School of Information & Communications

数据输出

12

▪ 输入电路 ➢ 完成信号的转换:模数转换器、译码器、数据选 择器和寄存器 ➢ 输入应该包含缓冲电路

▪ 输出电路 ➢ 输出驱动与执行 ➢ 译码器、显示电路、寄存器和数模转换器来实现 ➢ 输出应该锁存

2019/12/31

GUET School of Information &

13

Communications

▪ 数据处理器 ➢ 主要包括逻辑运算与算术运算 ➢ 数字系统不可缺少的部分

▪ 控制器 ➢ 协调数字系统工作的部件 ➢ 数字系统不可缺少的部分 ➢ 输入:时钟/条件信号/全局信号/…… ➢ 输出:控制信号/相对于时钟的信号(时序)/……

▪ 时钟电路 ➢ 产生使系统工作的同步全局信号——时钟

2019/12/31

GUET School of Information &

14

Communications

▪ 复杂数字系统的组成

➢ 控制器 ➢ 若干子系统

子

子

子

系

系

系

第4章应用VHDL设计数字系统-电子琴和音乐播放器的设计

CLK

IF EN = '1' THEN

--检测是否允许计数(同步使能)

IF CNTI < 9 THEN --检测是否小于9

RST

CNTI := CNTI + 1; --小于9,允许加1计数

EN

ELSE

CNTI := (OTHERS =>‘0’); --大于等于9,计数值清零 END IF;

inst

END IF;

END IF;

IF CNTI = 9 THEN COUT <= ‘1’; --计数等于9,输出进位信号

ELSE COUT <= '0';

END IF;

CNT <= CNTI; --将计数值向端口输出

END PROCESS;

END behav;

CNT[3..0] COUT

项目1:电子琴的设计

仿真结果:10进制计数器设计

结论: 计数器就可以完成分频器的任务!

项目1:电子琴的设计

设计关键:N进制计数器设计——可变分频器

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;

CNT_N CLK

RST

ENTITY CNT_N IS PORT (

CNT[11..0] COUT

项目1:电子琴的设计

设计关键:N进制计数器设计——可变分频器

ARCHITECTURE behav OF CNT_N IS

BEGIN

PROCESS(CLK, RST, EN)

VARIABLE CNTI : STD_LOGIC_VECTOR(11 DOWNTO 0);

数字系统设计ppt课件

数字系统设计与CPLD应用

29

硬件描述语言 HDL Hardware Description Language

用于设计硬件电子系统的计算机语言,它用软件编程的 方式来描述电子系统的逻辑功能、电路结构和连接形式,与 传统的门级描述方式相比,它更适合大规模系统的设计。

Abel HDL AHDL Verilog HDL VHDL Hardware C

数字系统设计与CPLD应用

30

例如,一个二选一的选择器的电原理图如图0-4所示

图0-4 二选一选择器的电原理

数字系统设计与CPLD应用

31

用VHDL语言描述的二选一选择器如下:

ENTITY mux IS

PORT(d0,d1,sel :IN BIT ;

q :OUT BIT) ;

END mux ;

ARCHITECTURE connect OF mux IS

数字系统设计与CPLD应用

19

自底向上(Bottom to Up)的主要设计步 第一步:选择逻辑元、骤器件。

由数字电路的基本知识可知,可以用与非 门,或非门,D触发器,JK触发器等基本逻 辑元、器件来构成一个计数器。设计者根据 电路尽可能简单,价格合理,购买和使用方 便及各自的习惯来选择构成六进制计数器的 逻辑元、器件。

当今的产品开发设计人员通常

采用建立数字系统的算法模型来

设计数字系统。

数字系统设计与CPLD应用

12

§ 0.2 数字系统设计方法论

• 数字系统设计的两个分支:

1.系统硬件设计

2.系统软件设计。

• 随着计算机技术的发展和硬件描述语言HDL( Hardware Description Language)的出现 ,硬件设计方法又有了新的变化。

eda第四章

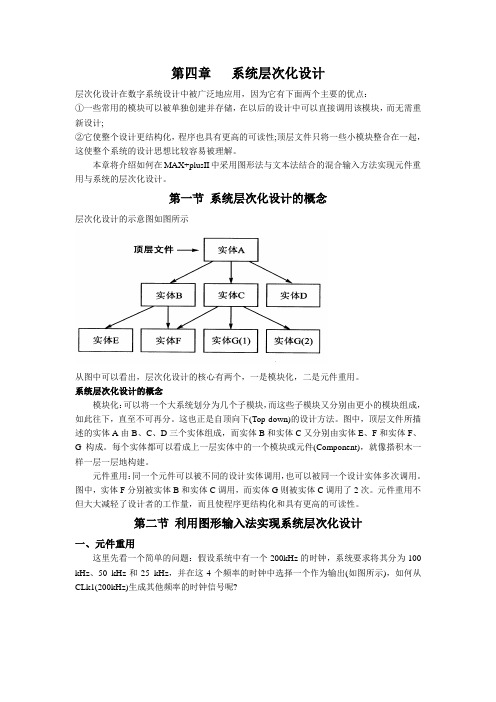

第四章系统层次化设计层次化设计在数字系统设计中被广泛地应用,因为它有下面两个主要的优点:①一些常用的模块可以被单独创建并存储,在以后的设计中可以直接调用该模块,而无需重新设计;②它使整个设计更结构化,程序也具有更高的可读性;顶层文件只将一些小模块整合在一起,这使整个系统的设计思想比较容易被理解。

本章将介绍如何在MAX+plusII中采用图形法与文本法结合的混合输入方法实现元件重用与系统的层次化设计。

第一节系统层次化设计的概念层次化设计的示意图如图所示从图中可以看出,层次化设计的核心有两个,一是模块化,二是元件重用。

系统层次化设计的概念模块化:可以将一个大系统划分为几个子模块,而这些子模块又分别由更小的模块组成,如此往下,直至不可再分。

这也正是自顶向下(Top-down)的设计方法。

图中,顶层文件所描述的实体A由B、C、D三个实体组成,而实体B和实体C又分别由实体E、F和实体F、G构成。

每个实体都可以看成上一层实体中的一个模块或元件(Component),就像搭积木一样一层一层地构建。

元件重用:同一个元件可以被不同的设计实体调用,也可以被同一个设计实体多次调用。

图中,实体F分别被实体B和实体C调用,而实体G则被实体C调用了2次。

元件重用不但大大减轻了设计者的工作量,而且使程序更结构化和具有更高的可读性。

第二节利用图形输入法实现系统层次化设计一、元件重用这里先看一个简单的问题:假设系统中有一个200kHz的时钟,系统要求将其分为100 kHz、50 kHz和25 kHz,并在这4个频率的时钟中选择一个作为输出(如图所示),如何从CLk1(200kHz)生成其他频率的时钟信号呢?很容易就可以想到两种方案:①设计一个2分频电路、一个4分频电路和一个8分频电路,直接从200kHz时钟信号分频得到所需的几个频率的时钟信号(如图所示);②只设计一个2分频电路,用3个2分频电路级联的方式,从200kHz信号中逐级分出所需的时钟信号(如图所示)。

第4章 CPU的设计方法及范例

非常简单CPU不具有应用价值,仅用来说明 设计过程。不过,只要我们能正确设计出只有4条 指令的CPU,就可以设计出拥有40条指令的CPU, 甚至更多·· ·。难道这样还有怀疑吗?当然不能期 望马上就有创新,但这个CPU是拥有自主知识产 权的。或者有些同学会这样想,我以后并非从事 硬件的工作,更不可能从事设计CPU的专业,我 也相信这是事实。但是,这绝对有利于我们掌握 计算机的工作原理,也有利于从事各种软、硬件 开发和计算机科学等领域的研究、教学工作。

图4.9 通用CPU的状态图

其实CPU就是一个复杂的有限状态机 【冯· 诺依曼机的理论是基于图灵(Turing) 机理论的,而图灵机就是一个有限状态 机】。通过确定状态及其对应的微操作, 就可明确CPU为了取数据(或指令),指 令译码和执行指令集中每一条指令所必须 要完成的步骤。 问题:什么是图灵机理论?

1966年美国计算机协会设立“图灵奖”,被视为计算机科学界的最高荣誉

它的“纸带”相当于作业薄,读写头相当于人的眼 睛、手、笔,对于输入集{x1,x2,…xn},r(i, 0)= xi,i= 1,2,..n相当于“抄题”,而映射f 的读写变换相当于人脑判断确定下一步的行为且 指挥手和笔如何去动作和书写。它高度概括地回 答了什么是运算,不但为计算复杂度理论提供了 研究工具,而且为20世纪50年代计算机的设计提 供了思想基础,即Moore机和Mealy机。【注:当 出现状态Sy或Sn时,即得到了Turing 机的运算结 论Yes或No,这时即S(t)∈{ Sy,Sn }时停机】

二、建立数据通路的原理和方法

1.存贮器数据通路的原理

2.CPU内部的数据通路(两种不同的方案)

三、CPU内部寄存器控制信号的定义和确定方法

2.决定每个部件应完成的功能(详见图4.14)

数字电子技术基础(第四版)-第4章-组合逻辑电路解析PPT课件

-

54

设计实例2:用2N选一数据选择器实现 N+1个变量的逻辑函数。

设计思想: ①将N个变量接数据选择器的选择输入端(即地址端) ②余下的一个变量作为数据选择器的数据输入端。

-

55

例:用74153实现三变量函数。

F (A ,B ,C ) m (1 ,3 ,5 ,6 )

解一:设B接A1,C接A0。

A

' 0

)

m2

'

...

Y7 ' ( A2 A1A0 ) m 7 '

-

45

-

46

-

47

三、用译码器构成函数发生器P186

例1:

请写出Y的逻辑函数式

Y(Y3'Y4'Y5')' Y3Y4 Y5

m3 m4 m5

m(3, 4,5)

Y A 'B C A B 'C ' A B 'C

-

48

例2:用74138构成下 列函数发生器:

F A 'B 'C A 'B C A B 'C A B C ' 0 B 'C ' ( A ' A ) B 'C A B C ' A 'B C

0 m 0 1 m 1 A m 2 A 'm 3

D 0 m 0 D 1 m 1 D 2 m 2 D 3 m 3

-

56

解二:设A接A1,B接A0。

4)画逻辑图(略)

-

31

三、优先编码器 8线-3线优先编码器

74HC148

-

1、功能表

输入:I 0 ~ I 7 ,共8个输入端

数字系统设计课件

数字电路与系统第十一章数字系统设计数字系统的基本概念算法状态机逐次逼近型转换器数字系统设计 数字系统设计举例数字系统的结构框图如图所示,主要由数据处理器和系统控制器两个核心部分组成。

◆输入/输出接口主要用于系统和外界交换信息,或者用来与模拟系统相连,将模拟量转化为数字量,或将数字量转化为模拟量。

◆控制器是控制数字系统内各模块协同工作的电路,它根据外部输入信号、系统状态及处理器反馈信号,产生对数字信号处理器的控制信号及系统对外输出信号。

◆处理器则在控制器的控制信号控制下,按一定工作步骤工作,并完成各种数字信号处理或复杂时序操作。

◆有些规模较大的数字系统控制还设置了存储器,用来存储数据和各种控制信息,以供控制器调用组合逻辑电路和时序逻辑电路,例如译码器、多路选择器、加法器、数据寄存器、移位寄存器、计数器等,通常称之为逻辑部件或功能模块,他们是构成数字系统的基本电路。

通常以是否有控制器作为区别功能部件和数字系统的标志,凡是包含控制器且能按顺序进行操作的系统,不论规模大小,一律称为数字系统,否则只能算是一个子系统部件,不能叫做一个独立的数字系统。

数字系统的规模可大可小,复杂程度也有很大差别,复杂的如计算机,数字通信设备,简单的如交通灯控制系统。

数字系统的设计方法一般采用自上而下(Top-Down)的设计方法。

所谓“上”指的是系统功能,向下就是按“系统一子系统一模块一触发器/门电路”的顺序逐层进行设计。

对于简单的小型数字系统,可以直接对它进行模块划分,其核心是将整个系统从逻辑上划分成控制器和处理器(受控电路)两大模块,采用ASM图来描述控制器和处理器的工作过程。

如果系统比较复杂,可以在将系统划分为多个子系统,逐步确定子系统方案与模块划分,分别设计和实现各子系统,最后由各子系统组成完整的数字系统。

数字系统设计过程ASM图是描述数字系统控制算法的流程图。

应用ASM图设计数字系统,可以很容易将语言描述的设计问题变成时序流程图的描述。

数字系统设计概述27页PPT

谢谢!

1、不要轻言放弃,否则对不起自己。

2、要冒一次险!整个生命就是一场冒险。走得最远的人,常是愿意 去做,并愿意去冒险的人。“稳妥”之船,从未能从岸边走远。-戴尔.卡耐基。

梦 境

3、人生就像一杯没有加糖的咖啡,喝起来是苦涩的,回味起来却有 久久不会退去的余香。

数字系统设计概述4、守业的最好办法就是不断的发展。 5、当爱不能完美,我宁愿选择无悔,不管来生多么美丽,我不愿失 去今生对你的记忆,我不求天长地久的美景,我只要生生世世的轮 回里有你。

61、奢侈是舒适的,否则就不是奢侈 。——CocoCha nel 62、少而好学,如日出之阳;壮而好学 ,如日 中之光 ;志而 好学, 如炳烛 之光。 ——刘 向 63、三军可教师 是幸福 ,不如 说好的 教师是 不幸。 ——海 贝尔 65、接受挑战,就可以享受胜利的喜悦 。——杰纳勒 尔·乔治·S·巴顿

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

并口18-25是地线,其他线分成三类,8根数据线,可进行数据输出,5根状态线, 输入,四根控制线,输出。设置成JTAG口。

主系统通用 10针标准 配置/下载接口

PIN1

目标板10针标准 配置接口

OTP配置器件插座 配置器件插座 配置器件

将编程完毕的配置 器件插在相应的 电路系统上

4.2.4 PAL结构原理 结构原理

4.2 简单 简单PLD结构原理 结构原理

2.2.4 PAL结构原理 结构原理

4.2.5 GAL结构原理 结构原理

4.2 简单 简单PLD结构原理 结构原理

4.2.5 GAL结构原理 结构原理

(1)寄存器模式 )

4.2 简单 简单PLD结构原理 结构原理

(2)复合模式 ) 1、组合输出双向口结构 、

2.5.2 JTAG边界扫描测试 边界扫描测试

4.5 硬件测试

4.5.2 JTAG边界扫描测试 边界扫描测试

4.6 PLD产品概述 产品概述

4.6.1 Lattice公司的 公司的PLD器件 公司的 器件

1. ispLSI系列器件 系列器件 2. MACHXO系列 系列 3. MACH4000系列 系列 4. LatticeSC FPGA系列 系列 5. LatticeECP3 FPGA系列 系列

其他PLD公司: 公司: 其他 公司 ACTEL公司: ACT1/2/3、40MX 公司: 公司 、 ATMEL公司:ATF1500AS系列、40MX 公司: 系列、 公司 系列 CYPRESS公司 公司 QUIKLOGIC公司 公司

SO MUCH IC!

FPGA CPLD

三大可编程逻辑器件公司样片

封装形式 20 脚 PL 、32 脚 TQFP CC 8 脚 PDIP、20 脚PLCC 8 脚 PDIP、20 脚PLCC 8 脚 PDIP、20 脚PLCC、32 脚TQFP 8 脚 PDIP、20 脚PLCC、32 脚TQFP 8 脚 PDIP、20 脚PLCC、32 脚TQFP

ALTERA的CPLD器件编程

4.6 PLD产品概述 产品概述

4.6.4 Actel公司的 公司的PLD器件 公司的 器件

4.6.5 Altera的FPGA配置方式 的 配置方式

4.7 CPLD/FPGA的编程与配置 的编程与配置

技术。 (1)基于电可擦除存储单元的 )基于电可擦除存储单元的EEPROM或Flash技术。 或 技术 查找表的编程单元。 (2)基于 )基于SRAM查找表的编程单元。 查找表的编程单元 (3)基于一次性可编程反熔丝编程单元。 )基于一次性可编程反熔丝编程单元。

2.4.1 查找表逻辑结构

4.4 FPGA的结构及其工作原理 的结构及其工作原理

2.4.1 查找表逻辑结构

4.4.2 Cyclone III 系列器件的结构与 原理

4.4.2 Cyclone III系列器件的结构与原理 系列器件的结构与原理

4.4.2 Cyclone III系列器件的结构与原理 系列器件的结构与原理

4.6 PLD产品概述 产品概述

4.6.3 Altera公司的 公司的PLD器件 公司的 器件

1. Stratix 4/6 系列 系列FPGA 2. Cyclone 4系列 系列FPGA 系列 3. Cyclone系列 系列FPGA(低成本 系列 (低成本FPGA) ) 4. Cyclone II系列 系列FPGA 系列 5. Cyclone III系列 系列FPGA 系列 6. MAX系列 系列CPLD 系列 7. MAX II系列器件 系列器件 8. Altera宏功能块及 核 宏功能块及IP核 宏功能块及

4.3 CPLD的结构及其工作原理 的结构及其工作原理

4.3 CPLD的结构及其工作原理 的结构及其工作原理

全局 清零 并 行

2 快速输入选择

全局 时钟 来自 I/O引脚

扩展项

寄存器 旁 路

PRN D Q ENA EN CLRN

通往 I/O 模块

乘 积 项 选 择 矩 阵

时钟 清零 选择

清零 共 享 辑

2.4.2 Cyclone III系列器件的结构与原理 系列器件的结构与原理

4.4.2 Cyclone III系列器件的结构与原理 系列器件的结构与原理

4.4 FPGA的结构及其工作原理 的结构及其工作原理

4.4.2 Cyclone III系列器件的结构与原理 系列器件的结构与原理

4.4 FPGA的结构及其工作原理 的结构及其工作原理

4.6 PLD产品概述 产品概述

4.6.2 Xilinx公司的 公司的PLD器件 公司的 器件

1. Virtex-6系列 系列FPGA 系列 2. Spartan-6器件系列 器件系列 3. XC9500/XC9500XL系列 系列CPLD 系列 4. Xilinx Spartan-3A系列器件 系列器件 5. Xilinx的IP核 的 核

2.4.2 Cyclone III系列器件的结构与原理 系列器件的结构与原理

4.4 FPGA的结构及其工作原理 的结构及其工作原理

4.4.2 Cyclone III系列器件的结构与原理 系列器件的结构与原理

4.4 FPGA的结构及其工作原理 的结构及其工作原理

4.4.2 Cyclone III系列器件的结构与原理 系列器件的结构与原理

ALTERA

FPGA: FLEX系列:10K、10A、10KE,EPF10K30E APEX系列:20K、20KE EP20K200E ACEX系列:1K系列 EP1K30、EP1K100 STRATIX系列:EP1系列 EP1S30、EP1S120 CPLD: MAX7000/S/A/B系列:EPM7128S MAX9000/A MAX9000/A系列 FPGA: XC3000系列, XC4000系列, XC5000系列 Virtex系列 SPARTAN系列:XCS10、XCS20、XCS30 CPLD: XC9500系列:XC95108、XC95256

第4章 可编程逻辑器件PLD原理及应用 可编程逻辑器件PLD原理及应用

半整数与奇数分频电路设计

半整数与奇数分频电路设计

接下页

半整数与奇数分频电路设计

接上页

半整数与奇数分频电路设计

4.1 概 述

4.1 概 述

4.1.1 PLD的发展历程 的发展历程

4.1.2 PLD分类 分类

4.2 简单 简单PLD结构原理 结构原理

逻辑阵列

逻

扩展项

通往 PIA

4.3 CPLD的结构及其工作原理 的结构及其工作原理

4.3 CPLD的结构及其工作原理 的结构及其工作原理

1. 逻辑阵列块 逻辑阵列块LAB

4.3 CPLD的结构及其工作原理 的结构及其工作原理

4. 宏单元

三种时钟输入模式 (1)全局时钟信号。 )全局时钟信号。 (2)全局时钟信号由高电平有效的时钟信号使能。 )全局时钟信号由高电平有效的时钟信号使能。 (3)用乘积项实现一个阵列时钟。 )用乘积项实现一个阵列时钟。

4.7.1 CPLD在系统编程 在系统编程

4.7 CPLD/FPGA的编程与配置 的编程与配置

4.7.1 CPLD在系统编程 在系统编程

4.7 CPLD/FPGA的编程与配置 的编程与配置

4.7.2 FPGA配置方式 配置方式

4.7 CPLD/FPGA的编程与配置 的编程与配置

4.7.3 FPGA专用配置器件 专用配置器件

4.2.2 PROM结构原理 结构原理

4.2 简单 简单PLD结构原理 结构原理

4.2.2 PROM结构原理 结构原理

4.2 简单 简单PLD结构原理 结构原理

4.2.3 PLA结构原理 结构原理

4.2 简单 简单PLD结构原理 结构原理

4.2.3 PLA结构原理 结构原理

4.2 简单 简单PLD结构原理 结构原理

4.3 CPLD的结构及其工作原理 的结构及其工作原理

3. 扩展乘积项

4.3 CPLD的结构及其工作原理 的结构及其工作原理

4. 可编程连线阵列 可编程连线阵列PIA

4.3 CPLD的结构及其工作原理 的结构及其工作原理

5. I/O控制块 控制块

4.4 FPGA的结构及其工作原理 的结构及其工作原理

4.7 CPLD/FPGA的编程与配置 的编程与配置

4.7.4 使用单片机配置 使用单片机配置FPGA

4.7 CPLD/FPGA的编程与配置 的编程与配置

4.7.4 使用单片机配置 使用单片机配置FPGA

4.7 CPLD/FPGA的编程与配置 的编程与配置

4.7.5 使用 使用CPLD配置 配置FPGA 配置

XILINX

4.6 PLD产品概述 产品概述

LATTICE VANTIS (AMD) ) CPLD

ispLSI系列:1K、2K、3K、5K、8K 系列: 、 、 、 、 系列 ispLSI1016 、ispLSI2032、 、 ispLSI1032E、ispLSI3256A 、 MACH系列 系列 ispPAC系列: 系列: 系列

在系统可编程( 在系统可编程(ISP)技术 )

未编程前先焊 接安装 减少对器 件的触摸 和损伤 不计较器 件的封装 形式

系统内编程--ISP 系统内编程

允许一般的 存储 样机制造方 便 支持生产和 测试流程中 的修改

在系统现场重 编程修改 允许现场硬 件升级 迅速方便地 提升功能

ALTERA 的 ByteBlaster(MV)下载接口 ByteBlaster(MV)下载接口

4.2 简单 简单PLD结构原理 结构原理

(2)复合模式 ) 2、组合输出结构 、

4.2 简单 简单PLDห้องสมุดไป่ตู้构原理 结构原理

(3)简单模式 ) 1、反馈输入结构 、