MCS_51单片机的时钟电路

单片机技术复习题(学生用)

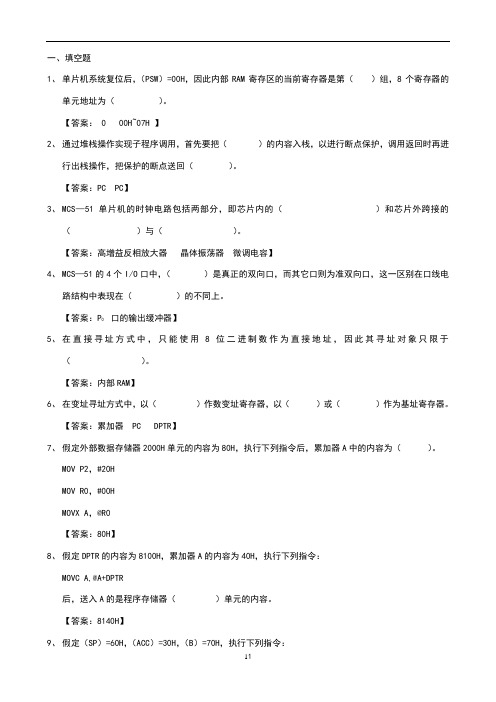

一、填空题1、单片机系统复位后,(PSW)=00H,因此内部RAM寄存区的当前寄存器是第()组,8个寄存器的单元地址为()。

【答案: 0 00H~07H 】2、通过堆栈操作实现子程序调用,首先要把()的内容入栈,以进行断点保护,调用返回时再进行出栈操作,把保护的断点送回()。

【答案:PC PC】3、MCS—51单片机的时钟电路包括两部分,即芯片内的()和芯片外跨接的()与()。

【答案:高增益反相放大器晶体振荡器微调电容】4、MCS—51的4个I/O口中,()是真正的双向口,而其它口则为准双向口,这一区别在口线电路结构中表现在()的不同上。

【答案:P0 口的输出缓冲器】5、在直接寻址方式中,只能使用8位二进制数作为直接地址,因此其寻址对象只限于()。

【答案:内部RAM】6、在变址寻址方式中,以()作数变址寄存器,以()或()作为基址寄存器。

【答案:累加器 PC DPTR】7、假定外部数据存储器2000H单元的内容为80H,执行下列指令后,累加器A中的内容为()。

MOV P2,#20HMOV R0,#00HMOVX A,@R0【答案:80H】8、假定DPTR的内容为8100H,累加器A的内容为40H,执行下列指令:MOVC A,@A+DPTR后,送入A的是程序存储器()单元的内容。

【答案:8140H】9、假定(SP)=60H,(ACC)=30H,(B)=70H,执行下列指令:PUSH ACCPUSH B后,SP的内容为(62H),61H单元的内容为(),62H单元的内容为()。

【答案:30H 70H】10、假定已把PSW的内容压入堆栈,再执行如下指令:MOV R0,SPORL @R0,#38HPOP PSW实现的功能是()【答案:修改PSW的 RS0、 RS1、 F0位为1】11、假定(A)=56H,(R5)=67H。

执行指令:ADD A,R5DA后,累加器A的内容为( ),CY的内容为()。

【答案:23H 1】12、假定(A)=50H,(B)=0A0H,执行指令:MUL AB后,寄存器B的内容为(),累加器A的内容为(),CY的内容为( ),OV的内容为()。

单片机原理 第2章 MCS-51单片机体系结构

2.4.2 MCS-51单片机数据存储器

2.4.2 MCS-51单片机数据存储器

1. 工作寄存器区

字节地址为00H~1FH的32个单元是4组通用工作寄存器区,每组占用8个 字节,都标记为R0~R7。在某一时刻,CPU只能使用其中的一组工作寄存 器,工作寄存器的选择由程序状态字寄存器PSW中RS1、RS0两位来确定 ,如表2-3所示。

2. 数据总线DB 数据总线宽度为8位(D0~D7),由P0提供。

3. 控制总线CB 控制总线由P3口的第二功能状态和4根独立控制线RESET、 和ALE组成。

2.3 MCS-51单片机的中央处理器

• 8051系列单片机的中央处理器CPU是单片机 的指挥中心和执行机构,它的作用是产生合适的 时序,读入和分析每条指令代码,根据每条指令 代码的功能要求,指挥并控制单片机的有关部件 和器件,具体执行指定的操作。

2.2.3 并行I/O引脚

3. P2口

P2口,为准双向I/O口,具有内部上拉电阻。一共8位,有P2.0~P2.7共8 条引脚。当8051系列单片机扩展外部存储器及I/O接口芯片时,P2口作为 地址总线(高8位),和P0输出的低8位地址一起构成16位地址,可以寻址 64KB的地址空间。

P2口位结构图如图2-3 (c)所示,它比P1口多了 一个转换控制部分,当P2 与P0配合作为“地址/数据总 线”方式下的高8位数据线 (A8~A15)时,CPU将写 控制信号“1”使MUX切换到 右边,在“地址/数据总线” 方式下,无论P2口剩余多 少地址线,均不能被用于 普通I/O操作。

(2)控制引脚—— 、

第1章 MCS-51单片机结构

一个8位的CPU。 程序存储器:4KBROM。

128字节RAM。

两个16位可编程定时器/计数器。 可寻址64KB外部数据存储器和64KB外部程序存储器的控制电路。

32条可编程的I/O线(四个8位并行I/O端口)。

一个可编程全双工串行口。 具有两个优先级嵌套的中断结构。

★ 掌握51系列单片机各存储空间的地址分配、使用特点。

位名称

1.3 特殊功能寄存器

CY:进/借位标志,反映最高位的进位借位情况,加法为进位、 减法为借位。CY=1,有进/借位 ; CY=0,无进/借位。 AC:辅助进/借位标志,反映高半字节与低半字节之间的进/借 位,AC=1有进/借位; AC=0无进/借位 。 FO:用户标志位,可由用户设定其含义。 RS1,RS0:工作寄存器组选择位。 OV:溢出标志,反映补码运算的运算结果有无溢出 有溢出 OV=1,无溢出OV=0。 -:无效位。 P:奇偶标志,运算结果有奇个“1”,P=1;运算结果有偶个“1”, P=0。

1.5 引脚功能

8XX51单片机有44引脚的方形 封装和40个引脚的双列直插式封 装形式,最常用的40个引脚DIP 封装。

各个引脚的功能如下: Vss:接地端。 Vcc:电源端,接+5V。 XTAL1,XTAL2: 接外部晶体或外部时 钟。 RST/VPD:①复位信号输入。 ②接备用电源,当VCC掉电

在中断入口地址中通常用一条无条件转移指令,转到 中断处理子程序。

1.2.2 外部数据储存器

用于存放随机读写的数据;

外部数据存储器和外部I/O口统一编址。 控制信号相同,使用相同的MOVX指令访问。 最多可扩展64KB外部数据存储器

1.2.3 内部数据储存器

基于51的电子闹钟设计报告(附原理图、PCB图、程序)

基于51的电⼦闹钟设计报告(附原理图、PCB图、程序)成都信息⼯程学院第五届嵌⼊式创新技术⼤赛基于MCS51的智能电⼦闹钟设计报告姓名学院班级实物图⽬录1.电⼦时钟的设计原理和⽅法 (1)1.1设计原理 (1)1.2 硬件电路的设计 (1)1.2.1 STC89C51RC简介 (1)1.2.2 键盘电路的设计 (2)1.2.3蜂鸣器驱动电路 (3)1.2.4 数码管驱动电路 (3)1.2.5 电源电路 (4)1.3软件部分的设计 (4)1.3.1主程序部分的设计 (4)1.3.2中断计时器及时间进位 (5)1.3.3 闹钟⼦函数 (7)1.3.4 按键扫描 (8)1.3.5 时钟闹钟设置 (9)1.3.6 显⽰数字函数 (10)1.3.7 显⽰界⾯函数 (10)1.3.8 闹钟记录及读取 (11)2.硬件调试 (13)附录A:电路原理图 (15)附录B:电路PCB图 (16)附录C:源程序 (17)1.电⼦时钟的设计原理和⽅法1.1设计原理系统框图1.2硬件电路的设计1.2.1 STC89C51RC简介STC89C52R CSTC89C51RC是⼀种带8K闪烁可编程可擦除只读存储器(FPETOM-FlashProgrammabalandErasableReadOnlyMemory )的低电压、⾼性能CMOS8位微型处理器,即单⽚机芯⽚。

单⽚机的可擦除只读存储器可以反复擦除1000次,内部FLASH 擦写次数为100000次以上。

该芯⽚使⽤⾼密度⾮易失存储制造技术,与⼯业标准的MCS-51指令集和输出管脚相兼容。

由于将多功能8位CPU 和闪烁存储器集成在单个芯⽚中,使得STC89C51RC 成为了⼀种性价⽐极⾼的微型处理器芯⽚,在许多电路设计中都得到了应⽤。

STC89C51RC 单⽚机特点:⼯作电压:5.5V-3.4V ⼯作频率:0-40MHz ⽤户应⽤程序空间:8K ⽚上集成128*8RAMISP (在系统可编程)/IAP (在应⽤可编程),⽆需专⽤编程器/仿真器可通过串⼝(P3.0/P3.1)直接下载⽤户程序EEPROM 功能共3个16位定时器/计数器,其中定时0还可以当成2个8位定时器使⽤外部中断4路通⽤异步串⾏⼝(UART ),还可⽤定时器软件实现多个UART ⼯作温度范围:0-75℃引脚说明:VCC:供电电压 GND :接地P0:P0是⼀个8位漏级开路双向I/O ⼝,低8位地址复⽤总线端⼝。

单片机原理与应用复习题【附答案】

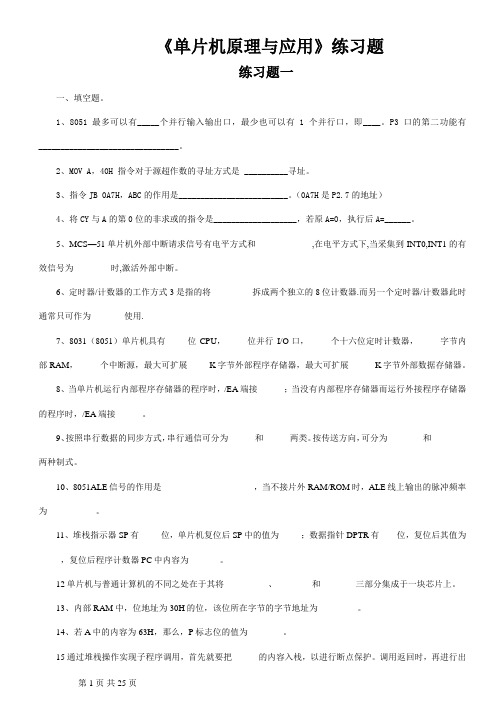

《单片机原理与应用》练习题练习题一一、填空题。

1、8051最多可以有_____个并行输入输出口,最少也可以有1个并行口,即____。

P3口的第二功能有________________________________。

2、MOV A,40H 指令对于源超作数的寻址方式是 __________寻址。

3、指令JB 0A7H,ABC的作用是_________________________。

(0A7H是P2.7的地址)4、将CY与A的第0位的非求或的指令是___________________,若原A=0,执行后A=______。

5、MCS—51单片机外部中断请求信号有电平方式和____________ ,在电平方式下,当采集到INT0,INT1的有效信号为________ 时,激活外部中断。

6、定时器/计数器的工作方式3是指的将_________ 拆成两个独立的8位计数器.而另一个定时器/计数器此时通常只可作为_______ 使用.7、8031(8051)单片机具有_____位CPU,_____位并行I/O口,_____个十六位定时计数器,_____字节内部RAM,_____个中断源,最大可扩展_____K字节外部程序存储器,最大可扩展______K字节外部数据存储器。

8、当单片机运行内部程序存储器的程序时,/EA端接______;当没有内部程序存储器而运行外接程序存储器的程序时,/EA端接______。

9、按照串行数据的同步方式,串行通信可分为______和______两类。

按传送方向,可分为________和________两种制式。

10、8051ALE信号的作用是_____________________,当不接片外RAM/ROM时,ALE线上输出的脉冲频率为___________。

11、堆栈指示器SP有_____位,单片机复位后SP中的值为_____;数据指针DPTR有____位,复位后其值为_____,复位后程序计数器PC中内容为_______。

第二章 MCS-51系列单片机结构与工作

2.3.1运算器 2.3.1运算器

• 4.程序状态字寄存器PSW • 程序状态字寄存器PSW是8位寄存器,用来存储当前指令执行后的状 态,便于程序查询和判别。程序状态字寄存器各位的定义如表2-2。

• (1)进位标志位C:又名CY,在加法和减法运算时, 表示运算结果 最高位的进位或借位情况。

2.3.1运算器 2.3.1运算器

2.2.1 MCS-51系列单片机的引脚与功能 MCS-51系列单片机的引脚与功能

• (8)XTAL2(18脚):片内振荡电路反向放大器的输出端,采用外 部时钟时该引脚为振荡信号的输入端。 • (9)P0口:P0.0~P0.7依次为第39~32脚,P0口除了可以作普通 的双向I/O口使用外,也可以在访问外部存储器时用作低8位地址线和 数据总线。 • (10)P1口:P1.0~P1.7依次为第1~8脚,P1口是带内部上拉电 阻的双向I/O口,向P1口写入“1” 时,P1口被内部上拉为高电平, 可用作输入口。当作为输出脚时,被外部拉低的P1口会因为内部上拉 电阻的存在而输出电流。

单片机时钟电路的原理

单片机时钟电路的原理

单片机时钟电路的原理是指为单片机系统提供稳定、准确的时钟信号,以保证单片机能够按时序要求进行数据处理和控制操作的电路。

时钟信号是单片机系统的时间基准,所有的操作都依赖于时钟信号的驱动。

单片机的时钟电路主要由晶体振荡电路、分频电路和时钟分配电路组成。

晶体振荡电路是基础也是核心部分,通常采用由晶体振荡器和适当的放大电路构成的谐振回路。

晶体振荡器的工作原理是利用晶体的谐振特性,在输入信号作用下,晶体会产生自激振荡。

在振荡回路中,晶体振荡器输出的信号通过放大电路进行放大,经过滤波后得到一个稳定的、准确的时钟信号。

分频电路是时钟信号的处理电路,它能调节时钟信号的频率和周期。

分频器一般采用可编程的分频器,通过设置分频系数,将晶体振荡器输出的高频信号分频为单片机系统所需的低频信号。

分频电路的作用是根据单片机系统的需要,生成适合的时钟信号频率和周期。

时钟分配电路主要是将分频器输出的时钟信号分配给单片机系统中的不同模块和外设。

时钟分配电路一般由多路选择器和时序逻辑电路构成。

多路选择器能根据输入控制信号选择相应的时钟输入源,时序逻辑电路则根据时序要求,对时钟信号进行延时、分频或生成不同的时钟信号。

通过时钟分配电路,可以将时钟信号送达给单片机的各个模块,并控制不同模块的工作时间和时序。

总体来说,单片机时钟电路的原理是通过晶体振荡器产生稳定的高频信号,经过分频电路减小频率,然后经过时钟分配电路将时钟信号分配给不同的模块和外设。

这样,单片机系统的各个模块和外设可以根据时钟信号的驱动进行数据处理和控制操作,实现各种功能。

基于C51单片机的数字时钟课程设计(C语言,带闹钟).

单片机技术课程设计数字电子钟学院:班级:姓名:学号:教师:摘要电子钟在生活中应用非常广泛,而一种简单方便的数字电子钟则更能受到人们的欢迎。

所以设计一个简易数字电子钟很有必要。

本电子钟采用AT89C52单片机为核心,使用12MHz 晶振与单片机AT89C52 相连接,通过软件编程的方法实现以24小时为一个周期,同时8位7段LED数码管(两个四位一体数码管)显示小时、分钟和秒的要求,并在计时过程中具有定时功能,当时间到达提前定好的时间进行蜂鸣报时。

该电子钟设有四个按键KEY1、KEY2、KEY3、KEY4和KEY5键,进行相应的操作就可实现校时、定时、复位功能。

具有时间显示、整点报时、校正等功能。

走时准确、显示直观、运行稳定等优点。

具有极高的推广应用价值。

关键词:电子钟 AT89C52 硬件设计软件设计目录一、数字电子钟设计任务、功能要求说明及方案介绍 (4)1.1 设计课题设计任务 (4)1.2 设计课题的功能要求说明 (4)1.3 设计课的设计总体方案介绍及工作原理说明 (4)二、设计课题的硬件系统的设计 (5)2.1硬件系统各模块功能简要介绍 (5)2.1.1 AT89C52简介 (5)2.1.2 按键电路 (6)三、设计课题的软件系统的设计 (6)3.1 使用单片机资源的情况 (6)3.2 软件系统个模块功能简要介绍 (7)3.3 软件系统程序流程框图 (7)3.4 软件系统程序清单 (7)四、设计课题的设计结论、仿真结果、误差分析 (9)4.1 设计结论及使用说明 (9)4.2 仿真结果 (10)结束语 (12)参考文献 (12)附录 (13)附录A:程序清单 (13)一、数字电子钟设计任务、功能要求说明及方案介绍1.1 设计课题设计任务设计一个具有特定功能的电子钟。

具有时间显示,并有时间设定,时间调整功能。

1.2 设计课题的功能要求说明设计一个具有特定功能的电子钟。

该电子钟上电或按键复位后能自动显示系统提示符“d.1004-22”,进入时钟准备状态;第一次按电子钟启动/调整键,电子钟从12时59分0秒开始运行,进入时钟运行状态;按电子钟S5键,则电子钟进入时钟调整状态,此时可利用各调整键调整时间,调整结束后可按S5键再次进入时钟运行状态。

MCS51单片机时钟与复位电路

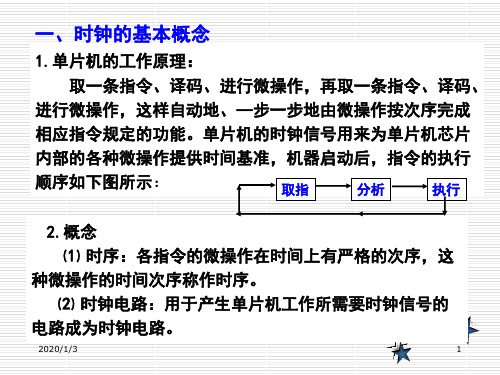

1.单片机的工作原理:

取一条指令、译码、进行微操作,再取一条指令、译码、

进行微操作,这样自动地、—步一步地由微操作按次序完成 相应指令规定的功能。单片机的时钟信号用来为单片机芯片

内部的各种微操作提供时间基准,机器启动后,指令的执行

顺序如下图所示:

取指

分析

执行

2.概念

⑴ 时序:各指令的微操作在时间上有严格的次序,这

2020/1/3

15

复位后各寄存器的初态如下表4-1所示,其意义为: ⑴ P0~P3=FFH,相当于各口锁存器已写入1,此时可用于输出/输入; ⑵ SP=07H,堆栈指针指向片内RAM的07H单元(第一个入栈内容将写入 08H中); ⑶ IP、IE和PCON的有效值为0,各中断源处于低优先级且均被关断,串 行通信的波特率不加倍; ⑷ PSW=00H,当前工作寄存器为0组。

2020/1/3

14

Байду номын сангаас

第4节 MCS-51系列单片机的复位与掉电处理

一、复位与复位电路 1.复位:是单片机的初始化操作,以便使CPU和系统中其 他部件都处于一个确定的状态,并从这个状态开始工作。

当单片机系统在运行出错或操作错误使系统处于死 锁存时,也可按复位键重新启动。

单片机复位后,PC内容初始化为0000H,那么单片机 就从0000H单元开始执行程序。片内RAM为随机值,运行 中的复位操作不改变片内RAM的内容。

2020/1/3

8

4. 指令周期 是CPU执行一条指令所需要的时间为指令周期。 MCS-51单片机指令包含1个或2个或4个机器周期。 若采用6MHz晶振,则振荡周期为1/6μs,机器周期为

2μs、4μs或8μs。

MCS-51单片机的硬件结构

XTAL1 19

VSS

20

8031 8051 8751

40 VCC 39 P0.0 38 P0.1 37 P0.2 36 P0.3 35 P0.4 34 P0.5 33 P0.6 32 P0.7 31 EA/Vpp 30 ALE/PROG 29 PSEN 28 P2.7

27 P2.6 26 P2.5 25 P2.4 24 P2.3

P1.0 1 P1.1 2 P1.2 3 P1.3 4

P1.4 5 P1.5 6 P1.6 7 P1.7 8 RST/VPD 9

RXD/P3.0

10

TXD/P3.1

11

INT0/P3.2

12

INT1/P3.3

13

T0/P3.4

14

T1/P3.5

15

WR/P3.6

16

RD/P3.7

17

XTAL2 18

17

RD(外部数据存储器读脉

P3.7

冲)

返回本节

2.2 MCS-51单片机的引脚及片外总线结构

2.2.1 MCS-51单片机芯片引脚描述 2.2.2 MCS-51单片机的片外总线结构

返回本章首页

2.2.1 MCS-51单片机芯片引脚描述

图2-7为MCS-51单片机的引脚配置图。 1.主电源引脚VCC和VSS 2.外接晶振引脚XTAL1和XTAL2 3.控制或其他电源复用引脚RST/ VPD、ALE/、 和/VPP 4.输入/输出引脚P0、P1、P2、P3(共32根)

VCC

P2.7 PP22..56 P2.4 P2.3 P2.2 P2.1 P2.0 PPP000...756

P0.3 P0.2 P0.1 P0.0

ALE

《单片机原理及应用》期末考试试题A(潘)

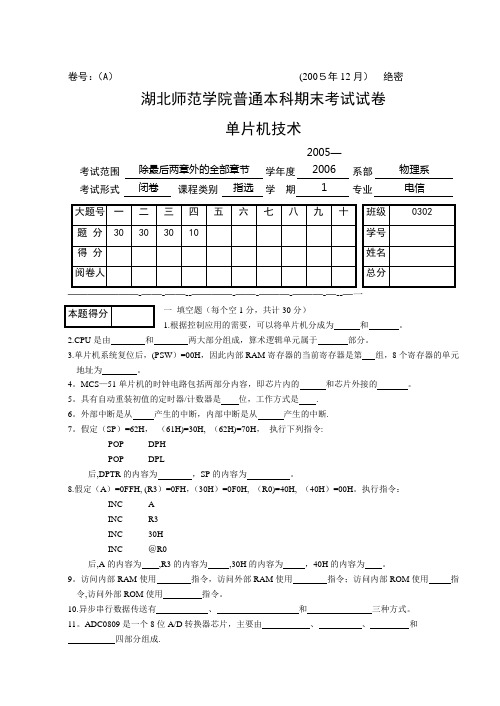

卷号:(A)(2005年12月)绝密湖北师范学院普通本科期末考试试卷单片机技术考试范围除最后两章外的全部章节学年度2005—2006 系部物理系考试形式闭卷课程类别指选学期 1 专业电信———————-——-——--————-——-———-———-—--—一一填空题(每个空1分,共计30分)1.根据控制应用的需要,可以将单片机分成为和。

2.CPU是由和两大部分组成,算术逻辑单元属于部分。

3.单片机系统复位后,(PSW)=00H,因此内部RAM寄存器的当前寄存器是第组,8个寄存器的单元地址为。

4。

MCS—51单片机的时钟电路包括两部分内容,即芯片内的和芯片外接的。

5。

具有自动重装初值的定时器/计数器是位,工作方式是.6。

外部中断是从产生的中断,内部中断是从产生的中断.7。

假定(SP)=62H,(61H)=30H, (62H)=70H,执行下列指令:POP DPHPOP DPL后,DPTR的内容为,SP的内容为。

8.假定(A)=0FFH, (R3)=0FH,(30H)=0F0H, (R0)=40H, (40H)=00H。

执行指令:INC AINC R3INC 30HINC @R0后,A的内容为,R3的内容为,30H的内容为,40H的内容为。

9。

访问内部RAM使用指令,访问外部RAM使用指令;访问内部ROM使用指令,访问外部ROM使用指令。

10.异步串行数据传送有、和三种方式。

11。

ADC0809是一个8位A/D转换器芯片,主要由、、和四部分组成.二 选择题(只有一个答案是正确的,每小题3分,共计30分)1。

以下有关PC 和DPTR 的结论中错误的是(A ) DPTR 是可以访问的而PC 不能访问;(B)它们都是16位的寄存器;(C)它们都具有加“1”功能;(D )DPTR 可以分为2个8位的寄存器使用,但PC 不能 2.在MCS —51中(A) 具有独立的专用的地址线;(B) 由P0口和P1口的口线作地址线; (C ) 由P0口和P2口的口线作地址线;(D ) 由P1口和P2口的口线作地址线;3.以下运算中对溢出标志OV 没有影响或不受OV 影响的运算是(A ) 逻辑运算;(B) 符号数加减法运算;(C) 乘法运算;(D ) 除法运算 4.在工作方式0下,计数器是由TH 的全部8位和TL 的5位组成,因此其计数范围是 (A) 1~8192; (B ) 0~8191; (C) 0~8192;(D ) 1~40965。

51单片机定时时钟工作原理

51单片机定时时钟工作原理51单片机(也被称为8051微控制器)的定时器/计数器是一个非常有用的功能,它允许用户在特定的时间间隔内执行任务。

下面是其基本工作原理:1. 结构:8051单片机通常包含两个定时器/计数器,称为Timer0和Timer1。

每个定时器都有一个16位的计数器,可以用来跟踪经过的时间或事件。

2. 时钟源:定时器的核心是一个振荡器或外部时钟源,为计数器提供脉冲。

通常,这个时钟源可以是内部的,也可以是外部的。

内部时钟源通常基于系统时钟,而外部时钟源则直接从外部硬件输入。

3. 计数过程:每当振荡器产生一个脉冲,计数器就会增加(对于向上计数的定时器)或减少(对于向下计数的定时器)一个单位。

这取决于定时器的模式。

4. 溢出:当计数器达到其最大值(对于向上计数的定时器)或达到0(对于向下计数的定时器)时,会发生溢出事件。

这会导致一个中断,可以用来执行特定的任务或操作。

5. 分频:在某些模式下,计数器的输出可以用来分频系统时钟,从而产生更精确的定时器时钟。

6. 预分频器:预分频器允许用户设置一个值,该值决定了振荡器的输入脉冲被分频的次数。

这有助于控制计数器的速度,从而控制定时器的精度。

7. 工作模式:8051微控制器支持多种定时器模式,包括正常模式、自动重装载模式和比较模式。

每种模式都有其特定的应用和行为。

8. 中断:当定时器溢出时,可以产生一个中断。

这意味着微控制器可以暂时停止当前的任务,转而处理与定时器相关的特定任务。

通过合理配置和使用这些定时器/计数器,开发人员可以在8051单片机上实现精确的时间控制和事件调度。

这对于实现诸如延时、精确计时和脉冲生成等功能非常有用。

51单片机的时钟工作原理

51单片机的时钟工作原理-标准化文件发布号:(9556-EUATWK-MWUB-WUNN-INNUL-DDQTY-KII51单片机时钟电路原理2.4.2 时钟电路和时序1. 时钟电路在MCS-51单片机片内有一个高增益的反相放大器,反相放大器的输入端为XTAL1,输出端为XTAL2,由该放大器构成的振荡电路和时钟电路一起构成了单片机的时钟方式。

根据硬件电路的不同,单片机的时钟连接方式可分为内部时钟方式和外部时钟方式,如图2.11所示。

(a)内部方式时钟电路(b)外接时钟电路图2.11 时钟电路内部时钟原理图(就是一个自激振荡电路)在内部方式时钟电路中,必须在XTAL1和XTAL2引脚两端跨接石英晶体振荡器和两个微调电容构成振荡电路,通常C1和C2一般取30pF,晶振的频率取值在1.2MHz~12MHz之间。

对于外接时钟电路,要求XTAL1接地,XTAL2脚接外部时钟,对于外部时钟信号并无特殊要求,只要保证一定的脉冲宽度,时钟频率低于12MHz即可。

晶体振荡器的振荡信号从XTAL2端送入内部时钟电路,它将该振荡信号二分频,产生一个两相时钟信号P1和P2供单片机使用。

时钟信号的周期称为状态时间S,它是振荡周期的2倍,P1信号在每个状态的前半周期有效,在每个状态的后半周期P2信号有效。

CPU就是以两相时钟P1和P2为基本节拍协调单片机各部分有效工作的。

2. 指令时序我们将单片机的基本操作周期称作机器周期,一个机器周期由6个状态组成,每个状态由两个时相P1和P2构成,故一个机器周期可依次表示为S1P1,S1P2,…,S6P1,S6P2,即一个机器共有12个振荡脉冲。

为了大家便于分析CPU的时序,在此先对以下几个概念作一介绍。

(1)振荡周期振荡周期指为单片机提供定时信号的振荡源的周期或外部输入时钟的周期。

(2)时钟周期时钟周期又称作状态周期或状态时间S,它是振荡周期的两倍,它分为P1节拍和P2节拍,通常在P1节拍完成算术逻辑操作,在P2节拍完成内部寄存器之间的传送操作。

51单片机时钟电路作用

51单片机时钟电路作用

51单片机是一种广泛应用于嵌入式系统中的微控制器,它的工作需要一个稳定的时钟信号。

因此,51单片机时钟电路是非常重要的,它的作用是提供一个稳定的时钟信号,以确保单片机的正常工作。

时钟信号是指一种周期性的信号,它可以用来同步各种电子设备的工作。

在51单片机中,时钟信号的频率通常为12MHz或者11.0592MHz,这个频率是由晶振产生的。

晶振是一种能够产生稳定频率的元件,它的工作原理是利用晶体的振荡特性来产生一个稳定的频率信号。

51单片机时钟电路通常由晶振、电容和晶振驱动电路组成。

晶振驱动电路的作用是将晶振产生的信号放大,并将其传递给单片机。

电容的作用是为晶振提供稳定的电源,以确保晶振的稳定性。

在51单片机中,时钟信号的作用非常重要。

它可以用来控制单片机的运行速度,以及各种外设的工作。

例如,当单片机需要进行定时器中断时,时钟信号可以用来控制定时器的计数速度。

当单片机需要进行串口通信时,时钟信号可以用来控制串口的波特率。

51单片机时钟电路是单片机工作的基础,它的作用非常重要。

只有在稳定的时钟信号下,单片机才能够正常工作,从而实现各种功能。

因此,在设计嵌入式系统时,时钟电路的设计是非常重要的,需要仔细考虑。