北京理工大学数电期末试卷(含答案)

数字电子技术期末复习试卷及答案(四套)

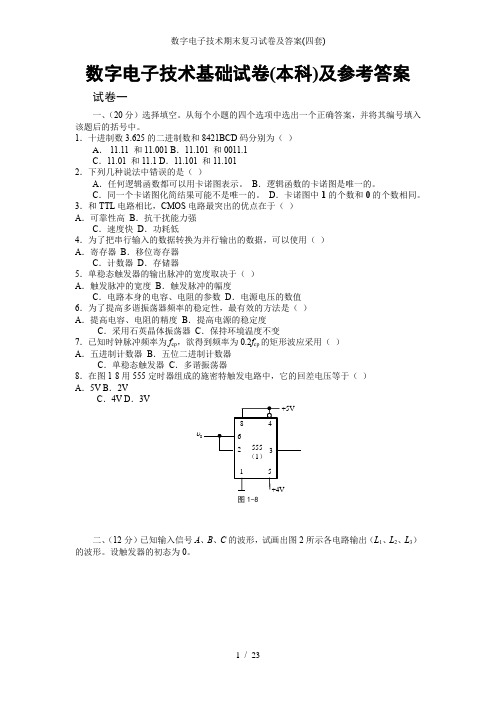

二、(12分)逻辑电路如图2a、b、c所示。试对应图d所示输入波形,分别画出输出端L1、、L2和L3的波形。(设触发器的初态为0)

(a)(b)

(c ) (d)

图2

三、(12分)发由全加器FA、2-4线译码器和门电路组成的逻辑电路如图3 a所示。试在图b中填写输出逻辑函数L的卡诺图(不用化简)。

试卷二

一、(18分)选择填空题

1. 用卡诺图法化简函数F(ABCD)= (0,2,3,4,6,11,12)+ (8,9,10,13,14,15)得最简与-或式________。

A. B.

C. D.

2. 逻辑函数F1、F2、F3的卡诺图如图1-2所示,他们之间的逻辑关系是。

A.F3=F1•F2B.F3=F1+F2

C.4.25V D.-8.25V

图1-5

6.用1K×4位的DRAM设计4K×8位的存储器的系统需要的芯片数和地址线的根数是( )

A.16片,10根 B.8片,10根

C.8片,12根 D.16片,12根

7.某逻辑门的输入端A、B和输出端F的波形图1-7所示,F与A、B的逻辑关系是:

A. 与非; B. 同或; C.异或; D. 或。

图2

三、(10分)如图3所示,为检测水箱的液位,在A、B、C、三个地方安置了三个水位检测元件,当水面低于检测元件时,检测元件输出低电平,水面高于检测元件时,检测元件输出高电平。试用与非门设计一个水位状态显示电路,要求:当水面在A、B之间的正常状态时,仅绿灯G亮;水面在B、C间或A以上的异常状态时,仅黄Y灯亮;水面在C以下的危险状态时,仅红灯R亮。

三、输出逻辑函数L的卡诺图如图A3所示。

图A3

四、1.逻辑函数Y的卡诺图如图A4所示。

数字电子技术期末考试试题及答案(试卷一)

、 代入规则 对偶规则 反

演规则

、

。

5、为 了 实 现 高 的 频 率 稳 定 度 , 常 采 用 石英晶体

振荡

器 ; 单 稳 态 触 发 器 受 到 外 触 发 时 进 入 暂稳态 态

6、同步 RS 触发器中 R、S 为 高 电平有效,基本 R、S 触发器中 R、S

为低

电平有效

7、在进行 A/D 转换时,常按下面四个步骤进行, 采样 保持 量化 编

码、

、

、。Βιβλιοθήκη 二、选择题(每题 1 分,共 10 分)

1、有八个触发器的二进制计数器,它们最多有(

)种计数状态。

A、8; B、16; C、256; D、64

2、下列触发器中上升沿触发的是( )。

A、主从 RS 触发器;B、JK 触发器;C、T 触发器;D、D 触发器

3、下式中与非门表达式为( d ),或门表达式为(a )。

数字电子技术期末考试试题及答案(试卷一)

目录

数字电子技术期末考试试题及答案(试卷一) ........................................................................... 1 一、填空题(每空 1 分,共 20 分).............................................................................................2 二、选择题(每题 1 分,共 10 分).............................................................................................2 三、判断(每题 1 分,共 10 分):...............................................................................................3 四、数制转化(每题 2 分,共 10 分):.......................................................................................3 五、逻辑函数化简(每题 5 分,共 10 分):...............................................................................3 六、分析电路:(每题 10 分,共 20 分).....................................................................................4 七、设计电路(共 10 分).............................................................................................................4 试题答案(一)...............................................................................................................................5

数字电子技术基础_北京理工大学中国大学mooc课后章节答案期末考试题库2023年

数字电子技术基础_北京理工大学中国大学mooc课后章节答案期末考试题库2023年1.逐次渐近型8位A/D转换器中的8位D/A转换器的Vomax=10.2V,若输入为3V,则转换后的数字输出D为:答案:010010112.用ROM设计逻辑电路实现两个两位二进数的全加运算,则需要ROM的地址线和数据线至少为:答案:5,33.存储容量为8k×16位的RAM,地址线有()根。

答案:134.静态RAM一般采用MOS管的栅极电容来存储信息,必须由刷新电路定期刷新。

答案:错误5.以下触发器电路中能够实现二进制计数器(对输入的时钟进行计数,辨识两个时钟周期)功能的电路有:答案:___6.ROM为只读存储器,因此不能对其进行写操作。

答案:错误7.施密特触发器具有两个稳定状态。

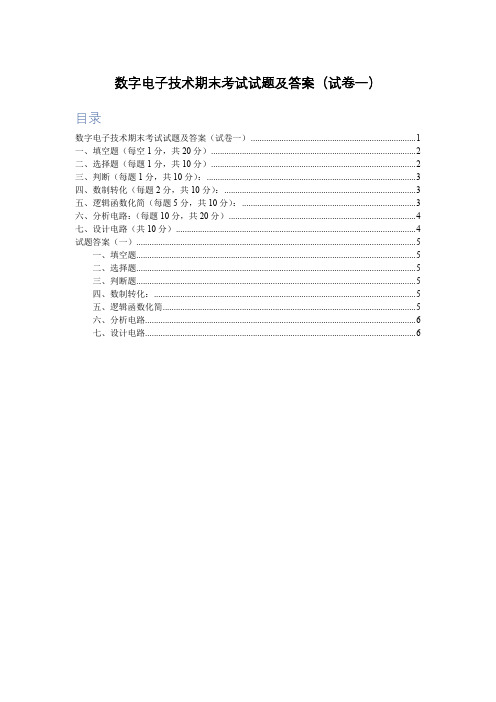

答案:正确8.由555定时器构成的电路如图所示,则此电路能够实现()功能。

【图片】答案:单稳态触发器9.555定时器构成电路如图所示,则此电路的功能为:【图片】答案:施密特触发器10.【图片】上图可以实现的逻辑功能为:答案:半减器11.下图所示74LS151为8选1数据选择器,当用此器件设计逻辑函数【图片】时,D0D1D2D3D4D5D6D7应分别连接到:【图片】答案:0100101012.如图所示74LS283为四位二进制加法计数器,如果要将输入的8421BCD码D3D2D1D1转换为余3码F3F2F1F0,并且把D3D2D1D1分别接到输入端A3A2A1A0上,则输入端B3B2B1B0和低位进位输入CI分别接到:【图片】答案:0010113.已知TTL反相器电路的参数如下:VOH/ VOL=3.6V/0.3V,IOH/IOL=0.2mA/8mA, IIH/ IIL=20uA/0.4mA ,则其驱动同类门的数量即其扇出系数为多少。

答案:1014.三位环形计数器的模为()?答案:315.如图所示电路输出信号为00110010。

【图片】答案:正确16.单稳态触发器输出信号的脉宽由输入的触发信号决定。

北理通信考试期末试题组合版

;学号

;姓名

;成绩

请用公式表示。 二、 (本题 25 分) 一线性移不变离散时间系统的单位抽样响应为: h(n)=(1+0.3n+0.6n)u(n) (1) 求系统的转移函数,并画出其极-零图; (10 分) (2) 写出系统的差分方程; (5 分) (3) 画出系统直接实现、并联实现的信号流图。 (10 分) 三、 (本题 20 分) (1) 、画出基―2 按时间抽取的 4 点 FFT 算法的完整的信流 图; (10 分) (2) 、用直接法和该快速算法分别计算序列 x(n)={1,2,3,4}的 离散傅氏变换 X(K) 。 (10 分) 四、 (本题 15 分) 已知序列 x(n) = an u(n),现对 x(n)的 Z 变换 X(z)在单位 上 N 等分抽样,抽样值为

课程编号:

北京理工大学 02---03 学年第二学期

00 级机电类《数字信号处理试题(A) 》期终考试题 班级 一、 (本题 25 分) 研究一个输入为 x ( n ) 和输出为 y ( n ) 的时域线性离散移不变 已知它满足 y ( n 1) 系统, 是稳定的。 (1) 求单位抽样响应、系统函数,并指出其收敛域; (10 分) (2) 写出系统的差分方程,指出它是一 IIR 数字滤波器还 是一 FIR 数字滤波器; (5 分) (3) 画出系统直接Ⅰ型、Ⅱ型实现的信号流图。 (10 分) 二、 (本题 15 分) 试求: (1) 、有限长序列 x(n) R5 (n) 的 DTFT; (模和相角表达式) (7 分) (2) 、有限长序列 x(n) nR N (n) 的 N 点 DFT。 (闭合形式表 达式) (8 分) 三、 (本题 15 分) (1) 、画出基―2 按时间抽取的 4 点 FFT 算法的完整的信流 图; (5 分) (2) 、用直接法和该快速算法分别计算序列 x(n)={1,2,3,4}的 离散傅氏变换 X(K) 。 (10 分) ;学号 ;姓名 ;成绩

数电期末试卷与答案(共4套)

数电期末试卷与答案(共4套)XX⼤学信息院《数字电⼦技术基础》期终考试试题( 110 分钟) (第⼀套 )⼀、填空题:(每空 1 分,共 15 分)1.逻辑函数YABC 的两种标准形式分别为()、()。

2.将 2004 个“ 1”异或起来得到的结果是()。

3 .半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8 位 D/A 转换器当输⼊数字量10000000 为 5v。

若只有最低位为⾼电平,则输出电压为() v;当输⼊为 10001000,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D 转换器⽽⾔,()的抗⼲扰能⼒强,()的转换速度快。

6.由 555 定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与 PAL 相⽐,GAL 器件有可编程的输出结构,它是通过对()进⾏编程设定其()的⼯作模式来实现的,⽽且由于采⽤了()的⼯艺结构,可以重复编程,使它的通⽤性很好,使⽤更为⽅便灵活。

⼆、根据要求作题:(共 15 分)1.将逻辑函数P=AB+AC 写成“与或⾮”表达式,并⽤“集电极开路与⾮门”来实现。

2.图 1、2 中电路均由 CMOS 门电路构成,写出 P、Q 的表达式,并画出对应 A 、B、C 的 P、Q 波形。

三、分析图 3 所⽰电路:(10 分)1)试写出 8 选 1 数据选择器的输出函数式;2)画出 A2、 A1、 A0 从 000~111连续变化时, Y 的波形图;3)说明电路的逻辑功能。

四、设计“⼀位⼗进制数”的四舍五⼊电路(采⽤8421BCD 码)。

要求只设定⼀个输出,并画出⽤最少“与⾮门”实现的逻辑电路图。

(15 分)五、已知电路及、4(a) (b)所⽰,设触发器的初态均为“ 0”,试CP A 的波形如图画出输出端 B 和 C 的波形。

(8 分)BC六、⽤ T 触发器和异或门构成的某种电路如图5(a)所⽰,在⽰波器上观察到波形如图 5(b)所⽰。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明 T 的取值。

2022年北京理工大学数据科学与大数据技术专业《操作系统》科目期末试卷B(有答案)

2022年北京理工大学数据科学与大数据技术专业《操作系统》科目期末试卷B(有答案)一、选择题1、下列关于批处理系统的叙述中,正确的是()I.批处理系统允许多个用户与计算机直接交互II.批处理系统分为单道批处理系统和多道批处理系统III.中断技术使得多道批处理系统的1/O设备可与CPU并行工作A.仅II、IIIB.仅IIC.仅I、IID. 仅I、III2、()不是操作系统的功能。

A.CPU管理B.存储管理C.网络管理D.数据管理3、有若干并发进程均将一个共享变量count的值加1一次,那么有关count中的值的说法正确的是()。

I.肯定有不正确的结果II.肯定有正确的结果,III.若控制这些并发进程互斥执行count加1操作,count中的值正确A. I和IIIB.II和IIIC.IIID. I、II和III的说法均不正确4、一个进程的读磁盘操作完成后,操作系统针对该进程必做的是(),A.修改进程状态为就绪态B.降低进程优先级C.给进程分配用户内存空间D.增加进程时间片大小5、进程从运行态到阻塞态可能是()A.运行进程执行P操作B.进程调度程序的调度C.运行进程的时间片用完D.运行进程执行了V操作6、缓冲技术的缓冲池通常设立在()中。

A.主存B.外存C.ROMD.寄存器7、若I/O所花费的时间比CPU的处理时间短很多,则缓冲区()A.最有效B.几乎无效C.均衡D.以上都不是8、若某文件系统索引节点(inode)中有直接地址项和间接地址项,则下列选项中,与单个文件长度无关的因素是().A.索引节点的总数B.间接地址索引的级数C.地址项的个数D.文件块大小9、在文件系统中,若文件的物理结构采用连续结构,则文件控制块FCB中有关文件的物理位置的信息包括(),I.首块地址 II.文件长度 III.索引表地址A.只有IIIB. I和IIC. II和IIID. I和III10、在可变分区分配管理中,某一作业完成后,系统收回其内存空间,并与相邻区合并,为此修改空闲区说明表,造成空闲分区数减1的情况是()。

北理通信考试期末试题组合版

x(n / r ), n ir,0 i N 1 y(n) 0, 其他n

试求 rN 点 DFT [ y (n)] 与 X ( K ) 的关系。 五、 (本题 15 分) 已知一个 5 点序列 x(n)=(1,2,3,4,5),试分别求出:

(1)、 x(n) 和 x(n) 的线性卷积y 1 (n); (2)、 x(n) 和 x(n) 的 5 点圆周卷积y 2 (n); (3)、 x(n) 和 x(n) 的 10 点圆周卷积y 3 (n);

2

课程编号:

北京理工大学 02---03 学年第二学期

00 级机电类《数字信号处理》补考试题 班级 一、 (本题 15 分) 直接计算下面两个序列的卷积和 y( n ) x( n ) * h( n )

a n , 0 n N 1 h( n ) , 其他 n 0 n n 0 ,n 0 n x( n ) , n n0 0

00 级机电类《数字信号处理试题(B) 》期终考试题 班级 一、 (本题 10 分) 一个输入为 x(n)和输出为 y(n)的系统,输入-输出关系由下式 确定:y(n)-ay(n-1)=x(n),y(-1)=0, 试判断该系统是否是时不变的,是否是线性的。 二、 (本题 25 分) 一线性移不变离散时间系统的单位抽样响应为: h(n)=(1+0.3n+0.6n)u(n) (1) 求系统的转移函数,并画出其极-零图; (10 分) (2) 写出系统的差分方程; (5 分) (3) 画出系统直接实现、并联实现的信号流图。 (10 分) 三、 (本题 20 分) 分别用直接法和基―2 按时间抽取的 8 点 FFT 快速算法计算 序列 x(n)={1,1,1,1,1,1,1,1}的离散傅氏变换 X(K) 。 四、 (本题 15 分) 已知序列 x(n) = an u(n),现对 x(n)的 Z 变换 X(z)在单位 圆上 N 等分抽样,抽样值为 ;学号 ;姓名 ;成绩

北京理工大学2020年9月《电路分析基础》期末试卷(B卷)参考答案

2.用叠加定理求图示电路中电流I。

答:

3. 化简图示电路。

答:

4.图示电路中电容元件的uC(t)=e-10tV,求电流iC(t)。

答:电流iC(t)=2F +Uc- 1

5.单口网络N无独立源,已知:u(t)=100cos(10t+90o)V,i(t)=5cos(10t+45o)A,求单口网络ab端的等效阻抗。

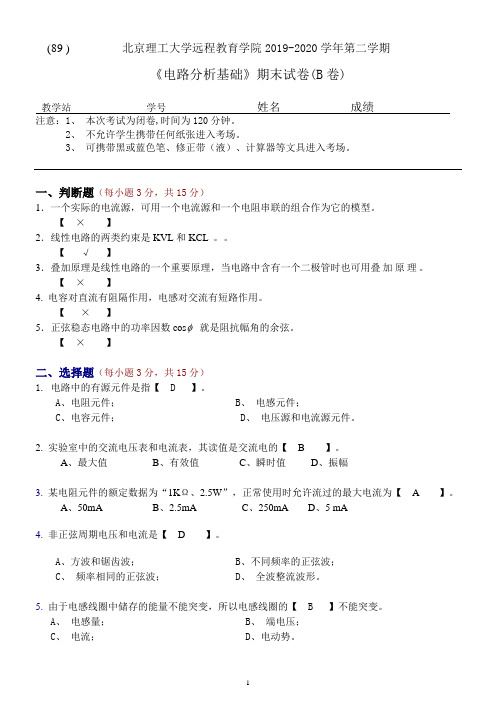

(89 )北京理工大学远程教育学院2019-2020学年第二学期

《电路分析基础》期末试卷(B卷)

教学站学号姓名成绩

注意:1、 本次考试为闭卷,时间为120分钟。

2、 不允许学生携带任何纸张进入考场。

3、 可携带黑或蓝色笔、修正带(液)、计算器等文具进入考场。

一、判断题(每小题3分,共15分)

1.一个实际的电流源,可用一个电流源和一个电阻串联的组合作为它的模型。

【×】

2.线性电路的两类约束是KVL和KCL。。

【√】

3.叠加原理是线性电路的一个重要原理,当电路中含有一个二极管时也可用叠加原理。

【×】

4.电容对直流有阻隔作用,电感对交流有短路作用。

【×】

5.正弦稳态电路中的功率因数cos 就是阻抗幅角的余弦。

【×】

二、选择题(每小题3分,共15分)

1.电路中的有源元件是指【D】。

A、电阻元件; B、 电感元件;

C、电容元件; D、 电压源和电流源元件。

2.实验室中的交流电压表和电流表,其读值是交流电的【B】。

A、最大值B、有效值C、瞬时值D、振幅

3.某电阻元件的额定数据为“1KΩ、2.5W”,正常使用时允许流过的最大电流为【A】。

2021年北京理工大学数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)

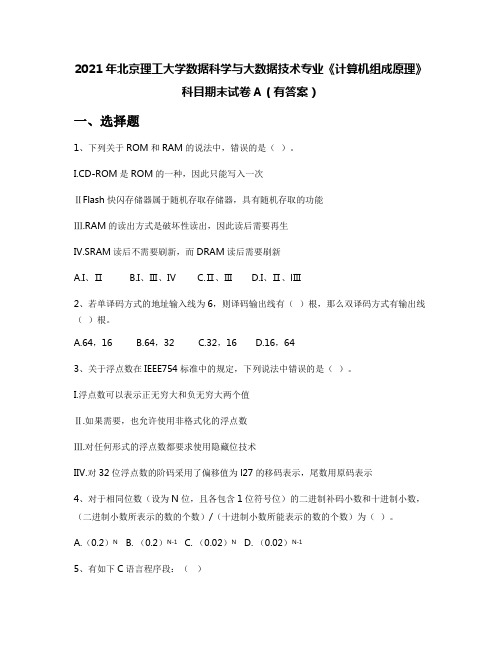

2021年北京理工大学数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、下列关于ROM和RAM的说法中,错误的是()。

I.CD-ROM是ROM的一种,因此只能写入一次ⅡFlash快闪存储器属于随机存取存储器,具有随机存取的功能Ⅲ.RAM的读出方式是破坏性读出,因此读后需要再生IV.SRAM读后不需要刷新,而DRAM读后需要刷新A.I、ⅡB.I、Ⅲ、ⅣC.Ⅱ、ⅢD.I、Ⅱ、lⅢ2、若单译码方式的地址输入线为6,则译码输出线有()根,那么双译码方式有输出线()根。

A.64,16B.64,32C.32,16D.16,643、关于浮点数在IEEE754标准中的规定,下列说法中错误的是()。

I.浮点数可以表示正无穷大和负无穷大两个值Ⅱ.如果需要,也允许使用非格式化的浮点数Ⅲ.对任何形式的浮点数都要求使用隐藏位技术IⅣ.对32位浮点数的阶码采用了偏移值为l27的移码表示,尾数用原码表示4、对于相同位数(设为N位,且各包含1位符号位)的二进制补码小数和十进制小数,(二进制小数所表示的数的个数)/(十进制小数所能表示的数的个数)为()。

A.(0.2)NB. (0.2)N-1C. (0.02)ND. (0.02)N-15、有如下C语言程序段:()short si=-32767;unsigned short usi=si;执行上述两条语句后,usi的值为A.-32767B.32767C.32768D.327696、总线的数据传输速率可按公式Q=Wf/N计算,其中Q为总线数据传输速率,W为总线数据宽度(总线位宽/8),f为总线时钟频率,N为完成一次数据传送所需的总线时钟周期个数。

若总线位宽为16位,总线时钟频率为8MHz,完成一次数据传送需2个总线时钟周期,则总线数据传输速率Q为()。

A.16Mbit/sB.8Mbit/sC.16MB/sD.8MB/s7、在下面描述的PCI总线的基本概念中,不正确的表述是()。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程编号:ELC06011 北京理工大学2010-2011学年第二学期

2009级数字电子技术基础B 期末试题A 卷

注:试题答案必须书写在答题纸上,在试题和草稿纸上答题无效。

班级 学号 姓名 成绩

一、(20分)填空

1.在如下门电路中,哪些输出端能够直接互连 bcde 。

若输出端不能互连,为什么? 输出都呈现低阻抗,如果相连,如果一个门工作在高电平,

一个门工作在低电平,会使两个门内部形成过电流而损坏器件67

a )

普通TTL 门电路;b )普通CMOS 门电路;c )OC 门;d )三态输出门;

e )OD 门。

2.一个4位D/A 转换器的分辨率为 1/15 1/(2^n-1) ,若参考电压V REF = 6V ,当输入码为0110时,输出电压为 6/16*(8*0+4*1+2*1+1*0)=2 V 。

3.存储容量为2K ×8位的随机存储器,地址线为 11(2的几次方就是十几根) 根,数据线为 8 根;若用1K ×4位的RAM 来实现上述存储容量,需要 4 片。

4.A/D 转换器一般需要经过采样、保持、 量化 、 编码 4个过程。

5.单稳态触发器输出脉冲的频率取决于 ,输出脉冲的宽度取决于 。

6.施密特触发器有 2 个稳定状态,单稳态触发器有 1 个稳定状态,多谐振荡器 0 个稳定状态。

7.ROM 设计的组合逻辑电路如图T1所示,写出逻辑函数0Y 和1Y 的表达式。

0Y = ∑(m1,m2,m6) ,1Y = ∑(m0,m1,m5) 。

A B 0Y 1

Y

C

图T1

二、(10分)

将下列各式化简为最简与或式,方法不限。

1.CD D AC ABC C A F 1+++

=

2.CD B BCD A C B A D C AB F 2+++=,约束条件: 答案略 三、(10分)

已知图T3中(a )

(b )(c )为TTL 门电路,(d )(e )为CMOS 门电路,分别写出各电路的输出状态(0或1或高阻)或输出表达式。

V

1

Y

A

B C D

2

V 3

Y V 0

(a ) 高电平 VL 代表低电平(b )cmos ,ABCD (c )高阻

4

Y A B

1

5

Y IH

V

(d ) CMOS 高阻 (e )高电平

图T3

四、(10分)

试用一片4位并行加法器74LS283(图T4)和异或门设计一个加/减法运算电路。

当控制信号M=0时,实现输入的两个四位二进制数相加(Y3Y2Y1Y0=A3A2A1A0+B3B2B1B0);当M=1时,实现输入的两个四位二进制数相减(Y3Y2Y1Y0=A3A2A1A0-B3B2B1B0)。

图T4

关键:减法为补码+1

五、(10分)

编码器74LS148和数据选择器74LS151构成的逻辑电路如图T5所示,当输

入

7654321000001010

D D D D D D D D=,

7654321011111111

D D D D D D D D=,试分别写出所示电路输出F的表达式(要求有分析过程)。

74LS148和74LS151功能表分别如表T5-1和T5-2所示。

D

1

D

D

D

D

D

D

D

图T5

个人建议将常用器件逻辑关系式记下来

可以知道74LS148编码器,74LS151数据选择器

对于数据选择器

简单可知,例如输出D0就是A2A1A0,对于D1就是A2A1A0

那么我们简单写出其逻辑表达式

表T5-1 74LS151功能表

F=EN(D0A1A2A0+D1A2A1A0.....略) 接下来是编码器 观察其输出为0的点

Y2=I7+I6I7+I5 I6I7+I4 I5 I6I7 其余同理,不做赘述 分别代入D0-D7,得到输出

六、(15分)

电路如图T6所示,其中Ω==k 10R R 21,F .C μ10=。

1.说明555定时器构成电路的名称,计算输出o u 的频率o f ,并计算输出o u 的占空比q 。

多谐振荡器,占空比q=R1/(R1+R2) f=1/[(R1+2*R2)*C *ln2] 2.分析由触发器FF0、FF1、FF2构成的时序电路的功能,要求写出驱动方程、状态方程,输出方程,画出状态转换图,检查电路能否自启动,并说明电路功能。

R 1

R

2

C

Y

10k 10k 0.1μ

图T6

首先是D 触发器, =D

先写出Q0,Q1,Q2,以及D0,D1,D2 D0=Q1Q2 D1=Q1⊕Q2 D2=Q0Q2

= = = 列出真值表

画出状态转换图

因为形成环路,可以自启动 功能相当于五进制计数器 输出Y= 七、(15分)

图T7所示是用两片四位同步二进制加法计数器74LS161接成的计数器。

74LS161的功能表见表T7所示。

1.试分析电路接成的是几进制计数器,两片之间是几进制? 2.是同步计数器还是异步计数器?异步(CP 非同一时钟) 3.输出Y 与脉冲CP 的频率比? 1:16 4.画出第二片74LS161(II )的状态转换图。

V

图T7

表T7 74LS161的功能表

其中:0123T Q Q Q Q CT ⋅⋅⋅⋅=

CO

片I 的Q2与片II 的Q2都为1时置零,片1进位时激活片2,那就是说片I 从0000----1111片2走1,不难看出片2为0100时,片1为0100时置零,那就是4X16+4=68位,片1为16位,片II 为4位

八、(10分)

试用JK触发器设计一个三位计数器,其状态转换表如表T8所示。

(要求写明设计过程)。

表T8

参考书上P156

进位CO=Q2Q1Q0

利用JK触发器

=J+K

观察JK触发器公式

我们分别对Q2,Q1,Q0

Q2

= Q0

=Q0

=Q1+Q1

代入

J2=1 K2= Q0

J1=Q0 K1=1

J0=Q1 K0=Q1

连接略

CO

.......... 我是红领巾,别谢我

欢迎您的下载,

资料仅供参考!

致力为企业和个人提供合同协议,策划案计划书,学习资料等等

打造全网一站式需求。