第4节 Xilinx公司原语的使用方法1

Xilinx使用步骤.doc

Xilinx使用步骤:第一步:打开Xilinx→打开File→点击New Project然后输入工程名qq,点击Next点击Next点击Next点击New Source→点击VHDL Module→在File name处输入文件名Cui→点击下一步端口的名字自己随便写,这是两个输入端a,b。

一个输出端c。

用来实现与门的功能,继续点击Next点击Finish点击Yes然后继续点击下一步,下一步,直到点击Finish,将出现此对话框然后大概到39行左右(begin 与end Behavioral之间)就可以输入VHDL 代码。

例如:输入c<=a and b;//实现与门的功能。

然后点击保存(这个很重要)然后点击运行如果程序正确,将运行成功,如下然后可以查看(老师说这种图要保存):在这个图上继续点击(双击):(这个图要保存)第二步:仿真测试在Sources For处修改Synthesis/Implementation为Behavioral Simulation,然后再cui- Behavioral右击NewSource,结果如下:添加Test Bench WaveForm,及File Name,然后下一步然后下一步,下一步,下一步……直到Finish屏幕上b处的波形是可以点出来的,b处必须有波动,不可以是直线,然后必须保存,如下:然后点击Processes,右击Simulate Behavioral Model ,点击运行将出现以下结果点击Wave default,就可以看到结果(这个要保存),如下(F5、F6调大小):大家不懂得问哦!!!这个工程要保存下来,用来答辩!!!。

vivado原语使用方法

vivado原语使用方法Vivado原语使用方法Vivado原语是一种在Xilinx Vivado设计工具中使用的基本构建模块。

它们是硬件描述语言(HDL)中的预定义硬件元素,可用于构建数字电路设计。

Vivado原语提供了一种快速和灵活的方法来实现常见的数字逻辑功能。

本文将介绍Vivado原语的使用方法,以帮助读者更好地理解和应用这些常用的硬件构建模块。

在Vivado中,原语可以通过两种方式使用:RTL(Register Transfer Level)和Schematic。

RTL是一种基于HDL的设计方法,允许工程师按照信号的传输和寄存器的级联来描述电路。

Schematic是一种基于图形界面的设计方法,它提供了一种直观的方式来构建电路图。

下面将分别介绍这两种方法的使用步骤。

1. RTL方法:在Vivado中创建一个新的RTL工程。

然后,使用文本编辑器打开新建的工程文件,并在文件中添加所需的原语。

Vivado原语通常以模块的形式存在,每个模块都包含一个或多个输入和输出端口。

通过声明输入和输出端口,可以定义原语的功能和接口。

接下来,使用连接运算符将原语的输入和输出端口连接到其他模块或信号。

最后,编译RTL设计并生成比特流文件。

2. Schematic方法:在Vivado中创建一个新的Schematic工程。

然后,在工程中打开Schematic编辑器。

在编辑器中,可以选择所需的原语并将其拖放到设计窗口中。

Vivado提供了一个图形库,其中包含各种常用的原语,例如逻辑门、寄存器和计数器等。

选择原语后,可以通过添加和连接线路来定义原语的功能和接口。

最后,编译Schematic设计并生成比特流文件。

无论是使用RTL还是Schematic方法,都需要注意以下几点:1. 确保原语的输入和输出端口的数据类型和宽度与设计需求一致。

2. 仔细阅读原语的文档和规范,了解其功能和使用方法。

3. 在设计中合理使用原语,避免过度使用或重复使用,以提高设计的性能和效率。

Xilinx FPGA常用原语介绍

Xilinx FPGA常用原语介绍

原语,即primitive。

不同的厂商,原语不同;同一家的FPGA,不同型号的芯片,可以也不一样;原语类似最底层的描述方法。

使用原语的好处,可以直接例化使用,不用定制IP;即可通过复制原语的语句,然后例化IP,就可使用;Xilinx是通过直接修改原语中的参数再例化IP来使用;Xilinx公司的原语分为10类,包括:计算组件,IO端口组件,寄存器/锁存器,时钟组件,处理器组件,移位寄存器,配置和检测组件,RAM/ROM 组件,Slice/CLB组件,G-tranceiver。

下图所示为UG799中对原语的分类列表。

项目中主要用到的原语与IO端口有关,所以基本在Input/Output FuncTIons 和IO两类中。

下面着重介绍实际中所用到的几个原语,芯片A7系列。

1. IBUF和IBUFDS(IO)

IBUF是输入缓存,一般vivado会自动给输入信号加上,IBUFDS是IBUF的差分形式,支持低压差分信号(如LVCMOS、LVDS等)。

在IBUFDS中,一个电平接口用两个独特的电平接口(I和IB)表示。

一个可以认为是主信号,另一个可以认为是从信号。

主信号和从信号是同一个逻辑信号,但是相位相反。

举例说明:

LVDS_25的差分输入的ADC数据。

IBUFDS #(// 差分输入原语,用于LVDS_25端口

.DIFF_TERM(“TRUE”),

.IOSTANDARD(“LVDS_25”)

)IBUFDS_ADC01 (

.O(ADC01_D[i]),

.I(ADC01_P_D[i]),

.IB(ADC01_N_D[i])。

Xilinx ISE使用流程1

Xilinx ISE使用流程(从新建项目到仿真执行)最近在忙着做毕业设计(计算机专业,非电子专业),从小就喜欢电子技术,但由于之前没有接触过FPGA,所以特意跑书店买了一本《Xilinx FPGA数字设计》一书,这本书同时用VHDL和Verilog HDL两种语言讲解,使用的示例非常简洁明了,是一本非常适合入门的图。

我在学习VHDL的时候,发现网上资料很少,所有决定把自己所学的知识和心得分享给广大网友,以便初学FPGA的同学们可以快速掌握Xilinx ISE工具的应用。

注意:阅读本篇文章需要数字电路和C语言等语言基础,本篇文章的代码示例出自《Xilinx FPGA数字设计》,请大家尊重版权。

我使用的Xilinx版本为ISE 14.2。

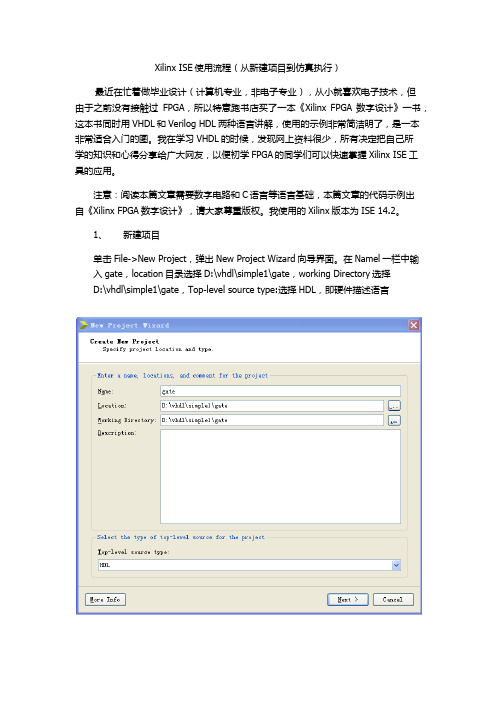

1、新建项目单击File->New Project,弹出New Project Wizard向导界面。

在Namel一栏中输入gate,location目录选择D:\vhdl\simple1\gate,working Directory选择D:\vhdl\simple1\gate,Top-level source type:选择HDL,即硬件描述语言单击Next,选择芯片型号和封装等,其中,芯片大家可以选择自己喜欢的,Synthesis Tool(综合工具)选择XST (VHDL/Verilog),Simluator(仿真工具)选择ISim (VHDL/Verilog),当然你也可以选择Modesim工具,Preferred Language(偏好语言)选择VHDL,VHDL Source Analysis Standard(VHDL语言分析标准)选择VHDL-200X单击Next,进入Project Summary页面,单击Finish,这一节我就不截图了。

进入程序主界面,我们可以看到一个空视图(Empty View),如下图:接下来我们要添加源代码了,在Hierarchy(层级)面板中选中XC6SLX16-3CSG324节点,右键单击New Source菜单,弹出New Source wizard向导界面,选中VHDL Module树节点,在右侧的File name输入gate。

xilinx使用步骤

Xilinx软件使用步骤目录基本操作1. 打开xilinx2. open project3. New project4. 创建新的 .vhd文件5. 建立波形文件6. 综合7. 仿真8. 下载程序到电路板中需要注意的问题1.生成顶层原理图2.建立.ucf文件3. implement时出错的原因4.仿真时的问题基本操作1. 打开xilinx图1 打开xilinx界面2. open project图2 open project图3 查找要打开的.ise文件单击打开后,出现在左侧box中。

图4 open project3. New project顶层文件类型,原理图类型选Schematic,否则选择HDL;单击下一步,通过右侧value各项目,配置器件类型,即FPGA 型号。

注意:此处配置错误的话,综合时会出现放不下或者些不进去的错误。

配置完成后,单击下一步,出现创建源文件对话框如下图所示。

不需做设置更改,直接点击下一步,出现添加现有源对话框如下图所示。

不需做任何设置,直接单击下一步,出现New project information对话框,如下图所示。

确认信息无误后,单击完成,创建的新的project即出现在主页面左侧Sources in project中,如下图所示。

4. 创建新的 .vhd文件右击主页面左侧Sources in project中xc2s200-5pq208,在右键菜单中选择New source,如下图所示;出现New source对话框;左侧选择VHDL Module,右侧输入文件名,如下图所示,单击下一步;出现define vhdl source对话框,输入端口名,输入输出类型和MSB,LSB, 如下图所示,然后单击下一步,出现信息对话框,如下图所示,确认无误后,单击完成。

然后主页面如下图所示:5. 建立波形文件在主页面,编程之后保存。

在如下图所示位置右击.vhd文件,选择new source选项。

Xilinx ISE 使用入门手册

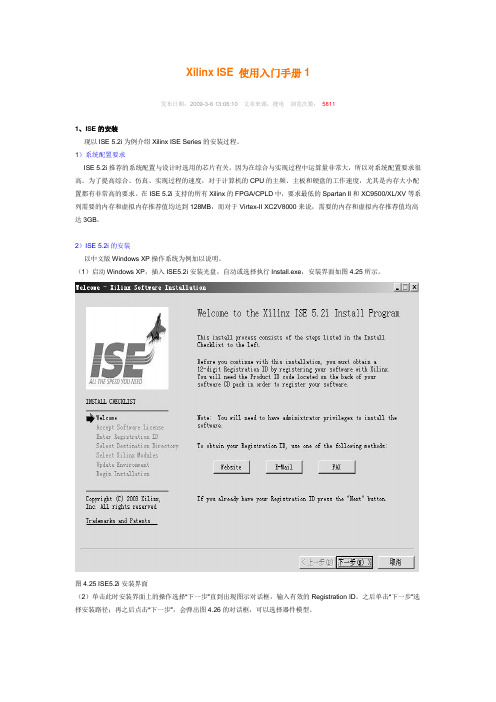

Xilinx ISE 使用入门手册1发布日期:2009-3-6 13:06:10文章来源:搜电浏览次数:58111、ISE的安装现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。

1)系统配置要求ISE 5.2i推荐的系统配置与设计时选用的芯片有关。

因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。

为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。

在ISE 5.2i支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。

2)ISE 5.2i的安装以中文版Windows XP操作系统为例加以说明。

(1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。

图4.25 ISE5.2i安装界面(2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。

之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框(3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。

安装完成后,环境变量应作如下描述:若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入:变量名:Xilinx变量值:C:Xilinx(即安装路径)具体设置如图4.28所示。

图4.28 环境变量设置操作图3)安装第三方软件在PC上安装完ISE之后,还需要安装第三方仿真软件,如ModelSim等。

Xilinx原语ODDR概述和使用

Xilinx原语ODDR概述和使用ODDR is Xilinx HDL Language Template。

ODDR:Output Double Data Rate(DDR)。

在介绍ODDR之前,我们先简单了解一下OLOGIC。

OLOGIC块在FPGA内的位置紧挨着IOB,其作用是FPGA通过IOB发送数据到器件外部的专用同步块。

OLOGIC 资源的类型有OLOGIC2(位于HP I/O banks)和OLOGIC3(位于HR I/O banks)。

OLOGIC2和OLOGIC3不属于原语,正因为这样,所以它们不能被直接例化。

它包含在布局布线后用户可例化的一些元素,例如一个输出触发器(OFD–output flip-flop)或者一个ODDR(output DDR element)。

OLOGIC主要由两个block组成,一个用于配置输出路径。

另外一个用于配置三态控制路径。

这两个block具有共同的时钟,但是具有不同的使能信号OCE和TCE。

两者具有由SRV AL属性精致的异步和同步set和reset(S/R信号)。

输出路径和三态控制路径可以以下列模式之一独立配置:1.边沿触发的D触发器2.DDR模式(ASAME_EDGE 或OPPOSITE_EDGE)3.电平敏感锁存器4.异步电路/组合逻辑OLOGIC block中的各种逻辑资源如下:Output DDR概述(ODDR)7系列器件在OLOGIC中有专用寄存器来实现输出DDR寄存器。

这个功能在例化ODDR 时可见。

在使用OLOGIC时,DDR的复用是自动的,不需要手动控制多路复用。

这个控制是从时钟产生的。

ODDR原语是由一个时钟输入,下降沿数据由输入时钟的本地反转来计时。

反馈到I/O块。

ISE使用指南完整版

第4章ISE开发环境使用指南第1节ISE套件的介绍与安装4.1.1 ISE简要介绍Xilinx是全球领先的可编程逻辑完整解决方案的供应商,研发、制造并销售应用范围广泛的高级集成电路、软件设计工具以及定义系统级功能的IP(Intellectual Property)核,长期以来一直推动着FPGA技术的发展。

Xilinx的开发工具也在不断地升级,由早期的Foundation 系列逐步发展到目前的ISE 9.1i系列,集成了FPGA开发需要的所有功能,其主要特点有:•包含了Xilinx新型SmartCompile技术,可以将实现时间缩减2.5倍,能在最短的时间内提供最高的性能,提供了一个功能强大的设计收敛环境;•全面支持Virtex-5系列器件(业界首款65nm FPGA);•集成式的时序收敛环境有助于快速、轻松地识别FPGA设计的瓶颈;•可以节省一个或多个速度等级的成本,并可在逻辑设计中实现最低的总成本。

Foundation Series ISE具有界面友好、操作简单的特点,再加上Xilinx的FPGA芯片占有很大的市场,使其成为非常通用的FPGA工具软件。

ISE作为高效的EDA设计工具集合,与第三方软件扬长补短,使软件功能越来越强大,为用户提供了更加丰富的Xilinx平台。

4.1.2 ISE功能简介ISE的主要功能包括设计输入、综合、仿真、实现和下载,涵盖了FPGA开发的全过程,从功能上讲,其工作流程无需借助任何第三方EDA软件。

•设计输入:ISE提供的设计输入工具包括用于HDL代码输入和查看报告的ISE文本编辑器(The ISE Text Editor),用于原理图编辑的工具ECS(The Engineering Capture System),用于生成IP Core的Core Generator,用于状态机设计的StateCAD以及用于约束文件编辑的Constraint Editor等。

•综合:ISE的综合工具不但包含了Xilinx自身提供的综合工具XST,同时还可以内嵌Mentor Graphics公司的LeonardoSpectrum和Synplicity公司的Synplify,实现无缝链接。

XIlinx公司ISE软件使用中文说明

十分钟学会ISE声明本系列文档、软件的版权为Digital Power Studio工作组所有。

Digital Power Studio工作组保留所有权利。

欢迎转载,但请保留这段版权声明;请勿用于商业用途。

Copyright (c) 2004, Digital Power Studio. All rights reserved.HistoryRevision Date Issuer NotesRelease1.0 Mar 3, 2005 Badfish First目录概述 (4)实验目的 (4)软件准备 (5)流程介绍 (5)新建项目: (5)编写和导入代码文件 (8)调用Modsim进行仿真 (11)约束文件 (13)综合与实现 (15)下载 (16)十分钟学会ISE 概述这个文档主要帮助大家熟悉利用ISE进行Xilinx公司FPGA代码开发的基本流程。

主要是帮助初学者了解和初步掌握ISE的使用,不需要FPGA的开发基础,所以对每个步骤并不进行深入的讨论。

本文介绍的内容从新建project一直到下载到硬件观察现象为止,涵盖整个开发过程。

考虑到我们的开发一般以Verilog HDL或VHDL为主,在本文中未介绍原理图输入工具和IP核使用工具等。

这同时是出于为了使文章脉络更清晰,让大家更快地学会ISE的考虑。

关于这些专用工具,可以参看HELP或者其他文档。

为了有个更直观的理解,我们需要一个实验平台,在本文中,采用的是Digital Power Studio工作组FPGA SPARK1.1综合开发平台的Xilinx标准型开发系统。

如图1所示(图中为Altera子板,只需改成Xilinx的即可)。

在该开发系统中,所采用的芯片是SPARTAN II系列的XC2S200。

可以参看/solution/fpgaspark.htm中对该系统的介绍。

图1 FPGA SPARK1.1 外观图实验目的在如上系统中右边有一个128×64带背光的点阵型液晶。

FPGA的LVDS介绍和xilinx原语的使用方法中文说明

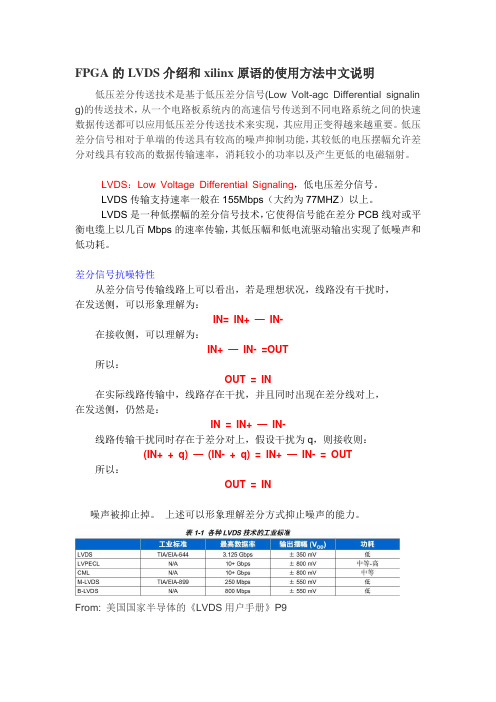

FPGA的LVDS介绍和xilinx原语的使用方法中文说明低压差分传送技术是基于低压差分信号(Low Volt-agc Differential signalin g)的传送技术,从一个电路板系统内的高速信号传送到不同电路系统之间的快速数据传送都可以应用低压差分传送技术来实现,其应用正变得越来越重要。

低压差分信号相对于单端的传送具有较高的噪声抑制功能,其较低的电压摆幅允许差分对线具有较高的数据传输速率,消耗较小的功率以及产生更低的电磁辐射。

LVDS:Low Voltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

差分信号抗噪特性从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时,在发送侧,可以形象理解为:IN= IN+ —IN-在接收侧,可以理解为:IN+ —IN- =OUT所以:OUT = IN在实际线路传输中,线路存在干扰,并且同时出现在差分线对上,在发送侧,仍然是:IN = IN+ —IN-线路传输干扰同时存在于差分对上,假设干扰为q,则接收则:(IN+ + q) —(IN- + q) = IN+ —IN- = OUT 所以:OUT = IN噪声被抑止掉。

上述可以形象理解差分方式抑止噪声的能力。

From: 美国国家半导体的《LVDS用户手册》P9FPGA中的差分管脚为了适用于高速通讯的场合,现在的FPGA都提供了数目众多的LVDS接口。

如Spartan-3E系列FPGA提供了下列差分标准:LVDSBus LVDSmini-LVDSRSDSDifferential HSTL (1.8V, Types I and III)Differential SSTL (2.5V and 1.8V, Type I)2.5V LVPECL inputs所拥有的差分I/O管脚数目如下From:Spartan-3E FPGA Family:Complete Data Sheet p5I/O管脚的命名方式:From:Spartan-3E FPGA Family:Complete Data Sheet p164From:Spartan-3E FPGA Family:Complete Data Sheet p18 Spartan-3E系列FPGA器件差分I/O接口输入工作的特性参数:From:Spartan-3E FPGA Family:Complete Data Sheet p126 Spartan-3E系列FPGA器件差分I/O接口输出工作的特性参数:From:Spartan-3E FPGA Family:Complete Data Sheet p127Xilinx公司差分原语的使用(原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C+ +中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。

xilinx 时钟单端转差分原语

xilinx 时钟单端转差分原语

"Xilinx 时钟单端转差分原语" 这个句子是关于Xilinx FPGA(现场可编程门阵列)的时钟处理方面的描述。

在这里,它涉及到将单端时钟信号转换为差分时钟信号的过程。

首先,让我们来解释一下单端和差分时钟信号:

●单端时钟信号:这种类型的时钟信号只使用一个线路来传输时钟信号。

在

单端时钟中,信号是接地参考的单端电压。

●差分时钟信号:差分信号使用两个线路来传输信号,通常被称为“正”和

“负”或“非”。

这种类型的时钟信号设计用于减少电磁干扰(EMI)和提高信号完整性。

在某些应用中,可能需要将单端时钟转换为差分时钟。

这可以通过Xilinx FPGA中的特定原语(primitive)或IP核来实现。

具体的实现方式和工具可能会根据Xilinx FPGA的型号和版本有所不同。

一般来说,Xilinx提供了一些内置的时钟管理IP核,这些IP核可以用来实现各种时钟转换功能,包括单端到差分的转换。

总结来说,"Xilinx 时钟单端转差分原语" 指的是Xilinx FPGA中的一种功能或模块,它可以实现将输入的单端时钟信号转换为输出的差分时钟信号。

这种功能在需要高精度和低噪声的时钟信号的应用中尤其有用,例如在高速度或高数据速率通信系统中的应用。

xilinx使用步骤

Xilinx软件使用步骤目录基本操作1. 打开xilinx2. open project3. New project4. 创建新的 .vhd文件5. 建立波形文件6. 综合7. 仿真8. 下载程序到电路板中需要注意的问题1.生成顶层原理图2.建立.ucf文件3. implement时出错的原因4.仿真时的问题基本操作1. 打开xilinx图1 打开xilinx界面2. open project图2 open project图3 查找要打开的.ise文件单击打开后,出现在左侧box中。

图4 open project3. New project顶层文件类型,原理图类型选Schematic,否则选择HDL;单击下一步,通过右侧value各项目,配置器件类型,即FPGA 型号。

注意:此处配置错误的话,综合时会出现放不下或者些不进去的错误。

配置完成后,单击下一步,出现创建源文件对话框如下图所示。

不需做设置更改,直接点击下一步,出现添加现有源对话框如下图所示。

不需做任何设置,直接单击下一步,出现New project information对话框,如下图所示。

确认信息无误后,单击完成,创建的新的project即出现在主页面左侧Sources in project中,如下图所示。

4. 创建新的 .vhd文件右击主页面左侧Sources in project中xc2s200-5pq208,在右键菜单中选择New source,如下图所示;出现New source对话框;左侧选择VHDL Module,右侧输入文件名,如下图所示,单击下一步;出现define vhdl source对话框,输入端口名,输入输出类型和MSB,LSB, 如下图所示,然后单击下一步,出现信息对话框,如下图所示,确认无误后,单击完成。

然后主页面如下图所示:5. 建立波形文件在主页面,编程之后保存。

在如下图所示位置右击.vhd文件,选择new source选项。

FPGA的LVDS介绍和xilinx原语的使用方法中文说明

FPGA的LV DS介绍和x i linx原语的使用方法中文说明低压差分传送技术是基于低压差分信号(Low Volt-agc Differe ntialsignali ng)的传送技术,从一个电路板系统内的高速信号传送到不同电路系统之间的快速数据传送都可以应用低压差分传送技术来实现,其应用正变得越来越重要。

低压差分信号相对于单端的传送具有较高的噪声抑制功能,其较低的电压摆幅允许差分对线具有较高的数据传输速率,消耗较小的功率以及产生更低的电磁辐射。

LVDS:Low Voltage Differe ntialSignali ng,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MH Z)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

差分信号抗噪特性从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时,在发送侧,可以形象理解为:IN= IN+ —IN-在接收侧,可以理解为:IN+ —IN- =OUT所以:OUT = IN在实际线路传输中,线路存在干扰,并且同时出现在差分线对上,在发送侧,仍然是:IN = IN+ —IN-线路传输干扰同时存在于差分对上,假设干扰为q,则接收则:(IN+ + q) —(IN- + q) = IN+ —IN- = OUT所以:OUT = IN噪声被抑止掉。

上述可以形象理解差分方式抑止噪声的能力。

From: 美国国家半导体的《LVDS用户手册》P9FPGA中的差分管脚为了适用于高速通讯的场合,现在的FPGA都提供了数目众多的LVDS接口。

如Spartan-3E系列FPG A提供了下列差分标准:LVDSBus LVDSmini-LVDSRSDSDiffere ntialHSTL (1.8V, Types I and III)Differe ntialSSTL (2.5V and 1.8V, Type I)2.5V LVPECLinputs所拥有的差分I/O管脚数目如下From:Spartan-3E FPGA Family:Complet e Data Sheet p5I/O管脚的命名方式:From:Spartan-3E FPGA Family:Complet e Data Sheet p164From:Spartan-3E FPGA Family:Complet e Data Sheet p18 Spartan-3E系列FPG A器件差分I/O接口输入工作的特性参数:From:Spartan-3E FPGA Family:Complet e Data Sheet p126 Spartan-3E系列FPG A器件差分I/O接口输出工作的特性参数:From:Spartan-3E FPGA Family:Complet e Data Sheet p127Xilinx公司差分原语的使用(原语,其英文名字为P rimiti ve,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilin x公司为用户提供的库函数,类似于C+ +中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。

xilinx 源语

xilinx 源语

Xilinx的源语包含一系列的硬件描述语言(HDL)和高级综合

语言(HLS)。

以下是Xilinx常用的源语言:

1. Verilog:Verilog是一种硬件描述语言,它用于描述数字电

路和系统级电路的行为和结构。

Xilinx支持使用Verilog进行FPGA设计和开发。

2. VHDL:VHDL是一种硬件描述语言,它用于描述数字电路

和系统级电路的行为和结构。

Xilinx支持使用VHDL进行FPGA设计和开发。

3. SystemVerilog:SystemVerilog是一种扩展的硬件描述语言,它结合了HDL和HLS的特性。

它提供了丰富的语法和功能,

用于描述数字电路和系统级电路的行为和结构。

4. C/C++:Xilinx提供了利用高级综合语言(HLS)将C或

C++代码转换为FPGA电路的工具。

通过使用C/C++,开发人

员可以更快速、更简单地进行FPGA设计和开发。

5. OpenCL:OpenCL是一种并行计算框架,可用于在Xilinx FPGA上实现高性能计算。

Xilinx提供了OpenCL开发工具,

使得使用OpenCL进行FPGA设计和开发变得更加容易。

这些源语言可以在Xilinx的开发环境中进行使用,如Vivado Design Suite和Vitis Unified Software Platform。

Xilinx中ise原语的使用

Xilinx中ise原语的使用1、IBUFGDS输入全局时钟及DCM分频使用:IBUFGDS #(.DIFF_TERM(FALSE), // DifferenTIal TerminaTIon (Virtex-4/5, Spartan-3E/3A).IOSTANDARD(DEFAULT) // Specifies the I/O standard for this buffer) IBUFGDS_inst (.O(CLK_SYS), // Clock buffer output.I(CLKP_SYS), // Diff_p clock buffer input.IB(CLKN_SYS) // Diff_n clock buffer input);DCM_BASE #(.CLKDV_DIVIDE(2.0), // Divide by: 1.5,2.0,2.5,3.0,3.5,4.0,4.5,5.0,5.5,6.0,6.5// 7.0,7.5,8.0,9.0,10.0,11.0,12.0,13.0,14.0,15.0 or 16.0.CLKFX_DIVIDE(3), // Can be any integer from 1 to 32.CLKFX_MULTIPLY(2), // Can be any integer from 2 to 32.CLKIN_DIVIDE_BY_2(FALSE), // TRUE/FALSE to enable CLKIN divide by two feature.CLKIN_PERIOD(8.14),//(10.0), // Specify period of input clock in ns from 1.25 to 1000.00.CLKOUT_PHASE_SHIFT(NONE), // Specify phase shift mode of NONE or FIXED.CLK_FEEDBACK(1X), // Specify clock feedback of NONE, 1X or 2X.DCM_PERFORMANCE_MODE(MAX_SPEED), // Can be MAX_SPEED or MAX_RANGE.DESKEW_ADJUST(SYSTEM_SYNCHRONOUS), // SOURCE_SYNCHRONOUS, SYSTEM_SYNCHRONOUS or// an integer from 0 to 15.DFS_FREQUENCY_MODE(LOW), // LOW or HIGH frequency mode for frequency synthesis.DLL_FREQUENCY_MODE(LOW), // LOW, HIGH, or HIGH_SER frequency mode for DLL.DUTY_CYCLE_CORRECTION(TRUE), // Duty cycle correction, TRUE or FALSE.FACTORY_JF(16hf0f0), // FACTORY JF value suggested to be set to 16hf0f0.PHASE_SHIFT(0), // Amount of fixed phase shift from -255 to 1023.STARTUP_WAIT(FALSE) // Delay configuration DONE until DCM LOCK, TRUE/FALSE) DCM_BASE_inst (.CLK0(CLK0), // 0 degree DCM CLK output.CLK180(CLK180), // 180 degree DCM CLK output.CLK270(CLK270), // 270 degree DCM CLK output.CLK2X(CLK2X), // 2X DCM CLK output.CLK2X180(CLK2X180), // 2X, 180 degree DCM CLK out.CLK90(CLK90), // 90 degree DCM CLK output.CLKDV(clk4608), // Divided DCM CLK out (CLKDV_DIVIDE).CLKFX(clk), // DCM CLK synthesis out (M/D).CLKFX180(CLKFX180), // 180 degree CLK synthesis out.LOCKED(LOCKED), // DCM LOCK status output.CLKFB(CLK0), // DCM clock feedback.CLKIN(CLK_SYS), // Clock input (from IBUFG, BUFG or DCM).RST(1b0) // DCM asynchronous reset input);2、ODDR、IDDR单边缘与双边缘触发的转换。

Xilinx_ISE使用教程__1

Xilinx公司软件平台介绍 公司软件平台介绍

--DSP_Tools软件

Xilinx公司推出了简化FPGA数字处理系统的集成开 发工具DSP Tools,快速、简易地将DSP系统的抽象算法 转化成可综合的、可靠的硬件系统,为DSP设计者扫清 了编程的障碍。DSP Tools主要包括System Genetator和 AccelDSP两部分,前者和Mathworks公司的Simulink实现 无缝链接,后者主要针对c/.m语言。

Slice S2

F7

F6

MUXF7 连接两个 连接两个MUXF6输出 输出

F5

Slice S1

F5

Slice S0

F6

MUXF6 连接slices S0和S1 连接 和 MUXF5连接 连接Slice内的 LUT 连接 内的

北京中教仪装备技术有限公司

Xilinx公司产品概述 公司产品概述

---FPGA内部结构(IO块)

北京中教仪装备技术有限公司

Xilinx公司产品概述 公司产品概述

---PROM产品

串行配置

并行配置

北京中教仪装备技术有限公司

Xilinx公司软件平台介绍 公司软件平台介绍

--开发工具

ISE Design Suite涉及了FPGA设计的各个应用方面, 包括逻辑开发、数字信号处理系统以及嵌入式系统开发等 FPGA开发的主要应用领域,主要包括 1 ISE Foundation 1)ISE Foundation:集成开发工具 2) EDK:嵌入式开发套件 3)DSP_TOOLs:数字信号处理开发工具 4)ChipScope Pro:在线逻辑分析仪工具 5)PlanAhead:用于布局和布线等设计分析工具

xilinx原语手册手册

xilinx原语手册手册

Xilinx原语手册是一份详细介绍Xilinx FPGA(现场可编程门

阵列)器件中可用原语的手册。

Xilinx原语是一组预定义的硬件功

能模块,可以在FPGA设计中使用。

这些原语包括逻辑门、存储器单元、乘法器、加法器等,它们可以用于构建复杂的数字逻辑电路和

信号处理系统。

这份手册通常包含了各种原语的详细说明,包括其

功能、输入输出接口、时序特性以及在设计中的最佳实践等内容。

在Xilinx原语手册中,你可以找到关于各种原语的详细描述,

包括其功能、使用方法、时序要求、资源占用情况等。

这些信息对

于FPGA设计工程师来说非常重要,因为它们可以帮助工程师更好地

理解和利用FPGA中的硬件资源,从而设计出高性能、低功耗的电路。

除了具体的原语介绍外,Xilinx原语手册还可能包括一些设计

实例和最佳实践,帮助工程师更好地应用这些原语来解决实际的设

计问题。

此外,手册中也可能包含一些与原语相关的设计注意事项、时序约束建议等内容,这些对于确保设计的正确性和稳定性非常重要。

总之,Xilinx原语手册是Xilinx FPGA设计工程师日常工作中

的重要参考资料,它提供了关于FPGA原语的全面而详细的信息,帮助工程师更好地应用这些原语来设计出高性能、可靠的数字电路系统。

Xilinx原语ODDR概述和使用

Xilinx原语ODDR概述和使用Xilinx原语ODDR概述和使用ODDR is Xilinx HDL Language Template。

ODDR:Output Double Data Rate(DDR)。

在介绍ODDR之前,我们先简单了解一下OLOGIC。

OLOGIC块在FPGA内的位置紧挨着IOB,其作用是FPGA通过IOB发送数据到器件外部的专用同步块。

OLOGIC 资源的类型有OLOGIC2(位于HP I/O banks)和OLOGIC3(位于HR I/O banks)。

OLOGIC2和OLOGIC3不属于原语,正因为这样,所以它们不能被直接例化。

它包含在布局布线后用户可例化的一些元素,例如一个输出触发器(OFD–output flip-flop)或者一个ODDR(output DDR element)。

OLOGIC主要由两个block组成,一个用于配置输出路径。

另外一个用于配置三态控制路径。

这两个block具有共同的时钟,但是具有不同的使能信号OCE和TCE。

两者具有由SRV AL属性精致的异步和同步set和reset(S/R信号)。

输出路径和三态控制路径可以以下列模式之一独立配置:1.边沿触发的D触发器2.DDR模式(ASAME_EDGE 或OPPOSITE_EDGE)3.电平敏感锁存器4.异步电路/组合逻辑OLOGIC block中的各种逻辑资源如下:Output DDR概述(ODDR)7系列器件在OLOGIC中有专用寄存器来实现输出DDR寄存器。

这个功能在例化ODDR 时可见。

在使用OLOGIC时,DDR的复用是自动的,不需要手动控制多路复用。

这个控制是从时钟产生的。

ODDR原语是由一个时钟输入,下降沿数据由输入时钟的本地反转来计时。

反馈到I/O块。

第4节 Xilinx公司原语的使用方法1

第4节Xilinx公司原语的使用方法1Xilinx 原语3.4 Xilinx公司原语的使用方法原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C++中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM 等,相当于软件中的机器语言。

在实现过程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否则就是不可实现的。

原语在设计中可以直接例化使用,是最直接的代码输入方式,其和HDL语言的关系,类似于汇编语言和C语言的关系。

Xilinx公司提供的原语,涵盖了FPGA开发的常用领域,但只有相应配置的硬件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。

在Verilog中使用原语非常简单,将其作为模块名直接例化即可。

本节以Virtex-4平台介绍各类原语,因为该系列的原语类型是最全面的。

其它系列芯片原语的使用方法是类似的。

Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB 组件以及G比特收发器组件。

下面分别对其进行详细介绍。

3.4.1 计算组件计算组件值得就是DSP48核,也有人将其称为硬件乘法器,功能描述如表3-6所示。

表3-6 计算组件清单DSP48 其结构为一个18*18比特的有符号乘法器,且在后面还级联了一个带有可配置流水线的3输入加法器DSP48核由一个18比特的乘法后面级联一个48比特的加法器,乘法器和加法器的应用位宽分别可以在18、48比特内任意调整。

其在乘加模块中有广泛应用,特别是各类滤波器系统中,不仅可以提高系统稳定性,还能够节省逻辑资源且工作在高速模式下。

其在Verilog中的例化模版为:module fpga_v4_dsp48(BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN,CARRYINSEL, CEA, CEB,CEC, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK, OPMODE,PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RSTP, SUBTRACT);output [17:0]BCOUT;output [47:0] P, PCOUT; //input [17:0] A, B; //input [47:0] C, PCIN;input [1:0] CARRYINSEL;input [6:0] OPMODE;input BCIN, CARRYIN,CEA,CEB, CEC,CECARRYIN,CECINSUB,CECTRL,CEM,CEP,CLK, RSTA, RSTB,RSTC,RSTCARRYIN,RSTM,RSTP,SUBTRACT;//对DSP48原语的功能进行配置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第4节Xilinx公司原语的使用方法1Xilinx 原语3.4 Xilinx公司原语的使用方法原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C++中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM 等,相当于软件中的机器语言。

在实现过程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否则就是不可实现的。

原语在设计中可以直接例化使用,是最直接的代码输入方式,其和HDL语言的关系,类似于汇编语言和C语言的关系。

Xilinx公司提供的原语,涵盖了FPGA开发的常用领域,但只有相应配置的硬件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。

在Verilog中使用原语非常简单,将其作为模块名直接例化即可。

本节以Virtex-4平台介绍各类原语,因为该系列的原语类型是最全面的。

其它系列芯片原语的使用方法是类似的。

Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB 组件以及G比特收发器组件。

下面分别对其进行详细介绍。

3.4.1 计算组件计算组件值得就是DSP48核,也有人将其称为硬件乘法器,功能描述如表3-6所示。

表3-6 计算组件清单DSP48 其结构为一个18*18比特的有符号乘法器,且在后面还级联了一个带有可配置流水线的3输入加法器DSP48核由一个18比特的乘法后面级联一个48比特的加法器,乘法器和加法器的应用位宽分别可以在18、48比特内任意调整。

其在乘加模块中有广泛应用,特别是各类滤波器系统中,不仅可以提高系统稳定性,还能够节省逻辑资源且工作在高速模式下。

其在Verilog中的例化模版为:module fpga_v4_dsp48(BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN,CARRYINSEL, CEA, CEB,CEC, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK, OPMODE,PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RSTP, SUBTRACT);output [17:0]BCOUT;output [47:0] P, PCOUT; //input [17:0] A, B; //input [47:0] C, PCIN;input [1:0] CARRYINSEL;input [6:0] OPMODE;input BCIN, CARRYIN,CEA,CEB, CEC,CECARRYIN,CECINSUB,CECTRL,CEM,CEP,CLK, RSTA, RSTB,RSTC,RSTCARRYIN,RSTM,RSTP,SUBTRACT;//对DSP48原语的功能进行配置。

DSP48 #(.AREG(1), // Number of pipeline registers on the A input, 0, 1 or 2 .BREG(1), // Number of pipeline registers on the B input, 0, 1 or 2 .B_INPUT("DIRECT"),// B input DIRECT from fabric or CASCADE from another DSP48.CARRYINREG(1),// Number of pipeline registers for the CARRYIN input, 0 or 1.CARRYINSELREG(1),// Number of pipeline registers for the CARRYINSEL, 0 or 1.CREG(1), // Number of pipeline registers on the C input, 0 or 1.LEGACY_MODE("MULT18X18S"),// Backward compatibility, NONE, MULT18X18 or MULT18X18S.MREG(1), // Number of multiplier pipeline registers, 0 or 1.OPMODEREG(1), // Number of pipeline regsiters on OPMODE input, 0 or 1.PREG(1), // Number of pipeline registers on the P output, 0 or 1.SUBTRACTREG(1)// Number of pipeline registers on the SUBTRACT input, 0 or 1 ) fpga_v4_dsp48 (.BCOUT(BCOUT), // 18-bit B cascade output.P(P), // 48-bit product output.PCOUT(PCOUT), // 48-bit cascade output.A(A), // 18-bit A data input.B(B), // 18-bit B data input.BCIN(BCIN), // 18-bit B cascade input.C(C), // 48-bit cascade input.CARRYIN(CARRYIN), // Carry input signal.CARRYINSEL(CARRYINSEL), // 2-bit carry input select.CEA(CEA), // A data clock enable input.CEB(CEB), // B data clock enable input.CEC(CEC), // C data clock enable input.CECARRYIN(CECARRYIN), // CARRYIN clock enable input.CECINSUB(CECINSUB), // CINSUB clock enable input.CECTRL(CECTRL), // Clock Enable input for CTRL regsiters.CEM(CEM), // Clock Enable input for multiplier regsiters.CEP(CEP), // Clock Enable input for P regsiters.CLK(CLK), // Clock input.OPMODE(OPMODE), // 7-bit operation mode input.PCIN(PCIN), // 48-bit PCIN input.RSTA(RSTA), // Reset input for A pipeline registers.RSTB(RSTB), // Reset input for B pipeline registers.RSTC(RSTC), // Reset input for C pipeline registers.RSTCARRYIN(RSTCARRYIN), // Reset input for CARRYIN registers .RSTCTRL(RSTCTRL), // Reset input for CTRL registers.RSTM(RSTM), // Reset input for multiplier registers.RSTP(RSTP), // Reset input for P pipeline registers.SUBTRACT(SUBTRACT) // SUBTRACT input);endmodule3.4.2 时钟组件时钟组件包括各种全局时钟缓冲器、全局时钟复用器、普通I/O本地的时钟缓冲器以及高级数字时钟管理模块,如表3-7所示。

表3-7 时钟组件的清单下面对几个常用时钟组件进行简单介绍,其余组件的使用方法是类似的。

1.BUFGBUFG是具有高扇出的全局时钟缓冲器,一般由综合器自动推断并使用,其和同类原语的RTL结构如图3-28所示。

全局时钟是具有高扇出驱动能力的缓冲器,可以将信号连到时钟抖动可以忽略不计的全局时钟网络,BUFG组件还可应用于典型的高扇出信号和网络,如复位信号和时钟使能信号。

如果要对全局时钟实现PLL或DCM等时钟管理,则需要手动例化该缓冲器。

其例化的代码模板如下所示:// BUFG: 全局时钟缓存(Global Clock Buffer),只能以内部信号驱动// Xilinx HDL库向导版本,ISE 9.1BUFG BUFG_inst (.O(O), //时钟缓存输出信号.I(I) // /时钟缓存输入信号);// 结束BUFG_ins模块的例化过程在综合结果分析中,其和同类原语的RTL结构如图3-32所示。

图3-32 全局时钟原语的RTL级结构示意图2. BUFMUXBUFMUX是全局时钟复用器,选择两个输入时钟I0或I1中的一个作为全局时钟,其和同类原语BUFMUX1的RTL级结构如图M所示。

当选择信号S为低时,选择I0;否则输出I1,其真值表如表M所示。

BUFMUX原语和BUFMUX1原语的功能一样,只是选择逻辑不同,对于BUFMUX1,当选择信号S为低时,选择I1;否则输出I0。

BUFMUX原语的例化代码模板如下所示:BUFMUX原语的例化代码模板如下所示:// BUFGMUX: 全局时钟的2到1复用器(Global Clock Buffer 2-to-1 MUX)// 适用芯片:Virtex-II/II-Pro/4/5, Spartan-3/3E/3A// Xilinx HDL库向导版本,ISE 9.1BUFGMUX BUFGMUX_inst (.O(O), //时钟复用器的输出信号.I0(I0), // 0时钟输入信号.I1(I1), //1时钟输入信号.S(S) // 时钟选择信号);// 结束BUFGMUX_inst模块的例化过程需要注意的是:该原语只用用全局时钟处理,不能作为接口使用。

在综合结果分析时,它和同类原语BUFMUX1的RTL级结构如图3-33所示。

图3-33 全局时钟复用器的RTL级结构示意图3. BUFIOBUFIO是本地I/O时钟缓冲器,其RTL结构如图M所示,只有一个输入与输出,非常简单。