51单片机英文翻译

51单片机英文文献及翻译

Data Memory

数据存储器

Te context with microcontrollers,

术语“数据存储器”用于微控制器。

The memory which stores data,i.e.RAM,is called data memory.

用来存储数据的存储器,即RAM,被称作数据存储器

The diffenent versions of 8048 series of microcontrollers microcontrollers contain 64,128.256 bytes of RAM.

8048系列的不同版本的微控制器包含64、128、256字节的RAM。

Data Memory The term data memory is used in the context with microcontrollers,The memory which stores data,i.e.RAM,is called data memory.The diffenent versions of 8048 series of microcontrollers microcontrollers contain 64,128.256 bytes of RAM.The 8048AH,8049AH and 8050AH contain 64,128 and 256 bytes of RAM respectively.64/128/256 bytes of RAM is used either as read/write memory or general-purpose registers.

There is need of cyclical reading (lower than 1 minute periods) of the actual values from the real-time clock and the sensors for pressure and temperature, and to store the read values into the microcontroller’s memory. The communication with the real-time clock and the sensors is possible with the use of I2C interface and the previously defined in the specifications protocols for reading and writing.

51单片机缩写的英文全称及中文名称

ET = enable timer //定时器使能

EX = enable exterior //外部使能(中断)

PX = priority exterior //外部中断优先级

PT = priority timer //定时器优先级

PS = priority serial //串口优先级

DB = define byte //字节定义

EQU = equal //等于

DW = define word //字定义

E = enable //使能

OE = output enable //输出使能

RD = read //读

WR = write //写

中断部分:

INT0 = interrupt 0 //中断0

MSB = most significant bit//最高有效位

LSB = last significant bit//最低有效位

CY = carry //进位(标志)

AC = assistant carry //辅助进位

OV = overflow //溢出

ORG = originally //起始来源

IP = intenterrupt enable // 中断使能

TMOD = timer mode //定时器 方式 (定时器/计数器 控制寄存器)

ALE = alter (变更,可能是)

PSEN = progammer saving enable //程序存储器使能(选择外部程序存储器的意思)

EA = enable all(允许所有中断)完整应该是 enable all interrupt

51单片机寄存器中英文全称对照

51单片机寄存器中英文全称对照51 单片机英文全称<51 外部引脚>缩写英文解释中文解释RST (9) Rest 复位信号引脚RXD(10--P3.0) Receive Data 串口接收端TXD(11--P3.1) Transmit Dat 串口发送端INT0(12--P3.2) Interrupt0 外部中断0信号输入引脚INT1(13--P3.3) Interrupt1 外部中断1信号输入引脚T0(14--P3.4) Timer0 定时/计数器0输入引脚T1(15--P3.5) Timer1 定时/计数器1输入引脚WR(16--P3.6) Write 写信号引脚RD(17--P3.7) Read 读信号引脚PSEN(29) Programmer Saving Enable 外部程序存储器读选通信号ALE(30) Address Latch Enable 地址锁存允许信号EA(31) Enable 外部ROM选择信号<51内部寄存器>SFR special function register 特殊功能寄存器ACC accumulate 累加器APSW programmer status word 程序状态字CY(PSW.7) carry 进位标志位AC(PSW.6) assistant carry 辅助进位标志位OV(PSW.2) overflow 溢出标志位PC programmer counter 程序计数器DPTR data point register 数据指针寄存器SP stack point 堆栈指针TCON timer control 定时器控制寄存器TF1 (TCON.7) timer1 flag T1中断标志位TR1(TCON.6) timer1 run T1运行控制位TF0 (TCON.5) timer0 flag T0中断标志位TR0 (TCON.4) timer0 run T0运行控制位IE1(TCON.3) interrupt1 exterior 外部中断1中断标志位IT1(TCON.2) interrupt1 touch 外部中断1触发方式选择位IE0(TCON.1) interrupt0 exterior 外部中断0中断标志位IT0(TCON.0) interrupt0 touch (0--电平触发1--下降沿触发) IE(A8H) interrupt enable 中断允许寄存器EA(IE7) enable all interrupt 中断总允许位ES(IE.4) enable serial 串口中断允许位ET1(IE.3) enable timer1T1 中断允许位EX1(IE.2) enable exterior1 外部中断1中断允许位ET0(IE.1) enable timer0 T0中断允许位EX0(IE.0) enable exterior0 外部中断0中断允许位IP(B8H) interrupt priority 中断优先级寄存器PS(IP.4) priority serial 串口优先级标志位PT1(IP.3) priority timer1 定时器1优先级标志位PX1(IP.2) priority exterior1 外部中断1优先级标志位PT0(IP.1) priority timer0 定时器0优先级标志位PX0(IP.0) priority exterior0 外部中断0优先级标志位PCON(87H) power control 电源控制和波特率选择TMOD(89H) timer mode 定时器方式控制寄存器MSB most significant bit 最高有效位LSB last significant bit 最低有效位OE output enable 输出使。

完整word版,51单片机英文及其翻译

英文翻译原文:51 Microcontroller IntroductionMicrocontrollers basic component is a central processing unit (CPU in the computing device and controller), read-only memory (usually expressed as a ROM), read-write memory (also known as Random Access Memory MRAM is usually expressed as a RAM) , input / output port (also divided into parallel port and serial port, expressed as I / O port), and so composed. In fact there is also a clock circuit microcontroller, so that during operation and control of the microcontroller, can rhythmic manner. In addition, there are so-called "break system", the system is a "janitor" role, when the microcontroller control object parameters that need to be intervention to reach a particular state, can after this "janitor" communicated to the CPU, so that CPU priorities of the external events to take appropriate counter-measures.Microcontrollers are used in a multitude of commercial applications such as modems, motor-control systems, air conditioner control systems, automotive engine and among others. The high processing speed and enhanced peripheral set of these microcontrollers make them suitable for such high-speed event-based applications. However, these critical application domains also require that these microcontrollers are highly reliable. The high reliability and low market risks can be ensured by a robust testing process and a proper tools environment for the validation of these microcontrollers both at the component and at the system level. Intel Platform Engineering department developed an object-oriented multi-threaded test environment for the validation of its AT89C51 automotive microcontrollers. The goals of this environment was not only to provide a robust testing environment for the AT89C51 automotive microcontrollers, but to develop an environment which can be easily extended and reused for the validation of several other future microcontrollers. The environment was developed in conjunction with Microsoft Foundation Classes (AT89C51). The paper describes the design and mechanism of this test environment, its interactions with various hardware/software environmental components, and how to use AT89C51.Are 8-bit microcontroller early or 4 bits. One of the most successful is the INTEL 8031, for a simple, reliable and good performance was a lot of praise. Then developed in 8031 out of MCS51 MCU Systems. SCM systems based on this system until now is still widely used. With the increased requirements of industrial control field, began a 16-bit microcontroller, but not ideal because the cost has not been very widely used. After 90 years with the great development of consumer electronics, microcontroller technology has been a huge increase. With INTEL i960 series, especially the later series of widely used ARM, 32-bit microcontroller quickly replace high-end 16-bit MCU status and enter the mainstream market. The traditional 8-bit microcontroller performance have been therapid increase capacity increase compared to 80 the number of times. Currently, high-end 32-bit microcontroller clocked over 300MHz, the performance catching the mid-90s dedicated processor, while the average model prices fall to one U.S. dollar, the most high-end model is only 10 dollars. Modern SCM systems are no longer only in the development and use of bare metal environment, a large number of proprietary embedded operating system is widely used in the full range of SCM. The handheld computers and cell phones as the core processing of high-end microcontroller can even use a dedicated Windows and Linux operating systems.SCM relies on the program, and can be modified. Through different procedures to achieve different functions, in particular special unique features, this is another device much effort needs to be done, some are great efforts are very difficult to achieve. A not very complex functions if the 50's with the United States developed 74 series, or the 60's CD4000 series of these pure hardware buttoned, then the circuit must be a large PCB board! But if the United States if the 70's with a series of successful SCM market, the result will be a drastic change! Just because you are prepared by microcomputer programs can achieve high intelligence, high efficiency and high reliability!IntroductionThe 8-bit AT89C51 CHMOS microcontrollers are designed to handle high-speed calculations and fast input/output operations. MCS 51 microcontrollers are typically used for high-speed event control systems. Commercial applications include modems, motor-control systems, printers, photocopiers, air conditioner control systems, disk drives, and medical instruments. The automotive industry use MCS 51 microcontrollers in engine-control systems, airbags, suspension systems, and antilock braking systems (ABS). The AT89C51 is especially well suited to applications that benefit from its processing speed and enhanced on-chip peripheral functions set, such as automotive power-train control, vehicle dynamic suspension, antilock braking, and stability control applications. Because of these critical applications, the market requires a reliable cost-effective controller with a low interrupt latency response, ability to service the high number of time and event driven integrated peripherals needed in real time applications, and a CPU with above average processing power in a single package. The financial and legal risk of having devices that operate unpredictably is very high. Once in the market, particularly in mission critical applications such as an autopilot or anti-lock braking system, mistakes are financiallyProhibitive. Redesign costs can run as high as a $500K, much more if the fix means back annotating it across a product family that share the same core and/or peripheral design flaw. In addition, field replacements of components are extremely expensive, as the devices are typically sealed in modules with a total value several times that of the component. To mitigate these problems, it is essential that comprehensive testing of the controllers be carried out at both the component level and system level under worst case environmental and voltage conditions. This complete and thorough validation necessitates not only a well-defined process but also a proper environment and tools to facilitate and execute the mission successfully.Intel Chandler Platform Engineering group provides postSilicon system validation (SV) of various micro-controllers and processors. The system validation process can be broken into three major parts. The type of the device and its application requirements determine which types of testing are performed on the device.The AT89C51 provides the following standard features: 4Kbytes of flash, 128 bytes of RAM, 32 I/O lines, two 16-bittimer/counters, five vector two-level interrupt architecture, a full duple ser -ail port, on-chip oscillator and clock circuitry. In addition, the AT89C51 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt sys -tem to continue functioning. The Power-down Mode saves the RAM contents but freezes the social -labor disabling all other chip functions until the next hardware reset.Pin DescriptionVCC Supply voltage.GND Ground.Port 0Port 0 is an 8-bit open-drain bi-directional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high impedance inputs.Port 0 may also be configured to be the multiplexed lowered address/data bus during accesses to external program and data memory. In this mode P0 has internal pull-ups’.Port 0 also receives the code bytes during Flash programming, and outputs the code bytes during program verification. External pull-ups are required during program verification.Port 1Port 1 is an 8-bit bi-directional I/O port with internal pullups.The Port 1 output buffers can sink/so -urge four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups.Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2Port 2 is an 8-bit bi-directional I/O port with internal pullups.The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups.Port 2 emits the high-order address byte during fetches from external program memory and during accesses to Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups.Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that uses 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that uses 8-bit addresses (MOVX @ RI); Port 2 emits the contents of the P2 Special Function Register.Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.Port 3Port 3 is an 8-bit bi-directional I/O port with internal pullups.The Port 3 output buffers can sink/soul -race four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL) because of the pull-ups.RSTReset input. A high on this pin for two machine cycles while the oscillator is running resets the device.ALE/PROGAddress Latch Enable output pulse for latching the low byte of the address during accesses to external memory.This pin is also the program pulse input (PROG) during Flash programming.In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped dui -nag each access to external DataMemory.If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.PSENProgram Store Enable is the read strobe to external program memory. When the AT89C51 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.EA/VPPExternal Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset. A should be strapped to VCC for internal program executions. This pin also receives the 12-volt programming enable voltage (VPP) during Flash programming, for parts that require 12-volt VPP.The AT89C51 code memory array is programmed byte-by byte in either programming mode. To program any nonblank byte in the on-chip Flash Memory, the entire memory must be erased using the Chip Erase Mode.Data Polling: The AT89C51 features Data Polling to indicate the end of a write cycle. During a write cycle, an attempted read of the last byte written will result in the complement of the written datum on PO.7. Once the write cycle has been completed, true data are valid on all outputs, andThe next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.Ready/Busy: The progress of byte programming can also be monitored by the RDY/BSY output signal. P3.4 is pulled low after ALE goes high during programming to indicate BUSY. P3.4 is pulled high again when programming is done to indicate READY.Program Verify: If lock bits LB1 and LB2 have not been programmed, the programmed code data can be read back via the address and data lines for verification. The lock bits cannot be verified directly. Verification of the lock bits is achieved byobserving that their features are enabled.A microcomputer interface converts information between two forms. Outside the microcomputer the information handled by an electronic system exists as a physical signal, but within the program, it is represented numerically. The function of any interface can be broken down into a number of operations which modify the data in some way, so that the process of conversion between the external and internal forms is carried out in a number of steps.An analog-to-digital converter (ADC) is used to convert a continuously variable signal to a corresponding digital form which can take any one of a fixed number of possible binary values. If the output of the transducer does not vary continuously, no ADC is necessary. In this case the signal conditioning section must convert the incoming signal to a form which can be connected directly to the next part of the interface, the input/output section of the microcomputer itself.Output interfaces take a similar form, the obvious difference being that here the flow of information is in the opposite direction; it is passed from the program to the outside world. In this case the program may call an output subroutine which supervises the operation of the interface and performs the scaling numbers which may be needed for a digital-to-analog converter (DAC). This subroutine passes information in turn to an output device which produces a corresponding electrical signal, which could be converted into analog form using a DAC. Finally the signal is conditioned (usually amplified) to a form suitable for operating an actuator.The signals used within microcomputer circuits are almost always too small to be connected directly to the “outside world” and some kind of interface must be used to translate them to a more appropriate form. The design of section of interface circuits is one of the most important tasks facing the engineer wishing to apply microcomputers. We have seen that in microcomputers information is represented as discrete patterns of bits; this digital form is most useful when the microcomputer is to be connected to equipment which can only be switched on or off, where each bit might represent the state of a switch or actuator.To solve real-world problems, a microcontroller must have more than just a CPU, a program, and a data memory. In addition, it must contain hardware allowing the CPU to access information from the outside world. Once the CPU gathers information and processes the data, it must also be able to effect change on some portion of the outside world. T hese hardware devices, called peripherals, are the CPU’s window t o the outside.The most basic form of peripheral available on microcontrollers is the general purpose I70 port. Each of the I/O pins can be used as either an input or an output. The function of each pin is determined by setting or clearing corresponding bits in a corresponding data direction register during the initialization stage of a program. Each output pin may be driven to either a logic one or a logic zero by using CPU instructions to pin may be viewed (or read.) by the CPU using program instructions.Some type of serial unit is included on microcontrollers to allow the CPU to communicate bit-serially with external devices. Using a bit serial format instead of bit-parallel format requires fewer I/O pins to perform the communication function, which makes it less expensive, but slower. Serial transmissions are performed either synchronously or asynchronously.Its applicationsSCM is widely used in instruments and meters, household appliances, medical equipment, aerospace, specialized equipment, intelligent management and process control fields, roughly divided into the following several areas:SCM has a small size, low power consumption, controlling function, expansion flexibility, the advantages of miniaturization and ease of use, widely used instrument, combining different types of sensors can be realized, such as voltage, power, frequency, humidity, temperature, flow, speed, thickness, angle, length, hardness, elemental, physical pressure measurement. SCM makes use of digital instruments, intelligence, miniaturization, and functionality than the use of more powerful electronic or digital circuits. Such as precision measuring equipment (power meter, oscilloscope, various analytical instrument).译文:51单片机简介单片机的基本组成是由中央处理器(即CPU中的运算器和控制器)、只读存贮器(通常表示为ROM)、读写存贮器(又称随机存贮器通常表示为RAM)、输入/输出口(又分为并行口和串行口,表示为I/O口)等等组成。

51单片机英文及其翻译

英文翻译原文:51 Microcontroller IntroductionMicrocontrollers basic component is a central processing unit (CPU in the computing device and controller), read-only memory (usually expressed as a ROM), read-write memory (also known as Random Access Memory MRAM is usually expressed as a RAM) , input / output port (also divided into parallel port and serial port, expressed as I / O port), and so composed. In fact there is also a clock circuit microcontroller, so that during operation and control of the microcontroller, can rhythmic manner. In addition, there are so-called "break system", the system is a "janitor" role, when the microcontroller control object parameters that need to be intervention to reach a particular state, can after this "janitor" communicated to the CPU, so that CPU priorities of the external events to take appropriate counter-measures.Microcontrollers are used in a multitude of commercial applications such as modems, motor-control systems, air conditioner control systems, automotive engine and among others. The high processing speed and enhanced peripheral set of these microcontrollers make them suitable for such high-speed event-based applications. However, these critical application domains also require that these microcontrollers are highly reliable. The high reliability and low market risks can be ensured by a robust testing process and a proper tools environment for the validation of these microcontrollers both at the component and at the system level. Intel Platform Engineering department developed an object-oriented multi-threaded test environment for the validation of its AT89C51 automotive microcontrollers. The goals of this environment was not only to provide a robust testing environment for the AT89C51 automotive microcontrollers, but to develop an environment which can be easily extended and reused for the validation of several other future microcontrollers. The environment was developed in conjunction with Microsoft Foundation Classes (AT89C51). The paper describes the design and mechanism of this test environment, its interactions with various hardware/software environmental components, and how to use AT89C51.Are 8-bit microcontroller early or 4 bits. One of the most successful is the INTEL 8031, for a simple, reliable and good performance was a lot of praise. Then developed in 8031 out of MCS51 MCU Systems. SCM systems based on this system until now is still widely used. With the increased requirements of industrial control field, began a 16-bit microcontroller, but not ideal because the cost has not been very widely used. After 90 years with the great development of consumer electronics, microcontroller technology has been a huge increase. With INTEL i960 series, especially the later series of widely used ARM, 32-bit microcontroller quickly replace high-end 16-bit MCU status and enter the mainstream market. The traditional 8-bit microcontroller performance have been therapid increase capacity increase compared to 80 the number of times. Currently, high-end 32-bit microcontroller clocked over 300MHz, the performance catching the mid-90s dedicated processor, while the average model prices fall to one U.S. dollar, the most high-end model is only 10 dollars. Modern SCM systems are no longer only in the development and use of bare metal environment, a large number of proprietary embedded operating system is widely used in the full range of SCM. The handheld computers and cell phones as the core processing of high-end microcontroller can even use a dedicated Windows and Linux operating systems.SCM relies on the program, and can be modified. Through different procedures to achieve different functions, in particular special unique features, this is another device much effort needs to be done, some are great efforts are very difficult to achieve. A not very complex functions if the 50's with the United States developed 74 series, or the 60's CD4000 series of these pure hardware buttoned, then the circuit must be a large PCB board! But if the United States if the 70's with a series of successful SCM market, the result will be a drastic change! Just because you are prepared by microcomputer programs can achieve high intelligence, high efficiency and high reliability!IntroductionThe 8-bit AT89C51 CHMOS microcontrollers are designed to handle high-speed calculations and fast input/output operations. MCS 51 microcontrollers are typically used for high-speed event control systems. Commercial applications include modems, motor-control systems, printers, photocopiers, air conditioner control systems, disk drives, and medical instruments. The automotive industry use MCS 51 microcontrollers in engine-control systems, airbags, suspension systems, and antilock braking systems (ABS). The AT89C51 is especially well suited to applications that benefit from its processing speed and enhanced on-chip peripheral functions set, such as automotive power-train control, vehicle dynamic suspension, antilock braking, and stability control applications. Because of these critical applications, the market requires a reliable cost-effective controller with a low interrupt latency response, ability to service the high number of time and event driven integrated peripherals needed in real time applications, and a CPU with above average processing power in a single package. The financial and legal risk of having devices that operate unpredictably is very high. Once in the market, particularly in mission critical applications such as an autopilot or anti-lock braking system, mistakes are financiallyProhibitive. Redesign costs can run as high as a $500K, much more if the fix means back annotating it across a product family that share the same core and/or peripheral design flaw. In addition, field replacements of components are extremely expensive, as the devices are typically sealed in modules with a total value several times that of the component. To mitigate these problems, it is essential that comprehensive testing of the controllers be carried out at both the component level and system level under worst case environmental and voltage conditions. This complete and thorough validation necessitates not only a well-defined process but also a proper environment and tools to facilitate and execute the mission successfully.Intel Chandler Platform Engineering group provides postSilicon system validation (SV) of various micro-controllers and processors. The system validation process can be broken into three major parts. The type of the device and its application requirements determine which types of testing are performed on the device.The AT89C51 provides the following standard features: 4Kbytes of flash, 128 bytes of RAM, 32 I/O lines, two 16-bittimer/counters, five vector two-level interrupt architecture, a full duple ser -ail port, on-chip oscillator and clock circuitry. In addition, the AT89C51 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt sys -tem to continue functioning. The Power-down Mode saves the RAM contents but freezes the social -labor disabling all other chip functions until the next hardware reset.Pin DescriptionVCC Supply voltage.GND Ground.Port 0Port 0 is an 8-bit open-drain bi-directional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high impedance inputs.Port 0 may also be configured to be the multiplexed lowered address/data bus during accesses to external program and data memory. In this mode P0 has internal pull-ups’.Port 0 also receives the code bytes during Flash programming, and outputs the code bytes during program verification. External pull-ups are required during program verification.Port 1Port 1 is an 8-bit bi-directional I/O port with internal pullups.The Port 1 output buffers can sink/so -urge four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups.Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2Port 2 is an 8-bit bi-directional I/O port with internal pullups.The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups.Port 2 emits the high-order address byte during fetches from external program memory and during accesses to Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups.Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that uses 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that uses 8-bit addresses (MOVX @ RI); Port 2 emits the contents of the P2 Special Function Register.Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.Port 3Port 3 is an 8-bit bi-directional I/O port with internal pullups.The Port 3 output buffers can sink/soul -race four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL) because of the pull-ups.RSTReset input. A high on this pin for two machine cycles while the oscillator is running resets the device.ALE/PROGAddress Latch Enable output pulse for latching the low byte of the address during accesses to external memory.This pin is also the program pulse input (PROG) during Flash programming.In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped dui -nag each access to external DataMemory.If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.PSENProgram Store Enable is the read strobe to external program memory. When the AT89C51 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.EA/VPPExternal Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset. A should be strapped to VCC for internal program executions. This pin also receives the 12-volt programming enable voltage (VPP) during Flash programming, for parts that require 12-volt VPP.The AT89C51 code memory array is programmed byte-by byte in either programming mode. To program any nonblank byte in the on-chip Flash Memory, the entire memory must be erased using the Chip Erase Mode.Data Polling: The AT89C51 features Data Polling to indicate the end of a write cycle. During a write cycle, an attempted read of the last byte written will result in the complement of the written datum on PO.7. Once the write cycle has been completed, true data are valid on all outputs, andThe next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.Ready/Busy: The progress of byte programming can also be monitored by the RDY/BSY output signal. P3.4 is pulled low after ALE goes high during programming to indicate BUSY. P3.4 is pulled high again when programming is done to indicate READY.Program Verify: If lock bits LB1 and LB2 have not been programmed, the programmed code data can be read back via the address and data lines for verification. The lock bits cannot be verified directly. Verification of the lock bits is achieved byobserving that their features are enabled.A microcomputer interface converts information between two forms. Outside the microcomputer the information handled by an electronic system exists as a physical signal, but within the program, it is represented numerically. The function of any interface can be broken down into a number of operations which modify the data in some way, so that the process of conversion between the external and internal forms is carried out in a number of steps.An analog-to-digital converter (ADC) is used to convert a continuously variable signal to a corresponding digital form which can take any one of a fixed number of possible binary values. If the output of the transducer does not vary continuously, no ADC is necessary. In this case the signal conditioning section must convert the incoming signal to a form which can be connected directly to the next part of the interface, the input/output section of the microcomputer itself.Output interfaces take a similar form, the obvious difference being that here the flow of information is in the opposite direction; it is passed from the program to the outside world. In this case the program may call an output subroutine which supervises the operation of the interface and performs the scaling numbers which may be needed for a digital-to-analog converter (DAC). This subroutine passes information in turn to an output device which produces a corresponding electrical signal, which could be converted into analog form using a DAC. Finally the signal is conditioned (usually amplified) to a form suitable for operating an actuator.The signals used within microcomputer circuits are almost always too small to be connected directly to the “outside world” and some kind of interface must be used to translate them to a more appropriate form. The design of section of interface circuits is one of the most important tasks facing the engineer wishing to apply microcomputers. We have seen that in microcomputers information is represented as discrete patterns of bits; this digital form is most useful when the microcomputer is to be connected to equipment which can only be switched on or off, where each bit might represent the state of a switch or actuator.To solve real-world problems, a microcontroller must have more than just a CPU, a program, and a data memory. In addition, it must contain hardware allowing the CPU to access information from the outside world. Once the CPU gathers information and processes the data, it must also be able to effect change on some portion of the outside world. T hese hardware devices, called peripherals, are the CPU’s window t o the outside.The most basic form of peripheral available on microcontrollers is the general purpose I70 port. Each of the I/O pins can be used as either an input or an output. The function of each pin is determined by setting or clearing corresponding bits in a corresponding data direction register during the initialization stage of a program. Each output pin may be driven to either a logic one or a logic zero by using CPU instructions to pin may be viewed (or read.) by the CPU using program instructions.Some type of serial unit is included on microcontrollers to allow the CPU to communicate bit-serially with external devices. Using a bit serial format instead of bit-parallel format requires fewer I/O pins to perform the communication function, which makes it less expensive, but slower. Serial transmissions are performed either synchronously or asynchronously.Its applicationsSCM is widely used in instruments and meters, household appliances, medical equipment, aerospace, specialized equipment, intelligent management and process control fields, roughly divided into the following several areas:SCM has a small size, low power consumption, controlling function, expansion flexibility, the advantages of miniaturization and ease of use, widely used instrument, combining different types of sensors can be realized, such as voltage, power, frequency, humidity, temperature, flow, speed, thickness, angle, length, hardness, elemental, physical pressure measurement. SCM makes use of digital instruments, intelligence, miniaturization, and functionality than the use of more powerful electronic or digital circuits. Such as precision measuring equipment (power meter, oscilloscope, various analytical instrument).译文:51单片机简介单片机的基本组成是由中央处理器(即CPU中的运算器和控制器)、只读存贮器(通常表示为ROM)、读写存贮器(又称随机存贮器通常表示为RAM)、输入/输出口(又分为并行口和串行口,表示为I/O口)等等组成。

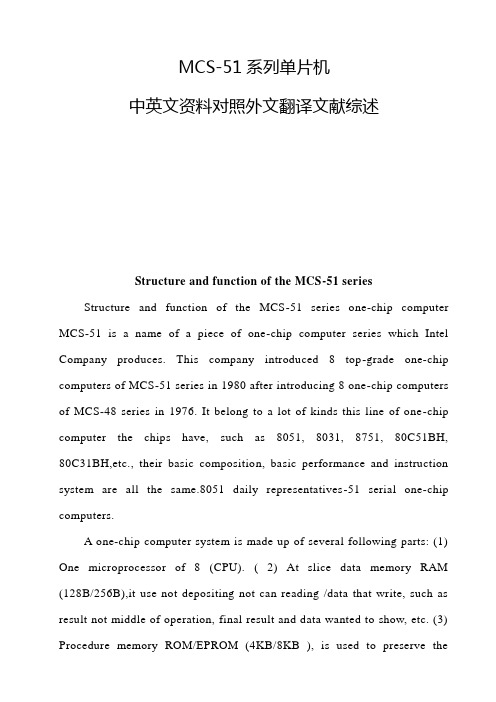

(完整版)MCS-51系列单片机中英文资料对照外文翻译文献综述

MCS-51系列单片机中英文资料对照外文翻译文献综述Structure and function of the MCS-51 seriesStructure and function of the MCS-51 series one-chip computer MCS-51 is a name of a piece of one-chip computer series which Intel Company produces. This company introduced 8 top-grade one-chip computers of MCS-51 series in 1980 after introducing 8 one-chip computers of MCS-48 series in 1976. It belong to a lot of kinds this line of one-chip computer the chips have, such as 8051, 8031, 8751, 80C51BH, 80C31BH,etc., their basic composition, basic performance and instruction system are all the same.8051 daily representatives-51 serial one-chip computers.A one-chip computer system is made up of several following parts: (1) One microprocessor of 8 (CPU). ( 2) At slice data memory RAM (128B/256B),it use not depositing not can reading /data that write, such as result not middle of operation, final result and data wanted to show, etc. (3) Procedure memory ROM/EPROM (4KB/8KB ), is used to preserve theprocedure , some initial data and form in slice. But does not take ROM/EPROM within some one-chip computers, such as 8031, 8032.(4) Four 8 run side by side I/O interface P0 four P3, each mouth can use as introduction , may use as exporting too. (5) Two timer / counter, each timer / counter may set up and count in the way, used to count to the external incident, can set up into a timing way too, and can according to count or result of timing realize the control of the computer. (6) Five cut off cutting off the control system of the source. (7) One all duplex serial I/O mouth of UART (universal asynchronous receiver/transmitter (UART) ), is it realize one-chip computer or one-chip computer and serial communication of computer to use for. (8) Stretch oscillator and clock produce circuit, quartz crystal finely tune electric capacity need outer. Allow oscillation frequency as 12 megahertz now at most. Every the above-mentioned part was joined through the inside data bus .Among them, CPU is a core of the one-chip computer, it is the control of the computer and command centre, made up of such parts as arithmetic unit and controller , etc.. The arithmetic unit can carry on 8 persons of arithmetic operation and unit ALU of logic operation while including one, the 1 storing device temporaries of 8, storing device 2 temporarily, 8's accumulation device ACC, register B and procedure state register PSW, etc. Person who accumulate ACC count by 2 input ends entered of checking etc. temporarily as one operation often, come from person who store 1 operation is it is it make operation to go on to count temporarily , operation result and loop back ACC with another one. Inaddition, ACC is often regarded as the transfer station of data transmission on 8051 inside. The same as general microprocessor, it is the busiest register. Help remembering that agreeing with a express in the order. The controller includes the procedure counter, the order is deposited, the order deciphering, the oscillator and timing circuit, etc. The procedure counter is made up of counter of 8 for two, amounts to 16. It is a byte address counter of the procedure in fact, the content is the next IA that will carried out in PC. The content which changes it can change the direction that the procedure carries out. Shake the circuit in 8051 one-chip computers, only need outer quartz crystal and frequency to finely tune the electric capacity, its frequency range is its 12MHZ of 1.2MHZ. This pulse signal, as 8051 basic beats of working, namely the minimum unit of time. 8051 is the same as other computers, the work in harmony under the control of the basic beat, just like an orchestra according to the beat play that is commanded.There are ROM (procedure memory , can only read ) and RAM in 8051 slices (data memory, can is it can write ) two to read, they have each independent memory address space, dispose way to be the same with general memory of computer. Procedure 8051 memory and 8751 slice procedure memory capacity 4KB, address begin from 0000H, used for preserving the procedure and form constant. Data 8051- 8751 8031 of memory data memory 128B, address false 00FH, using for middle result to deposit operation, the data are stored temporarily and the data are buffered. In RAM of this 128B, there is unit of 32 bytes that can be appointed as the jobregister, this and general microprocessor is different, 8051 slice RAM and job register rank one formation the same to arrange the location. It is not very the same that the memory of MCS-51 series one-chip computer and general computer disposes the way in addition. General computer for first address space, ROM and RAM can arrange in different space within the range of this address at will, namely the addresses of ROM and RAM, with distributing different address space in a formation. While visiting the memory, corresponding and only an address Memory unit, can ROM, it can be RAM too, and by visiting the order similarly. This kind of memory structure is called the structure of Princeton. 8051 memories are divided into procedure memory space and data memory space on the physics structure, there are four memory spaces in all: The procedure stores in one and data memory space outside data memory and one in procedure memory space and one outside one, the structure forms of this kind of procedure device and data memory separated form data memory, called Harvard structure. But use the angle from users, 8051 memory address space is divided into three kinds: (1) In the slice, arrange blocks of FFFFH, 0000H of location, in unison outside the slice (use 16 addresses). (2) The data memory address space outside one of 64KB, the address is arranged from 0000H 64KB FFFFH (with 16 addresses) too to the location. (3) Data memory address space of 256B (use 8 addresses). Three above-mentioned memory space addresses overlap, for distinguishing and designing the order symbol of different data transmission in the instruction system of 8051: CPU visit slice, ROM orderspend MOVC , visit block RAM order uses MOVX outside the slice, RAM order uses MOV to visit in slice.8051 one-chip computer have four 8 walk abreast I/O ports, call P0, P1, P2 and P3. Each port is 8 accurate two-way mouths, accounts for 32 pins altogether. Every one I/O line can be used as introduction and exported independently. Each port includes a latch (namely special function register), one exports the driver and a introduction buffer. Make data can latch when outputting, data can buffer when making introduction, but four function of pass away these self-same. Expand among the system of memory outside having slice, four ports these may serve as accurate two-way mouth of I/O in common use. Expand among the system of memory outside having slice, P2 mouth see high 8 address off; P0 mouth is a two-way bus, send the introduction of 8 low addresses and data / export in timesharing The circuit of 8051 one-chip computers and four I/O ports is very ingenious in design. Familiar with I/O port logical circuit, not only help to use port correctly and rationally, and will inspire to designing the peripheral logical circuit of one-chip computer to some extent. Load ability and interface of port have certain requirement, because output grade, P0 of mouth and P1 end output, P3 of mouth grade different at structure, so, the load ability and interface of its door demand to have nothing in common with each other. P0 mouth is different from other mouth, its output grade draws the resistance supremely. When using it as the mouth in common use, output grade is it leak circuit to turn on, is it urge NMOS draw the resistanceon taking to be outer with it while inputting to go out to fail. When being used as introduction, should write"1" to a latch first. Every one with P0 mouth can drive 8 Model LS TTL load to export. P1 mouth is an accurate two-way mouth too, used as I/O in common use. Different from P0 mouth output of circuit its, draw load resistance link with power on inside have. In fact, the resistance is that two effects are in charge of FET and together: One FET is in charge of load, its resistance is regular. Another one can is it lead to work with close at two state, make its President resistance value change approximate 0 or group value heavy two situation very. When it is 0 that the resistance is approximate, can draw the pin to the high level fast; when resistance value is very large, P1 mouth high electricity at ordinary times, can is it draw electric current load to offer outwards, draw electric current load to offer outwards, draw the resistance on needn't answer and thinking. Here when the port is used as introduction, must write into 1 to the corresponding latch first too, make FET end relatively about 20,000 ohms because of load resistance in scene and because 40,000 ohms, will not exert an influence on the data that are input. The structure of P2 some mouth is similar to P0 mouth, there are MUX switches. Is it similar to mouth partly to urge, but mouth large a conversion controls some than P1.P3 mouth one multi-functional port, mouth getting many than P1 it have "3 doors and 4 buffers". Two parts there, make her besides accurate two-way function with P1 mouth just, can also use the second function of every pin, "and" door 3 functions one switch in fact, it determines to be to output data of latch tooutput second signal of function. Act as W=At 1 o'clock, output Q end signal; act as Q=At 1 o'clock, can output W line signal. At the time of programming, it is that the first function is still the second function but needn't have software that set up P3 mouth in advance .It hardware not inside is the automatic to have two function outputted when CPU carries on SFR and seeks the location to visit to P3 mouth/at not lasting lining, there are inside hardware latch Qs=1. The operation principle of P3 mouth is similar to P1 mouth.Output grade, P3 of mouth, P1 of P1, connect with inside have load resistance of drawing, every one of they can drive 4 Model LS TTL load to output. As while inputting the mouth, any TTL or NMOS circuit can drive P1 of 8051 one-chip computers as P3 mouth in a normal way. Because draw resistance on output grade of them have, can open a way collector too or drain-source resistance is it urge to open a way, do not need to have the resistance of drawing outer. Mouths are all accurate two-way mouths too. When the conduct is input, must write the corresponding port latch with 1 first. As to 80C51 one-chip computer, port can only offer milliampere of output electric currents, is it output mouth go when urging one ordinary basing of transistor to regard as, should contact a resistance among the port and transistor base, in order to the electricity while restraining the high level from exporting P1~P3 Being restored to the throne is the operation of initializing of an one-chip computer. Its main function is to turn PC into 0000H initially, make the one-chip computer begin to hold the conductprocedure from unit 0000H. Except that the ones that enter the system are initialized normally, as because procedure operate it make mistakes or operate there aren't mistake, in order to extricate oneself from a predicament , need to be pressed and restored to the throne the key restarting too. It is an input end which is restored to the throne the signal in 8051 China RST pin. Restore to the throne signal high level effective, should sustain 24 shake cycle (namely 2 machine cycles) the above its effective times. If 6 of frequency of utilization brilliant to shake, restore to the throne signal duration should exceed 4 delicate to finish restoring to the throne and operating. Produce the logic picture of circuit which is restored to the throne the signal: restore to the throne the circuit and include two parts outside in the chip entirely. Outside that circuit produce to restore to the throne signal (RST) hand over to Schmitt's trigger, restore to the throne circuit sample to output , Schmitt of trigger constantly in each S5P2 , machine of cycle in having one more , then just got and restored to the throne and operated the necessary signal inside. Restore to the throne resistance of circuit generally, electric capacity parameter suitable for 6 brilliant to shake, can is it restore to the throne signal high level duration greater than 2 machine cycles to guarantee. Being restored to the throne in the circuit is simple, its function is very important. Pieces of one-chip computer system could normal running, should first check it can restore to the throne not succeeding. Checking and can pop one's head and monitor the pin with the oscilloscope tentatively, push and is restored to the throne the key, the wave form that observes andhas enough range is exported (instantaneous), can also through is it restore to the throne circuit group holding value carry on the experiment to change.MCS-51系列单片机的功能和结构MSC-51系列单片机具有一个单芯片电脑的结构和功能,它是英特尔公司的系列产品的名称。

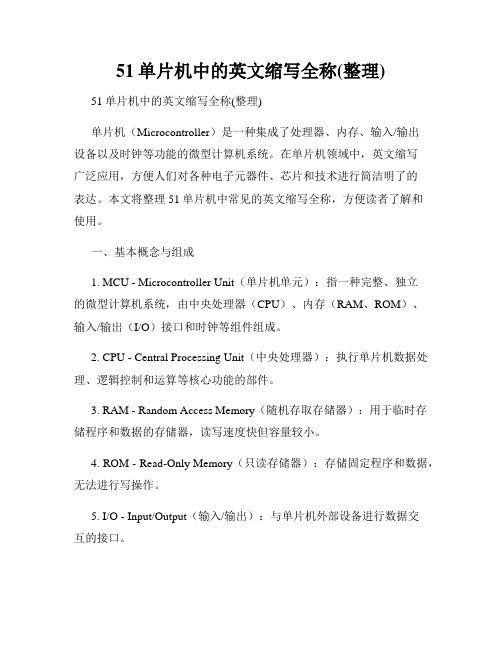

51单片机中的英文缩写全称(整理)

51单片机中的英文缩写全称(整理) 51单片机中的英文缩写全称(整理)单片机(Microcontroller)是一种集成了处理器、内存、输入/输出设备以及时钟等功能的微型计算机系统。

在单片机领域中,英文缩写广泛应用,方便人们对各种电子元器件、芯片和技术进行简洁明了的表达。

本文将整理51单片机中常见的英文缩写全称,方便读者了解和使用。

一、基本概念与组成1. MCU - Microcontroller Unit(单片机单元):指一种完整、独立的微型计算机系统,由中央处理器(CPU)、内存(RAM、ROM)、输入/输出(I/O)接口和时钟等组件组成。

2. CPU - Central Processing Unit(中央处理器):执行单片机数据处理、逻辑控制和运算等核心功能的部件。

3. RAM - Random Access Memory(随机存取存储器):用于临时存储程序和数据的存储器,读写速度快但容量较小。

4. ROM - Read-Only Memory(只读存储器):存储固定程序和数据,无法进行写操作。

5. I/O - Input/Output(输入/输出):与单片机外部设备进行数据交互的接口。

6. Clock - 时钟:提供单片机工作所需的时序信号,控制指令执行和数据传输的节奏。

二、核心技术与模块1. ISP - In-System Programming(系统编程):通过特定的下载器将程序和数据下载到单片机内部,实现在线编程。

2. UART - Universal Asynchronous Receiver/Transmitter(通用异步收发器):用于实现串行通信的接口。

3. ADC - Analog-to-Digital Converter(模数转换器):将模拟信号转换为相应的数字量。

4. PWM - Pulse Width Modulation(脉宽调制):通过改变信号的脉宽来控制电气或电子设备的输出功率。

51单片机英文缩写全称(整理最全)

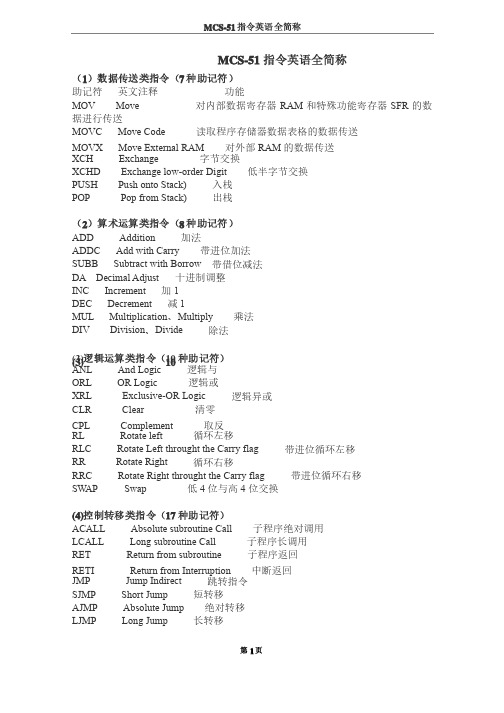

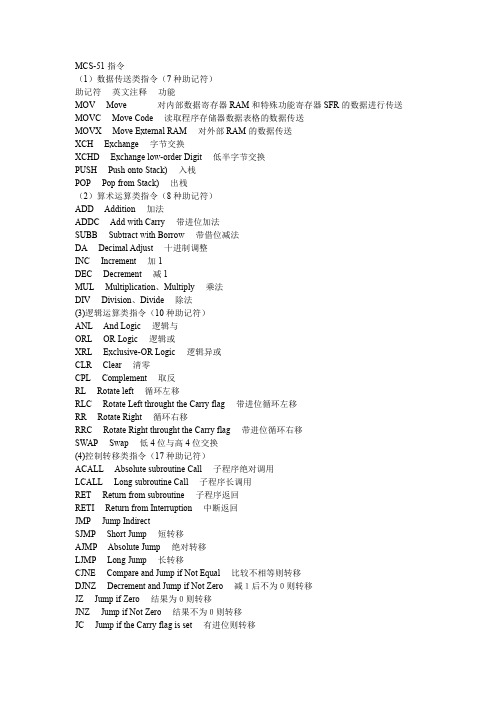

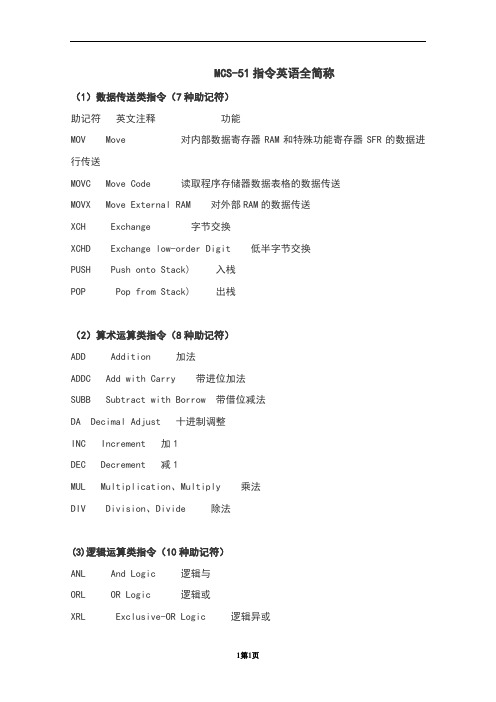

MCS-51指令英语全简称第1页MCS-51指令英语全简称(1)数据传送类指令(7种助记符)助记符 英文注释 功能MOV Move 对内部数据寄存器RAM 和特殊功能寄存器SFR 的数据进行传送MOVC Move Code 读取程序存储器数据表格的数据传送MOVX Move External RAM 对外部RAM 的数据传送 XCH Exchange 字节交换XCHD Exchange low-order Digit 低半字节交换PUSH Push onto Stack) 入栈POP Pop from Stack) 出栈(2)算术运算类指令(8种助记符)ADD Addition 加法ADDC Add with Carry 带进位加法SUBB Subtract with Borrow 带借位减法DA Decimal Adjust 十进制调整INC Increment 加1DEC Decrement 减1MUL Multiplication 、Multiply 乘法DIV Division 、Divide 除法(3)逻辑运算类指令(10种助记符)ANL And Logic 逻辑与ORL OR Logic 逻辑或XRL Exclusive-OR Logic 逻辑异或CLR Clear 清零CPL Complement 取反 RL Rotate left 循环左移RLC Rotate Left throught the Carry flag 带进位循环左移RR Rotate Right 循环右移RRC Rotate Right throught the Carry flag 带进位循环右移SW AP Swap 低4位与高4位交换(4)控制转移类指令(17种助记符)ACALL Absolute subroutine Call 子程序绝对调用LCALL Long subroutine Call 子程序长调用RET Return from subroutine 子程序返回RETI Return from Interruption 中断返回 JMP Jump Indirect 跳转指令SJMP Short Jump 短转移AJMP Absolute Jump 绝对转移LJMP Long Jump 长转移CJNE Compare and Jump if Not Equal 比较不相等则转移DJNZ Decrement and Jump if Not Zero 减1后不为0则转移JZ Jump if Zero 结果为0则转移JNZ Jump if Not Zero 结果不为0则转移JC Jump if the Carry flag is set 有进位则转移JNC Jump if Not Carry 无进位则转移JB Jump if the Bit is set) B 位为1则转移JNB Jump if the Bit is Not set B 位为0则转移JBC Jump if the Bit is set and Clear the bit 位为1则转移,并清除该位 NOP No Operation 空操作(5)位操作指令(1种助记符)SETB Set Bit 置位伪指令助记符 英文注释 功能ORG Origin 起始地址DB Define Byte 定义字节DW Define Word 定义字义EQU Equal 赋值(右赋左) 等于DA T A Data 数据赋值(右赋左)XDA T A External Data 外部数据赋值(右赋左)BIT Bit 位地址赋值END End 汇编结束DS Define storage 定义存储空间51外部引脚缩写 英文解释 中文解释RST (9) Reset 复位信号引脚RxD (10--P3.0) Receive Data 串口接收端TxD (11--P3.1) Transmit Data 串口发送端INT0(————)( 12--P3.2) Interrupt0 外部中断0信号输入引脚INT1(————) (13--P3.3) Interrupt1 外部中断1信号输入引脚T0 (14--P3.4) Timer0 定时/计数器0输入信号引脚T1 (15--P3.5) Timer1 定时/计数器1输入信号引脚WR(———) (16--P3.6) write 存储器的写信号写信号引脚RD(———) (17--P3.7) read 读信号引脚PSEN(—————) (29) progammer saving enable 外部程序存储器读选通信号ALE (30) Address Latch Enable 地址锁存允许信号EA(———) (31) enable 外部ROM选择信号51内部寄存器SFR special funtion register 特殊功能寄存器ACC accumulate 累加器APSW progammer status word 程序状态字CY (PSW.7) carry 进位标志位AC (PSW.6) assistant carry 辅助进位标志位OV (PSW.2) overflow 溢出标志位PC progammer counter 程序计数器DPTR data point register 数据指针寄存器SP stack point 堆栈指针TCON timer control 定时器控制寄存器TF1 (TCON.7) Timer1 flag T1中断标志位TR1 (TCON.6) Timer1 Run T1运行控制位TF0 (TCON.5) Timer0 flag T0中断标志位TR0 (TCON.4) Timer0 Run T0运行控制位IE1 (TCON.3) Interrupt1 exterior 外部中断1中断标志位IT1 (TCON.2) Interrupt1 touch 外部中断1 触发方式选择位 IE0 (TCON.1) Interrupt0 exterior 外部中断0中断标志位IT0 (TCON.0) Interrupt0 touch 0-电平触发 1-下降沿触发IE (A8H) interrupt enable 中断允许寄存器EA (IE.7) enable all interrupt 中断总允许位ES (IE.4) enable serial 串行口中断允许位ET1 (IE.3) enable timer 1 T1中断允许位EX1 (IE.2) enable exterior 1 外部中断1中断允许位ET0 (IE.1) enable timer 0 T0中断允许位EX0 (IE.0) enable exterior 0 外部中断0中断允许位IP (B8H) interrupt priority 中断优先级寄存器PS (IP.4) priority serial 串口优先级标志位PT1 (IP.3) priority timer 1 定时器1优先级标志位PX1 (IP.2) priority exterior 1 外部中断1优先级标志位PT0 (IP.1) priority timer 0 定时器0优先级标志位PX0 (IP.0) priority exterior 0 外部中断0优先级标志位 PCON (87H) power control 电源控制和波特率选择TMOD (89H) timer mode 定时器方式控制寄存器MSB = most significant bit//最高有效位LSB = last significant bit//最低有效位OE = output enable //输出使能PROG progamme 程序XTAL:External Crystal Oscillator,外部晶体振荡器 CLKOUT:Clock out,时钟输出BUSWDITH:总线宽度Vref:参考电压(带ADC的单片机中有的)RESET:复位,重启ACH:??HSO:High Speed Output,高速输出HSI:High Speed Input:高速输入INST:Instruction,指令READY:就绪,总线中的就绪信号或引脚NMI:No Mask Interruput (Input):不可屏蔽的中断请求(输入)RXD:Receive Data ,接收串行数据,单片机中有UART/USART功能的串行数据 输入引脚TXD:Transmit Data,发送串行数据,单片机中有UART/USART功能的串行数据输出引脚BHE:Bank High Enable:存储器的高位允许,如在80286系统中RAM的组织为16位的,分为高8位和低8位数据,分别的控制信号为BHE和BLEALE:Address Latch Enable,地址信号锁定允许,这在早期Intel总线结构中是必不可少的信号,常和锁存器使用来分离地址/数据复用端口的地址和数据信。

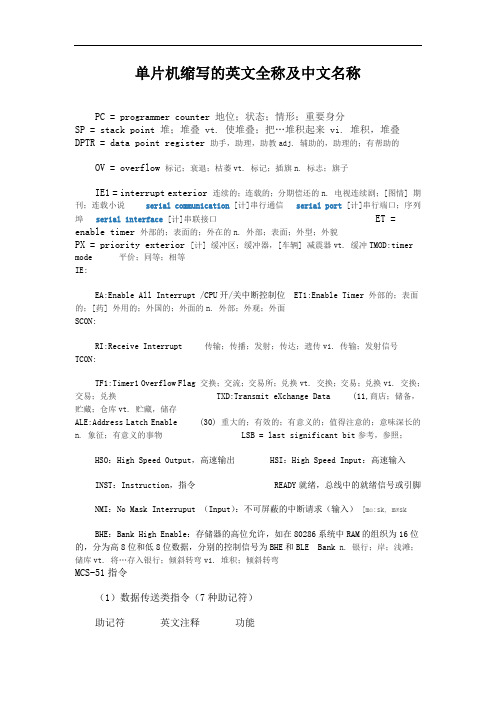

51单片机缩写的英文全称及中文名称

单片机缩写的英文全称及中文名称PC = programmer counter 地位;状态;情形;重要身分SP = stack point 堆;堆叠 vt. 使堆叠;把…堆积起来 vi. 堆积,堆叠DPTR = data point register 助手,助理,助教adj. 辅助的,助理的;有帮助的OV = overflow 标记;衰退;枯萎vt. 标记;插旗n. 标志;旗子IE1 = interrupt exterior 连续的;连载的;分期偿还的n. 电视连续剧;[图情] 期刊;连载小说serial communication [计]串行通信serial port [计]串行端口;序列埠serial interface [计]串联接口ET = enable timer 外部的;表面的;外在的n. 外部;表面;外型;外貌PX = priority exterior [计] 缓冲区;缓冲器,[车辆] 减震器vt. 缓冲TMOD:timer mode 平价;同等;相等IE:EA:Enable All Interrupt /CPU开/关中断控制位 ET1:Enable Timer 外部的;表面的;[药] 外用的;外国的;外面的n. 外部;外观;外面SCON:RI:Receive Interrupt 传输;传播;发射;传达;遗传vi. 传输;发射信号TCON:TF1:Timer1 Overflow Flag 交换;交流;交易所;兑换vt. 交换;交易;兑换vi. 交换;交易;兑换TXD:Transmit eXchange Data (11,商店;储备,贮藏;仓库vt. 贮藏,储存ALE:Address Latch Enable (30) 重大的;有效的;有意义的;值得注意的;意味深长的n. 象征;有意义的事物LSB = last significant bit参考,参照;HSO:High Speed Output,高速输出 HSI:High Speed Input:高速输入INST:Instruction,指令 READY就绪,总线中的就绪信号或引脚NMI:No Mask Interruput (Input):不可屏蔽的中断请求(输入)[mɑ:sk, mæskBHE:Bank High Enable:存储器的高位允许,如在80286系统中RAM的组织为16位的,分为高8位和低8位数据,分别的控制信号为BHE和BLE Bank n. 银行;岸;浅滩;储库vt. 将…存入银行;倾斜转弯vi. 堆积;倾斜转弯MCS-51指令(1)数据传送类指令(7种助记符)助记符英文注释功能MOV Move 对内部数据寄存器RAM和特殊功能寄存器SFR的数据进行传送MOVC Move Code 读取程序存储器数据表格的数据传送MOVX Move External RAM 对外部RAM的数据传送XCH Exchange 字节交换XCHD Exchange low-order Digit ['didʒit]低半字节交换POP Pop from Stack) 出栈 PUSH Push onto ['ɔntu, -tə] Stack) 入栈(2)算术运算类指令(8种助记符)ADD Addition 加法 ADDC Add withCarry 带进位加法SUBB Subtract [səb'trækt] with Borrow 带借位减法vt. 减去;扣DA Decimal ['desiməl]adj. 小数的;十进位的n. 小数Adjust [ə'dʒʌst]调整十进制调整INC Increment ['inkrimənt加1DEC Decrement 'dekrimənt]减1MUL Multiplication、Multiply 乘法[,mʌltipli'keiʃən n. [数] 乘法;增加['mʌltiplai vt. 乘;使增加;使繁殖;使相乘vi. 乘;繁殖;增加adv. 多样地;复合地adj. 多层的;多样的DIV Division[di'viʒən n. [数] 除法;部门;分割;师(军队);赛区、Divide 除法di'vaid vt. 划分;除;分开;使产生分歧vi. 分开;意见分歧n. [地理] 分水岭,分水线(3)逻辑运算类指令(10种助记符)ANL And Logic 逻辑与'lɔdʒik] n. 逻辑;逻辑学;逻辑性adj. 逻辑的ORL OR Logic 逻辑或CLR Clear kliə]清零XRL Exclusive-OR Logic 逻辑异或[ik'sklu:siv] adj. 独有的;排外的;专一的n. 独家新闻;独家经营的项目;排外者CPL Complement 取反'kɔmplimənt] n. 补语;余角;补足物vt. 补足,补助RL Rotate left 循环左移[rəu'teit, 'rəut-, 'rəuteit vi. 旋转;循环vt. 使旋转;使转动;使轮流adj. [植] 辐状的RLC Rotate Left throught the Carry flag 带进位循环左移RR Rotate Right 循环右移RRC Rotate Right throught the Carry flag 带进位循环右移SWAP Swap 低4位与高4位交换[swɔp, swɔ:p n. 交换;交换之物vt. 与...交换;以...作交换vi. 交换;交易(4)控制转移类指令(17种助记符)ACALL Absolute subroutine Call 子程序绝对调用'æbsəlju:t, ,æbsə'lju:t adj. 绝对的;完全的;专制的n. 绝对;绝对事物'sʌbru:,ti:n, ,sʌbru:'ti:n] n. [计] 子程序LCALL Long subroutineCall 子程序长调用 RET Return from subroutine 子程序返回RETI Return from Interruption 中断返回SJMP Short Jump 短转移JMP Jump Indirect 间接跳越[,indi'rekt, -dai-] adj. 间接的;迂回的;非直截了当的AJMP Absolute Jump 绝对转移 LJMP Long Jump 长转移CJNE Compare and Jump if Not Equal 比较不相等则转移kəm'pεə] vt. 比较;对照;比喻为vi. 比较;相比n. 比较DJNZ Decrement and Jump if Not Zero 减1后不为0则转移JZ Jump if Zero 结果为0则转移 JNZ Jump if NotZero 结果不为0则转移JC Jump if the Carry flag is set 有进位则转移JNC Jump if Not Carry 无进位则转移JB Jump if the Bit is set) B位为1则转移JNB Jump if the Bit is Not set B位为0则转移JBC Jump if the Bit is set and Clear the bit 位为1则转移,并清除该位NOP No Operation 空操作[,ɔpə'reiʃən] n. 操作;经营;[外科] 手术;[数][计] 运算(5)位操作指令(1种助记符)SETB Set Bit 置位伪指令助记符英文注释功能ORG OriginDB Define ByteDW Define WordEQU EqualDATA DataXDATA External DataBIT BitEND End51外部引脚缩写英文解释中文解释RST (9) Reset 复位信号引脚[,ri:'set, 'ri:set vi. 重置;清零vt. 重置;重新设定;重新组合n. 重新设定;重新组合;重排版RxD Receive Data 串口接收端TxD Transmit Data 串口发送端INT0(————) ()Interrupt0 外部中断0信号输入引脚INT1(————) ()Interrupt1 外部中断1信号输入引脚T0 Timer0 定时/计数器0输入信号引脚T1 Timer1 定时/计数器1输入信号引脚LSB = last significant bit助手,助理,助教adj. 辅助的,助理的;有帮助的OE = output enable 外部的;表面的;外在的n. 外部;表面;外型;外貌MSB = most significant bit连续的;连载的;分期偿还的n.电视连续剧;[图情] 期刊;连载小说ET0 ()enable timer 0 T0中断允许位ET1()enable timer 1 T1中断允许位EX1 ()enable exterior 1 外部中断1中断允许位EX0 ()enable exterior 0 外部中断0中断允许位IP (B8H)interrupt priority 中断优先级寄存器PS priority serial 串口优先级标志位PT1 priority timer 1 定时器1优先级标志位PX1 priority exterior 1 外部中断1优先级标志位PT0 priority timer 0 定时器0优先级标志位PX0 priority exterior 0 外部中断0优先级标志位PCON (87H) power control 电源控制和波特率选择TMOD (89H)timer mode 定时器方式控制寄存器。

51单片机缩写的英文全称及中文名称

单片机缩写的英文全称及中文名称PC = programmer counter 地位;状态;情形;重要身分SP = stack point 堆;堆叠 vt. 使堆叠;把…堆积起来 vi. 堆积,堆叠DPTR = data point register 助手,助理,助教adj. 辅助的,助理的;有帮助的OV = overflow 标记;衰退;枯萎vt. 标记;插旗n. 标志;旗子IE1 = interrupt exterior 连续的;连载的;分期偿还的n. 电视连续剧;[图情] 期刊;连载小说serial communication [计]串行通信serial port [计]串行端口;序列埠serial interface [计]串联接口ET = enable timer 外部的;表面的;外在的n. 外部;表面;外型;外貌PX = priority exterior [计] 缓冲区;缓冲器,[车辆] 减震器vt. 缓冲TMOD:timer mode 平价;同等;相等IE:EA:Enable All Interrupt /CPU开/关中断控制位 ET1:Enable Timer 外部的;表面的;[药] 外用的;外国的;外面的n. 外部;外观;外面SCON:RI:Receive Interrupt 传输;传播;发射;传达;遗传vi. 传输;发射信号TCON:TF1:Timer1 Overflow Flag 交换;交流;交易所;兑换vt. 交换;交易;兑换vi. 交换;交易;兑换TXD:Transmit eXchange Data (11,商店;储备,贮藏;仓库vt. 贮藏,储存ALE:Address Latch Enable (30) 重大的;有效的;有意义的;值得注意的;意味深长的n. 象征;有意义的事物LSB = last significant bit参考,参照;HSO:High Speed Output,高速输出 HSI:High Speed Input:高速输入INST:Instruction,指令 READY就绪,总线中的就绪信号或引脚NMI:No Mask Interruput (Input):不可屏蔽的中断请求(输入)[mɑ:sk, mæskBHE:Bank High Enable:存储器的高位允许,如在80286系统中RAM的组织为16位的,分为高8位和低8位数据,分别的控制信号为BHE和BLE Bank n. 银行;岸;浅滩;储库vt. 将…存入银行;倾斜转弯vi. 堆积;倾斜转弯MCS-51指令(1)数据传送类指令(7种助记符)助记符英文注释功能MOV Move 对内部数据寄存器RAM和特殊功能寄存器SFR的数据进行传送MOVC Move Code 读取程序存储器数据表格的数据传送MOVX Move External RAM 对外部RAM的数据传送XCH Exchange 字节交换XCHD Exchange low-order Digit ['didʒit]低半字节交换POP Pop from Stack) 出栈 PUSH Push onto ['ɔntu, -tə] Stack) 入栈(2)算术运算类指令(8种助记符)ADD Addition 加法 ADDC Add withCarry 带进位加法SUBB Subtract [səb'trækt]with Borrow 带借位减法vt. 减去;扣DA Decimal ['desiməl]adj. 小数的;十进位的n. 小数Adjust [ə'dʒʌst]调整十进制调整INC Increment ['inkrimənt加1DEC Decrement 'dekrimənt]减1MUL Multiplication、Multiply 乘法[,mʌltipli'keiʃən n. [数] 乘法;增加['mʌltiplai vt. 乘;使增加;使繁殖;使相乘vi. 乘;繁殖;增加adv. 多样地;复合地adj. 多层的;多样的DIV Division[di'viʒən n. [数] 除法;部门;分割;师(军队);赛区、Divide 除法di'vaid vt. 划分;除;分开;使产生分歧vi. 分开;意见分歧n. [地理] 分水岭,分水线(3)逻辑运算类指令(10种助记符)ANL And Logic 逻辑与'lɔdʒik]n. 逻辑;逻辑学;逻辑性adj. 逻辑的ORL OR Logic 逻辑或CLR Clear kliə]清零XRL Exclusive-OR Logic 逻辑异或[ik'sklu:siv] adj. 独有的;排外的;专一的n. 独家新闻;独家经营的项目;排外者CPL Complement 取反'kɔmplimənt] n. 补语;余角;补足物vt. 补足,补助RL Rotate left 循环左移[rəu'teit, 'rəut-, 'rəuteit vi. 旋转;循环vt. 使旋转;使转动;使轮流adj. [植] 辐状的RLC Rotate Left throught the Carry flag 带进位循环左移RR Rotate Right 循环右移RRC Rotate Right throught the Carry flag 带进位循环右移SWAP Swap 低4位与高4位交换[swɔp, swɔ:p n. 交换;交换之物vt. 与...交换;以...作交换vi. 交换;交易(4)控制转移类指令(17种助记符)ACALL Absolute subroutine Call 子程序绝对调用'æbsəlju:t, ,æbsə'lju:t adj. 绝对的;完全的;专制的n. 绝对;绝对事物'sʌbru:,ti:n, ,sʌbru:'ti:n] n. [计] 子程序LCALL Long subroutineCall 子程序长调用 RET Return from subroutine 子程序返回RETI Return from Interruption 中断返回SJMP Short Jump 短转移JMP Jump Indirect 间接跳越[,indi'rekt, -dai-]adj. 间接的;迂回的;非直截了当的AJMP Absolute Jump 绝对转移 LJMP Long Jump 长转移CJNE Compare and Jump if Not Equal 比较不相等则转移kəm'pεə] vt. 比较;对照;比喻为vi. 比较;相比n. 比较DJNZ Decrement and Jump if Not Zero 减1后不为0则转移JZ Jump if Zero 结果为0则转移 JNZ Jump if Not Zero 结果不为0则转移JC Jump if the Carry flag is set 有进位则转移JNC Jump if Not Carry 无进位则转移JB Jump if the Bit is set) B位为1则转移JNB Jump if the Bit is Not set B位为0则转移JBC Jump if the Bit is set and Clear the bit 位为1则转移,并清除该位NOP No Operation 空操作[,ɔpə'reiʃən] n. 操作;经营;[外科] 手术;[数][计] 运算(5)位操作指令(1种助记符)SETB Set Bit 置位伪指令助记符英文注释功能ORG OriginDB Define ByteDW Define WordEQU EqualDATA DataXDATA External DataBIT BitEND End51外部引脚缩写英文解释中文解释RST (9) Reset 复位信号引脚[,ri:'set, 'ri:set vi. 重置;清零vt. 重置;重新设定;重新组合n. 重新设定;重新组合;重排版RxD Receive Data 串口接收端TxD Transmit Data 串口发送端INT0(————) ()Interrupt0 外部中断0信号输入引脚INT1(————) ()Interrupt1 外部中断1信号输入引脚T0 Timer0 定时/计数器0输入信号引脚T1 Timer1 定时/计数器1输入信号引脚LSB = last significant bit助手,助理,助教adj. 辅助的,助理的;有帮助的OE = output enable 外部的;表面的;外在的n. 外部;表面;外型;外貌MSB = most significant bit连续的;连载的;分期偿还的n.电视连续剧;[图情] 期刊;连载小说ET0 ()enable timer 0 T0中断允许位ET1()enable timer 1 T1中断允许位EX1 ()enable exterior 1 外部中断1中断允许位EX0 ()enable exterior 0 外部中断0中断允许位IP (B8H)interrupt priority 中断优先级寄存器PS priority serial 串口优先级标志位PT1 priority timer 1 定时器1优先级标志位PX1 priority exterior 1 外部中断1优先级标志位PT0 priority timer 0 定时器0优先级标志位PX0 priority exterior 0 外部中断0优先级标志位PCON (87H) power control 电源控制和波特率选择TMOD (89H)timer mode 定时器方式控制寄存器。

51单片机英文及其翻译