约束满足问题求解途径之比较与分析

约束法的原理及应用

约束法的原理及应用1. 原理介绍约束法(Constrain Method)是一种基于约束的问题求解方法,它通过定义问题的约束条件并将其转化为一个优化问题,从而寻求最优解。

该方法适用于各种类型的问题,包括线性规划、非线性规划、约束满足问题等。

其核心思想是通过逐步缩小可行解的搜索空间,直到找到满足所有约束条件的最优解。

约束法的原理可以归结为以下几个步骤:1.1 定义问题约束条件首先,需要明确问题的约束条件,这些条件可以是线性等式或不等式、逻辑条件等。

约束条件可以是单个的,也可以是多个同时存在的。

1.2 将问题转化为优化问题基于问题的约束条件,需要将原问题转化为一个数学优化问题。

优化问题的目标是找到满足所有约束条件的最优解,可以是最小化或最大化某个目标函数。

1.3 确定搜索空间在约束法中,需要确定问题的搜索空间,即可行解的可能范围。

搜索空间的确定可以基于约束条件进行,剔除不满足条件的解。

1.4 寻求最优解通过逐步缩小搜索空间,约束法可以找到满足所有约束条件的最优解。

这一过程可以采用不同的优化算法,如线性规划算法、遗传算法等。

2. 应用领域约束法在各个领域都有广泛的应用。

以下列举几个常见的应用领域:2.1 生产调度约束法在生产调度领域有着重要的应用。

通过定义生产过程中的约束条件,并将其转化为一个优化问题,可以实现生产过程的优化。

例如,在某工厂中,约束法可以用来确定最优的生产时间表,以尽量减少生产成本和提高生产效率。

2.2 物流规划在物流规划领域,约束法被广泛应用于路径规划、运输规划等问题。

通过定义物流网络中的约束条件,并将其转化为一个优化问题,可以实现最优的物流规划。

例如,在某快递公司中,约束法可以用来确定最佳的送货路径,以最小化运输成本和缩短送达时间。

2.3 金融风险管理约束法在金融风险管理领域也有重要的应用。

通过定义风险管理的约束条件,并将其转化为一个优化问题,可以帮助金融机构降低风险并提高效益。

例如,在投资组合优化中,约束法可以用来确定最佳的资产配置,以实现风险最小化和收益最大化。

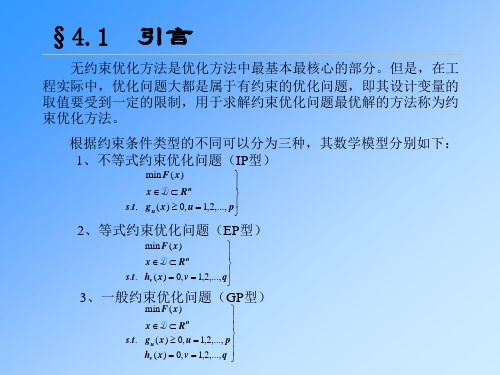

约束问题的最优化方法

§4.2 内点惩罚函数法(障碍函数法)

一. 基本思想: 内点法将新目标函数 Φ( x , r ) 构筑在可行域 D 内,随着惩罚 因子 r(k) 的不断递减,生成一系列新目标函数 Φ(xk ,r(k)),在可 行域内逐步迭代,产生的极值点 xk*(r(k)) 序列从可行域内部趋向 原目标函数的约束最优点 x* 。 内点法只能用来求解具有不等式约束的优化问题。

x ∈ D ⊂ Rn s.t. g u ( x ) ≥ 0, u = 1,2,..., p hv ( x ) = 0, v = 1,2,..., q min F ( x )

一. 约束优化问题解法分类: 约束优化方法按求解原理的不同可以分为直接法和间接法两类。

直接解法:随机方向搜索法、复合形法、可行方向法

φ[ x * (r k ), r k ] − φ[ x * (r k −1 ), r k −1 ] ≤ ε1 * k −1 k −1 φ[ x (r ), r ]

x * (r k ) − x * (r k −1 ) ≤ ε 2

五.

方法评价:

用于目标函数比较复杂,或在可行域外无定义的场合下: 由于优化过程是在可行域内逐步改进设计方案,故在解决工程 问题时,只要满足工程要求,即使未达最优解,接近的过程解也 是可行的; 初始点和序列极值点均需严格满足所有约束条件; 不能解决等式约束问题。

新目标函数: Φ ( x, r1 , r2 ) =

(k ) M

(k ) p

G[ g u ( x)] + r2 ∑ H [hv ( x)] f ( x) + r1 ∑ u =1 v =1

m

p

H [hv ( x)] 其中r ∑ G[g u ( x)] 和 r ∑ 称为加权转化项,并根据它们在惩 v =1 u =1 罚函数中的作用,分别称为障碍项和惩罚项。

约束满足问题及其求解方法研究

约束满足问题及其求解方法研究随着现代科技的快速发展,人们对各种求解问题的需求日益增长,其中,约束满足问题是一个相对独特却又十分重要的问题类型。

在此,我们将从定义、特点、应用以及求解方法几个方面谈一谈约束满足问题及其求解方法的相关内容。

一、定义约束满足问题(Constraint Satisfaction Problem,CSP)是指在一定约束条件下,满足对变量的限制(约束条件)的数学问题。

因此,CSP可以被定义为一个元组(X,D,C):X 表示所有的变量集合,D 表示每个变量 x ∈ X 的定义域,C 表示x∈X 的约束集合。

二、特点CSP问题通常具有以下几个特点:1、通用性强:CSP问题可以用于描述各种类型的问题,如图着色和行程问题等。

2、规模大:CSP问题通常涉及到大量的变量和约束,其求解过程相对复杂,因此,系统的设计和求解方法是至关重要的。

3、复杂度高:大多数CSP问题属于NP完全问题,无法在多项式时间内精确地解决,同时,这些问题的求解方法也比较困难。

三、应用CSP的应用非常广泛,以下是其中几个代表性的应用领域。

1、人工智能:CSP可以用于优化问题、机器学习、计算机视觉等人工智能任务。

2、排程问题:CSP可以用于作业坊调度、员工排班等任务中。

3、生产问题:CSP可以用于零件生产、工厂排布等任务中。

4、电子设计自动化:CSP可以用于电路自动布局、芯片设计等任务中。

四、求解方法针对CSP问题的复杂性,目前有多种求解方法,这里简要介绍几种主流的方法。

1、基于启发式算法的方法:启发式算法通常针对CSP问题中的子问题进行求解,能够得到比较好的求解结果,但是求解时间可能较长。

2、基于局部搜索的方法:局部搜索算法的优点在于其求解速度较快,但其无法得到全局最优解,可能只能得到局部最优解。

3、基于约束传播的方法:约束传播算法利用限制传播的策略进行求解,能够得到可行解或确定无解,但是在求解大规模问题方面表现相对不足。

5.约束满足问题

– 从Xi向前是无解的 / 从Xi回到某个以前的变量 赋值

– 例如:赋值顺序是WA-NSW-NT-Q-SA(发生错

误)

28

– 每个变量都有一个非空可能值域Di – 每个约束指定了包含若干变量的一

个子集内各变量的赋值范围

• CSP的一个状态—对一些或全部变量的赋值 {Xi=vi, Xj=vj, …}

3

CSP问题的解

• 一个不违反任何约束的对变量的赋值称 为相容赋值或合法赋值

• 对每个变量都进行赋值称为完全赋值 • 一个(一组)既是相容赋值又是完全赋值的

– 考虑U有进位:R={0,2,4,6,8} O={5,……} R=0/O=5(有进位)/T=7/W=6/U=3 解={1530 | 765}

8

例2:密码算术问题(2)

• 四列算式约束

– O+O=R+10*X1

– X1+W+W=U+10*X2

– X2+T+T=O+10*X3

– X3=F

• 对应的约束超图如右

– 当到达Y时,可知回溯到哪个变量

26

后向跳转

• 回溯检验导致失败的变量的赋值—后向 跳转:回溯到冲突集中时间最近(最后赋 值)的变量

• 每个被后向跳转剪枝的分支在前向检验 算法中也被剪枝—简单的后向跳转在前 向检验(弧相容性检验)搜索中是多余的

• 因为都是做取值相容的检测,只要在弧 相容检验时增加一个变量集合记录即可

–当前变量的赋值会对其他未赋值变量产生什 么约束?怎样利用这种约束以提高效率?

–当遇到某个失败的变量赋值时,怎样避免同 样的失败?就是说找到对这种失败起到关键 作用的某个变量赋值

18

PSO求解约束优化问题剖析

2018/10/14

CO-PSO

2

约束优化问题描述

2018/10/14

CO-PSO

3

约束优化问题的求解难点

(1) 优化曲面的复杂性。复杂的优化曲面对约束 优化带来的求解难点类似于无约束优化问题, (2) 不可行域的存在性。约束的存在,导致决策

变量的搜索空间产生了不可行域。

(3) 满足约束与优化目标的不平衡。

2018/10/14 CO-PSO 28

sum_ viol按如下公式计算

2018/10/14

CO-PSO

29

2. Swarm 2的评价函数

Swarm 2的每一个微粒B,均代表一组罚因子,即 w1和w2。当Swarm1 ,j进化G1代后,Swarm 2 的第j个微粒B,采用如下方法进行评价。 (1)若Swarm 1 , j中至少有一个可行解,则称B, 为一个有效(valid)微粒,并按下式评价B,

2018/10/14

CO-PSO

4

求解约束极值问题的传统方法

可行方向法(Feasible Direction)、 梯度投影法(Gradient Projection Method)、 约束集法(Active Set Method)、 罚函数法(Penalty Function Method)等等。

通过采用非支配解的概念来比较解,可使搜索向Pareto前沿方向前进,其中非支配解集中第一个目标函数 值最小且其余目标值均等于0的解就是原约束优化问题 的最优解。

2018/10/14 CO-PSO 19

2.基于支配的选择技术

一种基于支配的约束处理规则: (1)可行解总优于不可行解;

(2)若两个解均可行,则目标值好的解为优;

CO-PSO 34

满足约束条件的优化问题

满足约束条件的优化问题优化问题是指在一定的约束条件下,寻找最优解的过程。

满足约束条件的优化问题是指除了要求最优解外,还需要满足额外的约束条件。

下面我们来看一些常见的满足约束条件的优化问题。

1. 线性规划线性规划是一种常见的优化问题,它的约束条件和目标函数都是线性关系。

线性规划常常被用来解决资源分配和生产优化等问题。

例如,一个公司需要在不同的工厂生产不同的产品,而每个工厂的产能和资源有限,需要通过线性规划来确定最优的生产方案。

2. 整数规划整数规划是一种特殊的线性规划问题,其中所有变量必须是整数。

整数规划通常被用来解决分配问题、调度问题和路线规划等问题。

例如,在运输物品时,一些物品只能装载整数个,需要通过整数规划算法来确定最优的装载方案。

3. 二次规划二次规划是一种约束条件下目标函数为二次函数的优化问题。

二次规划通常被用来解决加工优化和精度控制等问题。

例如,在加工零件时,需要通过二次规划来确定加工参数,以达到最优的加工效果和精度要求。

4. 非线性规划非线性规划是一种约束条件下目标函数为非线性函数的优化问题。

非线性规划通常被用来解决生产调度、经济模型和工业设计等问题。

例如,制造企业需要通过非线性规划来确定最优的生产调度方案,以便在产品需求高峰期满足市场需求。

总之,满足约束条件的优化问题广泛应用于各个领域,它们可以通过各种算法和技术来求解,例如线性规划算法、整数规划算法、二次规划算法和非线性规划算法等。

在解决实际问题时,需要结合具体的情况和需求,选择最合适的优化算法和技术,来求解满足约束条件的最优解。

数学建模优化模型中的约束条件分析与设计

数学建模优化模型中的约束条件分析与设计数学建模是一种将现实问题转化为数学问题,并通过数学方法解决问题的方法。

在数学建模中,优化模型是常见的一种模型类型,它通过改变某些变量,使得目标函数达到最优值。

然而,在进行优化模型设计的过程中,约束条件起到了至关重要的作用。

约束条件是指在优化模型中必须满足的条件,它们可以是物理限制、逻辑限制、经济限制等等。

约束条件的分析与设计是确保优化模型能够真实反映实际问题,并得到可行解的关键步骤。

下面将介绍数学建模中约束条件分析与设计的几个重要方面。

一、问题理解与约束条件梳理在进行优化模型设计之前,首先需要充分理解问题的背景与需求,并明确目标函数和决策变量。

然后,根据问题的特点,梳理整理约束条件。

约束条件的梳理可以从以下几个方面出发:1. 数据与实际限制:根据实际情况,确定决策变量的取值范围,如数量的非负性、时间的合理性等。

2. 物理限制:考虑物理因素对问题的影响,如能量守恒、质量平衡等。

3. 逻辑限制:根据问题的逻辑关系,确定决策变量之间的关系,如约束条件的逻辑限制。

4. 经济限制:考虑经济因素对问题的影响,如成本、资源利用率等。

二、约束条件建模与数学形式确定约束条件的建模是将实际问题中的限制条件转化为数学形式的过程。

在进行建模时,需要将问题中的约束条件与目标函数进行合理的数学表达。

具体步骤如下:1. 使用变量表示决策变量和目标函数。

变量的选择应该与问题的实际特点相符。

2. 将约束条件用数学的方式进行表示,可以使用不等式、等式等形式,确保约束条件的完整性。

3. 将目标函数用数学的方式进行表示,并与约束条件进行连接,形成一种综合考虑的数学模型。

这里需要考虑目标函数的优化方向(最大化或最小化)。

三、约束条件的灵活性与敏感度分析一旦建立了优化模型的约束条件,接下来需要对约束条件的灵活性和敏感度进行分析。

这是因为在实际问题中,约束条件可能会发生变化,或者存在一些不确定性。

灵活性和敏感度分析是评估优化模型的鲁棒性和稳定性的重要手段。

约束满足问题(CSP)的算法探索

约束满足问题(CSP)的算法探索约束满足问题(Constraint Satisfaction Problem,CSP)是人工智能领域中的一个重要问题类型,涉及到在一组变量上的取值,同时满足一系列约束条件。

CSP在实际生活中有着广泛的应用,比如在排课、时间表安排、资源分配等领域都可以看到CSP的身影。

为了解决CSP问题,人们提出了各种不同的算法,本文将对CSP问题及其相关算法进行探索和介绍。

### 什么是约束满足问题(CSP)?约束满足问题是指一组变量,每个变量有一定的取值范围,同时还有一系列约束条件限制这些变量的取值。

CSP的目标是找到一组取值,使得所有约束条件都得到满足。

通常来说,CSP可以用一个三元组表示:CSP = (X, D, C),其中:- X = {X1, X2, ..., Xn} 表示一组变量;- D = {D1, D2, ..., Dn} 表示每个变量对应的取值范围;- C = {C1, C2, ..., Cm} 表示约束条件的集合。

### CSP的经典问题CSP问题有许多经典的应用场景,下面介绍几个常见的CSP问题:1. **地图着色问题**:给定一张地图和一定数量的颜色,要求每个地区用一种颜色着色,相邻的地区不能使用相同的颜色。

2. **八皇后问题**:在8×8的国际象棋棋盘上放置8个皇后,使得它们互相不能攻击到对方。

3. **数独问题**:填充一个9×9的网格,使得每一行、每一列和每个3×3的子网格中的数字都是1到9且不重复。

### CSP的求解算法为了解决CSP问题,人们提出了多种求解算法,常见的包括回溯算法、约束传播算法和启发式搜索算法等。

下面分别介绍这几种算法: #### 1. 回溯算法回溯算法是解决CSP问题最常用的方法之一。

其基本思想是逐步尝试每个变量的取值,并检查是否满足约束条件,如果不满足则回溯到上一步重新选择取值。

回溯算法的优点是简单易懂,但在处理大规模问题时效率较低。

几何约束满足问题的求解

自由度分析

定义 6.1 二元组 M(E,C) 表示一个几何约束模型,即对于一个有限元素集 E = {e | i = 1,…,n },存在一组约束关系 C = {c | j = 1,…,m }。 几何约束模型通过记录几何元素和几何约束之间的关系,自动捕获设计师的设计意 图,推理出几何元素的求解次序,支持产品的参数化设计。

6.1 引言

几何约束满足问题(Geometric Constraint Satisfaction Problem -- GCSP)可描述为: 给定一组几何元素和一组描述几何元素间关系的约束条件,求解这组几何元素以满足这 组约束[Kra92]。几何约束满足问题的求解是智能 CAD 的核心技术。 我们参考了国内外关于基于构造法的约束求解技术的最新研究成果, 设计实现了一个 二维几何约束求解器,该求解器可作为智能 CAD 系统的核心之一。 同其它构造法一样,求解器对几何约束问题的求解可分为两个阶段: 分析阶段:对几何约束系统进行分析,求得一个几何元素的构造序列; 构造阶段:根据分析阶段所得到的构造序列,采用相应的求解方法依次构造各几 何元素,重构几何模型。 本章首先回顾几何约束满足问题的国内外研究现状。 然后讨论了几何约束系统及其约 束图表示。接着,提出了几何元素的构造规则,讨论了多解问题的解决。提出了求解几 何约束系统的构造法,包括:(1)基于对构造规则的抽象和深化,提出了两个重写规则 和一个基于点簇归约的几何推理算法(以下简称归约算法),实现对几何约束系统的分 析,求取一个几何元素的归约序列;(2)讨论了基于归约序列的几何元素的构造计划生 成方法,实现对几何模型的重构。此外,我们对归约算法的正确性和可解域进行了讨论, 介绍了过约束和欠约束的解决方法。最后给出了基于构造法的二维几何约束求解器的实 现及应用实例。

约束法求解方法

约束法求解方法

约束法求解方法通常是指通过设定一些约束条件,将问题简化为一个优化问题,然后使用各种优化算法进行求解。

这种方法在许多领域都有应用,例如计算机图形学、机器学习、运筹学等。

在约束法求解中,最重要的步骤是设定合适的约束条件。

这些条件可以根据问题的特性来设定,例如,在机器学习中,可以根据已知的训练数据来设定一些约束条件,使得求解的模型能够更好地拟合训练数据。

一旦约束条件设定好,就可以使用各种优化算法进行求解。

常见的优化算法包括梯度下降法、牛顿法、遗传算法等。

这些算法可以在一定的时间内找到最优解或近似最优解。

约束法求解方法的一个重要特点是它可以处理大规模的问题。

由于约束条件的引入,可以将问题分解为多个子问题,从而可以并行处理这些子问题,提高求解效率。

需要注意的是,约束法求解方法也存在一些限制。

例如,有时候设定的约束条件可能会引入新的噪声或偏差,影响最终的求解结果。

此外,对于一些复杂的问题,可能难以找到合适的约束条件或优化算法进行求解。

总之,约束法求解方法是一种有效的解决问题的方法,它可以处理大规模的问题,提高求解效率。

但在使用这种方法时,需要注意设定合适的约束条件和选择合适的优化算法。

约束法的原理和应用

约束法的原理和应用一、约束法的原理介绍约束法(Constrained Optimization)是一种数学方法,用于解决多维变量的优化问题,其中包含一个或多个约束条件。

它是优化问题的一种有效求解方法,可以帮助人们在满足一定约束条件下,找到问题的最优解。

约束法的原理基于约束方程和目标函数之间的关系,以及约束条件对可行解的限制。

具体来说,约束法通过建立一个数学模型,在变量的取值范围内,通过不断调整变量的值,使目标函数达到最优值。

同时,约束法会检查每次调整后的解是否满足约束条件,从而保证解的可行性。

二、约束法的应用领域约束法的应用广泛,涉及到许多领域。

以下是一些常见的应用领域:1.金融领域–资产组合优化:在风险、收益等约束条件下,优化投资组合的权重分配,以提高投资回报率。

–期权定价:考虑到利率、标的资产价格以及约束条件,计算出期权的合理价格。

2.生产运营管理–生产计划优化:最大化生产效率,同时考虑到人力资源、设备利用率等约束条件。

–供应链优化:考虑到成本、库存和交付时间等约束条件,优化供应链的配置和运作。

3.交通规划–路网优化:在考虑到交通流量、道路容量以及交通规则等约束条件下,优化交通网络的设计和布局。

–公交线路规划:在满足乘客需求和交通规则的前提下,优化公交线路的选择和安排。

4.工程设计–结构优化:在材料限制、成本预算和负载等约束条件下,优化工程结构的设计,以确保强度和稳定性。

–设备配置优化:考虑到能源消耗、物料流动和工作效率等约束条件,优化设备配置的布局。

5.人力资源管理–人员调度:在满足员工需求、工作时间和法律法规等约束条件下,优化人员的排班和调度。

–岗位匹配:根据员工技能、能力、经验以及工作需求等约束条件,优化岗位的匹配和分配。

三、约束法的优势和局限性约束法具有以下优势:•可以应用于多维变量的优化问题,具有广泛的适用性。

•能够在满足约束条件的前提下,找到问题的最优解。

•可以灵活调整约束条件,以适应实际需求的变化。

约束满足问题(高校排课问题)

最小剩余值启发式+前向检验的 改进回溯算法

S1 获取课程、教师、班级、教学场地、教学时间及约束信息,建立排课任务并 根据自约束确定各排课任务变量的值域,如存在值域为空,则问题无解; S2 i=1( i为当前待排课任务序号); S3 如果i大于排课任务数量,则得到问题解而终止; S4 采用最小剩余值启发式,按值域空间大小对剩余排课任务进行升序排列,即 优先安排可选资源少的排课任务; S5 逐次考察排课任务变量 X i 值域中的元素,直至利用关系约束的前向检验,检 测到所有剩余排课任务均存在可选资源; S6 如果变量X i 的值域已越界,则i=i-1;否则,对排课任务X i 赋值,并修改相 关剩余排课任务的值域,i=i+1,并转S3; S7 如果i=0,则问题无解而终止;否则,恢复由 X i 引发的对相关排课任务值域 的修改,取消 X i 的赋值并转S4。

优化约束与解的质量

高校排课问题具有多个优化目标,将目标通过约束表征 而得到高质量解的间接求解方法,通常是有效的。 优化约束是针对高校排课问题的优化目标而建立的约束。 它可以是自约束,也可以是关系约束。当排课问题的解满 足连同优化约束在内的全部约束条件时,则可以认为解是 高质量的。

BOOLEAN C3=(|Ti .教学时间.星期-Tj .教学时间.星期| ≥ 间隔天数)

谢谢

高校排课问题

在高校排课问题中,一个排课任务是指为一次教学任务做出的场地 及时间的选择,这种选择必须满足教学任务自身的条件需求,并且不 能与其他排课任务发生冲突。 这里,排课任务是变量,可供选取的资源为问题的值域,而需求与 冲突就是约束。 由上可见,排课问题可以看做一个约束满足问题,问题的求解表现 为对各排课任务寻找满足约束的资源,解的优劣也可以通过约束来表 征。

大规模有约束优化问题的解法

大规模有约束优化问题的解法涉及到复杂的数学和计算方法。

这类问题可能涉及大量的决策变量和多个约束条件,需要采用高效的算法和计算技术。

以下是解决大规模有约束优化问题的一些方法:1. 线性规划(Linear Programming, LP):当目标函数和约束条件均为线性时,可以采用线性规划方法。

常用的算法包括单纯形法、内点法等。

线性规划在很多实际问题中都能够得到高效的解。

2. 整数规划(Integer Programming, IP):如果决策变量需要取整数值,就需要使用整数规划方法。

分支定界法、割平面法等是解决整数规划问题的经典算法。

3. 非线性规划(Nonlinear Programming, NLP):当目标函数或者约束条件为非线性时,需要使用非线性规划方法。

梯度下降法、牛顿法、拟牛顿法等是一些常见的优化算法。

4. 全局优化方法:针对存在多个局部最优解的问题,全局优化方法致力于找到全局最优解。

遗传算法、模拟退火算法、粒子群算法等元启发式算法被广泛用于全局优化。

5. 约束优化算法:专门针对带有约束的问题,如罚函数法、拉格朗日乘子法等。

这些算法在考虑约束条件的同时寻找最优解。

6. 分解与协调算法:将大规模问题分解为小规模子问题,通过协调各子问题的解来得到整体最优解。

分解协调算法在处理大规模问题时能够降低计算复杂性。

7. 凸优化:针对凸优化问题,有一些高效的算法,如内点法、随机梯度法等。

8. 并行计算:利用并行计算的能力,通过分布式计算或GPU加速等手段提高求解效率。

对于大规模问题,通常需要综合考虑问题的特性、求解算法的复杂性和计算资源等多个方面因素,选择合适的方法进行求解。

在实际应用中,常常需要根据具体问题的特点进行定制化的算法设计。

数学优化与约束条件问题的求解

数学优化与约束条件问题的求解数学优化是指在给定的一组约束条件下,寻找使得目标函数达到最优值的一组变量取值。

在实际问题中,许多决策问题都可以被转化为数学优化问题,如生产优化、资源分配、路径规划等。

然而,由于约束条件的存在,优化问题的解并不总是容易获得。

因此,本文将介绍数学优化中的约束条件问题,并探讨其求解方法。

一、约束条件问题的定义与分类在数学优化中,约束条件是对优化变量的取值进行限制的条件。

根据约束条件的性质,可将约束条件问题分为等式约束条件和不等式约束条件两类。

1. 等式约束条件等式约束条件指的是将优化变量的某些参数通过等式进行约束。

例如,若要优化一个长度为L的长方形的面积,则可以设长为x,宽为y,且满足x * y = L。

这个约束条件即为等式约束条件。

2. 不等式约束条件不等式约束条件则是通过不等式来约束优化变量的取值范围。

例如,在生产优化问题中,某种产品的生产成本与产量之间存在关系,若生产量为x,成本为y,则可能存在y >= f(x)的不等式约束条件,其中f(x)为生产成本函数。

二、约束条件问题的求解方法为了解决约束条件问题,数学优化领域提出了一系列求解方法,包括拉格朗日乘子法、KKT条件等。

1. 拉格朗日乘子法拉格朗日乘子法是一种常用的求解约束条件问题的方法。

该方法通过构建拉格朗日函数,并通过求导等条件,将优化问题转化为一个无约束条件的问题。

具体步骤如下:(1)构建拉格朗日函数:设目标函数为f(x),等式约束条件为g(x),不等式约束条件为h(x),则拉格朗日函数L(x, λ)为L(x, λ) =f(x) + λg(x) + μh(x),其中λ和μ为拉格朗日乘子。

(2)通过求导求解:将L(x, λ)对x进行求偏导,并令其等于0,求得优化问题的解。

2. KKT条件KKT条件是指在最优解处,优化变量的取值要同时满足目标函数、等式约束条件和不等式约束条件的一组条件。

具体包括原始可行性条件、对偶可行性条件、互补松弛条件和梯度条件等。

约束多目标 算法

约束多目标算法【原创实用版】目录一、多目标约束算法的概述二、多目标约束算法的实现方法三、多目标约束算法的应用案例四、多目标约束算法的优缺点分析五、总结正文一、多目标约束算法的概述多目标约束算法是一种在多个目标之间进行权衡和优化的算法,主要应用于解决复杂的多目标决策问题。

在实际应用中,多目标决策问题通常涉及多个相互矛盾的目标,如在工程项目中,需要在成本、进度、质量等多方面进行综合考虑。

多目标约束算法就是在这种背景下应运而生的。

二、多目标约束算法的实现方法多目标约束算法的实现方法有很多,其中较为常见的有以下几种:1.线性规划法:线性规划法是一种基于数学模型的优化方法,它通过建立目标函数和约束条件来描述问题,并利用线性规划求解器进行求解。

2.遗传算法:遗传算法是一种基于生物进化理论的优化方法,它通过模拟自然选择和遗传遗传机制来逐步搜索问题的最优解。

3.粒子群算法:粒子群算法是一种基于群体智能理论的优化方法,它通过模拟鸟群觅食过程中的协同搜索行为来寻找问题的最优解。

4.模拟退火算法:模拟退火算法是一种基于统计物理学理论的优化方法,它通过模拟金属冶炼过程中的退火过程来逐步搜索问题的最优解。

三、多目标约束算法的应用案例多目标约束算法在许多领域都有广泛的应用,如在项目管理、生产调度、供应链管理等方面。

以下以项目管理为例,简要说明多目标约束算法在工程项目中的应用。

在工程项目中,通常需要在成本、进度、质量等多个方面进行综合考虑。

利用多目标约束算法,可以建立一个描述工程项目多方面目标的数学模型,并通过求解该模型,找到满足多个目标的最优解。

这样,项目管理者可以根据求解结果,制定出最优的项目计划,从而实现项目目标的最优化。

四、多目标约束算法的优缺点分析多目标约束算法具有以下优点:1.可以处理多个相互矛盾的目标,具有较强的实用性。

2.算法具有较好的通用性,可以应用于多种领域的优化问题。

3.可以得到满足多个目标的最优解,有助于实现决策的科学化和精确化。

约束优化问题的求解方法

约束优化问题的求解方法约束优化问题(Constrained Optimization Problem)是指在一个给定的约束条件下,在所有可行的解中找到最优解的问题。

这类问题在现实中广泛存在,包括物流配送、资源分配、工程设计等领域。

如何有效地求解约束优化问题是科学研究和工程实践中的一个重要问题。

求解约束优化问题的基本方法是利用数学模型和优化算法。

数学模型是对问题的抽象和表达,它将问题中的各种因素、变量、约束、目标函数都用数学符号和方程式来描述。

优化算法则是根据数学模型对解进行求解的方法和技术。

具体来说,一个典型的约束优化问题可以描述为:$$\min f(\mathbf{x})$$$$s.t. \quad g_j(\mathbf{x}) \leq 0, j=1,2,...,m$$$$h_k(\mathbf{x})=0, k=1,2,...,p$$其中,$f(\mathbf{x})$是目标函数,$\mathbf{x} = [x_1, x_2, ..., x_n]$是决策变量向量,$g_j(\mathbf{x})$是不等式约束,$h_k(\mathbf{x})$是等式约束,$m$和$p$分别是不等式约束和等式约束的数量。

对于约束优化问题,大致有以下几种求解方法。

1. 等式约束和不等式约束均为线性约束的约束优化问题可以使用线性规划方法求解。

线性规划是指目标函数和所有约束均为线性函数的优化问题。

线性规划具有较好的求解效率且有高度的理论成熟度。

目前已经有很多线性规划求解器可供使用。

例如OpenSolver、Gurobi等。

2. 不等式约束为凸函数的约束优化问题可以使用凸优化方法求解。

凸优化问题是指其目标函数和不等式约束均为凸函数的优化问题。

凸优化具有全局最优性和求解效率高的特点,其求解方法有许多,例如基于梯度的方法、基于内点的方法等。

凸优化库MATLAB Optimization Toolbox和Python库CVXPY都提供了凸优化的求解工具。

数学建模中的优化问题与约束条件的求解

数学建模中的优化问题与约束条件的求解在数学建模的广阔领域中,优化问题与约束条件的求解是至关重要的组成部分。

优化问题旨在寻找某种最佳的解决方案,而约束条件则限制了可行解的范围。

理解和解决这些问题对于解决实际生活中的各种复杂情况具有深远的意义。

首先,让我们明确什么是优化问题。

简单来说,优化问题就是在给定的一组条件下,寻找能够使某个目标函数达到最大值或最小值的变量取值。

例如,一家工厂在生产多种产品时,需要决定每种产品的产量,以在有限的资源和市场需求的限制下,实现利润最大化。

这里,每种产品的产量就是变量,利润就是目标函数,而资源和市场需求则构成了约束条件。

优化问题的类型多种多样。

常见的有线性规划、非线性规划、整数规划等。

线性规划是指目标函数和约束条件都是线性的问题。

非线性规划则涉及到目标函数或约束条件中至少有一个是非线性的。

整数规划要求变量取整数值。

每种类型的优化问题都有其特定的求解方法和特点。

接下来谈谈约束条件。

约束条件可以分为等式约束和不等式约束。

等式约束表示某些变量之间必须满足精确的相等关系,比如在一个物理系统中,能量守恒定律就可以表示为一个等式约束。

不等式约束则限制了变量的取值范围,比如资源的有限性可能导致生产过程中对某些投入的使用不能超过一定的上限。

在实际问题中,约束条件往往是复杂且多样化的。

它们可能来自于物理规律、经济规律、技术限制、政策法规等多个方面。

例如,在交通运输规划中,道路的容量限制、车辆的速度限制等都是约束条件;在投资决策中,资金预算、风险承受能力等也是约束条件。

求解优化问题与约束条件的方法有很多。

经典的方法如单纯形法,适用于线性规划问题。

对于非线性规划问题,常用的方法有梯度下降法、牛顿法等。

此外,还有一些智能算法,如遗传算法、模拟退火算法等,它们在处理复杂的优化问题时表现出了强大的能力。

单纯形法是一种通过在可行域的顶点上进行搜索来找到最优解的方法。

它的基本思想是从一个可行解开始,通过不断地移动到相邻的顶点,逐步改进目标函数的值,直到找到最优解。