版图课程设计注意事项tanner)

常用EDA工具之Tanner

常用EDA工具之Tanner常用EDA工具之Tanner集成电路版图编辑器L-Edit(Layout-Editor)在国内已具有很高的知名度。

Tanner EDA Tools 也是在L-Edit 的基础上建立起来的。

整个设计工具总体上可以归纳为电路设计级和版图设计级两大部分。

即以S-Edit 为核心的集成电路设计、模拟、验证模块和以L-Edit 为核心的集成电路版图编辑与自动布图布线模块。

电路设计级包括电路图编辑器S-Edit、电路模拟器T-Spice 和高级模型软件、波形编辑器W-Edit、NetTran 网表转换器、门电路模拟器GateSim,以及工艺映射库、符合库SchemLib、Spice 元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit 可以把设计的电路图转换成SPICE,VHDL,EDIF 和TPR 等网表文件输出,提供模拟或自动布图布线。

版图设计级包括集成电路版图编辑器L-Edit 和用于版图检查的网表比较器LVS 等模块。

L-Edit 本身又嵌入设计规则检查DRC、提供用户二次开发用的编辑界面UPI、标准版图单元库及自动布图布线SPR、器件剖面观察器Cross Section Viewer)版图的SPICE 网表和版图参数提取器Extract(LPE)等。

网表比较器LVS 则用于把由L-Edit 生成的版图反向提取的SPC 网表和由S- Edit 设计的逻辑电路图输出的SPC 网表进行比较实现版图检查、对照分析。

L-Edit 除了拥有自已的中间图形数据格式(TDB 格式)外,还提供了两种最常用的集成电路版图数据传递格式(CIF 格式和GDSII 格式)的输入、输出功能,可以非常方便地在不同的集成电路设计软件之间交换图形数据文件或把图形数据文件传递给光掩模制造系统。

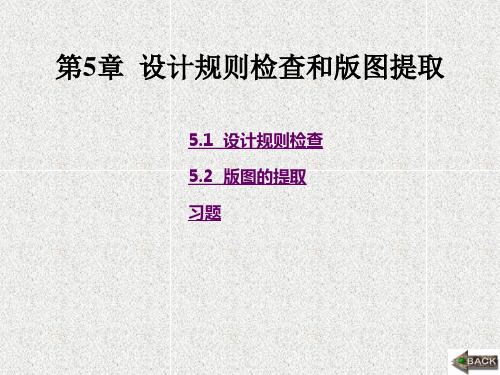

《集成电路版图设计与TannerEDA工具的使用》课件第5章

图5.3 错误导航窗口

图5.4 标记DRC错误

在错误导航界面中有一些图标对查看和修改DRC错误 很有帮助。点击图标“ ”可以使错误标记在显示和隐藏 之间切换。对版图进行修改后,如果想要去掉错误标记,点 击错误导航界面中的图标“ ”。点击图标“ ”可以 在版图中标记下一个DRC错误,点击图标“ ”可以在 版图中标记上一个DRC错误。点击图标“ ”可以对错 误导航界面进行设置,对于一般的DRC检查,默认的设置 是比较符合需要的,不需要另外再作修改。点击图标“ ” 会出现一个下拉菜单,此菜单中比较经常用的选项是 “Export DRC Result”,即导出DRC结果。

要对整个单元的版图进行设计规则检查,选择命令 Tools→DRC。如果只对单元的一部分进行设计规则检查, 选择命令Tools→DRC Box,然后在要检查的版图上按住鼠 标左键画一个矩形框来确定检查的范围。

在运行DRC的过程中,在版图界面会出现一个与图5.1 类似的对话框,这个对话框中列出了被检查单元的名字、使 用的设计规则文件的名字、当前正在检查的设计规则的名字、 使用的时间、估计要做完全部检查所剩余的时间及已经完成 的设计规则检查的数量。对每个检查出来的错误,对话框中 会列出规则名和错误的数量。这个对话框中的内容同样会被 保存在DRC结果报告中。可以通过DRC错误导航来查看 DRC结果报告,所使用的命令是Actions→Open DRC Summary Report。

(4) Write terminal names for subcircuits:在注释语句中 给出子电路的端点名和网表中子电路的状态。例如:

X1 1 2 4 ICResPoly L=3.4u W=250n * X1 PLUS MINUS BULK

(5) Write shorted devices:如果在提取定义文件中 “IGNORE_SHORTS”被设置,则在网表的注释语句中写出 短路的器件,否则短路的器件将被忽略;如果在提取定义文 件中“IGNORE_SHORTS”没有被设置,则在网表中短路的 器件将作为正常器件被写进。

tanner设计规则

a

Well Edge -5λ

最小覆盖

2.3 Source/Drain Active to 阱外器件有源区距阱

b

Well Space -5λ

最小间距

1

1

1 P+

2

3a

3b N+

1

设计规则——active

2.4a WellContact(Active) to 阱对其中阱接触(有源

Well Edge -3λ

接触孔最小围绕

5.3A

PolyContact to

接触孔间距

PolyContact Spacing -2λ

1A

2A 3A

设计规则——Active

contact

定义为金属1与有 源区的所有连接

符号

名称

含义

6.1A Active Contact Exact Size -2λ 有源区接触孔确切宽度

6.2A FieldActive Overlap of ActCnt - 有源区与有源区接触孔

8.5a/ 8.5c 8.5b/ 8.5d

Via to PolyContact/ 通孔与多晶硅 / 有源区 ActiveContact spacing 接触孔的最小间距

-2λ

Via to Poly/Active Spacing -2λ

Poly与有源区对通孔 的最小间距

Via(On Poly/Active) to Poly与有源区对通孔 Poly/Active Edge -2λ 的最小围绕

5a

5b

4a

5c

5d

4b

可用于电源线、地线、总线、

设计规则——metal2 时钟线及各种低阻连接

版图-tanner

摘要供电电路是提电路工作的电能,无论是生活还是电路板都必须要有供电电路,电路才能正常工作。

具体什么时候要什么电源,必须有控制电路来控制。

Tanner Pro集成电路设计软件是由Tanner Research 公司开发的基于Windows平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

L-Edit是Tanner EDA软件公司所出品的一个IC 设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-Edit包含IC设计编辑器、自动布线系统、线上设计规则检查器(DRC)、组件特性提取器、设计布局与电路netlist的比较器,这些模块组成了一个完整的IC设计与验证解决方案。

关键词供电,控制,电路,版图设计目录摘要 (I)1 设计内容及目的 (2)1.1设计内容 (2)1.2设计目的 (2)2 三输入两级供电控制电路图设计 (3)2.1电路模型图 (3)2.2电路真值表 (3)2.3电路原理图 (4)2.4电路仿真 (5)3 三输入两级供电控制电路版图实现 (8)3.1版图设计 (8)3.2DRC验证 (8)3.3功能仿真 (9)3.4LVS检测 (14)总结 (18)参考文献 (19)1.设计内容及目的1.1 设计内容三输入两级供电控制电路设计完成三输入两级供电控制电路设计的整个设计流程,包括电路图和版图设计。

1.2设计目的1). 培养学生严谨认真的工作态度2). 培养学生独立分析和解决实际问题的能力3). 进一步熟悉Tanner Pro工具的使用4). 进一步熟悉集成电路设计方法5). 学会撰写课程设计总结报告2 三输入两级供电控制电路图设计2.1电路模型图A、B、C分别为三个不同电源电流流入控制电路,三个电路并联,一起组成第一级控制,D为控制电源输入控制电路,为第二级控制。

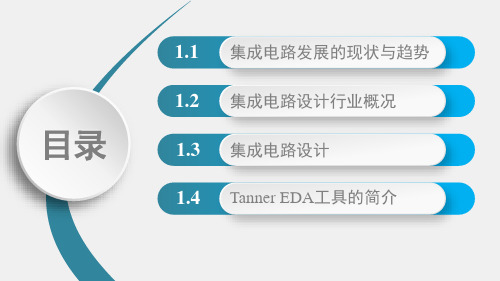

《基于Tanner的集成电路版图设计技术》课件第一章 集成电路设计前沿技术

1.2集成电路设计行业概况

1.2.3 我国集成电路设计行业发展情况

我国集成电路设计行业的起步较晚,但是发展速度很快,过去10年 的年复合增长率达到了29%。2004~2014年中国集成电路设计企业销售额 及增速,如图1.2所示。

1.2集成电路设计行业概况

1.2.1 集成电路设计行业概况

集成电路设计行业是集成电路行业的子行业,集成电路行业包括集 成电路设计业、集成电路制造业、集成电路封装业、集成电路测试业、 集成电路加工设备制造业、集成电路材料业等子行业。集成电路设计行 业处于产业链的上游,主要根据终端市场的需求设计开发各类芯片产品, 兼具技术密集型和资金密集型等特征,对企业的研发水平、技术积累、 研发投入、资金实力及产业链整合运作能力等均有较高的要求。

1.2集成电路设计行业概况

1.2.3 我国集成电路设计行业发展情况

2015年排名 1 2 3 4 5 6 7 8 9 10

厂商 Qualcomm OSR Avago/Broadcom

MTK Nvidia AMD Hisilicon(海思) Apple/TSMC Marvell Xilinx Spreadtrum(紫光展讯) 合计

1.2集成电路设计行业概况

1.2.2 集成电路设计行业的市场分类

集成电路按照应用领域大致分为标准通用集成电路和专用集成电路。 其中标准集成电路是指应用领域比较广泛、标准型的通用电路,如存储 器(DRAM)、微处理器(MPU)及微控制器(MCU)等;专用集成电 路是指某一领域会某一专门用途而设计的电路,系统集成电路(SoC) 属于专用集成电路。

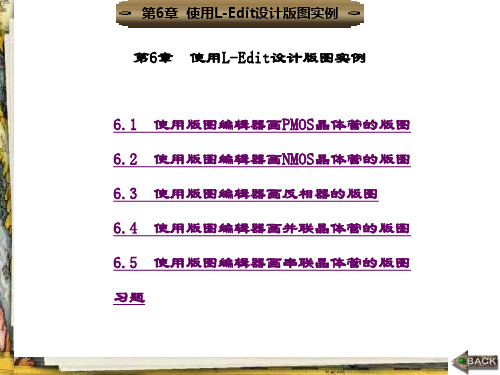

精品文档-集成电路版图设计与TannerEDA工具的使用(王颖)-第6章

第6章 使用L-Edit设计版图实例

6.1 使用版图编辑器画PMOS晶体管的版图 6.2 使用版图编辑器画NMOS晶体管的版图 6.3 使用版图编辑器画反相器的版图 6.4 使用版图编辑器画并联晶体管的版图 6.5 使用版图编辑器画串联晶体管的版图 习题

第6章 使用L-Edit设计版图实例

后点击鼠标左键,然后点击Generate Cross-Section对话框

中的确认键(OK),最后得到的版图与横截面窗口如图6.13所

示。

第6章 使用L-Edit设计版图实例

图6.12 产生横截面观察对话框

பைடு நூலகம்

第6章 使用L-Edit设计版图实例

图6.13 版图与横截面图

第6章 使用L-Edit设计版图实例

第6章 使用L-Edit设计版图实例

图6.6 绘制P Select层

第6章 使用L-Edit设计版图实例

③ 画Active层。在DRC文件中规定有源区的最小宽度 (Active Minimum Width)为0.35微米,PMOS晶体管的有源区 到N阱之间的最小距离(PMOS Source/Drain spacing to Well Edge)为0.75微米。在选择了有源区绘图层和方框绘图工具后, 在版图区域中画一个高0.55微米、宽1.55微米的有源区,即 PMOS晶体管的沟道宽度为0.55微米,如图6.7所示。

第6章 使用L-Edit设计版图实例

第6章 使用L-Edit设计版图实例

图6.11 DRC相关窗口

第6章 使用L-Edit设计版图实例

(7) 进行晶体管的横截面观察。Tanner的版图编辑器配

有版图横截面观察功能,利用此功能可以观察所画版图与实际

《集成电路版图设计与TannerEDA工具的使用》课件第2章

图2.9 反相器的尺寸标注方法

反相器的驱动能力与其尺寸有着密切的关系,尺寸越大 其等效电阻越小,驱动能力也就越大。

2.3.2 CMOS与非门

当所有给定条件中至少有一个条件不满足时,结果才能 出现,这种逻辑关系就是“与非”逻辑关系,实现“与非” 逻辑关系的门电路就叫做与非门(NAND Gate)。本节将介绍 两输入的与非门,其他更多输入的与非门可以通过MOS管 的扩展来实现。

在反相器电路图中,同样需要标注尺寸,其标注方法如 图2.9所示。在图2.9(a)中,P代表PMOS晶体管的尺寸,N代 表NMOS管的尺寸。标注的尺寸同样是晶体管的宽度在前, 长度在后或可以省略。图2.9(b)给出了另外一种标注方法, 即PMOS晶体管的宽度在前,NMOS晶体管的宽度在后,晶 体管的长度省略。

NMOS晶体管由埋在P型衬底中的N型漏区和源区构成。 源、漏之间的电流是由通过源极和漏极之间的N型导电沟道 中的电子形成的。图2.2给出了NMOS晶体管的结构图和电 路符号图。

图2.2 NMOS晶体管的结构图和电路符号图

NMOS晶体管和PMOS晶体管的衬底总是连接到固定电 平上。对于NMOS晶体管来说,衬底总是接逻辑“0”电平。 当NMOS晶体管的栅极接逻辑“1”电平的时候,晶体管导通。

图2.4(b)给出了PMOS晶体管的开关模型,当PMOS晶体 管的栅极加上逻辑“0”电平的时候,开关“闭合”或者“导 通”,漏极和源极被连接起来,漏极的电平可以传递到源极。 与NMOS晶体管类似,PMOS开关在传递“1”电平的时候性 能比传递“0”电平的时候要好。正因为NMOS晶体管和 PMOS晶体管在源极和漏极之间分别传递“0”和“1”的时候 有很好的开关性能,所以通常用NMOS晶体管传递逻辑“0” 电平,而用PMOS晶体管传递逻辑“1”电平。逻辑“0”电平 通常由芯片的地电平来表示;反之,逻辑“1”电平由电源电 压表示。

tanner课设

《集成电路计算机辅助设计》课程设计报告题目LED驱动芯片中的逻辑驱动电路设计及版图实现目录第一部分题目要求 (1)1.1课程设计项目 (1)1.2基本目标 (1)1.3设计要求 (1)第二部分电路设计 (2)2.1电路图设计 (2)2.1.1反相器 (2)2.1.2传输门 (2)2.1.3与非门 (3)2.1.4驱动电路D触发器 (4)2.2电路工作原理 (5)2.2.1原理图 (5)2.2.2工作原理 (5)2.3原理图输入步骤 (6)2.4MOS管尺寸汇总表 (6)第三部分电路仿真 (7)3.1仿真步骤 (7)3.2仿真结果 (2)第四部分版图实现 (9)4.1版图设计步骤 (9)4.1.1反相器版图设计 (9)4.1.2传输门版图设计 (12)4.1.3与非门版图设计 (12)4.1.4总电路图版图设计 (12)4.2版图设计结果 (13)第五部分结论 (16)第六部分心得体会 (17)参考文献 (18)第一部分题目要求1.1课程设计项目:LED驱动芯片中的逻辑驱动电路计及版图实现1.2基本目标:设计一个LED驱动芯片中的单元电路:逻辑驱动电路。

完成电路原理图的设计,仿真,以及版图设计。

要求尽可能满足下列要求。

Note:The Schematic input can use VIEWLOGIC or S-EDIT.The simulator can use Hspice or T-spice, The layout fulfilled with L-EDIT.Simulation and calculation were done with SMIC0.35um COMS model.1.3设计要求:(1)给出满足题目要求的电路图。

(2)给出MOS管的尺寸。

(3)利用Hspice或T-spice对电路进行仿真,仿真内容包括:舜态特性、温度特性、不同工艺角条件下的瞬态特性、功耗等。

(4)利用L-EDIT完成电路的版图设计,设计规则使用L-EDIT默认规则,要求电路布局合理、面积尽量做小。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

版图注意事项

①P管与N管分层放置,P管放入N阱中。

N阱中应尽量多的设置阱连接区,N管层应尽量多的设置衬底接触点。

②每一层晶体管要加保护环,保护环是为了减少栓锁效应,保护环分为硬环和软环。

P管用N型保护环,N管用P型保护环。

保护环由select、active、active contact、metal层组成。

N型保护环的select层用nselect,P型保护环的select层用pselect。

图1. P型保护环

③晶体管的放置要保证晶体管内部电流方向一致

图2 晶体管放置示意图

④重要晶体管(如差分输入对、电流镜)应增加虚拟管,高度匹配时在管子的四周都加虚拟器件。

图3为非高度匹配时虚拟管的运用。

图3 加入了虚拟器件的版图

⑤特殊晶体管的优化处理(见余华老师课件)

a)宽度很宽的晶体管b)长度很长的晶体管

c)宽度很窄的晶体管d)晶体管的合并

⑥注意晶体管的共质心布局。

如:叉指状MOS晶体管:ABBA

图4 叉指状MOS晶体管

⑦pad画法:Metal1:102×102;Metal2;100×100;Overglass:88×88;Via:90×90;Pad Comment:100×100。

图5 pad版图

⑧“poly-poly”结构电容画法:电容中要用到Poly、Poly2、Metal1、Poly Contact、Poly2 Contact、Capacitor ID等图层,电容的有效面积是Poly、Poly2的正对面积,也就是Poly2的面积。

下图为50*50的电容,其画法为:Poly(66*56)、Poly2(50*50)、Capacitor ID (50*50)、Metal1、Poly Contact、Poly2 Contact。

图6 50*50电容版图

其电容提取如下:

.SUBCKT c1

C1 1 2 c=1.1525e-012 $ (-29.5 20 20.5 70)

.ENDS

⑨ 版图:

图7 初学者所画轨对轨运放的版图

注意:1)此次版图所用工艺为MOSIS/ORBIT 1.2u SCNA 。

(设置替换路径为:C:\program files\Tanner EDA\Tanner Tools v13.1\L-Edit and LVS\Tech\Mosis\morbn12)

2)替换设置后,将设置-设计-technology 下的technology to micro map 改为: 1 Lambda=11 microns 。

T-spice 后仿真时所用工艺为余华老师所给的1.25u 的工艺。