Array制程及设备介绍

TFT-LCD ARRAY制程介绍

PVD

20040531

29

缺角欠損-PHO

GE_D

PVD膜完整無欠損

20040531

30

Al殘-PHO

GE_D GE_D GE_D

GE_D

GE_R

GE_R

樹枝狀異物 TEL PHO Ionizer噴嘴髒

20040531 31

Al殘-PVD

GE_D

GE_R

20040531 32

GOCO-PVD

學習目標

暸解TFT的結構 暸解TFT-LCD Array之製造流程 簡易Array相關缺陷介紹20040531来自1TFT產業結構

TFT基板 TFT基板 玻璃 彩色濾 光片 偏光片 CCFL TFT面板 液晶監視 器 液晶電視 背光模 組 控制IC 驅動IC 導光板 PCB 訊號傳 輸IC CCFFL

pvdthinfilm膜厚均一性均一性膜厚particle製程別製程別部門部門2004053120缺陷判斷之技巧與工具缺陷判斷之技巧與工具點線不良判定點線不良判定tft電性電性缺陷形狀缺陷形狀大小大小位置位置斷面元素比對元素比對缺陷形狀缺陷形狀大小斷面大小斷面斷面顏色顏色透光顏色顏色斑點透光斑點mura條紋條紋明暗明暗技巧技巧缺陷全檢再以缺陷全檢再以omreview顯示特性檢查顯示特性檢查缺陷正確位置確認缺陷正確位置確認taper量測缺陷成分比對缺陷成分比對量測3um以下之缺陷解析以下之缺陷解析3um以上之缺陷檢查以上之缺陷檢查快速快速明顯之缺陷檢查明顯之缺陷檢查適用範圍適用範圍點不良檢查機點不良檢查機tegfib斷面分析斷面分析eds成分分析成分分析semom顯微鏡顯微鏡斜光斜光目視目視工具工具方法方法2004053121例例1

Au as spattering metal.

Array工艺设备介绍

14

GPCS (General Process Control System)

PECVD

PECVD:Plasma Enhanced Chemical Vapor Deposition

PECVD采用13.56MHZ射频电源使含有薄膜组成原子的气体电离,形成等离子体,在基板上反应,沉积薄膜。在TFT工 艺中,PECVD主要进行FGI、MULTI及PVX Film沉积。

Process Chamber

Transfer Module

P/C-2

P/C-1

T/M

高真空 P/C-3

Load Lock ATM Arm Indexer

L/L

真空大气 之间转化

大气机械手

USC

Port 1 Port 2 Port3

L/L: 连接真空和大气压的一 个Chamber。Glass进入此 Chamber以后,Valve关闭, 开始抽真空。

9

Sputter

Sputter的作用: Sputter在Array工艺中负责进行Gate, S/D 以及ITO Layer的溅射镀膜。

a-Si

SD(Source)

SD(Drain)

PVX(Passivation SiNx )

VIA Hole

ITO

GI(Gate Insulator)

n+ a-Si

Gate

Exposure

利用紫外光,按照Mask图案对PR进行曝光, 以便后续显影成像

Etch 刻蚀

Dry Etch Wet Etch

利用反应气体干法刻蚀非 金属或金属

Wet Etch

Strip

amoled array工艺流程

AMOLED Array工艺流程

AMOLED Array工艺流程主要包括以下几个步骤:

1.清洗:在开始制作AMOLED显示屏之前,需要对硅片进行清洗,以去除

表面的污垢和杂质。

2.涂覆光刻胶:在硅片表面涂覆一层光刻胶,作为掩膜,用于保护不需要进

行刻蚀的区域。

3.曝光:通过紫外线曝光的方式,将光刻胶上的图案转移到硅片上。

4.显影:使用化学试剂将曝光后的光刻胶去除,留下所需的图案。

5.刻蚀:使用化学或物理方法将硅片表面的材料去除,形成电路结构。

6.去胶:在完成刻蚀后,去除涂覆在硅片表面的光刻胶。

7.清洗和烘干:最后进行清洗和烘干,去除残留的化学物质和杂质,为后续

的工艺步骤做准备。

8.封装测试:最后,对制成的AMOLED显示屏进行封装和测试,确保其正

常工作。

以上是AMOLED Array工艺流程的基本步骤,具体工艺参数和细节可能会根据不同的制造厂商和生产工艺有所不同。

ARRAY制程

ITO

此处充液晶, 形成液晶电容

CF层

通过导电晶球压破,使 CF和Common线导通

CF与Common线中 竖直方向的线导通

Array 5PEP 完整制作过程模拟

1PEP

成膜 ⇒涂光刻胶

⇒曝光 ⇒显影 ⇒刻蚀 ⇒剥离

光

SL

TFT

CS

2PEP

成膜

⇒涂光刻胶 ⇒曝光

⇒显影

⇒刻蚀

⇒剥离

1PEP俯视图

后续所有剖面图 是从此处剖开

Common线

Gate线

1 PEP 剖面图

1.金属膜材料: AL-Nd/Mo 2.成膜方式 : 溅射(PVD) 3.刻蚀方式: 湿蚀刻 4.作用:扫描电极,控制“开关” 的导通或断开。 PVD:物理气象沉积,即非化学反应成膜。

Gate线

玻璃基板

1PEP剖面图(2)

P-SINx

D 电极 ITO电极

第三层

第四层 第三层

第二层 第五层

Gate 电极

第一层

玻璃基板(Glass) GIN – a-Si GIN – N+a-Si GIN - SINx GI - SINx

工艺流程

Light Photo Resist Photo Mask Photo Resist Thin Film Thin Film Glass

Array制程、TFT等效电路介绍

Prepared by: update: 2012 /11/28

Array 制程

素玻璃 重 复 五 次 ( 五 层 膜 ) 成膜 上光阻 统称黄光 剥膜 蚀刻 显影 曝光

基板测试 OK

NG

进行维修

送至Cell厂

液晶板制作流程之前段Array

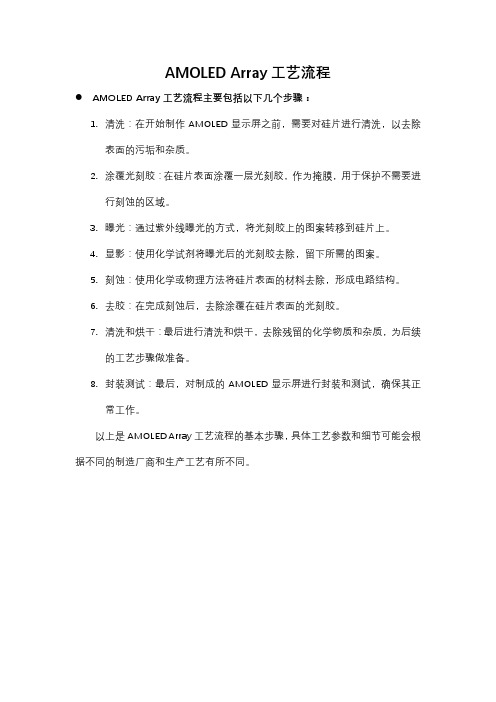

前段Array制程:薄膜/黄光/蚀刻/剥膜(一)液晶面板制造的前段Array制程主要是“薄膜、黄光、蚀刻、剥膜”四大部分,如果仅仅是这样看,很多网友根本不解这四步的具体含义,以及为什么会这样做。

首先,液晶分子的运动与排列都需要电子来驱动,因此在液晶的载体——TFT玻璃上,必须有能够导电的部分,来控制液晶的运动,这里将会用ITO(Indium Tin Oxide,透明导电金属)来做这件事情。

ITO是透明的,也成薄膜导电晶体,这样才不会阻挡背光。

液晶分子排列的不同以及快速的运动变化,才能保证每个像素精准显示相应的颜色,并且图像的变化精确快速,这就要求对液晶分子控制的精密。

ITO薄膜需要做特殊的处理,就犹如在PCB板上印刷电路一般,在整个液晶板上画出导电线路。

首先,需要在TFT玻璃上沉积ITO薄膜层,这样整块TFT 玻璃上就有了一层平滑均匀的ITO薄膜。

然后用离子水,将ITO 玻璃洗净,准备进入下一步骤。

接下来,要在沉积了ITO薄膜的玻璃上涂上光刻胶,在ITO 玻璃上形成一层均匀的光阻层。

然后烘烤一段时间,将光刻胶的溶剂部分挥发,增加光阻材料与ITO玻璃的粘合度。

用紫外光(UV)通过预先制作好的电极图形掩模版照射光刻胶表面,使被照光刻胶层发生反应,在涂有光刻胶的玻璃上覆盖光刻掩模版在紫外灯下对光刻胶进行选择性曝光。

●前段Array制程:薄膜/黄光/蚀刻/剥膜(二)我们以一个像素单位为例,如上图,这个像素中,浅色部分未曝光,而深色的是曝光部分。

接着,用显影剂将曝光部分的光刻胶清洗掉,这样就只剩下未曝光的光刻胶部分,然后用离子水将溶解的光刻胶冲走。

显影之后需要加热烘烤,让未曝光的光刻胶更加坚固的依附在ITO玻璃上然后用适当的酸刻液将无光刻胶覆盖的ITO膜的蚀刻掉,只保留光刻胶下方的ITO膜。

ITO玻璃为(In2O3 与SnO2)的导电玻璃,未被光刻胶覆盖的ITO膜易与酸发生反应,而被光刻胶覆盖的ITO膜可以保留下来,得到相应的拉线电极。

TFT-LCD Array 制程介绍

LCD的動作原理

TFT LC

Cs 保持電容

•為何叫做Array

1.Array是陣列的意思 2.RGB 與 Pixel(像素) 3.TFT:薄膜電晶體

4.解析度(如XGA)

解析度 VGA SVGA XGA SXGA

水平 640 800 1024 1280

像素個數 垂直 480 600 768 1024

乾蝕刻(Dry Etch)

目的:利用電漿以化學反應的方式將沒有光阻保護的沈積層去除,使線路圖案成型 原理:於反應器中通入特定的氣體,形成高能電漿,藉由電漿的高能離子或自由基 擴散至晶片表面與未被光阻保護的沈積層產生化學反應,藉以達到蝕刻的目 的,主要有PE,RIE,ICP等三種不同原理的機台,下圖所描述者為PE(Plasma Etch, 電漿蝕刻機)

蝕刻

蝕刻液分子 生成物分子 蝕刻液分子運動方向 生成物分子運動方向

蝕刻溶液

薄膜

去光阻機(Stripper)

目的:將蝕刻完成的玻璃基板去除其線路圖案上的保護光阻,以完成該PEP的最終動 作,然後送至薄膜區沈積下一PEP所需的薄膜

Array 製程介紹

By FA/CP

Array 製程介紹

• • • 何謂TFT-LCD 為何叫做Array Array製程的介紹 1. 製程簡介 2. 薄膜(Thin Film)區 3. 黃光(Photo)區 4. 蝕刻(Etching)區 5. 測試(Array Test)區

•何謂 TFT-LCD

ARRAY

Photo

Etching

Cell Area

薄膜(Thin Film)區

共有三種主要機台

清洗機(Cleaner)

CVD(化學氣相沈積)

Array工艺过程

Stress测量的是薄膜应力,薄膜应力太大,容易引起玻璃基板弯曲乃至broken。

Page 20

五、 Photo工艺简介

(3) 显影 Development DEV

品质、速度、团队

通过化学作用将感光的光刻胶溶解去掉,将未感光的光刻胶固化。

Six sigma for working smarter

Page 21

五、 Photo工艺简介

品质、速度、团队

1. 光刻工序在整个阵列工序中起着承上启下的作用,它和其他两个阵 列工序一样,光刻工序使用5MASK工艺处理玻璃基板,具体的说, 就是将最终要在玻璃基板上形成的TFT pattern 分成GATE ,ACTIVE , S/D , VIA ,ITO

Six sigma for working smarter

Page 3

二、Clean工艺简介

品质、速度、团队

目的: 除去基板表面影响成膜的具有物理特性、化学特性、电学特性 的异物及基板表面附着的灰尘、油份、自然氧化物等等,露出干 净的膜层及洁净的质地,此外还可以除去成膜后的表面灰尘、异 物等。

的:Glass输入时,去除残留的Particle和Metal/有机物等

Coat

此过程通过Track机单元来实现。

Six sigma for working smarterPage 19五、 Photo工艺简介

(2) 曝光Exposure Exposure

品质、速度、团队

Array工艺过程..

Six sigma for working smarter

Page 4

二、 Clean工艺简介

品质、速度、团队

Wet Cleaning

Spray Shower Aqua-knife Shower Brush Cleaning Ultra Sonic Mega Sonic bubble Jet Cleaning Detergent cleaning

湿法刻蚀:

① PR Mask后,利用化学药剂去除薄膜形成Pattern,主要适于金 属膜或ITO PATTERN的形成。 ② 有利于选择比和大面积刻蚀的均匀度,生产性的提高, 成本的 降低。

干法刻蚀:

利用真空气体和RF Power 生成的Gas Plasma反应产生原子和 原子团,该原子和原子团与淀积在基板上的物质反应生成挥发性 物质或者发生碰撞。利用该原理可进行干法刻蚀。

就要求 Magnet Bar 随着 Target 的使用量而

进行相应的调整。刚换完靶材后,TM值比较 小,当靶材消耗到一定程度后,需要适当调

Glass Backing TargetPlate Magnet Bar 共同板

整TM值,从而改善Rs均匀性。

Six sigma for working smarter

五、 Photo工艺简介

品质、速度、团队

(3) 显影 Development

DEV

通过化学作用将感光的光刻胶溶解去掉,将未感光的光刻胶固化。

Six sigma for working smarter

Page 21

五、 Photo工艺简介

品质、速度、团队

1. 光刻工序在整个阵列工序中起着承上启下的作用,它和其他两个阵 列工序一样,光刻工序使用5MASK工艺处理玻璃基板,具体的说, 就是将最终要在玻璃基板上形成的TFT pattern 分成GATE ,ACTIVE , S/D , VIA ,ITO 2 . 5个层,每次曝光形成一个层,最后叠加形成最终的TFT pattern 。

ARRAY-制程TFT等效电路解析

+ + + --+ +

+

+- +

+

+

++

-

-

-+

-+

+

-

+ -

GIN – N+a-Si (N plus层)

G电极给入高电平时: a-Si层中负离子向下偏移,由于总电荷为0, 一次正离子向上偏移, 使N plus中的负离子向下吸附,正离子向上 吸附。因此“开关”导通

GIN - a-Si (a-Si层)

IVO Confidential

3PEP俯视图

IVO Confidential

3 PEP剖面图

1.金属膜材料 : Mo/Al/Mo 2.成膜方式 : 溅射(PVD) 3.刻蚀方式 : 湿蚀刻M2 干蚀刻沟道 (N+a-Si) 4.作用:数据电极

(提供信号,对液晶电容进行充电)

Drain极

信号线、源电极(source极)

5PEP

成膜

⇒涂光刻胶 ⇒曝光 ⇒显影

⇒刻蚀

⇒剥离

TFT

CS

IVO Confidential

Thanks!

IVO Confidential

Glass

曝光

成膜

显影 蚀刻

IVO Confidential

剥膜

TFT等效电路

Gate线(栅 线/闸线/扫 描线) G(栅电 极或闸 极) Gate 有源层

a - Si

G(栅电极或闸极)

Gate

Data线 (信号线 /数据线)

=

Cs

储存电容

S(源电极) Source

Array制程及设备介绍

2.3.2 TN像素结构及制作工艺流程-Island Mask 2:SE (岛状半导体形成)

A

Source Drain α-Si

Gate

A

ITO CH Gate insulator

A’

A

A’

1. 成膜SiNx 2. 成膜后洗净 3. 成膜SiNx/a-Si/n+Si 4. 光阻涂布/曝光/显影 5. 蚀刻(DRY) 6. 光阻去除 7. 检查

2.4

像素形成的过程

3

Array面板重要指标

Pixel Matrix

TFT 特性

面板 特性

所有像素点阵保持一致的电特性和显示特性

电子迁移率Mobility 临界电压Vth 开关比Ion/Ioff

开口率: (1)TFT Size; (2) Line CD(Critical dimension) (3)Cst; (4) 上下基板对位误差;(5)Disclination of LC

低hillock(毛刺凸起) 低阻、barrier性能

Pixel RE

ITO

像素电极导电材料

4.1.2.1 PECVD

Plasma Enhanced Chemical Vapor Deposition

(等离子体增强型化学气相沉积)

利用等离子体辅助活化反应气体,降低反应温度,改善薄膜质量。

Process Gas

plasma assisted Chemical reaction

Thin Film

4

Array设备及工艺简介

Gate TFT

Pixel Cs

COM

B’ Data

Source Drain α-Si

Gate

A

array阵列工艺

array阵列工艺Array阵列工艺什么是Array阵列工艺?Array阵列工艺是一种先进的制造技术,广泛应用于电子领域。

它通过在基板上制作大量的微型元器件,如电阻、电容和晶体管等,形成一个二维排列的阵列结构。

Array阵列工艺的优势•高度集成:Array阵列工艺能够在一块基板上制作出大量的微型元器件,实现高度集成的电子器件。

这种高度集成的设计有助于缩小设备体积、提高性能和降低成本。

•可靠性:由于Array阵列工艺的制造过程经过严格的质量控制和检测,因此具有较高的可靠性。

这种可靠性可以保证制造出的电子器件在长时间的使用中不易出现故障。

•节约能源:Array阵列工艺充分利用基板表面的空间,通过紧凑的排列方式,有效地节约了能源。

与传统的分散布局相比,Array阵列工艺设计的电子器件可以在相同的工作面积上实现更高的性能。

Array阵列工艺的应用领域•芯片制造:Array阵列工艺广泛应用于芯片的制造过程中。

利用这种工艺,可以在一块芯片上制作出大量的晶体管、电阻和电容等元件,实现高密度的集成电路设计。

•平板显示器:Array阵列工艺是制造平板显示器的关键技术之一。

通过将大量的发光二极管排列在一块平板上,可以制造出高分辨率、高亮度的显示屏。

•太阳能电池板:Array阵列工艺也被应用于太阳能电池板的制造中。

通过在一块太阳能电池板上布置大量的太阳能电池单元,可以实现更高的能量转换效率。

•传感器:Array阵列工艺广泛用于各种传感器的制造中。

利用这种工艺,可以在一块传感器上集成多个传感器单元,实现多功能的传感器设计。

结论Array阵列工艺作为一种先进的制造技术,在电子领域具有广泛的应用前景。

它的高度集成、可靠性和节约能源的优势,使得电子器件的设计变得更加灵活和高效。

随着技术的不断进步,相信Array阵列工艺将在未来发展出更多的潜力和应用价值。

Array阵列工艺的制造流程•基板准备:首先,需要准备一块适用于Array阵列工艺的基板。

Array工艺卡(PVD)总览

拟 制

审 核

批 准

制程站点

制程站点

注意事项:1. 异常时请及时通知值班工程师; 2. 请注意工艺卡的版本日期及更新状况;

13100

13100Target life S4≤8600 kWh Target life S5

≤8600 kWh

S5加热温度233℃±10℃

Target life S3≤8600 kWh S3加热温度240℃±10℃S4加热温度

243℃±10℃二级管控参数

设备工艺参数名称

设备工艺参数指标

允许变化范围

H(0-4)加热温度125℃±10℃Mo Discharge power 31kW ±2kW Mo magnet scan times

12

±1

discharge pressure

0.3Pa ±0.03Pa Ar 流量

100sccm ±10sccm Mo target

ULVAC

1130mm*1200mm

一级管控参数

设备工艺参数名称

设备工艺参数指标

允许变化范围主要材料

材料名称材料生产厂家材料型号材料规格Mo target Plansee 1130mm*1200mm 工艺卡卡号A1PVD300

适用产品2200Å Mo 产品均适用 S/D deposition

文件编号: C-WI01007 附件3 版号:1.2

Array 工艺卡SD Depo

生效日期: 版本:1.1

工序

SD Depo Recipe No./Name

NPPVD02。

Array 制程简介

2

InnoLux

All Rights Reserved

TFT Array structure

數據線 控制線

銀交點 對位mark

InnoLux Confidential

3

InnoLux

All Rights Reserved

TFT Array PEP

主製程 次製程

PVD CVD

Monitor Item

InnoLux Confidential

11

InnoLux

All Rights Reserved

TFT Device operation

Vgs Vth

S

D

G

元件示意圖

i) 在閘極(G)給予適當之電壓 : Vgs > Vth 使通道感應出電子,由源極(S)導通至汲極(D)

S

D

ON

G

ii) 當閘極(G)之電壓 Vgs < Vth 則感應不出電子,使得通道形成斷路

Array Test – after 5 PEP process

TEG 元件測試 Laser Repair 畫素修補 Array finish cell

1. TEG元件測試 :量測元件導通截止電流及量測電壓 電流曲線 2. Laser repair : 係利用雷射加工使得不良之產品 變為良品,以增加工廠良率與提升產品等級.

ITO

鍍上ITO(銦錫氧化物,透明畫素電極)

InnoLux Confidential

6

InnoLux

All Rights Reserved

TFT Array 5 PEP Process

PEP1 GE Layer

GE:4000Å

Cst

array阵列制程释义

array阵列制程释义array阵列制程是一种在电子设备制造过程中广泛应用的技术。

阵列制程是指将多个类似的元件放置在一个阵列状的结构中,通过统一的工艺来制造,以提高生产效率和降低成本。

本文将介绍array阵列制程的原理、应用和未来发展趋势。

在电子设备制造过程中,阵列制程是一项重要的技术。

它通过将多个相同的元件进行批量生产,并通过一系列的工艺步骤来制造这些元件。

这种批量生产的方式可以大大提高生产效率,降低生产成本。

不仅如此,阵列制程还可以增加产品的一致性和可靠性,提高产品的质量和性能。

阵列制程可以应用于各种电子元件的制造,比如集成电路芯片、平板显示器和太阳能电池等。

这些元件通常都具有相同的结构和功能,因此适合使用阵列制程进行生产。

通过将这些元件按照一定的排列方式放置在同一个基板上,并通过一系列的工艺步骤完成制造,可以实现高效和精确的生产。

在阵列制程中,制造工艺是关键的一环。

制造工艺包括多个步骤,例如光刻、薄膜沉积、蚀刻和封装等。

这些步骤需要精密的设备和严格的操作控制,以确保产品的质量和性能。

制造工艺的改进和创新对于提高产品的性能和降低成本至关重要。

阵列制程的应用非常广泛。

在集成电路制造中,阵列制程可以用于生产存储器芯片、处理器芯片和传感器芯片等。

在平板显示器制造中,阵列制程可以用于生产液晶面板和有机发光二极管(OLED)屏幕等。

在太阳能电池制造中,阵列制程可以用于生产光伏电池阵列。

通过应用阵列制程,这些产品可以以更高的效率和更低的成本进行生产,从而使得电子设备更加普及和便宜。

随着科技的不断发展,阵列制程也在不断进步和创新。

新的材料、新的工艺和新的设备不断涌现,为阵列制程的发展提供了新的机遇。

例如,三维堆叠技术可以将多个器件叠加在一起,实现更高的集成度和更小的体积。

纳米技术可以制造出尺寸更小、性能更好的电子元件。

这些新技术的引入将进一步推动阵列制程的发展。

总之,array阵列制程是一种在电子设备制造中应用广泛的技术。

array工艺流程

array工艺流程Array工艺流程是指将半导体芯片的电路结构通过一系列工艺步骤逐渐建立起来的过程。

通常包括晶圆加工、光刻、沉积、蚀刻、清洗等多个环节。

下面将详细介绍一下Array工艺流程的各个步骤及其重要性。

首先是晶圆加工。

晶圆加工是将制造芯片所需的电路结构在硅片上进行刻印和形成。

这一步骤的关键工艺是化学气相沉积(CVD)和物理气相沉积(PVD)。

CVD是通过化学反应将气体沉积到晶圆表面上,形成所需的结构;而PVD是通过物理方式将有用元素沉积到晶圆表面。

这两种工艺在晶圆加工过程中是非常重要的,能够实现对晶圆表面进行修饰和成型。

然后是光刻。

光刻是将芯片上所需的电路图案通过光刻胶印在晶圆上的过程。

光刻工艺中使用的设备主要有光刻机和掩膜。

光刻机利用光刻胶对晶圆进行曝光和显影,形成所需的图案。

掩膜则是一张覆盖在晶圆上的玻璃板,上面有了所需的电路图案,可以指导光刻机进行曝光。

光刻过程具有精度高、适应性强的特点,是芯片制造中非常重要的工艺步骤。

接下来是沉积。

沉积是将芯片上所需的金属或化合物材料沉积到晶圆上的过程。

沉积工艺中使用的设备主要有化学气相沉积设备和物理气相沉积设备。

化学气相沉积设备可以将金属气体或化合物气体沉积到晶圆上,形成所需的金属或化合物薄膜;物理气相沉积设备则是通过物理方法将金属或化合物材料沉积到晶圆上。

沉积工艺在芯片制造中起着非常重要的作用,可以实现对晶圆表面进行修饰和成型。

然后是蚀刻。

蚀刻是将晶圆上不需要的结构或物质通过化学或物理方法进行去除的过程。

蚀刻工艺中主要使用的设备有湿蚀刻设备和干蚀刻设备。

湿蚀刻设备是通过酸性或碱性溶液将晶圆上的杂质或不需要的结构腐蚀掉;干蚀刻设备则是利用高能粒子束将晶圆上的杂质或不需要的结构腐蚀掉。

蚀刻工艺能够实现对晶圆上的结构精确的控制和去除,是芯片制造中非常重要的一环。

最后是清洗。

清洗是将芯片制造过程中产生的杂质或污染物从晶圆上清除的过程。

清洗工艺中主要使用的设备有超纯水设备和化学清洗设备。

array工艺流程

array工艺流程

《array工艺流程》

array是一种常用于集成电路制造中的工艺流程,它通过在硅片上建立一系列完整的电子元件来实现功能。

array工艺流程经历了多个步骤,如光刻、薄膜沉积、化学腐蚀、离子注入和金属化等。

首先,array工艺流程的第一步是光刻。

在这一步骤中,光刻胶被涂覆在硅片表面,然后使用掩模和紫外线将图案转移到光刻胶上。

接着,将光刻胶进行烘烤,以确定图案的形状。

这一步骤是制造电子元件的重要基础,因为它决定了元件的尺寸和排列。

接下来是薄膜沉积。

在这一步骤中,薄膜材料如氧化物或氮化物被沉积在硅片表面。

这一步骤可以改变硅片的特性,使其具有导电、绝缘或半导体特性。

然后是化学腐蚀。

这一步骤利用化学液体来去除光刻胶之外的材料,从而形成所需的结构。

化学腐蚀可以精确地去除材料,因此在array工艺流程中扮演着非常重要的角色。

离子注入是下一个步骤,它用于改变硅片的导电性能。

在这一步骤中,离子被注入硅片中,从而改变其导电性能。

这一步骤可以使得硅片在特定区域具有不同的导电性能,从而实现电子元件的功能。

最后是金属化。

在这一步骤中,金属被沉积在硅片表面,以形成电子元件之间的连接。

金属化是array工艺流程中的最后一步,它使得电子元件能够进行电子信号的传输。

综合来看,array工艺流程是集成电路制造中非常重要的一环。

通过不同步骤的精确控制,可以实现各种电子元件的高度集成和功能实现。

因此,array工艺流程的技术和工艺水平直接影

响着集成电路产品的性能和品质。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

固态

液态

气态

Plasma

状态转化 Entalpy change

4.1.2 CVD

Chemical Vapor Deposition(化学气相沉积)

APCVD (Atmospheric Pressure CVD)

760Torr,400℃ ~500℃ 优点是反应简单,反应温度低,成膜率高 缺点是Gas的使用量高,处理反应产物困难 现在基本不使用

2.3.3 TN像素结构及制作工艺流程-Souce/Drain Mask 3:SD (Source及Drain电极形成)

A

Source Drain α-Si

Gate

A

ITO CH Gate insulator

A’

A

A’

1.成膜Cr (4000A) 2.光阻涂布/曝光/显影 3.硬烤 4.蚀刻Cr(WET) 5.蚀刻n+Si(DRY) 6.光阻去除 7. 检查

2.4

像素形成的过程

3

Array面板重要指标

Pixel Matrix

TFT 特性

面板 特性

所有像素点阵保持一致的电特性和显示特性

电子迁移率Mobility 临界电压Vth 开关比Ion/Ioff

开口率: (1)TFT Size; (2) Line CD(Critical dimension) (3)Cst; (4) 上下基板对位误差;(5)Disclination of LC

(19202+10802)1/2/5.5= 400.5

@

课前知识

1

TFT LCD基本结构

2

TFT LCD基本发光原理

Gray Generation

TN Mode

Color Generation

3 显示器的驱动方式,无源驱动(PM-LCD)与有源驱动(AM-LCD)

无源驱动:利用视觉残留效应。存在占空比、串扰问题,无法实现高解析度 有源驱动:每颗像素单独控制,在下一帧刷新前保持当前亮度。

2.3

TN像素结构及制作工艺流程

Gate TFT

Pixel Cs

COM

B’ Data

Source Drain α-Si

Gate

A

ITO CH Gate insulator

A

A’

Mask1 Gate电极 Mo/Al

Mask2 Mask2

GI绝缘层 SiNx 半导体沟道 a-Si

Mask3 源漏电极 Mo/Al/Cr

2

像素的基本结构及Array工艺流程

3

Array工程重要指标

4

Array设备及工艺

5

Array设备布局及搬送系统

6

不同显示模式

7

低温多晶硅工艺介绍

1

Array是做什么的?

像素点阵的电路背板

2.1

Gate

像素的基本结构

TFT

Pixel Cst

B’ Data

随着TFT半导体材料选择的不同,器件结构和Array工艺也会产生很大的变化。

SR、SE、 椭圆偏振测量技术

SEM

扫描式电子显微镜

SE/Profile 对比刻蚀前后厚度差

SR、SE、 计算厚度的方差均匀度或者极

SEM

差均匀度

应力测量仪

激光相移方式或者光学聚焦方 式

FTIR/SIMS

傅氏转换红外线光谱分析仪/二 次离子质谱仪

4.1.2.5 CVD工艺可调参数

控制参数 温度 射频功率 气体流量 气体流量比 压力(真空度) Spacing (Plasma密度)

影响的薄膜质量评价参数 沉积速率、致密性、绝缘性、应力、氢含量、厚度均匀度 沉积速率、致密性 沉积速率、致密性、折射率 沉积速率、致密性、折射率、介电常数 沉积速率、致密性、折射率 沉积速率、Particle

4.1.3 PVD

Physical Vapor Deposition(物理气相沉积)

利用物理过程实现物质转移,将原子或分子由源转移到基材表面上。

基板

靶材原子

Ar+

磁铁

V1 V0

场电 电子e 靶材

阴极

E

磁场B

4.1.3.2 PVD(Sputter)设备结构

4.1.3.3 PVD(Sputter)薄膜种类

膜层

Gate

Source/ Drain

成分

Mo Ti Al Ti

作用

栅极导电材料 阻挡Al扩散 源漏极导电材料 阻挡Al扩散

特性要求

低阻

低阻、barrier性能 低阻,

SiNx

SiH4+NH3

绝缘层 阻挡性能、绝缘性能,介电常数

SiO

SiH4+N2O

绝缘层 绝缘、与半导体的界面缺陷

同样的薄膜结构,随着运用于不同的目的,其结构、工艺条件、作用 和特性要求相差甚远。

4.1.2.4 CVD膜质评价

评价项目 折射率(n)

作用说明 能反应薄膜中Si含量的变化

介电常数(k) 表征薄膜对电荷的存储能力

Array制程及设备介绍

几个概念

Retina

分辨率

M列

N行

分辨率=M×N

PPI( Pixels per inch) 屏幕对角线方向每英寸所拥有的像素点(Pixel)数目

问题

5.5英寸FHD(1920*1080)的手机屏是不是Retina屏幕?

乔布斯的定义:“当你所拿的东西距离你10-12英寸(约25-30厘米)时 ,它的分辨率只要达到300ppi这个‘神奇数字’ 以上,你的视网膜就无 法分辨出像素点了。”

2.3.4 TN像素结构及制作工艺流程-Contact Hole Mask 4:CH (Contact Hole形成)

A

Source Drain α-Si

Gate

A

ITO CH Gate insulator

A’

A

A

A’

1. 成膜SiNx 2. 光阻涂布/曝光/显影 3. 蚀刻(DRY) 4. 光阻去除&洗净 5. 检查

Mask4 接触孔

SiNx

Mask5 像素电极 ITO

2.3.1 TN像素结构及制作工艺流程-Gate

Mask 1:GE (Gate电极形成)

A

Source Drain α-Si

Gate

A

ITO CH Gate insulator

A’

A

A’

1. 玻璃洗淨 2. 溅镀Metal1(Al, For example) 3. 光阻涂布/曝光/显影 4. AlNd蚀刻(WET) 5. 光阻去除 6. 检查

4.1.2.1 PECVD

Plasma Enhanced Chemical Vapor Deposition

(等离子体增强型化学气相沉积)

利用等离子体辅助活化反应气体,降低反应温度,改善薄膜质量。

Process Gas

plasma assisted Chemical reaction

Thin Film

4.1

Thin film - 薄膜沉积

CVD:Chemical Vapor Deposition 化学气相沉积 (A+B→C)

PVD:Physical Vapor Deposition 物理气相沉积 (A+B→AB)

4.1.1 Plasma

Plasma① :等Pla离sm子a란 体?/ 电浆

等플 离라 子즈 体마 是란 一种전由기自적由인电방子전和으带로电离인子해为생主기要는成전分하的를物质띤形양态이,온广과泛전存자在들于의宇宙집中단말한다.

4

Array设备及工艺简介

Gate TFT

Pixel Cs

COM

B’ Data

Source Drain α-Si

Gate

A

ITO CH Gate insulator

A

PVD CVD CVD PVD CVD PVD

Gate电极 Gi绝缘层 半导体沟道 源漏电极 接触孔 像素电极

A’

Mo/Al SiNx a-Si Mo/Al SiNx ITO

厚度(THK)

沉积速率 (D.R)

蚀刻速率 (E.R)

表征薄膜的实际厚度 表征薄膜的生长速度 表征薄膜的致密性

均匀度(U%) 表征薄膜的平坦程度

应力(Stress) 表征薄膜内应力的大小

氢含量(H%) 表征薄膜内氢元素的含量

测试机台 SE CV测量仪

测试方式 椭圆偏振测量技术 汞探针方式测量CV曲线

讯号的时间延迟(RC Delay)及失真(Distortion) 因耦合电容(Cgs)产生的跳变电压

4

设备及工艺简介

4.1 Thin film-------------------薄膜沉积 4.2 Photolithography ----光刻 4.3 Etch ------------------------图形刻蚀

2.2

像素结构及Array制作工艺流程

Thin Film

4~13 Cycle

成膜 GALSS基板

成膜前洗浄

CVD装置、SPUTTER装置

PHOTO

涂布前洗浄

PR Coating

Exposure

Develop

Doping/ Etching

Doping ETCHING

PR Strip PR Strip

4 如何实现像素单独控制?

电荷 公共电极电位 电压(电位差)

电流 电容 晶体管开关 金属布线

类比

水量 水平面 水位差 水流 水槽Tank 水龙头 水管

说明

同一系统中的基准参考电位 重要的是两侧电极的电位差

容量与底面积成正比 有开关特性,同时决定着电流大小 粗细决定着电流大小