版图技术——CMOS集成电路版图设计

cmos数字集成电路设计流程

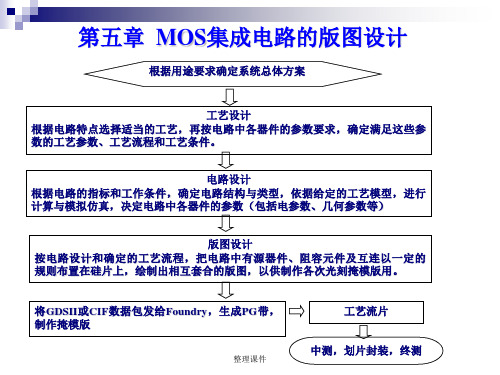

CMOS数字集成电路设计流程一、介绍CMOS数字集成电路设计是现代电子工程中的重要分支之一,涉及到数字逻辑、电子设计自动化、半导体器件物理和工艺等多个领域。

在数字集成电路的设计流程中,工程师需要进行功能分析、设计规划、逻辑综合、电路布局、版图设计、物理验证和后仿真等多个环节。

本文将就CMOS数字集成电路设计流程的各个环节进行详细介绍。

二、功能分析在进行CMOS数字集成电路设计之前,工程师需要首先完成功能分析。

在功能分析阶段,工程师需要明确电路的功能需求,包括各种逻辑门、寄存器、存储器等组件的功能与接口要求。

还需要对设计的电路进行规模估计,明确设计的规模和复杂度,为后续的设计规划和逻辑综合提供依据。

三、设计规划在完成功能分析之后,工程师需要进行设计规划。

设计规划阶段需要明确设计的总体结构、数据传输路径、时钟和控制信号的分配等。

还需要进行功耗和面积的预估,并确定设计的性能指标和约束条件等。

四、逻辑综合逻辑综合是数字集成电路设计的重要环节之一。

在逻辑综合过程中,工程师需要将设计的功能描述转换为门级网表,然后进行优化,包括面积优化、功耗优化、时序优化等。

逻辑综合的结果将是门级网表,为后续的电路布局和版图设计提供基础。

五、电路布局电路布局是数字集成电路设计的关键环节之一。

在电路布局过程中,工程师需要将逻辑综合的门级网表映射到物理结构上,并进行布线和布局设计。

电路布局需要考虑电路的面积、功耗、时序等多个方面的优化,并确保电路的稳定性和可靠性。

六、版图设计版图设计是数字集成电路设计中的重要环节之一。

在版图设计过程中,工程师需要将电路布局转换为实际的版图,并进行细化设计,包括晶体管布局、金属线路设计、接口电路设计等。

版图设计需要满足工艺规则和制约条件,确保设计的可制造性和可测试性。

七、物理验证物理验证是数字集成电路设计中不可或缺的一环。

在物理验证过程中,工程师需要进行电路的各种仿真和验证工作,包括静态时序分析、动态时序分析、功耗分析、布局抽取等。

CMOS版图设计

第5章CMOS版图设计5.1 版图设计基本概念5.2 设计规则5.3 基本工艺层版图5.4 FET版图尺寸的确定5.5 逻辑门的版图设计5.6标准单元版图5.7 设计层次化2/783/785.1 版图设计基本概念⏹什么是版图设计?☐Layout design :定义各工艺层图形的形状、尺寸以及不同工艺层的相对位置。

⏹版图设计的内容☐布局:就是将组成集成电路的各部分合理地布置在芯片上。

安排各个晶体管、基本单元、复杂单元在芯片上的位置。

☐布线:就是按电路图给出的连接关系,在版图上布置元器件之间、各部分之间的连接。

设计走线,实现管间、门间、单元间的互连。

☐尺寸确定:确定晶体管尺寸(W、L)、互连尺寸(宽度)以及晶体管与互连之间的相对尺寸等。

4/78⏹版图设计的目标☐满足电路功能、性能指标、质量要求☐尽可能节省面积,以提高集成度,降低成本☐尽可能缩短连线,以减少复杂度,缩短延时、改善可靠性5/78EDA工具的作用(EDA: Electronic Design Automation)⏹版图编辑☐规定各个工艺层上图形的形状、尺寸、位置(Layout Editor)⏹规则检查☐版图与电路图一致性检查(LVS,Layout VersusSchematic)☐设计规则检查(DRC,Design Rule Checker)☐电气规则检查(ERC,Electrical Rule Checker)⏹布局布线☐Place and route,自动给出版图布局与布线6/787/78电路图与版图一致性检查(LVS )从版图中提取的电路同原电路相比较,其方法通常是将两者的网表进行对比。

比较的结果,可以是完全一致或两者不全一致,设计者应对所示的错误进行必要的版图修改。

电路图与版图一致性检查(LVS: Layout Versus Schematic )设计规则检验(DRC:Design Rule Check)设计规则检查是一个运用版图数据库检查在版图上涉及的每条设计规则的程序。

集成电路版图设计 ppt课件

(b)

图8.3 交叠的定义

表8.5 TSMC_0.35μm CMOS工艺版图各层图形之间最小交叠

表 16.5 T SM C _0.35μ m C M O S 工 艺 版 图 各 层 图 形 之 间 最 小 交 迭

N _ w e ll A c tiv e P o ly P _ l\p lu s_ se le c t/N _ p lu s_ se l ect C o n ta c t M e ta l1 V ia 1 M e ta l2 E le c tro d e V ia 2 M e ta l3

MOS管的可变参数为:栅长(gate_length)、栅宽(gate_width) 和栅指数(gates)。

栅长(gate_length)指栅极下源区和漏区之间的沟道长度,最 小值为2lambda=0.4μm。

栅宽(gate_width)指栅极下有源区(沟道)的宽度,最小栅宽为 3 lambda=0.6μm。

201010233636cmos差动放大器单元电路设计版图的过程vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图716画l型金属线作地线图717画出两只mcs3并将它们的栅漏和源极互连201010233737vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图718画出两只mn1并将它们的栅漏和源极互连cmos差动放大器单元电路设计版图的过程201010233838图719依次画出r1并联的两只msf1和并联的两只mcf1以及偏压等半边电路版图vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outoutcmos差动放大器单元电路设计版图的过程201010233939cmos差动放大器单元电路设计版图的过程vinvinqr1r2vddmn1mn2mps2mcs2mgcsmcf1mcf2msf1msf2outout图720通过对图819中半边版图对x轴作镜像复制形成的完整版图201010234040在正式用cadence画版图之前一定要先构思也就是要仔细想一想每个管子打算怎样安排管子之间怎样连接最后的电源线地线怎样走

集成电路原理课件-cmos

1

微电子学

• 微电子技术是电子计算机和通信的核心技术 • 微电子技术的核心是集成电路(Integrated Circuit, IC) 技术 • 微电子学是电子学的一门分支,主要研究电子或离 子在固体材料中的运动规律及其应用 • 微电子学是以实现电路和系统的集成为目的,研究 如何利用半导体的微观特性以及一些特殊工艺,在 一块半导体芯片上制作大量的器件,从而在一个微 小面积中制造出复杂的电子系统。

I

D

dx

V 0

WC

ox

n [VGS V ( x) VTH ]dV

I/V特性的推导(3)

W 1 2 I D = nCox [(VGS - VTH )VDS - VDS ] (2.8) L 2 W VGS - VTH 称为过驱动电压; 称为宽长比 L 三极管区(线性区)

每条曲线在VDS=VGS-VTH时取最 大值,且大小为:

CGD CGS

WLCOX WCOv 2

CGB可以忽略不计

CSB = CDB =

WE源极Cj (1 VSB /B ) WE漏极Cj (1 VDB /B )

mj mj

源极周长 C jsw (1 VSB /B )

m jsw

漏极周长 C jsw (1 VDB/B )

MOS器件电容

栅源、栅漏、栅衬电容与VGS关系

1) VGS < VTH截止区

CGD CGS WCOv

CGB W 2 L2 COX q si N sub / 4 F WLCOX Cd = 其中Cd=WL q si N sub / 4 F WLCOX Cd WLCOX WL q si N sub / 4 F

制造工艺-CMOS集成电路原理图及版图

硅芯片上的电子世界—晶体管

• 三级管:pnp,npn • 硅芯片上的三极管:

2012年春季

P+ …N…+. P+

N阱

P型衬底

28中北大学

三极管的设计

CMOS工艺下可以做双极晶体管。 以N阱工艺为例说明PNP, NPN如何形成。

PNP

注:

薄氧

由于P衬底接最低电位vss/gnd

因此,VPNP集电极也必须接

C

N+

N–-epi

钝化层

SiO2

P+

P-Sub

2012年春季

N+埋层

P P(G- ND)

N+

Sub

EB C

N+ P

N+

P+

N–-epi

60

60中北大学

版图设计

• 电子设计 + 绘图艺术 • 仔细设计,确保质量

2012年春季

61中北大学

MOS管的版图设计

沟道宽

沟道长

当多晶硅穿过有源区时,就形成了一个管子。在图中当 多晶硅穿过N型有源区时,形成NMOS,当多晶硅穿过P型有 源区时,形成PMOS。

MIM 上电级

第n-1层金属

电容区的下方不要走线;

2012年春季

20中北大学

多层金属制作的平板电容和侧壁电容

多层平板电容(MIM) •增加单位面积电容; •精度高,匹配性好;

2012年春季

侧壁电容: •单位面积电容值可比左边的大; •精度较高,匹配性较好;

21中北大学

MOS电容

CGS

累积区

强反型

vss/gnd 。

C

B

精品PPTCMOS版图

基本IC单元版图设计 – CMOS layout

器件尺寸设计:SPICE - SPICE: Simulation Program for ICs Emphasis 利用SPICE去确定器件尺寸。

SPECS电路规范

mathematical model

SPICE

device size

schematic

on

off

D

input signal of A

基本IC单元版图设计 – CMOS layout

器件尺寸设计:大尺寸器件的设计

- 寄生栅电阻可减慢寄生电容的充放电速度,即存在一个 RC时间常数。

- 晶体管的长度,即沟道长度,决定了晶体管开关的速 度,因此,栅的长度是不允许改变的,同时,也必须 维持相同的有效栅宽。

连接后: 缺点:浪费了大量的空间。

好的连接办法:源和漏互换

对第二个和第四个晶体管进行左右翻转,两个B点彼此相对, 两个A点彼此相对。将相对的源漏区合并,这些合并的区域既 可以是一个晶体管的源,同时也可以是另一个晶体管的漏。

练习题:

如果是被同一根线进行连接,则可以类似源漏共用那 样进行共用,如果一个是A,另一个是B则不能。如 下电路图,那些可以共用,试着画出版图。

经验法则:如果需要分配电压是(如开关某些 器件),可以利用多晶硅,如果需要分配电流, 则采用金属。

可采用多晶硅作为内连线,但通常仅限于连接 栅,因为栅上电流小。

图形关系

总结

在本章学到以下内容: 1.模型、计算机模拟的原理图与参数规范; 2.确定器件尺寸; 3.通过分裂器件减小寄生电阻; 4.更好的适用的技术; 5.作为设计工具的棒状图; 6.借助钳位与连接释放电压; 7.避免固有的衬底二极管正偏; 8.原理图、棒状图和器件之间的关系; 9.源漏共用;

集成电路版图设计

02 集成电路版图设计基础

CHAPTER

电路设计基础

01

模拟电路设计

02

运算放大器

03

比较器

04

触发器

电路设计基础

01

数字电路设计

02

组合逻辑电路

时序逻辑电路

03

04

可编程逻辑电 路

版图设计基础

版图编辑软件 ICEDrawer

版图设计基础

01

Laker

02

P甩 Pro

版图设计规则

03

版图设计基础

管的形状和尺寸等。

案例二:低功耗模拟电路版图设计

总结词

通过优化模拟电路的版图设计,实现低功耗的目的, 以满足便携式电子设备和物联网等领域的需求。

详细描述

低功耗模拟电路版图设计需要考虑模拟电路的性能和 功耗等方面,同时还需要考虑噪声和失真等方面的因 素。为了实现低功耗的设计,需要采用优化的版图设 计方法,如使用低阻抗的走线、优化晶体管的形状和 尺寸等。

3

antenna effect simulation

物理验证基础 01

P/R/O/L/C分析

热学参数分析(T)

03

02

电学参数分析(P/R/O)

电磁兼容性分析(EMC)

04

03 集成电路版图设计技术

CHAPTER

逻辑电路版图设计

逻辑电路

逻辑电路是实现逻辑运算和逻辑控制的电路,分为组合逻 辑电路和时序逻辑电路。在版图设计中,需要考虑到电路 的复杂性、功耗、速度等因素。

提高芯片的可测试性。

可制造性版图设计实践

符合制造规范

遵循制造规范和流程,确保版图设计具有良好的可制 造性。

集成电路版图设计2

说明

文件结构:在本实例文件ex2.sdb中共有六个模块, 包括Vdd,Gnd,MOSFET_N,MOSFET_P,inv与 Nand2.各模块的内容可Module→Open命令打开 并进行修改. Wire(联机)按钮 :Wire按钮是用在电路设计模式 中各元件之间的信号连接. Line(直线)按钮 :Line按钮是画直线的工具,可以 用在符号模式中绘制电路符号,但不可以在电路设 计模式中进行电路之间的联机操作.

基本CMOS集成电路设计

包含NMOS和PMOS网络

Hale Waihona Puke 基本门电路:非门 与非门 或非门

组合门电路:

使用 S-Edit 编辑简单的逻辑电路

使用S-Edit 编辑反相器 使用S-Edit 编辑与非门 使用S-Edit 编辑与门 使用S-Edit 编辑或非门 使用S-Edit 编辑或门

使用S-Edit设计反向器的步骤

打开程序 建立反相器符号 另存新文件 加入输入端口与输出 环境设置 端口 编辑模块 更改模块名称 浏览组件库 反相器设计成果 从组件库引用模块 模块输出格式 编辑反相器 输出成SPICE文件 加入联机 加入输入端口与输出端口

集成电路版图设计2

内容: 使用tanner Pro软件设计简单的逻辑电路

任务清单:

使用S-Edit 编辑反相器(必选) 使用S-Edit 编辑与非门(以下四个任选其中两个) 使用S-Edit 编辑与门 使用S-Edit 编辑或非门 使用S-Edit 编辑或门

知识梳理

NMOS和PMOS的简单认识

CMOS版图设计技巧之一解读

集成电路版图设计

西南科技大学

实现源漏共用设计:晶体管有两 个端点A和V+,将它们在左边第一个栅的两边分 别标注。

NMOS版图

集成电路版图设计 西南科技大学

为了找到源漏共用的晶体管,建议把扩散区拆成 几段

集成电路版图设计

西南科技大学

改进:设法减小版图的面积。利用源漏共用,除去一些断 开点,试着连接V+端。 将第二个晶体管左右翻转。能达到的最好的结果:

集成电路版图设计

西南科技大学

二、棒状图(棍棒图)

如何才能容易的从电路图得到最有效的源漏共用版图

呢?——— 棒状图

棒状图的作用:

1、告诉器件的布局和连线关系,之后的工作是用实

际的器件和连线替代棒状图。

2、层之间的连接由“×”决定。表示对氧化层进行刻

蚀

集成电路版图设计 西南科技大学

倒相器

以倒相器为例 在设计中,P型器件通常放在一个共用的N阱 中,N型器件也被放置在一个共用的P阱中。

西南科技大学

集成电路版图设计

主讲 李斌

E_mail:bin_lichina@

信息类专业课程

集成电路版图设计 西南科技大学

内容

一、紧凑型版图 二、棒状图 三、CMOS主从触发器棍棒图的画法

集成电路版图设计

西南科技大学

一、紧凑型版图

经验法则:通过小的、易于理解的功能模块构造大 的设计。 设计目标是使版图紧凑,在设计器件时应尽可能利 用矩形。

集成电路版图设计

西南科技大学

MOS晶体管

1、用一条水平的棒状图形来表示P型扩散区并使其位于图的顶部, 以另一条水平的棒状图形表示N型扩散区并使其位于图的底部。 2、在棒状图中,多晶硅、扩散区以及连线都可以用一条简单的线 来表示 3、多晶硅与扩散区交叉的时候表示一个晶体管。通常棒状图中, 将p型器件放置在顶部,n型器件放置在底部。以“x”表示器 件接触点连接的位置。一两条平行的竖线表示扩散区断开点 的位置。

集成电路版图基础CMOS版图篇

(2)源漏共用── 合并源/漏区,将4个小MOS管并联

(a)形成S-G-D、S-G-D…排列

(b)左起第二个和第四个MOS管的、和漏互换

(c)将相邻S、D重叠

并联后MOS管宽长比与原大尺寸管宽长比 相同;

并联小MOS管个数为N,并联管的宽长比 等于原大尺寸管宽长比的1/N;

栅极串联电阻为原大尺寸管寄生电容的1/N

大面积的栅极与衬底之间有氧化 层隔绝,形成平板电容

栅电压降低

细长的栅极存在串联电阻,导 致栅极两端电压不同

MOS管寄生电容值

CW LC 0

MOS管栅极串联电阻值

RW/LR

S G

D

设计方法 (1)分段──

大尺寸MOS管分段成若干小尺寸MOS管。

(a) MOS管的W/L=200/1

(b) 截成4段(W/L=50/1)

含义 N阱 有源扩散区 P型注入掩膜 N型注入掩膜 多晶硅 引线孔 第一层金属 第二层金属 通孔

注意:

不同软件对图层名称定义不同; 严格区分图层作用。

版图图层名称 cc(或cont)

Via

含义

引线孔(连接金属与多晶硅 或有源区)

通孔(连接第一和第二层金 属)

MOS器件版图图层 ——PMOS

N阱——NWELL P型注入掩模——PSELECT 有源扩散区——ACTIVE 多晶硅栅——POLY 引线孔——CC 金属一——METAL1 通孔一——VIA 金属二——METAL2

a)由源、栅和漏组成的器件;

b)衬底连接。

源区、沟道区和漏区合称为MOS管的 有源区(Active),有源区之外的区域 定义为场区(Fox)。有源区和场区之 和就是整个芯片表面即基片衬底 (SUB)。

毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]

![毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]](https://img.taocdn.com/s3/m/15f996a177232f60dccca185.png)

目录摘要 (3)第一章引言 (3)§ (3)§ CMOS 电路的发展和特点 (5)第二章CMOS运算放大器电路图 (8)§Pspice软件介绍 (8)Pspice运行环境 (12)Pspice功能简介 (12)§CMOS运算放大器电路图的制作 (14)§小结 (20)第三章版图设计 (20)§L-EDIT软件介绍 (20)§设计规则 (21)§集成电路版图设计 (24)PMOS版图设计 (24)NMOS版图设计 (27)CMOS运算放大器版图设计 (27)优化设计 (32)第四章仿真 (40)§DRC仿真 (41)§LVS 对照 (42)第五章总结 (48)附录 (50)参考文献 (52)致谢 (53)摘要介绍了CMOS运算放大电路的版图设计。

并对PMOS、NMOS、CMOS运算放大器版图、设计规则做了详细的分析。

通过设计规则检查(DRC)和版图与原理图对照(LVS)表明,此方案已基本达到了集成电路工艺的要求。

关键词:CMOS 放大器 NMOS PMOS 设计规则检查版图与原理图的对照AbstractThe layout desigen of CMOS operation amplifer is presented in this the layouts and design rules of PMOS,NMOS, and CMOS operation amplifer. The results of design rule check(DRC)and layout verification schmatic(LVS) shown that the project have already met to the needs of IC fabricated processing. Keywords: CMOS Amplifer NMOS PMOS DRC LVS第一章引言1.1 集成电路版图设计的发展现状和趋势集成电路的出现与飞速发展彻底改变了人类文明和人们日常生活的面目。

CMOS集成电路设计课件

鲁棒设计

鲁棒设计

电路性能随工艺、电源电压、温度而变化

器件模型参数的改变

阈值电压、二级效应参数 工艺角参数 TT、FF、SS、FNSP、SNFP 鲁棒设计电路性能随工艺、源压温度而变化器件模型

电源电压对器件工作区的影响

电压变化范围:20%

温度的范围

室温:25度、或50度 民品、军品

简单电路

单级放大器、差动放大器、电路偏置、电流镜电路

器件

CMOS工艺、器件物理、器件Spice参数、 *版图设计、*电路模拟

模拟集成电路设计步骤

设计要求描述

电路设计

与设计指标比较

模拟集成电路设计步骤要求描述定义与指标比

设计定义 执行设计

仿真

物理层设计 芯片设计

物理层设计 物理层验证 提取寄生参数

芯片制造

磁盘驱动器中的模块电路(C/filter …

磁盘驱动器中的模块电路(3)写发送扰码、RL编

小结

什么是模拟集成电路设计,模拟集成电路设计和分立模拟 电路与数字电路设计的区别,设计的难点。 设计步骤和直观的、层次的、鲁棒的设计。 模拟集成电路的应用、不同的信号带宽和工艺对模拟电路 的影响。 模拟信号处理系统设计和各种典型的模拟电路模块 小结什么是模拟集成电路设计,和分立 VLSI混合模拟信号电路设计举例

考核标准和联系方式

考核标准 平时作业 设计课题 期中练习 期末 联系方式

15% 15% 15% 55%

%5考核标准和联系方式1

导论

1.1 模拟集成电路设计的特点

层次化设计 设计步骤 鲁棒(robust)设计

1.2 模拟集成电路的应用 导论1.模拟集成电路设计的特点层次化2 1.3 模拟信号处理 1.4 混合信号电路举例

集成电路原理-MOS集成电路的版图设计

1.08(ns)

整理课件

0.0330.001

2、导电层的选择

(1)VDD、VSS尽可能选用金属导电层,并适当增加连线宽 度,只有在连线交叉“过桥”时,才考虑其他导电层。 (2)多晶硅不宜用作长连线,一般也不用于VDD、VSS电源 布线。 (3)通常应使晶体管等效电阻远大于连线电阻,以避免出 现电压的“分压”现象,影响电路正常工作。

若要形成耗尽型NMOS器件,只需在第(5)、(6)步之间加 一道掩模版,进行沟道区离子注入。

NMOS工艺流程的实质性概括: P型掺杂的单晶硅片上生长一层厚SiO2。 MK1—刻出有源区或其他扩散区(薄氧化版/扩散版)。 MK2—形成耗尽型器件时,刻出离子注入区。 MK3—刻多晶硅图形(栅、多晶硅连线)。

以多晶硅栅为掩模,进行D、S的自对准扩散。 MK4—刻接触孔。 MK5—反刻 Al。 MK6—刻钝化孔(压焊点窗口)

共用到6道掩模版 整理课件

3、硅栅CMOS工艺 (1)P阱CMOS工艺流程 • MK1—P阱版,确定P阱深扩散区域(阱注入剂量11013cm-2,

能量60KeV) • MK2—确定薄氧化区,即有源区。 • MK3—多晶硅版。 • MK4—P+版,和MK2一起确定所有的P+扩散区域 (一般为B注入,41014cm-221015cm-2,6080KeV)。 • MK5—N+版,确定所有的N+区域

(4)通过掩模版MASK对光刻胶曝光 正胶被 UV曝光的部分分解, 影被 掉显 。 负胶曝光部分聚合 ,硬 不化 被显影掉。

整理课件

(5)刻有源区。 掩模版掩蔽区域下未被曝光的光刻胶 被显影液洗掉;再将下面的SiO2用HF 刻蚀掉,露出硅片表面。

(6)淀积多晶硅 除净曝光区残留的光刻胶(丙酮), 在整个硅片上生长一层高质量的SiO2 (约1000Å),即栅氧,然后再淀积 多晶硅(12m)。

CMOS模拟集成电路版图设计课程大纲

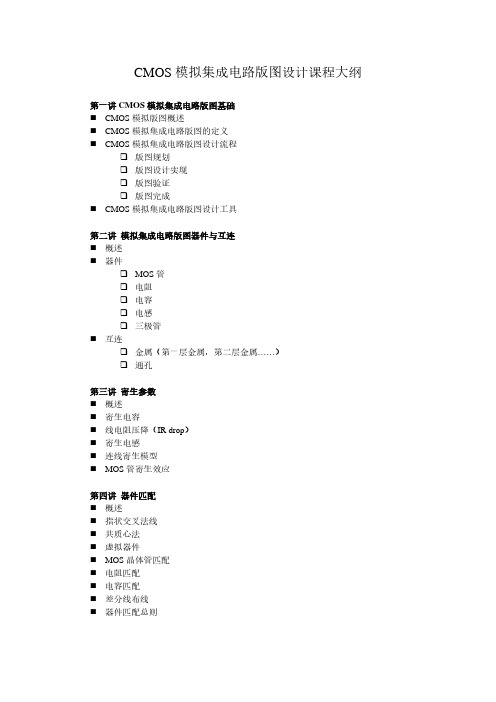

CMOS模拟集成电路版图设计课程大纲第一讲CMOS模拟集成电路版图基础⏹CMOS模拟版图概述⏹CMOS模拟集成电路版图的定义⏹CMOS模拟集成电路版图设计流程❑版图规划❑版图设计实现❑版图验证❑版图完成⏹CMOS模拟集成电路版图设计工具第二讲模拟集成电路版图器件与互连⏹概述⏹器件❑MOS管❑电阻❑电容❑电感❑三极管⏹互连❑金属(第一层金属,第二层金属……)❑通孔第三讲寄生参数⏹概述⏹寄生电容⏹线电阻压降(IR drop)⏹寄生电感⏹连线寄生模型⏹MOS管寄生效应第四讲器件匹配⏹概述⏹指状交叉法线⏹共质心法⏹虚拟器件⏹MOS晶体管匹配⏹电阻匹配⏹电容匹配⏹差分线布线⏹器件匹配总则第五讲设计规则⏹概述⏹工艺库中各类器件的层信息⏹设计规则细则⏹工业标准的基本数据格式第六讲验证⏹设计规则检查(DRC)Design Rule Check⏹版图与电路图的对照(LVS)Layout Versus Schematic⏹电气规则检查(ERC)Electrical Rule Check⏹天线规则检查(ANT)⏹静电放电检查(ESD)第七讲可靠性设计⏹天线效应⏹闩锁效应⏹静电放电保护(Electro-Static Discharge ,ESD)⏹数模混合集成电路版图设计第八讲工艺设计工具包(PDK)⏹ 1.PDK名称的涵义⏹ 2.PDK中包含的内容● 2.1 IO lib2.1.1 GDS文件的导入操作2.1.2 网表导入2.1.3 IO使用文档介绍● 2.2 SMIC_13_PDK_v2.6_20142.2.1 Smic13mmrf_1233文件夹2.2.2 model 文件夹2.2.3 Calibre 文件夹● 2.3 SMIC_13_TF_LG_LIST_2014122.3.1 Standard cell Timing lib2.3.2 Calview.cellmap2.3.3 Standard cell netlist及网表导入操作2.3.4 Ant rule (天线规则)第九讲Cadence spectre概述与操作界面⏹Cadence spectre 概述⏹Cadence spectre的特点⏹Cadence spectre的仿真设计方法⏹Cadence spectre与其他EDA软件的连接⏹Cadence spectre的基本操作第十讲Spectre窗口和库元件⏹模拟设计环境(Analog Design Environment)⏹波形显示窗口(Waveform)⏹波形计算器(Waveform Calculator)⏹Spectre库中的基本器件第十讲Cadence Virtuoso版图设计工具⏹Cadence Virtuoso概述⏹Virtuoso 界面介绍⏹Virtuoso 基本操作第十一讲Mentor Calibre版图验证工具⏹Mentor Calibre版图验证工具概述⏹Mentor Calibre版图验证工具调用⏹Mentor Calibre DRC验证⏹Mentor Calibre LVS验证⏹Mentor Calibre寄生参数提取(PEX)第十二讲版图设计与验证流程实例⏹设计环境准备⏹反相器链电路的建立和前仿真⏹反相器链版图设计⏹反相器链版图验证与参数提取⏹反相器链电路后仿真⏹输入输出单元环设计⏹主体电路版图与输入输出单元环的连接⏹导出GDSII文件。

详细的集成电路版图基础介绍-CMOS版图

(4)最小延伸 例如,多晶栅极

须延伸到有源区 外一定长度。

在符合设计规则的前 提下, 争取最小的版图面积

5、阱与衬底连接

通常将PMOS管的衬底接高电位(正压); NMOS管的衬底接低电位(负压),以保 证电路正常工作

衬底材料导电性较差,为了保证接触的效 果,需要在接触区域制作一个同有源区类 似的掺杂区域降低接触电阻,形成接触区。

大面积的栅极与衬底之间有氧化 层隔绝,形成平板电容

栅电压降低

细长的C W LC0

MOS管栅极串联电阻值

R W / L R

S G

D

设计方法 (1)分段──

大尺寸MOS管分段成若干小尺寸MOS管。

(a) MOS管的W/L=200/1

CMOS集成电路版图基础

定义版图

什么是版图? 集成电路制造工艺中,通过光刻和刻蚀将

掩膜版上的图形转移到硅片上。这种制造 集成电路时使用的掩膜版上的几何图形定 义为集成电路的版图。 版图要求与对应电路严格匹配,具有完全 相同的器件、端口、连线

一、单个MOS管的版图实现

栅极负责施加控制电压 源极、漏极负 责电流的流进 流出

MOS器件版图图层 ——NMOS

N型注入掩模——NSELECT 有源扩散区——ACTIVE 多晶硅栅——POLY 引线孔——CC 金属一——METAL1 通孔一——VIA 金属二——METAL2

结构图 立体结构和俯视图

多晶硅栅(POLY)

金属一(METAL1)

引线孔(CC)

N型注入掩模 (NSELECT)

a)由源、栅和漏组成的器件;

b)衬底连接。

源区、沟道区和漏区合称为MOS管的 有源区(Active),有源区之外的区域 定义为场区(Fox)。有源区和场区之 和就是整个芯片表面即基片衬底 (SUB)。

CMOS版图

焊盘提供了芯片内部信号到封装接脚的 连接,其尺寸通常定义为绑定导线需要的 最小尺寸。

第4章 CMOS版图

版图设计注意事项

1、无论在电路图中还是在版图中,PMOS晶体管都与VDD相连 接; 2、在电路图和版图中,NMOS晶体管都与VSS相连接;

3、在电路图和版图中,NMOS晶体管和PMOS晶体管的栅极有 相同的IN信号,而其漏极有相同的OUT信号;

可以进行全自动版图设计的EDA工具主要有 Cadence公司的SE、Synopsys的Apollo 等。

第4章 CMOS版图

2.半自动设计

版图的半自动设计是指在计算机上利用 符号进行版图输入,符号代表不同层版的 版图信息,然后通过自动转换程序将符号 转换成版图。

第4章 CMOS版图

3.人工设计

版图的人工设计主要应用在模拟集成电路的 版图设计、版图单元库文件的建立和全定制数字 集成电路设计中。模拟集成电路因其复杂而无规 则的电路形式(相对于数字电路而言),故在技术 上只适宜于采用全定制的人工设计方法;

第4章 CMOS版图

➢版图设计的流程是由设计方法决定的。版图设计 方法可以从不同的角度进行分类,如果按照自动化 程度,大致可分为三类:全自动设计、半自动设计 和手工设计。

版图设计的一般流程: 1、把整个电路划分成若干个模块; 2、对版图进行规划,确定各个模块在芯片中的具体 位置;完成各个模块的版图及模块之间的互连; 3、对版图进行验证。

➢在这种设计方法下,计算机只作为绘图与规则验证 工具而起辅助作用,对所设计的版图的每一部分, 设计者都要进行反复的比较、权衡、调整和修改, 要求得到最佳尺寸的元器件、最合理的版图布局和 路径最短的互连线等。

➢人工设计在获得最佳芯片性能的同时,也因为芯片 面积最小而大大降低了每个芯片的生产成本,但其 设计周期要比自动和半自动设计方法长。

集成电路课程设计--cmos反相器的电路设计及版图设计

目录摘要 (3)绪论 (5)1软件介绍及电路原理 (6)1.1软件介绍 (6)1.2电路原理 (6)2原理图绘制 (8)3电路仿真 (10)3.1瞬态仿真 (10)3.2直流仿真 (11)4版图设计及验证 (12)4.1绘制反相器版图的前期设置 (12)4.2绘制反相器版图 (13)4.3 DRC验证 (15)结束语 (17)参考文献 (18)摘要CMOS技术自身的巨大发展潜力是IC高速持续发展的基础。

集成电路制造水平发展到深亚微米工艺阶段,CMOS的低功耗、高速度和高集成度得到了充分的体现。

本文将简单的介绍基于ORCAD和L-EDIT的CMOS反相器的电路仿真和版图设计,通过CMOS反相器的电路设计及版图设计过程,我们将了解并熟悉集成电路CAD的一种基本方法和操作过程。

关键词:CMOS反相器ORCAD L-EDIT版图设计AbstractThe huge development potential of CMOS technology itself is the foundation of sustainable development of IC high speed. The manufacturing level of development of the integrated circuit to the deep sub micron technology, CMOS low power consumption, high speed and high integration have been fully reflected. In this paper, the circuit simulation and layout design of ORCAD and L-EDIT CMOS inverter based on simple introduction, through the circuit design and layout design process of CMOS inverter, we will understand and a basic method and operation process, familiar with IC CAD.Keywords: CMOS inverter layout ORCAD L-EDIT绪论20世纪是IC迅速发展的时代。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

② 直线形排列的NMOS管

结构图

立体结构和俯视图

③ 源区、沟道区和漏区合称为MOS管的有源区(Active),而有源区之外的区域 定义为场区(Fox)。有源区和场区之和就是整个芯片表面。 Fox + Active = Surface

芯片表面包含有源区和场区两部分

④ N阱CMOS集成电路使用P型衬底,NMOS管直接制作在P型衬底上,PMOS 管做在N阱内。

从库管理器建立新库的另一种方法

(6) 建立新文件:在库管理器,选命令File→New→Cell view…。在Create New File框 内输入库名和单元名(inv)后,先将tool选为virtuoso,在View Name的文本区会自动 生成Layout,点击Ok按钮,将同时出现版图编辑窗(virtuoso Layout Editing)和 层选择窗(LSW:Layer Select window)。

AS and NS buttons

Layers Scroll bar

层选择窗 (LSW )

1) Edit(编辑)——是个下拉式命令菜单,有六个子菜单

2) 层符号——分三部分,① 左表示层的颜色及图案;② 中为层名;③ 右表 示层的用途。

层名 层的颜色及图案 层的用途

3) Inst——设置Instance为可选或不可选。 4) Pin——设置布线工具。 5)Technology file——技术文件名。 6) AV和NV按钮 ① AV设置各层都可视(图a); ② 除输入层外,NV设置其余各层不可视(层符号变灰)(图b); ③ 击鼠标中键使各层在可视和不可视间转换(图c); ④ 层原为可视,点击中键变为不可视,再点击又恢复可视(图d); ⑤ 鼠标左键点击原不可视的层就变为可视,且成为输入层(图e)。

1. 建立新库步骤 (1) 从CIW进入库管理器,选命令Tools→Library Manager…。

(2) 在库管理器中选命令File→New→Library…,出现新库对话框。

进入库管理器

选建立新库命令

新库对话框

(3) 在Name 文本区输入新库名(例如mylib)。点击OK按钮,出现新库技术文件 对话框,新库mylib的技术文件有三种选项。

(a) 点击左键

(b) 移动鼠标

(c) 点击左键建立矩形

(d) 完成的矩形

4)按<Esc>键停止画矩形命令。 2. 多边形(polygon) (1)方法1 ① 建立多边形命令:Create→polygon。 ② 选输入层。 ③ 画多边形。

(a) 点击第一点

(b) 继续点击

(c) 双击或按<Enter>键使多边形封闭

在ASCII Technology File区输入技术文件名

报告技术文件加载成功

(5) 方法2:选“Attach to an existing techfile”,出现Attach Design Library to Technology File对话框。在Technology Library文本区下拉菜单中选择技术库,例如 csmc15tech,按OK按钮即完成建库。 若新库名为abcd,建库完成后在CIW中显示: Design Libraryˋabcdˊsuccessfully attached to technology Library ˋcsms15techˊ 新库abcd已成功建立。

⑤ 完整的MOS管版版图必须包含两个部分:a)由源、栅和漏组成的器件;b) 衬底连接。

(a)PMOS管 完整的MOS管版图图形

(b)NMOS管

5.1.2 MOS管阵列的版图实现

1.MOS管串联 (1) 两个MOS管的串联。 N1的源、漏区为X和Y,N0的源、漏区为Y和Z。Y是它们的公共区域,如 果把公共区域合并,得到图5.7(d)所示的两个MOS管串联连接的版图。 从电流的方向可以决定,当MOS管串联时,它们的电极按S-D-S-D-S-D方 式连接。

(c) 点击边框对角顶点

(d) 完成的椭圆

(3)圆环(Donut)——命令:Create→conics→Donut

(a) 点击圆心

(b) 点击内圆周

(c) 点击外圆周

Display Options 对话框

(2) Grid Controls 4个参数的缺省设置为1、5、0.5和0.5。对于1μm或者亚微米的设计规则,可设 置为0.1、0.5、0.01和0.01。

(3) Snap Modes 在下拉菜单中包含了各种选项。

Creat的模式

Edit的模式

2. 编辑器选项 选命令Option→layout Editor…<E>,=>“layout Editor Options”对话 框 。可以设置Gravity Controls(引力控制)、Conic sides(圆环边数)…等。

(a) 电路图

(b) N1版图

(c) N0版图

(d) N1和N0串联版图

(2) 任意个MOS管串联。例如3个MOS管串联的版图。

(a)电路图

(b) 版图

2.MOS管并联(并联是指它们的源和源连接,漏和漏连接,各自的栅还是独立的。) (1)栅极水平放置,节点X和Y可用金属连线连接(图b);也可用有源区连接(图c)。

⑤ 按Ok存盘。

(2) 设置层符号的颜色和图案 ① 在LSW中,选Edit→Display Resource Editor…,=>“Display Resource Editor”对话框。

Display Resource Editor对话框

② 设置层的填充类型(Fill sytle)、填充颜色(Fill color)、外框颜色(Outline Color)、点画(Stipple)和线型(line sytle)。 ③ 按Apply按钮。 ④ 选File→Save…,=>“Save Display Resource File”框。 ⑤ 在Files区点击左键,=>/root/display.drf, 左键点击,使它进入Selection的文本框, 点击Ok关闭。 ⑥ 对话框报告root/display.drf文件已经存在,按Yes键。

建立新文件

同时出现版图编辑窗和层选择窗(LSW)

5.3.2 层选择窗(LSW)的设置

1. 对LSW的说明

Edit menu Technology file Inst button AV and NV buttons Current drawing or entry layer Pin button

(d) 完成的多边形

(2)方法2

(3)加圆弧 ① 命令Create→polygon把多边形某一边画成圆弧。 ② 双击鼠标中键或按<F3>键,出=>reate Polygon选项框。 ③ 在框中点击Create Arc按钮。 ④ 在多边形中画圆弧。

(a)矩形拼接或重叠形成多边形

(b)合并后的多边形

(a) 点击起点 (b) 点击终点

(b) 完成的等宽线

4. 圆锥曲线 (1)圆(circle) ——命令:Create→conics→circle

(a) 点击圆心

(b) 移动鼠标

(c) 在圆周上点击画圆

(d) 完成的圆

(2)椭圆(Ellipse)——命令:Create→conics→Ellipse

(a) 点击边框第一角顶点

(b) 移动鼠标

第5章 CMOS集成电路的版图 设计

主要内容 5.1 MOS 场效应管的版图实现 5.2 版图设计规则 5.3 版图系统的设置 5.4 版图的建立 5.5 版图的编辑 5.6 棍棒图 5.7 版图设计方法概述

5.1 MOS 场效应管的版图实现

5.1.1 单个MOS管的版图实现

1. MOS管的结构和布局

建立显示文件

按Yes键得到新的显示文件

5.3.3 版图编辑窗的设置

版图编辑窗

1. 图标栏(Icon Menu)

图标栏包含的命令

2. 状态栏(Status Banner) 位于版图编辑窗的第二行。 3. 菜单栏(Menu Banner) 位于版图编辑窗第三行。 4. 启动命令和取消命令的方法 (1) 启动命令 ① 从版图窗的菜单栏选命令。 ② 点击版图窗的图标。 ③ 用快捷键。 (2) 取消命令 ① 按<Esc>键。 ② 点击对话框中的Cancel。 (3) 命令的对话框 有两种对话框: 1) 标准框。启动命令时自动出现。

(a)

(b)

(c)

(d)

(e)

7) AS和NS设置各层的选择性(后面介绍)。

2. 对LSW的设置

(1) 设置层符号。

① 在LSW中,选择Edit→Set Valid Layers…=>Set Valid Layer对话框。

Set Valid Layer对话框

② 点击层符号右边的选择开关,开关变黑,本层被选。 ③ 点击Apply按钮,层符号出现在LSW中。 ④ 点击LSW的Edit→Save,=>Save对话框。

(1)选命令window→Pan<Tab>,版图窗和CIW都显示: Point at center of the desired display:(希望显示的中点) 用鼠标左键点击屏幕右上角某一点,该点立即移到屏幕中心,第一象限成为画图区。 (2)用键盘上方向键实现坐标轴移动。

5.4.3建立几何图形 1. 矩形(Rectangle) 1)建立矩形命令:Create→Rectangle。 2)选输入层。 3)画矩形。

2) 选项框。

3) 显示对话框的方法: ① 若菜单命令后有三点,标准框会自动出现; ② 使用命令时双击中键或按<F3>键。

Move的选项对话框

5.3.4 使用Option菜单进行版图编辑窗设置

1. 显示命令 选命令Option→Display…<e>,=>“Display Options”对话框 。 (1) Display Controls