VHDL中数组的定义和使用

vhdl type用法 -回复

vhdl type用法-回复题目:VHDL type 用法:深入了解VHDL设计语言核心类型引言:VHDL(VHSIC Hardware Description Language)作为一种硬件描述语言,被广泛应用于数字电路设计和嵌入式系统开发中。

在VHDL中,type(类型)扮演着非常关键的角色。

理解VHDL type 的用法和特性对于设计和开发硬件系统至关重要。

本文将深入探讨VHDL type的基本概念和使用方法,帮助读者全面了解VHDL设计语言。

第一部分:VHDL基本类型简介VHDL类型分为标量(scalar)、复合(composite)和文件(file)类型,其中标量类型包括整型(integer)、实型(real)、位型(bit)、布尔型(boolean)、字符型(character)等。

复合类型包括数组型(array)和记录型(record)。

文件类型用于读写外部文件。

第二部分:标量类型的使用标量类型在VHDL设计中起到了基础类型的作用,它们是数字系统中最常用的类型。

以整型为例,介绍了如何声明、赋值和操作整型变量。

实型的使用也会在这一部分进行讨论,包括定点数和浮点数的处理。

第三部分:复合类型的使用复合类型是由标量类型组合而成的更复杂的类型。

数组类型是其中的一种常见形式。

我们将详细研究如何声明、初始化和操作数组类型的变量。

此外,记录型的定义和使用也将深入探讨。

第四部分:文件类型的使用文件类型可用于读取和写入外部文件,实现与外部环境的数据交互。

在这一部分中,我们将介绍如何声明文件类型的变量,并演示读取和写入操作。

第五部分:VHDL type的特性除了基本的类型定义和使用,VHDL提供了一些高级特性来增强类型的灵活性和可靠性。

在这一部分中,我们将讨论泛型(generic)类型和用户自定义类型的使用方法,并说明如何通过使用类型转换函数进行类型转换。

第六部分:VHDL type的应用示例为了更好地理解VHDL type 的使用,我们将以一个基于FIR滤波器的数字信号处理系统作为示例。

vhdl array用法

vhdl array用法VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和仿真。

在VHDL 中,数组(array)是一种非常常用的数据结构,它允许在单个信号名称下存储多个值。

这篇文章将详细介绍VHDL中的数组用法,重点关注中括号的使用,并逐步回答相关问题。

1. 什么是VHDL中的数组?数组是一种用于存储多个值的数据结构。

在VHDL中,数组可以是一维、二维或多维的,并且可以包含指定数量的元素。

2. 如何声明一个一维数组?在VHDL中,可以使用以下语法声明一个一维数组:type array_name is array (range) of element_type;其中,`array_name`是数组名称,`range`是数组的范围,可以是确定的或变量的,而`element_type`是数组元素的数据类型。

3. 如何声明一个二维数组?声明一个二维数组的语法如下:type array_name is array (range1) of element_type_1;type array2d_name is array (range2) of array_name;其中,`range1`和`range2`是数组的范围,`element_type_1`是数组元素的数据类型。

4. 如何初始化数组的元素?可以使用以下方式初始化数组的元素:array_name := (value1, value2, value3, ...);其中,`array_name`是数组名称,`value1`、`value2`等是要初始化的元素值。

5. 如何访问数组的元素?可以使用以下方式访问数组的元素:array_name(index);其中,`array_name`是数组名称,`index`是要访问的元素的索引。

VHDL中数组的定义和使用

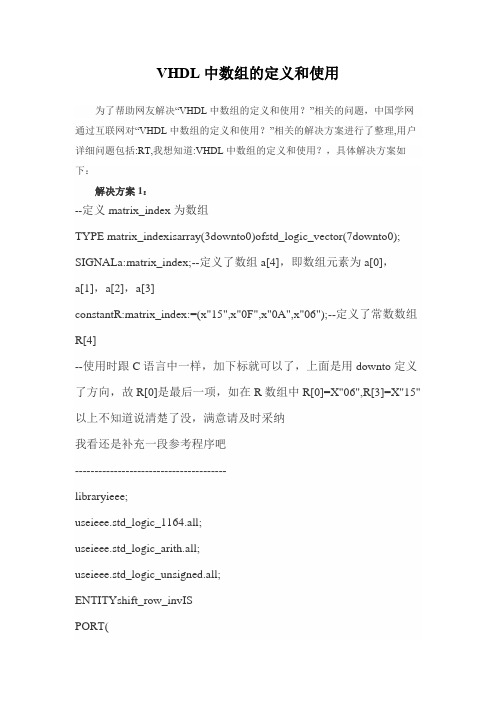

VHDL中数组的定义和使用为了帮助网友解决“VHDL中数组的定义和使用?”相关的问题,中国学网通过互联网对“VHDL中数组的定义和使用?”相关的解决方案进行了整理,用户详细问题包括:RT,我想知道:VHDL中数组的定义和使用?,具体解决方案如下:解决方案1:--定义matrix_index为数组TYPEmatrix_indexisarray(3downto0)ofstd_logic_vector(7downto0); SIGNALa:matrix_index;--定义了数组a[4],即数组元素为a[0],a[1],a[2],a[3]constantR:matrix_index:=(x"15",x"0F",x"0A",x"06");--定义了常数数组R[4]--使用时跟C语言中一样,加下标就可以了,上面是用downto定义了方向,故R[0]是最后一项,如在R数组中R[0]=X"06",R[3]=X"15" 以上不知道说清楚了没,满意请及时采纳我看还是补充一段参考程序吧---------------------------------------libraryieee;useieee.std_logic_1164.all;useieee.std_logic_arith.all;useieee.std_logic_unsigned.all;ENTITYshift_row_invISPORT(shiftrow_in:INSTD_LOGIC_VECTOR(127DOWNTO0);shiftrow_out:OUTSTD_LOGIC_VECTOR(127DOWNTO0));ENDshift_row_inv;ARCHITECTUREbehOFshift_row_invIS--typedescribingthebytearrayconsistingof16bytematrixarray TYPEmatrix_indexisarray(15downto0)ofstd_logic_vector(7downto0); SIGNALb,c:matrix_index;BEGIN--initialmappingofinputintoabytematrixarraynamedbmatrix_mapping:PROCESS(shiftrow_in)BEGINFORiIN15DOWNTO0LOOPb(15-i)<=shiftrow_in(8*i+7DOWNTO8*i);ENDLOOP;ENDPROCESSmatrix_mapping;--shiftrowtransformation--b(i)-->c(i)----|04812||04812|(noshift)--|15913|==>|13159|(1rightshift)--|261014||101426|(2rightshift) --|371115||711153|(3rightshift)--shiftedfirstcolumnc(0)<=b(0);c(1)<=b(13);c(2)<=b(10);c(3)<=b(7);--shiftedsecondcolumnc(4)<=b(4);c(5)<=b(1);c(6)<=b(14);c(7)<=b(11);--shfitedthirdcolumnc(8)<=b(8);c(9)<=b(5);c(10)<=b(2);c(11)<=b(15);--shiftedforthcolumnc(12)<=b(12);c(13)<=b(9);c(14)<=b(6);c(15)<=b(3);--mappingtemporarycvectorintoshiftedrowoutput matrix_mapping_back:PROCESS(c)BEGINFORiIN15DOWNTO0LOOPshiftrow_out(8*i+7DOWNTO8*i)<=c(15-i); ENDLOOP;ENDPROCESSmatrix_mapping_back; ENDbeh;。

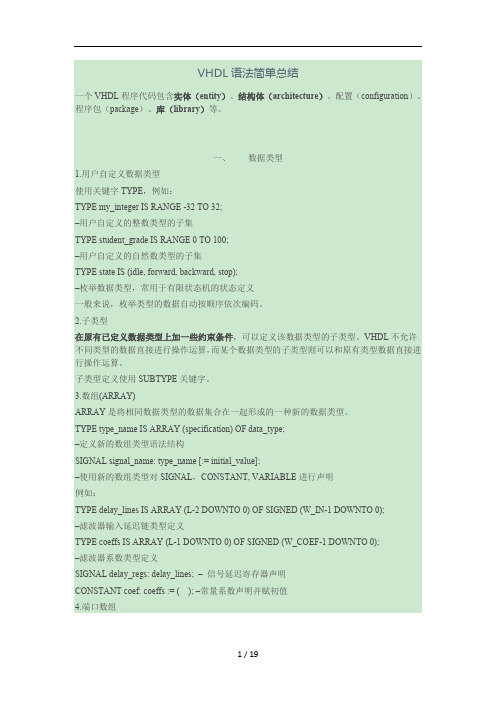

VHDL语法简单总结

VHDL语法简单总结一个VHDL程序代码包含实体(entity)、结构体(architecture)、配置(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型上加一些约束条件,可以定义该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型语法结构SIGNAL signal_name: type_name [:= initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数类型定义SIGNAL delay_regs: delay_lines; –信号延迟寄存器声明CONSTANT coef: coeffs := ( ); –常量系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

verilog 中数组定义

verilog 中数组定义【最新版】目录1.Verilog 简介2.Verilog 中数组的定义方法3.Verilog 中数组的访问方式4.Verilog 中数组的应用实例正文【1.Verilog 简介】Verilog 是一种硬件描述语言,主要用于数字系统硬件的描述和验证。

它被广泛应用于数字集成电路设计、FPGA 设计和 ASIC 设计等领域。

Verilog 具有简洁、易学的语法特点,是数字电路设计工程师必备的技能之一。

【2.Verilog 中数组的定义方法】在 Verilog 中,数组是一种数据类型,可以用来存储一组相同类型的数据。

数组的定义方法有两种:声明和实例化。

(1)声明:使用`array`关键字来声明一个数组,其语法如下:```array[i] <数据类型> <数组名>(<数组长度>);```其中,`<数据类型>`表示数组元素的数据类型,`<数组名>`表示数组的名称,`<数组长度>`表示数组的长度,`i`表示数组的下标。

例如,声明一个长度为 4 的整型数组,其语法如下:integer array[3] my_array(4);```(2)实例化:在声明数组后,需要实例化数组以分配存储空间。

实例化的方法有两种:使用循环和使用`generate`语句。

(a)使用循环:```integer i;for(i=0; i<4; i=i+1)my_array[i] = i;```(b)使用`generate`语句:```integer genvar i;generatefor(i=0; i<4; i=i+1)my_array[i] = i;endgenerate```【3.Verilog 中数组的访问方式】在 Verilog 中,可以使用下标访问数组元素。

数组下标从 0 开始,最大下标小于数组长度。

例如,访问上面声明的数组的第一个元素,其语法如下:my_array[0]```【4.Verilog 中数组的应用实例】假设我们需要设计一个 4 位加法器的 Verilog 模块,该模块的输入是两个 4 位二进制数 A 和 B,输出是它们的和 C。

VHDL语言详解

概述(4/4)

VHDL vs. Verilog HDL

USA—IBM,TI,AT&T,INTEL…VHDL; USA—Silicon Valley…Verilog; Europe—VHDL; Japan—Verilog; Korea—70-80%VHDL;

VHDL的一些基本概念

基本概念(1/7)

操作数的类型应该和运算操作符所要求并置一维数组整数和实数包括浮点数整数和实数包括浮点数mod整数rem整数sll逻辑左移bit或布尔型一维数组srl逻辑右移bit或布尔型一维数组sla算术左移bit或布尔型一维数组sra算术右移bit或布尔型一维数组rol逻辑循环左移bit或布尔型一维数组ror逻辑循环右移bit或布尔型一维数组乘方整数算术操作符abs取绝对值整数vhdl语言的运算操作符2等于任何数据类型不等于任何数据类型小于枚举与整数类型及对应的一维数组大于枚举与整数类型及对应的一维数组小于等于枚举与整数类型及对应的一维数组关系操作符大于等于枚举与整数类型及对应的一维数组bitbooleanstdlogibitbooleanstdlogibitbooleanstdlogibitbooleanstdlogibitbooleanstdlogibitbooleanstdlogibitbooleanstdlogi整数符号操作符整数vhdl语言的运算操作符3运算符优先级xnor最低优先级vhdlvhdl语言的运算操作符4norxorstdlogicvector1downtostdlogicsignalnandjnandbooleansignalstdlogicvector1downtostdlogicsignalbooleanvhdl语言的运算操作符5主要用于位和位矢量的连接

两个进程语句并行执行

VHDL语言的基本语法解析

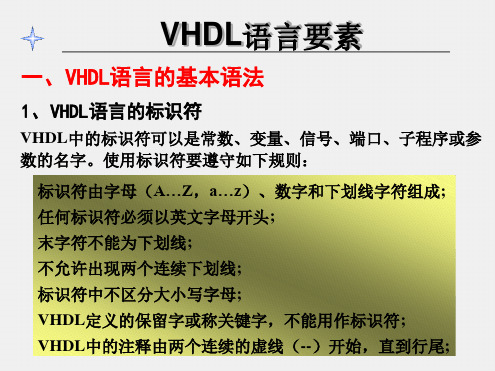

VHDL语言要素

一、VHDL语言的基本语法

1、VHDL语言的标识符

VHDL中的标识符可以是常数、变量、信号、端口、子程序或参 数的名字。使用标识符要遵守如下规则:

信号与变量的区别

(1)声明的形式与位置不同 信号 signal count : std_logic_vector(7 downto 0); 变量 variable tema:std_logic_vector(3 downto 0); 信号在结构体中声明;变量在进程中声明

(2)赋值符不同 count<=“00000000”, count<=“ZZZZZZZZ” count<=tema; tema:=0000;

2、变量( Variable )

变量是一个局部变量,它只能在进程语句、函数语句和过程 语句结构中使用,用作局部数据存储。变量常用在实现某种算 法的赋值语句中。

一般格式:

VARIABLE 变量名:数据类型 约束条件:= 表达式;

例: VARIABLE x, y: INTEGER;

--定义x,y为整数变量

(3)赋值生效的时间不同 信号:进程结束时 变量:立即生效

(4)进程对信号敏感,对变量不敏感

(5)作用域不同 信号可以是多个进程的全局信号, 变量只在定义后的顺序域可见

三、VHDL语言的数据类型 ? VHDL中的数据类型可以分成四大类。

标量型(Scalar Type) 复合类型(Composite Type)

1) 布尔(BOOLEAN)数据类型

verilog 中数组定义

verilog 中数组定义Verilog中数组定义定义•数组是Verilog中一种非常常用的数据结构,可以用于存储多个相同类型的数据元素。

•数组定义的一般形式是:data_typearray_name[array_size];•data_type指定数组中元素的类型,可以是任何有效的数据类型,比如整数类型,浮点类型等。

•array_name是数组的名称,用于在代码中引用该数组。

•array_size指定数组的大小,即数组中元素的个数。

理由1.组织数据:使用数组可以方便地组织和访问大量相关的数据。

比如在Verilog代码中,我们可以使用数组来存储一组输入信号或者一组状态变量。

2.简化代码:使用数组可以简化代码,减少重复的代码量。

通过定义一个数组,我们可以使用循环结构来处理数组中的每个元素,从而避免写多个类似的代码。

3.提高可读性:使用数组可以提高代码的可读性。

当我们在代码中看到一个数组时,就会明确知道这是一组相关的数据,而不需要通过多个单独的变量去描述和管理这些数据。

相关书籍1. “Verilog HDL: A Guide to Digital Design and Synthesis” by Samir Palnitkar该书是一本经典的Verilog教材,适用于初学者和有经验的设计工程师。

书中详细介绍了Verilog的语法和应用,包括数组的定义和使用。

作者通过实例和练习来帮助读者掌握Verilog的各个方面。

2. “Advanced Digital Design with the Verilog HDL” by Michael D. Ciletti这本书是一本高级Verilog指南,适用于那些已经熟悉Verilog 基础知识的人。

其中包含了关于数组的深入讨论,介绍了更高级的数组使用技巧和设计方法。

书中还包含了丰富的实例和练习,帮助读者深入理解Verilog中数组的应用。

3. “Verilog Digital System Design: Register Transfer Level Synthesis, Testbench, and Verification” by Zainalabedin Navabi这本书主要关注Verilog的应用和综合,对于那些想要将Verilog代码映射到硬件的设计工程师非常有用。

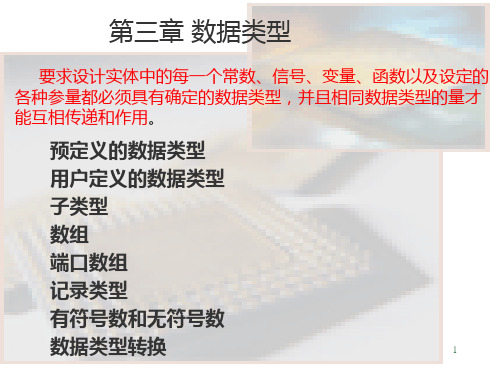

VHDL数字电路设计教程第3讲 数据类型

7)自然数(natural)和正整数(positive)

natural是integer的子类型,表示非负整数。 positive是integer的子类型,表示正整数。

定义如下:

subtype natural is integer range 0 to integer’high; subtype positive is integer range 1 to integer’high;

bit_vector(0 to 15);

SUBTYPE语句格式:

subtype 子类型名 is 基本数据类型 约束范围; 例: subtype digits is integer range 0 to 9;

由subtype 语句定义的数据类型称为子类型。

22

3.4 数组(ARRAY)

数组是将相同数据类型的数据集合在一起形成 的一种新的数据类型。可以是1D、2D或1D*1D,更高 维数的数组往往是不可综合(即综合库中没有直接 可以调用的器件)的。 数组的结构:

20

3.3 子类型

子类型是已定义的类型或子类型的一个子集。 格式: subtype 子类型名 is 数据类型名[范围]; 例: bit_vector 类型定义如下:

type bit_vector is array (natural range <>) of bit;

如设计中只用16bit;可定义子类型如下: subtype my_vector is 注:子类型与基(父)类型具有相同的操作符和子 程序。可以直接进行赋值操作。 21

9

6)整数(integer)

integer 表示所有正的和负的整数。硬件实现时, 利用32位的位矢量来表示。可实现的整数范围为: -(231-1) to (231-1)

vivado数组调用

vivado数组调用Vivado是Xilinx公司的一款集成开发环境(IDE),用于FPGA设计和开发。

在Vivado中,数组的调用通常是指在硬件描述语言(如Verilog或VHDL)中对数组进行操作或访问。

下面我将从多个角度对Vivado中数组调用进行详细解释。

1. 数组定义,在Vivado中,可以使用硬件描述语言(HDL)来定义数组。

在Verilog中,可以使用类似于`wire [7:0] my_array [0:3];`的语法来定义一个8位宽、4个元素的数组。

在VHDL中,可以使用类似于`type my_array is array(0 to 3) ofstd_logic_vector(7 downto 0);`的语法来定义相同类型的数组。

2. 数组初始化,在Vivado中,可以使用初始化列表来初始化数组。

例如,在Verilog中,可以使用`reg [7:0] my_array [0:3] = '{8'h01, 8'h02, 8'h03, 8'h04};`来初始化一个包含四个元素的数组。

在VHDL中,可以使用`my_array <= (8 => "00000001", 9 => "00000010", 10 => "00000011", 11 => "00000100");`来完成相同的初始化操作。

3. 数组访问,在Vivado中,可以使用数组下标来访问数组元素。

例如,在Verilog中,可以使用`my_array[2]`来访问数组`my_array`的第三个元素。

在VHDL中,可以使用`my_array(2)`来完成相同的操作。

4. 数组操作,在Vivado中,可以对数组进行各种操作,如遍历、排序、查找等。

这些操作可以通过硬件描述语言中的循环、条件语句和其他逻辑来实现。

VHDL基本语法

一、数据类型A. 标准数据类型1)整数类型(INTEGER)VARIBLE A:INTEGER RANGE -128 TO 128范围-(231-1)~ +(231-1)2#11111111# --binary,=255D8#377#16#FF#2)实数类型和浮点类型(REAL & FLOATING)实数范围-1.0E+38 ~ +1.0E+38大多数EDA工具不支持浮点类型16#0F#E+016#FF.FF#E-13)位类型(BIT)TYPE BITIS(‘0',‘1')4)位矢量类型(BIT_VECTOR)位矢量(bit_vector)类型实际上就是位(bit)的一位数组,它的表示方法是用双引号将一组位数据括起来。

例如:"11010111"。

不难看出,采用位矢量可以很方便地表示电路描述中的总线状态,这在VHDL程序中经常用到。

B"1111-1100" --长度为8X"FBC" --长度为12,=B"1111-1011-1100"O"371" --长度为9,=B"011-111-001"5)布尔类型(BOOLEAN)6)字符类型(CHARACTER)‘A',‘a',‘B',大小写不敏感。

7)字符串类型(TRING)"VHDL","MULTI_SCREEN"8)物理类型(physical)--时间类型--The physics unit time is a predefined typeTYPE time IS RANGE -1E18 TO 1E18UNITSfs; -- Femto-secondps = 1000 fs;ns = 1000 ps;us = 1000 ns;ms = 1000 us;sec = 1000ms;min = 60 sec;END UNITS--another--DISTANCE TYPETYPE distance IS RANGE 0 TO 1E16UNITSA;nm = 10A;um = 1000nm;mm = 1000um;cm = 10mm;m = 1000 mm;km = 1000m;END UNITS;9)错误类型(NOTE,WARNING,ERROR,FAILURE)10)自然数、正整数类型(NATURAL & POSITIVE)ENTITY_compare ISPORT(a,b:INTEGER RANGE 0 to 9:=0;c:out Boolean);END compare;B. 自定义数据类型1)枚举类型(ENUMERATED)TYPE PCI_BUSstate IS(Idle,busbusy,write,read,Back off); --PCI总线状态机变量TYPEstd_ulogic IS('U',‘X',‘1',‘0',‘Z',‘W',‘L',‘H',‘-‘);TYPE boolean IS(false,true);TYPE BITIS(‘0',‘1');2)整数类型(INTEGER)TYPE digit IS INTEGER RANGE -128 TO 1283)实数类型和浮点类型(REAL & FLOATING)4)数组类型(ARRAY)TYPE MYARRAY IS ARRAY(INTEGER 0 TO 9)OFstd_LOGIC5)存取类型(ACCESS)TYPE line IS ACCESS string; --Line是指向字符串的指针6)文件类型(FILES)TYPE text IS FILE OF string;TYPE input-type IS FILE OF character;7)记录类型(RECODE)--RECORD适于描写总线,通讯协议TYPE PCI_BUS IS RECORDADDR:std_LOCIG_VECTOR(31 DOWNTO 0);DATA:std_LOGIC_VECTOR(31 DOWNTO 0);END RECORD;SEGINAL DECODE1,DECODE2:PCI_BUS;PCI_DEVICE1 <= DECODE1.ADDR;PCI_DEVICE1RAM <= DECODE1.DATA;8)时间类型(TIME)9)VHDLstd_logic在VHDL中,设计人员经常使用的数据类型是枚举类型std_ulogic和它的子类型std_logic,它们都是一个九值逻辑系统。

VHDL 数据类型

数据类型

标量型(Scalar Type): 包括实数类型、整数类型、枚举类型、时间类型。

复合类型(Composite Type): 可以由小的数据类型复合而成,如可由标量型复合而成。复合

类型主要有数组型(Array)和记录型(Record)。

存取类型(Access Type): 为给定的数据类型的数据对象提供存取方式。

else CONV_STD_LOGIC_VECTOR(b3,4); --(2)

d3 < = c1 WHEN CONV_INTEGER(c2)= 8 ELSE c3; --(3)

d4 < = c1 WHEN c2 = 8 else c3;

--(4)

【例8-14】

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY decoder3to8 IS PORT ( input: IN STD_LOGIC_VECTOR (2 DOWNTO 0);

数据类型

1.4 数组类型

【例8-15】 FUNCTION To_bit ( s : std_ulogic; xmap : BIT := '0' ) RETURN BIT ; FUNCTION To_bitvector ( s : std_logic_vector ;

xmap : BIT := '0' ) RETURN BIT_VECTOR ; FUNCTION To_bitvector ( s : std_ulogic_vector ;

output: OUT STD_LOGIC_VECTOR (7 DOWNTO 0)); END decoder3to8; ARCHITECTURE behave OF decoder3to8 IS BEGIN

vhdl array用法

vhdl array用法VHDL中的数组是一种用于存储和操作多个元素的数据结构。

它可以包含同一类型的多个元素,并允许对这些元素进行统一的处理。

在VHDL中,数组可以有多种类型:一维数组、多维数组、固定大小数组、可变大小数组等。

以下是VHDL中数组的一些主要用法:1.声明数组变量:可以使用以下语法在VHDL中声明数组变量:```type array_type is array (range) of element_type;```其中,`array_type`是数组类型的名称,`range`指定数组的索引范围,`element_type`是数组中每个元素的数据类型。

2.初始化数组:可以在声明数组时初始化数组的元素,也可以在后续的赋值语句中初始化数组,例如:```variable my_array : array_type := (0 => 10, 1 => 20, 2 => 30);```或者```variable my_array : array_type;my_array(0) := 10;my_array(1) := 20;my_array(2) := 30;```3.访问数组元素:可以使用索引来访问数组中的特定元素,例如:```my_array(1) := 25;```4.遍历数组:可以使用`for...loop`循环结构来遍历数组,并对每个元素进行处理,例如:```for i in my_array'range loopmy_array(i) := my_array(i) * 2;end loop;```5.多维数组:VHDL还允许定义多维数组,即数组的索引具有多个维度,例如:```type matrix_type is array (integer range <>, integer range <>) of element_type;```其中`integer range <>`表示未指定索引范围,可以根据实际需要进行设置。

(完整word版)vhdl基本语法

VHDL 基础语法篇——VHDLVHDL硬件描述语言1。

1 VHDL概述1。

1。

1 VHDL的特点VHDL语言作为一种标准的硬件描述语言,具有结构严谨、描述能力强的特点,由于VHDL语言来源于C、Fortran等计算机高级语言,在VHDL语言中保留了部分高级语言的原语句,如if语句、子程序和函数等,便于阅读和应用。

具体特点如下:1。

支持从系统级到门级电路的描述,既支持自底向上(bottom-up)的设计也支持从顶向下(top—down)的设计,同时也支持结构、行为和数据流三种形式的混合描述。

2. VHDL的设计单元的基本组成部分是实体(entity)和结构体(architecture),实体包含设计系统单元的输入和输出端口信息,结构体描述设计单元的组成和行为,便于各模块之间数据传送.利用单元(componet)、块(block)、过程(procure)和函数(function)等语句,用结构化层次化的描述方法,使复杂电路的设计更加简便。

采用包的概念,便于标准设计文档资料的保存和广泛使用。

3. VHDL语言有常数、信号和变量三种数据对象,每一个数据对象都要指定数据类型,VHDL的数据类型丰富,有数值数据类型和逻辑数据类型,有位型和位向量型。

既支持预定义的数据类型,又支持自定义的数据类型,其定义的数据类型具有明确的物理意义,VHDL是强类型语言。

4. 数字系统有组合电路和时序电路,时序电路又分为同步和异步,电路的动作行为有并行和串行动作,VHDL语言常用语句分为并行语句和顺序语句,完全能够描述复杂的电路结构和行为状态。

1.1.2 VHDL语言的基本结构VHDL语言是数字电路的硬件描述语言,在语句结构上吸取了Fortran和C等计算机高级语言的语句,如IF语句、循环语句、函数和子程序等,只要具备高级语言的编程技能和数字逻辑电路的设计基础,就可以在较短的时间内学会VHDL语言。

但是VHDL毕竟是一种描述数字电路的工业标准语言,该种语言的标识符号、数据类型、数据对象以及描述各种电路的语句形式和程序结构等方面具有特殊的规定,如果一开始就介绍它的语法规定,会使初学者感到枯燥无味,不得要领.较好的办法是选取几个具有代表性的VHDL程序实例,先介绍整体的程序结构,再逐步介绍程序中的语法概念。

第十讲 VHDL语言的数据类型

关系操作符

/=

不等于

任何数据类型

<VHDL语言小于的操作枚符举与(整数类o型p,e及r对a应t的o一r维数)组

>

大于

枚举与整数类型,及对应的一维数组

<=

小于等于

枚举与整数类型,及对应的一维数组

>=

一、大于逻等辑于 操作符枚举与整数类型,及对应的一维数组

逻辑操作符

AND

与

BIT,BOOLEAN,STD_LOGIC

VHDL数据类型

字符(CHARACTER)数据类型

单引号引起来,如:‘A’ ‘a’ 字符分大小写。’A’不等于’a’

字符串(STRING)数据类型

双引号引起来字符串数组,一般用于程序的提示和结果说明, VARIABLE string_yin : STRING (1 TO 7 ) ; string_yin := "a b c d" ;

end record; singal bus : iocell; bus.Enable <= ‘1’; bus.Data <= “00110110”;

用户定义的子类型

用户对已定义的数据类型,作一些范围限制而形成新的数据类型

格式: SUBTYPE 子类型名 IS 数据类型名 范围

例:SUBTYPE data IS STD_LOGIC_VECTOR(7 DOWNTO 0); SUBTYPE digit IS INTEGER RANGE 0 TO 9;

信号和变量赋值区别举例

信号赋值(非立即)

Architecture abc of example is signal tmp:std_logic; Begin process(a,b,c) begin tmp<=a; x<=c and tmp; tmp<=b; y<=c and tmp; end process; End abc;

Verilog数组表示及初始化

Verilog数组表示及初始化要点补充:1.除了书本上常用的六种(各三种)用法外,还可以如下方式:$readmemb(“D:/file1/file2/ramh.dat”,a);即可以调用到放置在任意处的存储文件。

2.当采用$readmemb(“ramh.dat”,a);这种方式时,ramh.dat文件必须放置在工程下的simulation下,亲测其他放置都无效。

3.关于存储文件后缀,.dat .txt 甚至不加后缀都可以,只要保证程序里调用的与文件夹中实际的一致,可以索引到即可!4.存储顺序。

文档中由上至下,对应数组由低到高。

5.不可综合。

$readmemb、$readmemh、initial 都是不可综合语句(怎么可以这样呢!那大数组怎么赋值?)也就是说只能在仿真时调试用。

6.对于$readmemh对应的16进制文件,不用写成4'hA,最简单的A即可。

这里的内存模型指的是内存的行为模型。

Verilog中提供了两维数组来帮助我们建立内存的行为模型。

具体来说,就是可以将内存宣称为一个reg类型的数组,这个数组中的任何一个单元都可以通过一个下标去访问。

这样的数组的定义方式如下:reg [wordsize : 0] array_name [0 : arraysize];例如:reg [7:0] my_memory [0:255];其中 [7:0] 是内存的宽度,而[0:255]则是内存的深度(也就是有多少存储单元),其中宽度为8位,深度为256。

地址0对应着数组中的0存储单元。

如果要存储一个值到某个单元中去,可以这样做:my_memory [address] = data_in;而如果要从某个单元读出值,可以这么做:data_out = my_memory [address];但要是只需要读一位或者多个位,就要麻烦一点,因为Verilog不允许读/写一个位。

这时,就需要使用一个变量转换一下:例如:data_out = my_memory[address];data_out_it_0 = data_out[0];这里首先从一个单元里面读出数据,然后再取出读出的数据的某一位的值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VHDL中数组的定义和使用

为了帮助网友解决“VHDL中数组的定义和使用?”相关的问题,中国学网通过互联网对“VHDL中数组的定义和使用?”相关的解决方案进行了整理,用户详细问题包括:RT,我想知道:VHDL中数组的定义和使用?,具体解决方案如下:解决方案1:

--定义matrix_index为数组

TYPEmatrix_indexisarray(3downto0)ofstd_logic_vector(7downto0); SIGNALa:matrix_index;--定义了数组a[4],即数组元素为a[0],a[1],a[2],a[3]

constantR:matrix_index:=(x"15",x"0F",x"0A",x"06");--定义了常数数组R[4]

--使用时跟C语言中一样,加下标就可以了,上面是用downto定义了方向,故R[0]是最后一项,如在R数组中R[0]=X"06",R[3]=X"15" 以上不知道说清楚了没,满意请及时采纳

我看还是补充一段参考程序吧

---------------------------------------

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

ENTITYshift_row_invIS

PORT(

shiftrow_in:INSTD_LOGIC_VECTOR(127DOWNTO0);

shiftrow_out:OUTSTD_LOGIC_VECTOR(127DOWNTO0)

);

ENDshift_row_inv;

ARCHITECTUREbehOFshift_row_invIS

--typedescribingthebytearrayconsistingof16bytematrixarray TYPEmatrix_indexisarray(15downto0)ofstd_logic_vector(7downto0); SIGNALb,c:matrix_index;

BEGIN

--initialmappingofinputintoabytematrixarraynamedb

matrix_mapping:PROCESS(shiftrow_in)

BEGIN

FORiIN15DOWNTO0LOOP

b(15-i)<=shiftrow_in(8*i+7DOWNTO8*i);

ENDLOOP;

ENDPROCESSmatrix_mapping;

--shiftrowtransformation

--b(i)-->c(i)

--

--|04812||04812|(noshift)

--|15913|==>|13159|(1rightshift)

--|261014||101426|(2rightshift) --|371115||711153|(3rightshift)

--shiftedfirstcolumn

c(0)<=b(0);

c(1)<=b(13);

c(2)<=b(10);

c(3)<=b(7);

--shiftedsecondcolumn

c(4)<=b(4);

c(5)<=b(1);

c(6)<=b(14);

c(7)<=b(11);

--shfitedthirdcolumn

c(8)<=b(8);

c(9)<=b(5);

c(10)<=b(2);

c(11)<=b(15);

--shiftedforthcolumn

c(12)<=b(12);

c(13)<=b(9);

c(14)<=b(6);

c(15)<=b(3);

--mappingtemporarycvectorintoshiftedrowoutput matrix_mapping_back:PROCESS(c)

BEGIN

FORiIN15DOWNTO0LOOP

shiftrow_out(8*i+7DOWNTO8*i)<=c(15-i); ENDLOOP;

ENDPROCESSmatrix_mapping_back; ENDbeh;。