工程电磁场课后答案

工程电磁场课后习题答案

E2-9 在中心点位于原点,边长为L的媒质立方体内的极化强度矢量为()0e x y z P P e x e y e z =++,(a) 计算面和体束缚电荷密度; (b) 证明总束缚电荷为零。

解:据题,体束缚电荷密度为:03v e P P ρ=-∇⋅=- (公式y x zE E E E x y z∂∂∂∇⋅=++∂∂∂) 在2L x =的面002s x e L e P P x P ρ=⋅== 在2L x =-的面00()2s x e Le P P x P ρ=-⋅=-= 同理,在2Ly =和2L y =-的面,02s L P ρ=在2L z =和2L z =-的面,02s LP ρ=∴(a )六个面上的面束缚电荷密度均为:0/2P L ρ=s体束缚电荷密度为:03v P ρ=-∴ (b) 总束缚电荷为:23006()302s v LQ Q Q L P P L =+=-=E2-13 半径为a 的球内充满体电荷密度为f ρ的电荷。

已知球内外的电场强度是⎪⎩⎪⎨⎧≥+≤+=-)()()(24523a r rAa a a r Ar r E r求体电荷密度(全部空间的介电常数均为0ε)。

解:0f E ρε∇⋅=(1)在r a ≤的区域内:23221[()]E r r Ar r r∂∇⋅=⋅+∂ 254r Ar =+ 20(54)f r Ar ρε∴=+(2)在r a ≥的区域内:254221[()]E r a Aa r r r-∂∇⋅=⋅⋅+∂ = 0 0f ρ∴=∴体电荷密度为:20(54),(),()f r Ar r a r a ερ⎧+≤=⎨≥⎩E2-17 两媒质分界面为z=0面,已知1223r r εε==和,如果已知区域1中的123(5)x y z E e y e x e z =-++我们能求出区域2中哪些地方的2E 和2D 呢?能求出区域2中任意点的2E 和2D 吗? 解:(1)在两种媒质的分解面z=0上,由于没有电荷的存在,电位移矢量的法线方向连续。

工程电磁场部分课后习题答案

⼯程电磁场部分课后习题答案12-1 ⼀点电荷q放在⽆界均匀介质中的⼀个球形空腔中⼼■设介质的介电常数为⼀空腔的半径为S求空腔表⾯的极化电荷⾯密度。

解由⾼斯定律,介质中的电场强度为-P(SM- e r) =KT ⼆——_- E4πer2*r由关系式n = e0E+P,得电极化强度为P-(E - Eo)E = ---- --- -4 Tter因此,空腔表⾯的极化电荷⾯密度为1-3-1从静堪场基本⽅程出发‘证明当电介质均匀时*极化电荷密度P P 存在的条件是⾃由电荷的体密度P不为零,且有关系式P P- - (I-^)P O 解均匀介质的E为常数C t从关系式D= ε0E + P Xr> = εE1得介质中的电极化强度P=D-ε0E-D-E0≤ = (l扱化电荷密度PP =-V -P= - V *[(1 -~)D \=?D灼(1 ⼀“)Tl )V ?!>εε由円?DP和Sl -号)=仇故上式成为P P=-学)⼙1-4-3 IJillF列静电场的边值问题:(0电荷体密度分别为⾓和他,半径分别为G的双层同⼼带电球体(如题1 - 4 - 3 图(a));(2)在两同⼼导体球壳间,左半部和右半部分别填充介电常数为引与∈2 的均匀介质,内球壳带总电荷量为外球売接地(如题1-4-3图(b));(3)半径分别为α与B的两⽆限也空⼼同轴圆柱⾯导体,内圆柱表⾯上单位长度的电量为⼚外圆柱⾯导休接地(如题I -3图(C))O仅供⽤于学习版权所有郑州航院电⽓⼯程及其⾃动化邓燕博倾⼒之作J? t -4- 3 图解(1)选球坐标系,球⼼与原点重合⼨数,故有如下静电场边值问题:由对称性町知,电位护仅为⼚的函y1 d zd7σ豁-EO(0≤r< α)d / 不&豁-(aI Y Ct ( 乔& (XY 8:r = a=?’r ≡αιL严翠f P2F = A =拓I lr = A—⾦⼀e?r =卄L呦=有限值,P-I rf 8-0(2)选球坐标乘*球⼼与原点重介。

3工程电磁场 课后答案(王泽忠 全玉生 卢斌先 著) 清华大学出版社

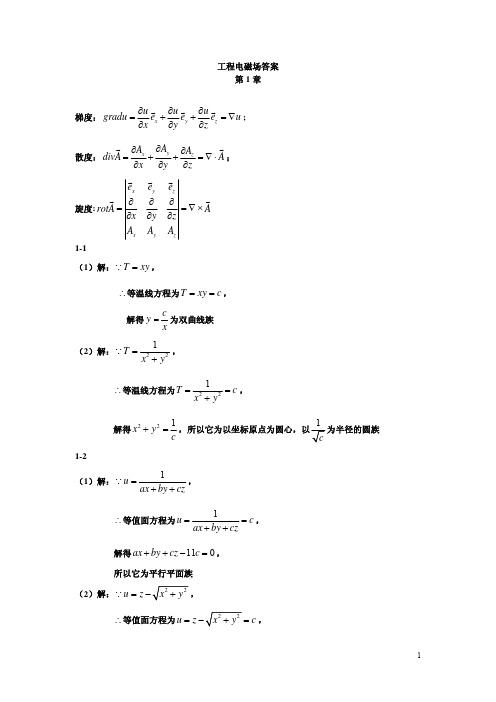

工程电磁场答案第1章梯度:x y z u u u gradu e e e u x y z∂∂∂=++=∇∂∂∂; 散度:y x z A A A divA A x y z∂∂∂=++=∇⋅∂∂∂ ; 旋度:xy zxy ze e e rotA A x y z A A A ∂∂∂==∂∂∂ ∇⨯ 1-1(1)解:,T xy = ∴等温线方程为T x ,y c ==解得cy x=为双曲线族 (2)解:21T 2x y=+ , ∴等温线方程为221T c x y ==+,解得221x y c +=为半径的圆族 1-2(1)解:1u ax by cz=++ ,∴等值面方程为1u c ax by cz==++,解得, 110ax by cz c ++-=所以它为平行平面族(2)解:u z =-,∴等值面方程为u z c ==,解得()222x y z c +=-,顶点在(的圆锥面族)0,0,c (3)解: ()222ln u x y z=++,∴等值面方程为,()222ln u x y z =++c =解得222cx y z e ++=, 所以它为球心在原点的球面族1-3解:由题意可得,,x y z 2A x A y A z ===,又x y zdx dy dz A A A ==,即2dx dy dzx y z ==, ,2dx dy dx dzx y x z∴==, 212,y c x z c x ==, 过()1.0,2.0,3.0M 122,3c c ∴==,即22,3y x z x ==(联立)1-4解:由题意可知22,,x y z 2A y x A x y A y z ===,,x y zdx dy dz A A A ==即222dx dy dz y x x y y z ==,,dx dy dx dzy x x z∴==, 可得2212,x y c z c -==x (联立) 1-5 解:|621M ux z x ∂=+=∂2, 0|2M uz y ∂=-=-∂6,|222M uz y x z ∂=-+=∂4,余弦cos αβγ===,所以方向导数为0|1264M u l ∂=-=∂ 1-6 解:000|5,|4,|M M M u u uy z x z x y x y z∂∂∂=+==+==+=∂∂∂3, 过点(), 1.0,2.0,3.0余弦cos α==,cos β==cos γ==543+=1-7 解:0|22,24,2M u u u y x z x y z∂∂∂==-===-=-∂∂∂2), 设点到点的方向余弦为()2.0, 1.0.1.0-(3.0,1.0. 1.0-1cos 3α==,22cos ,cos 33βγ==-, 所以方向导数为()12222333⎛⎫⨯-++-⨯-= ⎪⎝⎭103, 由题意可知。

工程电磁场课后答案

电磁兼容性

总结词

电磁兼容性是研究电磁场和电子系统相互作 用的学科。

详细描述

电磁兼容性主要关注电子系统在电磁环境中 的性能表现,包括电磁干扰(EMI)和电磁敏 感度(EMS)等问题。通过学习电磁兼容性,

学生可以了解如何设计和实施有效的电磁屏 蔽、滤波和接地措施,以确保电子系统的可 靠性和稳定性。这对于电子设备和系统的设

磁场能量存储

磁力发电机

利用磁场和导线的相对运动产生感应电动势的原理,将机械能转换为电能进行存 储。

磁性存储器

利用不同磁性材料的不同磁化方向来存储数据,通过改变磁性材料的磁化方向来 读取和写入数据。

电场能量存储

电容

利用电极板之间的电场储存电能,具 有充电和放电的能力,常用于滤波、 去耦和储能等电路中。

总结词

恒定磁场的散度和旋度均为零。

详细描述

由于恒定磁场中电流是恒定的,因此其磁 场强度不会随时间变化,散度和旋度均为 零。

时变电磁场

详细描述

时变电磁场具有以下特性,电场和磁场都 随时间变化,电场和磁场之间存在相互耦

合,电磁波可以传播。

A 总结词

时变电磁场是指电磁场随时间变化 的电磁场。

B

C

D

详细描述

总结词

静电场的散度和旋度分别为零 和不为零。

详细描述

由于静电场中电荷是静止的, 因此其电场线不会随时间变化 ,散度和旋度均为零。

恒定磁场

总结词

详细描述

恒定磁场是由恒定电流产生的磁场,其磁 场强度不随时间变化。

恒定磁场具有以下特性,磁场强度与电流 密度成正比,磁感应线是闭合曲线且无旋 、无源,磁场强度与磁势梯度成正比。

高频电磁波在医疗领域的应用

工程电磁场 (杨宪章 邹玲 樊亚东 著) 中国电力出版社 课后答案 题ch1

E2 ⋅ 2πR = E3 ⋅ 2πR =

τ1 τ1 , E2 = 2ε 0πR ε0

R > R2 :

S

课

后

v 仅 R2 中不填 ρ ,其内 E2 :

ρπr 2 E2 ⋅ 2πr = ε0

r v v v ρ v r ρa ∴ E = E1 − E2 = (R − r ) = 2ε 0 2ε 0

习题 1-17 解:任意半径 r 处 E: v v ∫ εEdS = q

v σ ⋅ 2πrdr ⋅ x v dE = i 3 2 2 2 4πε 0 r + x

网

P

x

(

故 r 从 R1 到 R2 积分即所有圆环产生的场强:

v R2 σ ⋅ 2πrdr ⋅ x v σx E=∫ i = 3 4ε 0 2 2 R1 4πε r + x 2 0

R2

(

)

d r 2 + x 2 v σx −2 i = 3 ∫ 4ε 0 2 R1 r 2 + x 2 2 r + x2

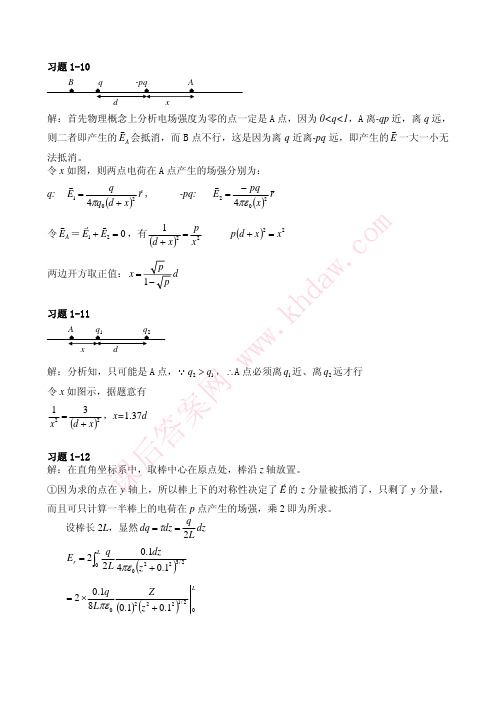

v E1 = q r r, 2 4πq0 (d + x )

-pq:

v E2 =

− pq v r 2 4πε 0 ( x )

两边开方取正值: x =

p 1− p

d

习题 1-11

A x q1 d q2

解:分析知,只可能是 A 点,Q q2 > q1 ,∴ A 点必须离 q1 近、离 q2 远才行 令 x 如图示,据题意有

σ ⎢ 1− E= 2ε 0 ⎢

⎣

⎡

(

⎤ ⎥ 1 2 2 2 ⎥ R2 + x ⎦ x

)

2)又

R2 →∞得 x

工程电磁场课后题目答案

2-5有两相距为d 的无限大平行平面电荷,电荷面密度分别为σ和σ-。

求由这两个无限大平面分割出的三个空间区域的电场强度。

解:100022E σσσεεε⎛⎫=--= ⎪⎝⎭20030022022E E σσεεσσεε⎛⎫=---= ⎪⎝⎭=-=2-7有一半径为a 的均匀带电无限长圆柱体,其单位长度上带电量为τ,求空间的电场强度。

解:做一同轴单位长度高斯面,半径为r(1)当r ≦a 时,222012112E r r a r E a τπππετπε⋅⋅=⋅⋅⋅=(2)当r>a 时,0022E r E rτπετπε⋅==2-15有一分区均匀电介质电场,区域1(0z <)中的相对介电常数12r ε=,区域2(0z >)中的相对介电常数25r ε=。

已知1234x y z =-+E e e e ,求1D ,2E 和2D 。

解:电场切向连续,电位移矢量法向连续()()11222111122212220202021022020,10,505020,10,201050502010201050x y z r r x r y r z rr x r y r z r x y zrr x r y r z E E D D D E D e e e E e e e D e e e εεεεεεεεεεεεεεεεεε==-===-=∴=-+=-+=-+2-16一半径为a 的金属球位于两种不同电介质的无穷大分界平面处,导体球的电位为0ϕ,求两种电介质中各点的电场强度和电位移矢量。

解:边界电场连续,做半径为r 的高斯面()()()()()()22121221202121212002222222Saar D dS r E E r E Q QE r Q QE dr dr r aQ a a E e rπεεπεεπεεϕπεεπεεπεεϕϕ∞∞⋅=+=+=∴=+⋅===++∴=+∴=⎰⎰⎰⎰12102012221020112210201020,,,r r p n p n a a D e D e r r D D aap e p e aaεϕεϕεϕεϕσσεεεεσϕσϕ======--=⋅=-=⋅=-两介质分界面上无极化电荷。

工程电磁场 (杨宪章 邹玲 樊亚东 著) 中国电力出版社 课后答案 题ch2

习题 2-21 解:求 q 受力,再加以分析即可。

q' =

R q d R q d

q" = Q + q ' = Q +

− q ' 与 q 相吸, q" 与 q 相斥,吸力有可能无穷大,斥力有限,故可能相吸。

所以 q 处场强:

课

后

R R2 解: q = q, b = , ϕ( x , y , z ) 由四个电荷产生。 d d

21

解:设两导线单位长带 τ A ,τ B 电荷,则由镜象知:

ϕA = ϕB =

课

τA τ 2h + D − R 2h − R ln + B ln 2πε 0 R 2πε 0 D−R τA τ 2h − R 2h − D − R ln + B ln 2πε 0 R + D 2πε 0 R

后

答

案

网

ww

课

2π (ε 1 + ε 2 )

,ϕ =

2 0

≤ 0.02 R0 2 x0 ≤ 0.02d

0

答

E1 = E2 =

∂ϕ A q =− = 2 ∂r r 2 2π (ε 1 + ε 2 )r

q 2π (ε 1 + ε 2 )r

案

D12πr +D22πr =q q ε1E1 + ε 2 E2 = 2πr 2

( 2h) 2 + d 2 τ1 τ 2h + 2 ln = α11τ 1 + α12τ 2 ln d 2πε 0 R0 2πε 0

α11 = α 22 , α12 = α 21

2πε 0 1

习题 2-31 解:相距很远,则 d>>a q q ∴ϕ1 = 1 + 2 = α11q1 + α12 q2 4πεa 4πεd q q ∴ϕ 2 = 1 + 2 = α 21q1 + α 22 q2 4πεd 4πεa

工程电磁场课后题答案

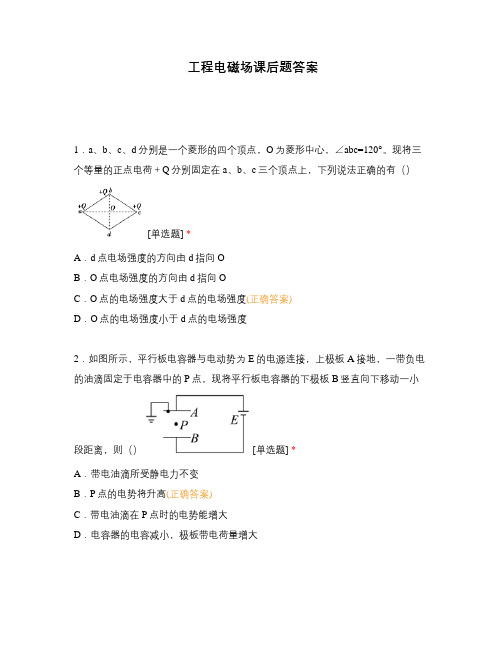

工程电磁场课后题答案1.a、b、c、d分别是一个菱形的四个顶点,O为菱形中心,∠abc=120°。

现将三个等量的正点电荷+Q分别固定在a、b、c三个顶点上,下列说法正确的有()[单选题] *A.d点电场强度的方向由d指向OB.O点电场强度的方向由d指向OC.O点的电场强度大于d点的电场强度(正确答案)D.O点的电场强度小于d点的电场强度2.如图所示,平行板电容器与电动势为E的电源连接,上极板A接地,一带负电的油滴固定于电容器中的P点,现将平行板电容器的下极板B竖直向下移动一小段距离,则() [单选题] *A.带电油滴所受静电力不变B.P点的电势将升高(正确答案)C.带电油滴在P点时的电势能增大D.电容器的电容减小,极板带电荷量增大3.如图为三根通电平行直导线的断面图,若它们的电流大小都相同,且,则A点的磁感应强度的方向是() [单选题] *A.垂直纸面指向纸外B.垂直纸面指向纸里C.沿纸面由A指向BD.沿纸面由A指向D(正确答案)4.如图所示,伏安法测电阻的电路中,电压表的量程为,内阻为,测量时发现电压表的量程过小,在电压表上串联一个阻值为的定值电阻,最后电压表示数为,电流表示数为,关于的阻值下列说法正确的是()[单选题] *A.Rx大于60Ω(正确答案)B.Rx等于60ΩC.Rx大于20ΩD.Rx等于20Ω5.在研究微型电动机的性能时,应用如图所示的实验电路,当调节滑动变阻器R使电动机停止转动时,电流表和电压表的示数分别为0.5A和2.0V。

重新调节R使电动机恢复正常运转,此时电流表和电压表的示数分别为2.0A和24.0V。

则这台电动机正常运转时输出功率为() [单选题] *A.47WB.44WC.32W(正确答案)D.18W6.用两只完全相同的电流表分别改装成一只电流表和一只电压表。

将它们串联起来接入电路中,如图所示,此时() [单选题] *A.电流表指针的偏转角小于电压表指针的偏转角(正确答案)B.两只电表的指针都不偏转C.两只电表的指针偏转角相同D.电流表指针的偏转角大于电压表指针的偏转角7.一带负电油滴在场强为E的匀强电场中的运动轨迹如图中虚线所示,电场方向竖直向下.若不计空气阻力,则此带电油滴从A运动到B的过程中,下列判断正确的是() [单选题] *A.油滴的电势能减少(正确答案)B.A点电势高于B点电势C.油滴所受电场力小于重力D.油滴重力势能减小8.如图所示,直线A为电源的U—I图线,直线B为电阻R的U—I图线,用该电源和电阻组成闭合电路时,电源的输出功率和电路的总功率分别是()[单选题] *A.4W,8WB.2W,4WC.4W,6W(正确答案)D.2W,3W9.电流表的内阻是,满刻度电流值是,现欲把这个电流表改装成量程为1.0V的电压表,正确的方法是() [单选题] *A.应串联一个0.1Ω的电阻B.应并联一个0.1Ω的电阻C.应串联一个1800Ω的电阻(正确答案)D.应并联一个1800Ω的电阻10.如图所示,带电粒子(不计重力)以初速度v0从a点垂直于y轴进入匀强磁场,运动过程中经过b点,Oa=Ob。

工程电磁场__课后答案(王泽忠_全玉生_卢斌先_著)_清华大学出版社课后题解

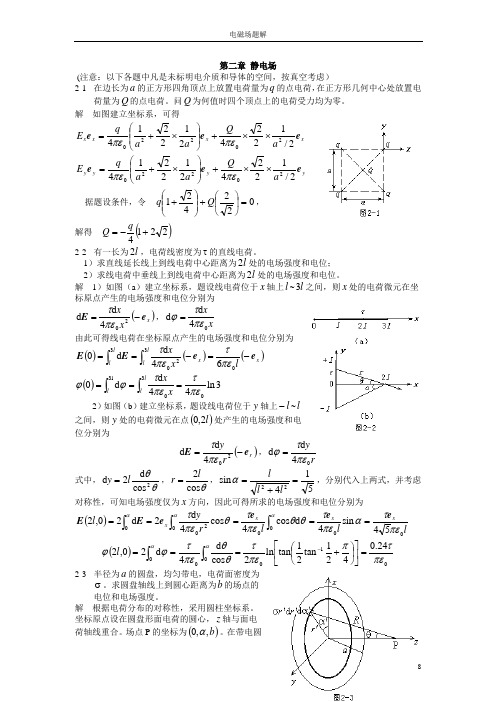

第二章 静电场 (注意:以下各题中凡是未标明电介质和导体的空间,按真空考虑) 2-1 在边长为 a 的正方形四角顶点上放置电荷量为 q 的点电荷, 在正方形几何中心处放置电 荷量为 Q 的点电荷。问 Q 为何值时四个顶点上的电荷受力均为零。 解 如图建立坐标系,可得

2 1 2 1 q 1 Q 2 + e x + × × × ex 2 2 πε 4πε 0 2 4 2 2 / 2 a a a 0 q 1 2 1 Q 2 1 2 + e y + Eyey = × × × ey 2 2 4πε 0 2 4 πε 2 a 2 a a / 2 0 2 2 + Q 据题设条件,令 q1 + = 0, 4 2 q 解得 Q = − 1 + 2 2 4 2-2 有一长为 2l ,电荷线密度为 τ 的直线电荷。 1)求直线延长线上到线电荷中心距离为 2l 处的电场强度和电位; 2)求线电荷中垂线上到线电荷中心距离为 2l 处的电场强度和电位。 解 1)如图(a)建立坐标系,题设线电荷位于 x 轴上 l ~ 3l 之间,则 x 处的电荷微元在坐 Exex =

11

电磁场题解

则 A 、 C 间 和 D 、 B 间 的 电 场 强 度 不 变 , 电 压 也 不 变 , 即 U AC = U DB = U / 3 ,

τdy (− e r ) , dϕ = τdy 2 4πε 0 r 4πε 0 r

ϕ (2l ,0) = 2∫ dϕ =

0

α

τ 4πε 0

∫

α

0

1 dθ 1 π 0.24τ τ ln tan tan −1 + = = 2 4 πε 0 cosθ 2πε 0 2

工程电磁场 (杨宪章 邹玲 樊亚东 著) 中国电力出版社 课后答案 题ch4

习题4-16解:B 只有x 分量,从平面图可见x =0时l Id v 与r r 垂直,x ≠0时l Id v 与r r垂直 απμπμRd dl R IRdlR R R Idl dB x ===∴,443'0'2'0()()3222032220203'202424X RIR X R IR d R IR B +=+==∴∫μππμαπμπ习题4-18解:dbd Ia dr r I S d r I S d B b d d S S +==⋅=⋅=Φ∫∫∫+ln2220000πμπμαπμv v v v习题4-19解:αcos 22221ab b =a R −+ααπcos 2)cos(2222222ab b a ab b =a R ++=−−+任一点xIB πμ20=1200ln 222221R Ra I adx r I R R AB πμπμ=⋅=Φ∴∫习题4-20解:由安培环路定律10R r <<时,取单位长,22102r R I r B ππμπ=⋅,r R IB 2102πμ=21R r R <<时,I r B 02μπ=⋅,rIB πμ20=32R r R <<时,)()([])()([22223222022232220R R R r I I R R R r I I r B −−−=−−−=⋅μππμπ课后答案网ww w.kh da w .c om)()(222232230R R r R r I B −−=πμ 3R r >时,02=⋅r B π,0=B习题4-21解:任意点:j x D Ix I B v v ))(22(00−+=πμπμ习题4-22解:电流反向,则磁力线反向j x D I x I B v v )(22(00−−=πμπμ习题4-23解:I r B μωπ=⋅2,rIB πμω2=wb R R Ib dr r Ib R R 31210973.0ln 2221−×==⋅=Φ∴∫πμωπμω习题4-24解:P176例中,)(220a d d I −−=Φμ本题,wb a d d I 322109696.0))((−×=−−=Φωμ习题4-25解:B 1、B 2只有t 分量,由边界条件H 1t =H 2tT H B t 2.10024.050000111===μμμ习题4-26解:...1)2(0201122232232223223=−−∂∂=−−∂∂∂∂∂∂=×∇z z r e r R R r R r I r R R r R r I z re r e e r H v v v v v ππαα课后答案网ww w.kh da w .c om习题4-27解:0点上下的m ϕ,0=∞m ϕ 带I 圆导线线圈在轴线上产生的2/32)(2x R IR BH +==μ I l d H BAB A =⋅=−∫vv ϕϕ习题4-28解:忽略边缘效应,H 是圆线m ϕ仅与α有关,D C m +=αϕ令0=α是障碍面,且0|0==αϕm 所以0=D 由安培定律∫∫∫+==πθθπω2020Hdl Hdl I Hdl在(0,2π)中,μ->∞,H 只有法线分量,B 1n =B 2n ,知00==μμHH t 所以02=∫πθdl H t所以00||==−==∫αθαθϕϕωm m Hdl ICQ I =ω,QIC ω=αωϕQIm =0000001αωμααϕμϕμμvv v v Qr I r H B m m −=∂∂−=∇−==习题4-29解:x e z y x F v v 1222)(−++= k z y x yj z y x z z y x z y xkj iF v v v v vv 222222221222)(2)(20)(++−++=++∂∂∂∂∂∂=×∇− 课后答案网ww w.kh da w .c om习题4-30解:∫⋅=Φ∴SS d B vvr<a ,22a rIB πμ=r>a ,rIB πμ2=]2ln 21[2ln 222222202+=+=+=⋅=Φ∴∫∫∫πμπμπμπμπμr Iaa a aI a a I adr r I adr a rI S d B a a a S v v习题4-32解:H R d l L 30010*119.2ln −==πμ习题4-34解:铜:0μμ=,钢:0200μμ=(1)算每公里长自感铜e i L L L +=其中km H L i /10100010008270−×=××=πμ km H l R DL e /1027631ln 700−×=⋅=πμ km mH L L L e i /863.2=+=钢:km H L i /102000010008270−×=××=πμ km H L e /10228157−×=km mH L L L e i /286.22=+=(2)互感:根据方向判断'11Φ+Φ=Φ∴km mH l M /036.02'1'12'2'112ln 20=⋅⋅⋅=πμ习题4-35 解:r I B πμω21=,21102−×=Φdr rId πμω 2122102−×=Φ=Ψdr rId d πωμωω课后答案网ww w.kh da w .c om67ln 10210221276212−−×=×=Ψ∫πωμωπωμωI dr r IH I M 0148.067ln 102212=×=−πωμω习题4-36 解:由题意得...2)(212)2(212)2(212121322112223223020021022=−−++===∫∫∫∫∫∫R R R R R v rdr I R R r R rdr r I rdr R Ir dVH LI W πμππμππμμ...22==I WL习题4-37解:C I mW M =∂∂=|αααcos 21max 21I I M I MI W m ==ααsin 21max I I M M −=∴o 45=α,m N M ⋅×−=∴−310035.0α习题4-38解:1220022102ln 21212)2(21211R R I rdr R Ir dV H W R v πμππμμ===∫∫∫∫ l r V 2π=,l R dR dV112π= 212201212212084|R I dV dR R R R R I V W f C I mg πμπμ−=−=∂∂==测验题4-39解:将其分段考虑,与0点在一条线上的两直线段上的电流不在0点产生磁场,仅两段圆弧上的电流在0点产生磁场。

工程电磁场课后答案

用正边沿D触发器实现1101序列检测器

第一章节

Q1

Q0

0

0

0

1

1

0

1

1

0

0

0

1

1

0

1

1

试用负边沿D触发器组成4位二进制异步加计数器,画出逻辑图。

7.1.4 试用正边沿D触发器组成3位二进制同步加计数器,画出逻辑图。

规律:

加:

减:

试用正边沿D触发器和门电路设计一个同步三进制减计数器。

5.2.11 触发器转换

6.1.1 由状态表作状态图

6.1.3 由状态图作状态表

5电路的初始状态为01,当序列X=100110时,求该 电路输出Z的序列。

解:011010

6.2.5 同步时序电路分析

6.2.9 异步时序电路分析

可自启动的异步七进制计数器

用同步结构实现状态度,要求电路最简,采用正边沿JK触发器。 解:(1) 画出状态表 列出真值表 写出逻辑表达式

7.1.18 用74161采用两种不同方法构成24进制。

试用两片74194构成8位双向移位寄存器。

并 联

第五章 触发器 5.1.1 R、S输入高电平有效 5.1.3 画同步RS触门组成的同步RS触发器功能

分析各种结构触发的翻转特点

同步触发器:有CP信号控制,高(低)电平期间Q状态保持, (高)低电平期间Q状态由输入端决定;

基本RS触发器:没有CP信号,Q状态由R/S直接决定;

7.1.9 分析计数器改制电路

7.1.11 分析计数器改制电路

异步清零反馈法 译码反馈状态(过渡状态):1010

有效状态:0000~1001 结论:十进制

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

7.1.14 74290用两种不同方法实现六进制

(1)异步清零法

(2)异步置九法

0 ~ 5 ~ 6 (0110)

9~0 ~ 1~2~3~4~5( 0101)

(高)低电平期间Q状态由输入端决定; 主从触发器:动作分两步, CP=1(0)时主触发器接收信号,从

触发器不变;CP下降沿(上升沿)到来,主触发 器保持,从触发器翻转,CP=0(1)后,主从触 发器都不再翻转而保持。 边沿触发器:触发沿前接收输入信号,触发沿时候翻转,触 发沿后封锁信号。

5.2.1 画输出波形

7.1.3 试用负边沿D触发器组成4位二进制异步加计数器,画出逻

辑图。

Q1 Q0

00

01

10

11

00

01

10

11

7.1.4 试用正边沿D触发器组成3位二进制同步加计数器,画出逻 辑图。

规律:

加: D0 Q0

D1 Q1 Q0 D2 Q2 Q1Q0 D3 Q3 Q2Q1Q0

减: D0 Q0

D1 Q1 Q0 D2 Q2 Q1Q0 D3 Q3 Q2 Q1Q0

7.1.7 试用正边沿D触发器和门电路设计一个同步三进制减计数器。

7.1.9 分析计数器改制电路

异步清零反馈法 译码反馈状态(过渡状态):1010

有效状态:0000~1001 结论:十进制

第五章 触发器

5.1.1 R、S输入高电平有效 5.1.3 画同步RS触发器输出波形(CP=1)

图5.1.6

5.1.6 分析由与或非门组成的同步RS触发器功能

5.1.10 分析各种结构触发的翻转特点

基本RS触发器:没有CP信号,Q状态由R/S直接决定; 同步触发器:有CP信号控制,高(低)电平期间Q状态保持,

Qn1 D S RQn

Qn1 D JQ n KQn

6.1.1 由状态表作状态图

6.1.3 由状态图作状态表

6.1.5电路的初始状态为01,当序列X=100110时,求该 电路输出Z的序列。

解:011010

6.2.5 同步时序电路分析

6.2.9 异步时序电路分析 可自启动的异步七进制计数器

6.3.3 用同步结构实现状态度,要求电路最简,采用正边沿 JK触发器。

解:(1) 画出状态表

(2) 列出真值表

(3) 写出逻辑表达式

J XQ n K XQn

0

1

0

1

J XQn

1

0

K X Qn

1

0

Z QnQn XQn

10

1

(4)画出电路图

6.3.7 用正边沿D触发器实现1101序列检测器1111

(1) 同步预置法: 反馈状态 (23)D=(17)H=(0001 0111)B

7.2.2 试用两片74194构成8位双向移位寄存器。

并 联

7.1.16 分析计数器电路

改制方法:整体清零反馈法(异步) 片间级联方式:并行进位 译码反馈状态:1010 1110 有效计数起始状态:0000 0000 ~1010 1101(173)

M=174

7.1.18 用74161采用两种不同方法构成24进制。 (1) 异步清零法: 反馈状态 (24)D=(18)H=(0001 1000)B

Q1 Q2

5.2.4 画输出波形

Q1 Qn1 QnQn 1Qn Qn Qn1 QnQn 1Qn 0 Q2

Q3

Qn1 1Qn 1Qn Qn

Q4

Qn1 1Qn QnQn 1

5.2.8 画输出波形

5.2.11 触发器转换

Qn1 D T Qn