基于PLL频率合成器锁相环的降噪技术

锁相环(PLL)频率合成调谐器

锁相环(PLL)频率合成调谐器调谐器俗称高频头,是对接收来的高频电视信号进行放大(选频放大)并通过内部的变频器把所接收到的各频道电视信号,变为一固定频率的图像中频(38MHz)和伴音中频以利于后续电路(声表面滤波器、中放等)对信号进行处理。

调谐器(高频头)原理:高频放大:把接收来的高频电视信号进行选频放大。

本机振荡器:产生始终高于高频电视信号图像载频38MHz的等幅载波,送往混频器。

混频器:把高频放大器送来的电视信号和本机振荡器送来的本振等幅波,进行混频产生38MHz的差拍信号(即所接收的中频电视信号)输出送往预中放及声表面滤波器。

结论:简单的说:只要改变本机振荡器的频率即可达到选台的目的)一、电压合成调谐器:早期彩色电视接收机大部分均采用电压合成高频调谐器,其调谐器的选台及波段切换均由CPU输出的控制电压来实现(L、H、U波段切换电压及调谐选台电压),其中调谐选台电压用来控制选频回路和本振回路的谐振频率,调谐选台电压的任何变化都将导致本机振荡器频率偏移,选台不准确、频偏、频漂。

为了保证本机振荡器频率频率稳定,必须加上AFT系统。

由于AFT系统中中放限幅调谐回路和移相网络一般由LC谐振回路构成,这个谐振回路是不稳定的,这就造成了高频调谐器本机振荡器频率不稳,也极易造成频偏、频漂。

二、频率合成调谐器1、频率合成的基本含义:是指用若干个单一频率的正弦波合成多个新的频率分量的方法(频率合成调谐器的本振频率是由晶振分频合成的)。

频率合成的方法有很多种。

下图为混频式频率合成器方框图以上图中除了三个基频外还有其“和频”及“差频”输出(还有各个频率的高次谐波输出)。

输出信号的频率稳定性由基准信号频率稳定性决定,而且输出信号频率误差等于各基准信号误差之和,因此要想减少误差除了要提高基准信号稳定度之外还应减少基准信号的个数。

2、锁相环频率合成器:其方框图类似于彩色电视接收机中的副载波恢复电路,只是在输入回路插入了一个基准信号分频器(代替色同步信号输入)而在反馈支路插入一个可编程分频器(代替900移相)。

改善锁相环相位噪声的方法

改善锁相环相位噪声的方法锁相环(Phase-Locked Loop, PLL)是一种常用的频率合成器和时钟恢复方法。

然而,在某些应用中,锁相环的相位噪声成为限制系统性能的因素。

因此,改善锁相环相位噪声是一个重要的课题。

下面将介绍几种改善锁相环相位噪声的方法。

首先,一个容易实施的方法是优化锁相环的环路滤波器。

环路滤波器的设计直接影响锁相环的带宽和噪声性能。

通过增加滤波器的阻尼比,可以提高锁相环的稳定性和减小相位噪声。

另外,合理选择滤波器的带宽,可以平衡相位追踪性能和噪声抑制能力,从而改善锁相环的相位噪声。

其次,采用抖动降低技术可以有效减小锁相环的相位噪声。

抖动降低技术基于频率抖动和相位抖动之间的关系,通过控制频率抖动来减小相位噪声。

常用的抖动降低技术包括相位锁定环(Phase-Locked Loop, PPL)、时钟周期抖动降低技术等。

这些技术通过引入额外的控制环路或采用特殊的抖动降低算法,可以显著改善锁相环的相位噪声性能。

第三,优化参考信号源也是改善锁相环相位噪声的有效方法。

参考信号源的噪声特性直接传递到锁相环的输出。

因此,选择低噪声的参考信号源对于改善锁相环的相位噪声非常重要。

常见的低噪声参考信号源包括晶体振荡器(Crystal Oscillator, XO)或原子钟等。

通过使用低噪声的参考信号源,可以有效降低锁相环的相位噪声。

总结起来,改善锁相环相位噪声的方法包括优化环路滤波器、采用抖动降低技术和选择低噪声的参考信号源。

通过合理应用这些方法,可以显著提升锁相环的相位噪声性能,从而满足不同应用对于相位噪声的要求。

锁相环原理及应用

锁相电路(PLL)及其应用自动相位控制(APC)电路,也称为锁相环路(PLL),它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

它是一个以相位误差为控制对象的反馈控制系统,是将参考信号与受控振荡器输出信号之间的相位进行比较,产生相位误差电压来调整受控振荡器输出信号的相位,从而使受控振荡器输出频率与参考信号频率相一致。

在两者频率相同而相位并不完全相同的情况下,两个信号之间的相位差能稳定在一个很小的范围内。

目前,锁相环路在滤波、频率综合、调制与解调、信号检测等许多技术领域获得了广泛的应用,在模拟与数字通信系统中已成为不可缺少的基本部件。

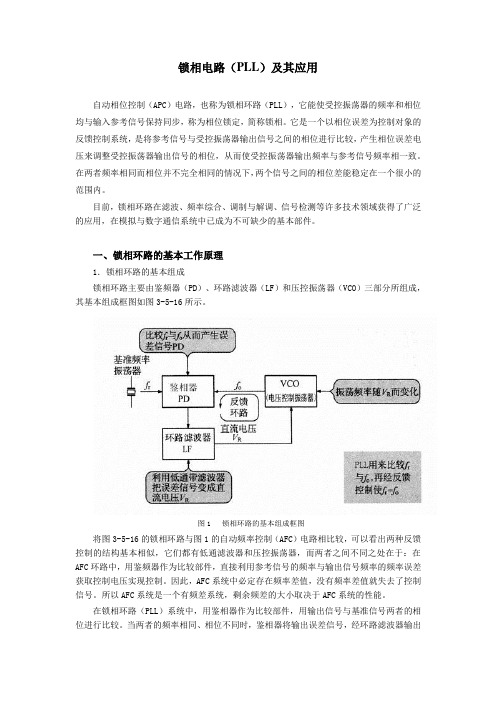

一、锁相环路的基本工作原理1.锁相环路的基本组成锁相环路主要由鉴频器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分所组成,其基本组成框图如图3-5-16所示。

图1 锁相环路的基本组成框图将图3-5-16的锁相环路与图1的自动频率控制(AFC)电路相比较,可以看出两种反馈控制的结构基本相似,它们都有低通滤波器和压控振荡器,而两者之间不同之处在于:在AFC环路中,用鉴频器作为比较部件,直接利用参考信号的频率与输出信号频率的频率误差获取控制电压实现控制。

因此,AFC系统中必定存在频率差值,没有频率差值就失去了控制信号。

所以AFC系统是一个有频差系统,剩余频差的大小取决于AFC系统的性能。

在锁相环路(PLL)系统中,用鉴相器作为比较部件,用输出信号与基准信号两者的相位进行比较。

当两者的频率相同、相位不同时,鉴相器将输出误差信号,经环路滤波器输出控制信号去控制VCO ,使其输出信号的频率与参考信号一致,而相位则相差一个预定值。

因此,锁相环路是一个无频差系统,能使VCO 的频率与基准频率完全相等,但二者间存在恒定相位差(稳态相位差),此稳态相位差经鉴相器转变为直流误差信号,通过低通滤波器去控制VCO ,使0f 与r f 同步。

2.锁相环路的捕捉与跟踪过程当锁相环路刚开始工作时,其起始时一般都处于失锁状态,由于输入到鉴相器的二路信号之间存在着相位差,鉴相器将输出误差电压来改变压控振荡器的振荡频率,使之与基准信号相一致。

锁相环频率合成器的相位噪声分析

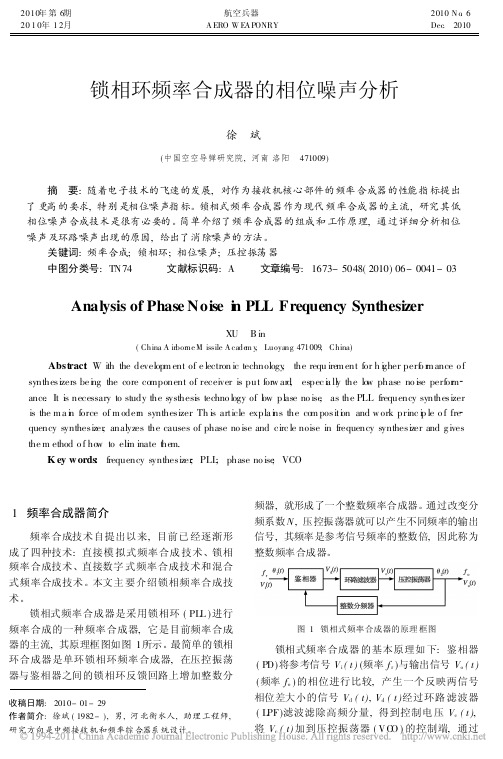

图 1 锁相式频率合成器的原理 框图

锁相式频率合成器 的基本原理如 下: 鉴相器 ( PD) 将参考信号 V i ( t ) (频率 f r )与输出信号 Vo ( t ) ( 频率 fo ) 的相位进行比较, 产生一个反映两信号 相位差大小的信号 Vd ( t) , Vd ( t ) 经过环路 滤波器 ( LPF )滤波滤除高频分量 , 得到控制电 压 Vc ( t ), 将 Vc ( t) 加到压控振荡器 ( VCO ) 的控制端, 通过

42

航空兵器

2010 年第 6 期

VCO 使得输出频率 fo 向 f r 靠拢 , 直到消除相差使 环路锁定。

令

pd

2 锁相环路中的相位噪声

锁相环频率合成器主要由倍频器、放大器、分 频器、混频器、鉴相器、 压控振荡器 ( VCO) 等基本 电路组成, 有的还包括辅助捕获电路、跳频控制电 路和电子开关等, 它们都不同程度地将噪声引入 频率合成器中, 因此对频率合成器各组成部件噪 声的研究就很有必要。 2 . 1 鉴相器对环路噪声的影响 鉴相器是 PLL 的关键部件之一, 它有许多不 同的类型和电路形式。目前较常用的鉴相器基本 上可分为两大类: 乘法器 ( 或逻辑组合 ) 电路和时 序电路。 这里主要讨论乘法器类鉴相器。 乘法器类 鉴相器将输 入信号波 形与本地 振荡器波 形相乘 , 并把乘积的平均值作为其有用的直流输出, 一个 设计正确的乘法器鉴相器可以对淹没在极大噪声 中的输入信号进行处理。 这里假设 PLL 环路是线性的, 鉴相器是理想 的。鉴相器引入的噪声用一个外加的等效干扰噪 声电压 vpd ( s) 代替 , 如图 2 所示。

1 频率合成器简介

频率合成技术自提出以来 , 目前已 经逐渐形 成了四种技术 : 直接模 拟式频率合成 技术、锁相 频率合成技术、直接数字 式频率合成技术和混合 式频率合成技术。本文主 要介绍锁相频率合成技 术。 锁相式频率合成器是采用锁相环 ( PLL ) 进行 频率合成的一种频率合成器, 它是目前频率合成 器的主流, 其原理框图如图 1 所示。 最简单的锁相 环合成器是单环锁相环频率合成器, 在压控振荡 器与鉴相器之间的锁相环反馈回路上增加整数分

锁相环输出信号相位噪声噪声及杂散特性分析应用实践

锁相环输出信号相位噪声噪声及杂散特性分析应用实践【摘要】本文详细地介绍了锁相环的鉴频鉴相器、分频器和输入参考信号的相位噪声对锁相环合成输出信号的近端相位噪声的具体贡献值。

并以CDMA 1X 基站系统中800MHz 的FS 单板的锁相环输出信号相位噪声指标进行理论计算。

为广大锁相环设计者提供理论计算方法的参考和实践设计的参考依据。

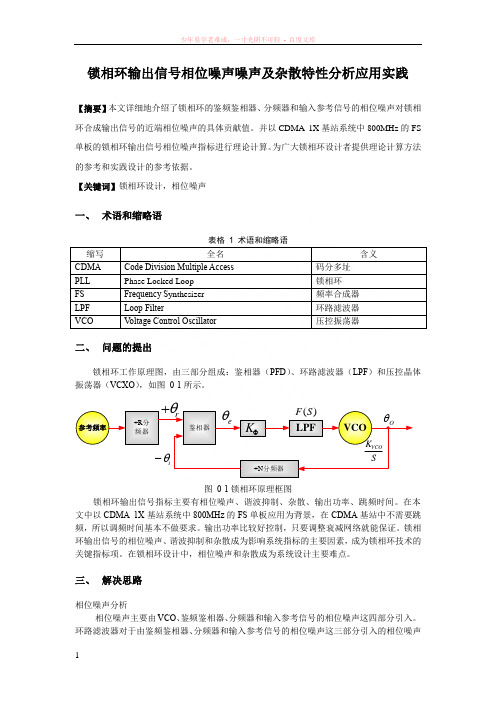

【关键词】锁相环设计,相位噪声一、 术语和缩略语表格 1 术语和缩略语 缩写全名 含义 CDMACode Division Multiple Access 码分多址 PLLPhase Locked Loop 锁相环 FSFrequency S ynthesizer 频率合成器 LPFLoop Filter 环路滤波器 VCO Voltage Control Oscillator压控振荡器 二、 问题的提出锁相环工作原理图,由三部分组成:鉴相器(PFD )、环路滤波器(LPF )和压控晶体振荡器(VCXO ),如图 0-1所示。

÷R 分频器VCO 参考频率鉴相器÷N 分频器LPF ΦK O θS K VCO )(S F rθ+iθ-e θ图 0-1锁相环原理框图锁相环输出信号指标主要有相位噪声、谐波抑制、杂散、输出功率、跳频时间。

在本文中以CDMA 1X 基站系统中800MHz 的FS 单板应用为背景,在CDMA 基站中不需要跳频,所以调频时间基本不做要求。

输出功率比较好控制,只要调整衰减网络就能保证。

锁相环输出信号的相位噪声、谐波抑制和杂散成为影响系统指标的主要因素,成为锁相环技术的关键指标项。

在锁相环设计中,相位噪声和杂散成为系统设计主要难点。

三、 解决思路相位噪声分析相位噪声主要由VCO 、鉴频鉴相器、分频器和输入参考信号的相位噪声这四部分引入。

环路滤波器对于由鉴频鉴相器、分频器和输入参考信号的相位噪声这三部分引入的相位噪声具有低通特性,对于VCO产生的相位噪声具有高通特性。

基于ADIsimPLL 3.1的锁相环环路滤波器设计

基于ADIsimPLL 3.1的锁相环环路滤波器设计作者:高立俊来源:《现代电子技术》2013年第15期摘要:对锁相环环路滤波器进行简单分析,对ADIsimPLL 3.1模拟软件的功能特点做了简要介绍,并利用仿真软件对一款频率合成器的环路滤波器进行仿真设计,结果表明该软件在设计应用中方便快捷,能够帮助设计出满足指标要求且性能稳定的环路滤波器。

关键词:环路带宽; PLL;环路滤波器;压控灵敏度中图分类号: TN713⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)15⁃0056⁃03 Design of PLL loop filter based on ADIsimPLL 3.1GAO Li⁃jun(Shaanxi Fenghuo Communication Group Co., Ltd., Baoji 721006, China)Abstract: The PLL loop filter is analyzed simply. The functions and characteristics of simulation software ADIsimPLL 3.1 are introduced. In addition, ADIsimPLL 3.1 is adopted to carried out simulation design of a loop filter of frequency synthesizer. The results indicates the software have advantages in designs and applications, and can help design the loop filter with steady performances which can meet the requirements.Keywords: bandwidth of loop; PLL; loop filter; VCO sensitivity0 引言随着通信技术在各个领域的高速发展,频率合成器作为通信设备的重要组成部分,对其也提出了越来越高的设计要求,不但要能满足宽的频率范围、高的频率稳定度和准确度,而且要求其具有良好的杂散和相位噪声、快速的频率切换。

锁相环PLL设计调试小结

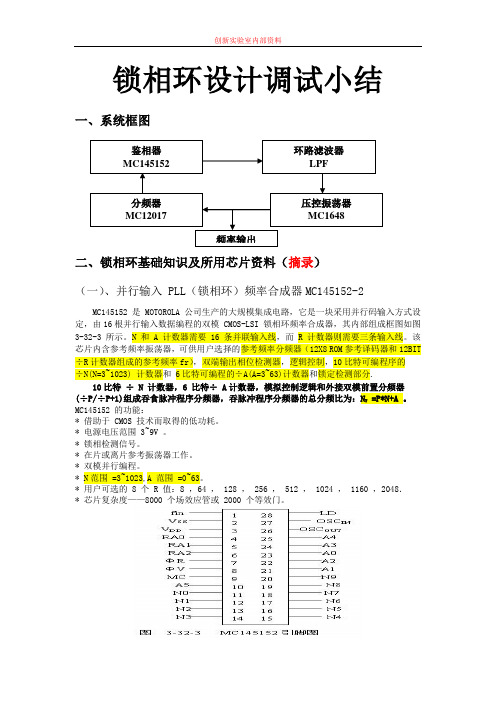

锁相环设计调试小结一、系统框图二、锁相环基础知识及所用芯片资料(摘录)(一)、并行输入 PLL (锁相环)频率合成器MC145152-2MC145152 是 MOTOROLA 公司生产的大规模集成电路,它是一块采用并行码输入方式设定,由16根并行输入数据编程的双模 CMOS-LSI 锁相环频率合成器,其内部组成框图如图 3-32-3 所示。

N 和 A 计数器需要 16 条并联输入线,而 R 计数器则需要三条输入线。

该芯片内含参考频率振荡器,可供用户选择的参考频率分频器(12X8 ROM 参考译码器和12BIT ÷R 计数器组成的参考频率fr ),双端输出相位检测器,逻辑控制,10比特可编程序的÷N(N=3~1023) 计数器和 6比特可编程的÷A(A=3~63)计数器和锁定检测部分.10比特 ÷ N 计数器,6 比特÷ A 计数器,模拟控制逻辑和外接双模前置分频器(÷P /÷P +1)组成吞食脉冲程序分频器,吞脉冲程序分频器的总分频比为:N T =P*N+A 。

MC145152 的功能:* 借助于 CMOS 技术而取得的低功耗。

* 电源电压范围 3~9V 。

* 锁相检测信号。

* 在片或离片参考振荡器工作。

* 双模并行编程。

* N 范围 =3~1023,A 范围 =0~63。

*用户可选的 8 个 R 值:8 ,64 , 128 , 256 , 512 , 1024 , 1160 ,2048. * 芯片复杂度——8000 个场效应管或 2000 个等效门。

鉴相器MC145152 环路滤波器 LPF压控振荡器 MC1648分频器MC12017频率输出引脚说明:N0-N9 (11-20 ):÷ N 计数器的编程输入端。

当÷ N 计数器的计数为0 时,这N个输入供给预置÷ N 计数器的数据。

N0 为最低位,N9 为最高位。

基于DDS+PLL频率合成器的设计

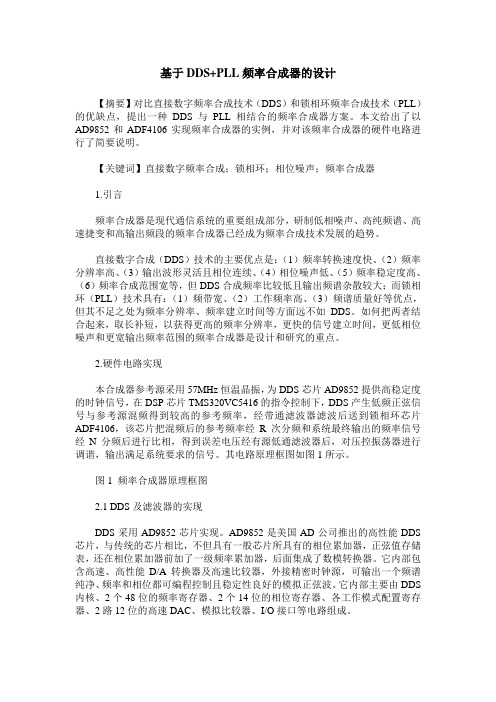

基于DDS+PLL频率合成器的设计【摘要】对比直接数字频率合成技术(DDS)和锁相环频率合成技术(PLL)的优缺点,提出一种DDS与PLL相结合的频率合成器方案。

本文给出了以AD9852和ADF4106实现频率合成器的实例,并对该频率合成器的硬件电路进行了简要说明。

【关键词】直接数字频率合成;锁相环;相位噪声;频率合成器1.引言频率合成器是现代通信系统的重要组成部分,研制低相噪声、高纯频谱、高速捷变和高输出频段的频率合成器已经成为频率合成技术发展的趋势。

直接数字合成(DDS)技术的主要优点是:(1)频率转换速度快、(2)频率分辨率高、(3)输出波形灵活且相位连续、(4)相位噪声低、(5)频率稳定度高、(6)频率合成范围宽等,但DDS合成频率比较低且输出频谱杂散较大;而锁相环(PLL)技术具有:(1)频带宽、(2)工作频率高、(3)频谱质量好等优点,但其不足之处为频率分辨率、频率建立时间等方面远不如DDS。

如何把两者结合起来,取长补短,以获得更高的频率分辨率,更快的信号建立时间,更低相位噪声和更宽输出频率范围的频率合成器是设计和研究的重点。

2.硬件电路实现本合成器参考源采用57MHz恒温晶振,为DDS芯片AD9852提供高稳定度的时钟信号,在DSP芯片TMS320VC5416的指令控制下,DDS产生低频正弦信号与参考源混频得到较高的参考频率,经带通滤波器滤波后送到锁相环芯片ADF4106,该芯片把混频后的参考频率经R次分频和系统最终输出的频率信号经N分频后进行比相,得到误差电压经有源低通滤波器后,对压控振荡器进行调谐,输出满足系统要求的信号。

其电路原理框图如图1所示。

图1 频率合成器原理框图2.1 DDS及滤波器的实现DDS采用AD9852芯片实现。

AD9852是美国AD公司推出的高性能DDS 芯片,与传统的芯片相比,不但具有一般芯片所具有的相位累加器,正弦值存储表,还在相位累加器前加了一级频率累加器,后面集成了数模转换器。