EDA实验箱手册

#eda实验箱介绍

前言本实验教材总体结构主要由三部分组成:其中第一部分是教案系统的简单介绍;第二部分是软件的安装及使用;第三部分为实验部分;在实验部分中其实验由易至难可分为基础类实验、应用类实验、模拟类实验和综合类实验。

本系统采用模拟与数字以及单片机相结合的设计思想,利用模块化组合设计,使得该实验系统操作简单,灵活,显示直观。

本实验系统主要是为了让学生通过实验了解并掌握MAX+plus II的逻辑输入方法,编译及仿真原理,PAC Designerr软件的使用,以及器件下载等基本内容;实验由简到难,由分离到综合,从而逐步提高学生实验能力和实验水平。

第一部分教案系统介绍一、配套硬件要求:1、PC机:要求586或以上的微机,内存需64MB以上,硬盘需1G以上。

2、示波器:20M示波器。

3、单片机仿真器。

二、NC-EDA-2000C型实验箱实验箱基本配套:NC-EDA-2000C实验箱一台;电源线一根;PAC、CPLD/FPGA 下载电缆各一根;RS-232电缆一根;实验指导书一本;实验连线30根。

2、系统结构组成:NC-EDA-2000C实验箱组成框图3、实验箱结构特点说明:芯片结构板:实验箱采用Altara公司的EP1K10TC100—3芯片,位于实验箱组成框图的14所示位置,具的低内核电压、低功耗的特点。

芯片内门电路高达1万门,内部使用RAM作电路结构,速度高达几百MHZ,其输出可用管脚已全部开放,位于芯片的四周,用户可以根据自己的要求和芯片本身的功能自己任意定义管脚。

同时为了体现实验箱的可扩展性,在芯片的两边各有一个34脚的IDE插口,可以通过数据排线与其它应用模块相连接,其具体的管脚如下图所示:其下载口位于实验箱组成框图的7所示位置。

EP1K10TC100—3芯片的管脚分见附图1。

显示类模块:实验箱中有液晶显示模块<LCD);8位7段数码管显示输出;;8位发光二极管<LED灯)等几个显示模块。

其功能是为了显示其实验的结果。

EDA实验指导书1209

实验一QuartusII软件应用一、实验目的1、熟悉EDA开发平台的基本操作。

2、掌握EDA开发工具的图形设计方法。

3、掌握图形设计的编译与验证方法。

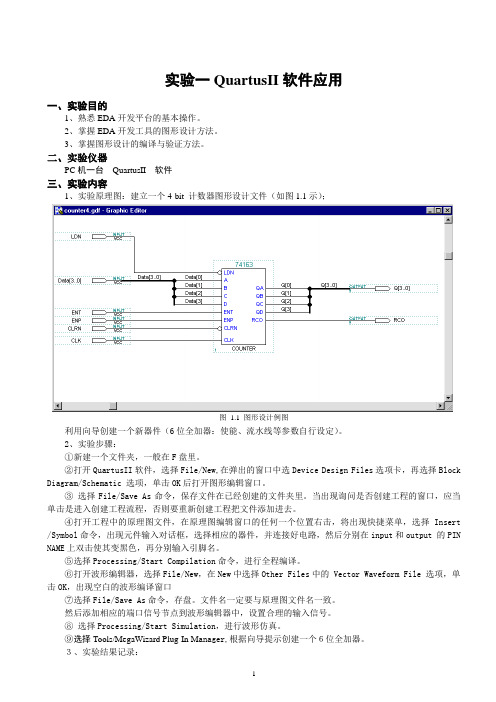

二、实验仪器PC机一台QuartusII软件三、实验内容1、实验原理图:建立一个4-bit 计数器图形设计文件(如图1.1示);图 1.1 图形设计例图利用向导创建一个新器件(6位全加器:使能、流水线等参数自行设定)。

2、实验步骤:①新建一个文件夹,一般在F盘里。

②打开QuartusII软件,选择File/New,在弹出的窗口中选Device Design Files选项卡,再选择Block Diagram/Schematic 选项,单击OK后打开图形编辑窗口。

③选择File/Save As命令,保存文件在已经创建的文件夹里。

当出现询问是否创建工程的窗口,应当单击是进入创建工程流程,否则要重新创建工程把文件添加进去。

④打开工程中的原理图文件,在原理图编辑窗口的任何一个位置右击,将出现快捷菜单,选择Insert /Symbol命令,出现元件输入对话框,选择相应的器件,并连接好电路,然后分别在input和output 的PIN NAME上双击使其变黑色,再分别输入引脚名。

⑤选择Processing/Start Compilation命令,进行全程编译。

⑥打开波形编辑器,选择File/New,在New中选择Other Files中的 Vector Waveform File 选项,单击OK,出现空白的波形编译窗口⑦选择File/Save As命令,存盘。

文件名一定要与原理图文件名一致。

然后添加相应的端口信号节点到波形编辑器中,设置合理的输入信号。

⑧选择Processing/Start Simulation,进行波形仿真。

⑨选择Tools/MegaWizard Plug-In M anager,根据向导提示创建一个6位全加器。

3、实验结果记录:打印出实验原理图与仿真波形图,打印出利用向导创建的新器件的图形,完成实验报告四、实验研究与思考1、延迟时间分析、最高工作频率分析等时间分析有何重要性?2、流水线的作用是什么?对那些性能有影响?2、功能仿真、验证起到什么作用?实验二VHDL软件设计一、实验目的1、熟悉EDA开发平台的基本操作。

EDA实验台使用说明书

第一部分软件使用说明一、MAX+PLUSⅡ软件安装和使用(一)概述MAX+PLUSⅡ开发系统是易学易用的完全集成化的EDA设计开发环境。

它包含了开发CPLD/FPGA器件的全过程。

下面将以MAX+PLUSⅡ的基本使用为基础介绍CPLD/FPGA器件的开发方法,CPLD/FPGA 器件及其开发系统是极其复杂的,因此在学习使用时应注意如下特点:1) MAX+PLUSⅡ的使用与学习一定要与CPLD/FPGA硬件的学习相结合。

2) 注意学习软件与动手练习相配合,只有多动手设计与调试才能真正掌握设计思想与设计方法。

3) 多参考相关的书籍或MAX+PLUSⅡ的帮助系统。

4) 在学习过程中要与数字电路、计算机语言等课程进行比较,找出相同点与不同点,进行比较、类比地学习。

5) 概念的区分与使用:器件与符号:如在数字电路中7400为一个器件,在MAX+PLUSⅡ中器件一般被CPLD/FPGA 器件专用,而MAX+PLUSⅡ中调用的中小规模的器件都称为符号。

本文中有时出于习惯,也会在该使用“符号”的地方而使用“器件”名称,因此在碰到像“器件”、“符号”这样的词,一定要注意上下文的联系。

模块与符号:传统习惯,一般是将一个电路抽象后形成模块,利用模块进行更高层次的设计。

而在MAX+PLUSⅡ中电路抽象后形成的模块依然称为“符号”。

因此在见到“模块”与“符号”这样的词语时,也要注意上下文的联系。

(二)MAX+PLUSⅡ的版本及其安装2.1单机版软件推荐下述系统配置:奔腾Ⅱ300MHz以上 CPU、64M以上内存、WIN95或WIN98/WIN2000操作系统、CDROM驱动器、2G或更大容量的硬盘。

2.2 安装过程1.将MAX+PLUSⅡ的安装光盘放入CDROM中。

2.在我的电脑下双击光盘图标,继续操作找到MAXPLUS2,在MAXPLUS2目录下双击INSTALL图标。

3.根据提示选择Full installation 进行全部安装或custom Installation进行定制安装,如2-1图所示:图2-1 MAX+PLUSⅡ安装示意图(1)4.根据提示设置好安装路径后,点击NEXT,在下一个界面中将所需部分选中,如果计算机有足够的硬盘空间,最好全部选中,因为有些文件虽然不是必须的,但安装后对改善MAX+PLUSⅡ的使用起到很大的作用。

电子设计自动化eda实验指导书样本

电子设计自动化(EDA)实验指引书前言近些年来,电子设计自动化(EDA)技术发展迅速。

一方面,各种大容量、高性能、低功耗可编程逻辑器件不断推出,使得专用集成电路(ASIC)生产商感受到空前竞争压力。

另一方面,浮现了许多EDA设计辅助工具,这些工具大大提高了新型集成电路设计效率,使更低成本、更短周期复杂数字系统开发成为也许。

于是一场ASIC 与FPGA/CPLD之争在所难免。

然而PLD器件具备先天竞争优势,那就是可以重复编程,在线调试。

EDA技术正是这场较劲推动引擎之一。

普通来说,EDA技术就是以计算机为平台,以EDA软件工具为开发环境,以HDL为设计语言,以可编程器件为载体,以ASIC、SOC芯片为目的器件,以电子系统设计为应用方向电子产品自动化设计过程。

设计者只需编写硬件描述语言代码,然后选取目的器件,在集成开发环境里进行编译,仿真,综合,最后在线下载调试。

整个过程,大某些工作由EDA软件完毕。

全球许多知名可编程器件提供商都推出了自己集成开发工具软件,如Altera公司MAX+PLUSⅡ、Quartus Ⅱ软件;Xilinx公司Foundation 、ISE软件,Lattice公司ispExpert 软件,Actel公司Libero软件等。

这些软件推出,极大地增进了集算法设计、芯片编程、电路板设计于一体EDA技术发展。

此外,在以SOC芯片为目的器件电子系统设计规定下,可编程器件内部开始集成高速解决器硬核、解决器软核、DSP模块、大量存储资源、高速串行收发模块、系统时钟管理器、多原则I/O接口模块,亦使得设计者更加得心应手,新一轮数字革命由此引起。

EDA技术是一门实践性很强学科,要培养出具备竞争力一流IC 设计人才,动手能力是核心。

只有通过理论学习,加上现场实验,在使用软件编程加硬件调试过程中真正获得锻炼,增长技能。

ZY11EDA13BE型实验系统采用主板加适配板加扩展板灵活构造,可以便进行基于不同PLD芯片实验开发,并易于升级,符合当前高校在此方面对人才培养规定。

实验箱使用说明

ZYE 1502D型EDA实验箱使用说明一、硬件系统1、芯片下载板:Altera公司:EPF10K10LC84-4下载板(数字部分)2、数码管显示:动态显示8位(M1-M8),静态显示4位(M5-M8);3、发光二极管输出:16位;4、输入位数(开关):16位;5、输入位数(按键):16位;6、时钟信号:由50MHz、12MHz、4.194304MHz晶振输出:7、喇叭一个;8、配有RS232接口;9、配有VGA接口;10、配有PS/2键盘接口;11、16X16点阵;12、配有并行A/D转换器ADC0809;并行D/A转换器DAC0832;13、配有存贮器62256;14、配有单片机(AT89C51)15、配有一片管理芯片EPM7128;16、含有一块通用下载模块;17、含有8038低频信号源输出模块;系统实物照片如图1。

图1 ZYE 1502D型EDA实验箱实物照片系统整体模块结构如图2。

图2 ZYE 1502D型EDA实验箱模块结构二、配套软件Max+Plus II 10.2版1、运行环境Win95/98或NT4.02、层次化设计支持3、原理图输入支持4、文本输入支持5、AHDL, VHDL输入支持6、全仿真/功能仿真支持7、逻辑综合支持8、硬件编程/下载支持9、原理图设计宏库基本库10、支持芯片CPLD/FPGA系列三、操作指南1、开关、按键及指示灯KD1-KD16、K1-K16、KL1-KL16:主板下方有16个按键K1-K16;16个拨位开关KD1-KD16;16个发光二极管KL1-KL16。

每个纵列的一组开关、按键、发光二极管与下载板上CPLD/FPGA 的一个I/O口对应相连。

当与I/O口相对应的开关KDi作为输入使用时,开关拨向上,开关上方的发光二极管亮,表示开关向该I/O口输入一个逻辑量为“1”的高电平,拨向下时,表示“0 "。

当需要用按键向I/O口输入一个短脉冲量时,首先需将开关拨向下方,按卜键Ki后,发光二极管KLi亮,表示该按键Ki向对应I/O口输入了一个正脉冲。

EDA实验手册

EDA 实验手册实验一3-8线译码器的设计一、实验目的同3-8线译码器的设计,让同学们掌握组合逻辑电路的设计方法,熟悉Quartu s Ⅱ设计硬件电路的基本流程。

二、实验步骤1、新建一个工程,注意工程名、文件名还有实体名要一致。

2、新建一个VHDL文件,输入设计程序并保存。

3、对新建的VHDL文件进行语法编译。

4、进行仿真(也可以跳过这一步)。

5、进行引脚分配,并进行总编译。

6、将程序下载到实验箱,在实验箱上连线进行实验。

三、参考程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity decoder3to8 isport(input:in std_logic_vector(2 downto 0);output:out bit_vector(7 downto 0));end decoder3to8;architecture behave of decoder3to8 isbeginoutput<="00000001" sll conv_integer(input);--用输入值来控制左移的位数end behave;四、实验要求1、仿真出3-8线译码器的实际波形。

2、根据实验结果画出3-8线译码器的真值表。

实验二十进制计数器的设计一、实验目的设计一个带使能输入、同步清零和同步加载功能的加1/减1计数器。

二、功能分析(1)同步清零端低电平有效,当其为低电平时,在下一个时钟上升沿来临时计数值清零,即清零功能与时钟同步。

(2)同步加载端低电平有效,当其为低电平时,在下一个时钟周期来临时将要加载的计数值读入计数器,然后将其置为高电平后,在读入的数的基础上加1或减1计数。

(3)使能输入端高电平有效,当其为高电平时正常计数,当其为低电平时停止计数。

(4)当计数方向控制端为高电平时加1计数,当其为低电平时减1计数。

EDA实验指导书(含目录)QuatursV1.0版分析

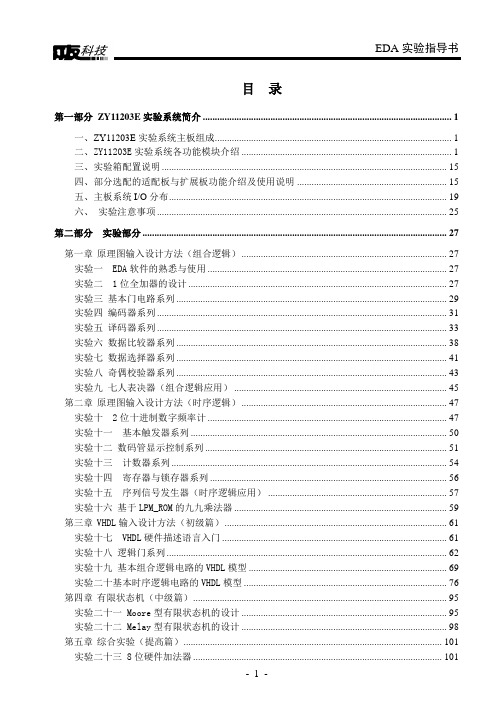

目录第一部分ZY11203E实验系统简介 (1)一、ZY11203E实验系统主板组成 (1)二、ZY11203E实验系统各功能模块介绍 (1)三、实验箱配置说明 (15)四、部分选配的适配板与扩展板功能介绍及使用说明 (15)五、主板系统I/O分布 (19)六、实验注意事项 (25)第二部分实验部分 (27)第一章原理图输入设计方法(组合逻辑) (27)实验一 EDA软件的熟悉与使用 (27)实验二 1位全加器的设计 (27)实验三基本门电路系列 (29)实验四编码器系列 (31)实验五译码器系列 (33)实验六数据比较器系列 (38)实验七数据选择器系列 (41)实验八奇偶校验器系列 (43)实验九七人表决器(组合逻辑应用) (45)第二章原理图输入设计方法(时序逻辑) (47)实验十 2位十进制数字频率计 (47)实验十一基本触发器系列 (50)实验十二数码管显示控制系列 (51)实验十三计数器系列 (54)实验十四寄存器与锁存器系列 (56)实验十五序列信号发生器(时序逻辑应用) (57)实验十六基于LPM_ROM的九九乘法器 (59)第三章VHDL输入设计方法(初级篇) (61)实验十七 VHDL硬件描述语言入门 (61)实验十八逻辑门系列 (62)实验十九基本组合逻辑电路的VHDL模型 (69)实验二十基本时序逻辑电路的VHDL模型 (76)第四章有限状态机(中级篇) (95)实验二十一 Moore型有限状态机的设计 (95)实验二十二 Melay型有限状态机的设计 (98)第五章综合实验(提高篇) (101)实验二十三 8位硬件加法器 (101)实验二十四 8位硬件乘法器 (103)实验二十五数字钟 (105)实验二十六频率计 (107)实验二十七“梁祝”乐曲演奏电路设计 (109)实验二十八 D/A接口电路与波形发生器设计 (111)实验二十九高速A/D采样控制器设计 (113)实验三十ROM设计 (116)实验三十一 RAM设计 (118)实验三十二 FIFO设计 (120)实验三十三键盘控制电路设计 (125)实验三十四带RC的TTL环形振荡器 (128)实验三十五 8人抢答器 (130)第六章扩展实验(高级篇) (132)实验三十六交通灯实验 (132)实验三十七点阵显示实验 (134)实验三十八 PS2键盘接口逻辑设计 (137)实验三十九VGA显示器控制器设计 (139)实验四十RS232通信方式控制电子琴 (142)实验四十一PC机、单片机、CPLD/FPGA双向通信 (144)实验四十二液晶显示控制器 (146)实验四十三电子密码锁实验 (149)实验四十四数字信号单元 (151)实验四十五码形变换 (154)实验四十六数字直接频率合成 (157)实验四十七数字调制解调 (161)实验四十八数字锁相环及位同步提取 (167)实验四十九 QPSK调制解调 (172)实验五十解扰码实验 (177)实验五十一帧同步信号提取单元 (179)实验五十二高速数字相关器设计 (183)实验五十三时分复用 (186)实验五十四差错校验 (192)实验五十五语音录放实验 (198)实验五十六 SPI数据传输语音录放实验 (200)第七章适配板实验(高级篇) (204)实验五十七基于EPM240的全加器实验 (204)实验五十八基于EPM240的反相器实验 (206)实验五十九基于EPM240的数码管显示控制 (208)第一部分ZY11203E实验系统简介一、ZY11203E实验系统主板组成➢通用编程模块➢液晶显示模块➢数码管显示模块➢A/D、D/A转换模块➢LED显示模块➢数字可调信号源➢滤波模块➢信号调节模块➢逻辑笔模块➢配置模块➢模式选择模块➢模拟信号源➢4×4键盘模块➢开关按键模块➢电源模块➢分立元件模块➢喇叭模块➢I/O口插孔➢核心芯片A➢适配板B插座➢扩展板C插座➢40PIN插座二、ZY11203E实验系统各功能模块介绍1、通用编程模块该模块为CPLD/FPGA器件的通用下载电路模块,可以对ALTERA、LATTICE、XILINX 等国际著名的PLD公司几乎所有isp或现场配置的CPLD/FPGA进行编程下载,且能自动识别。

EDA实验指导书全

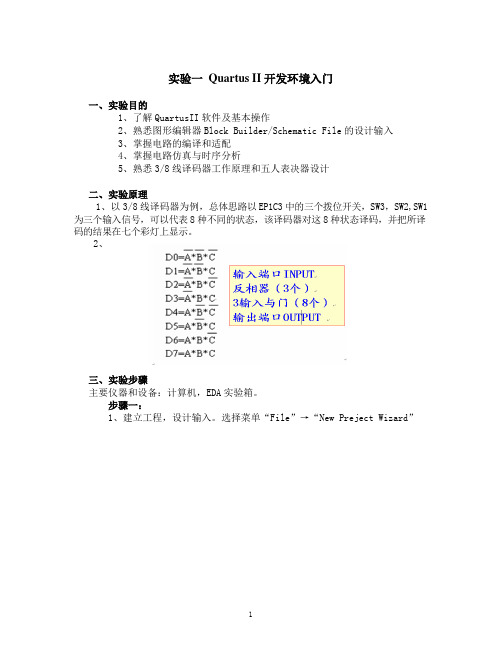

实验一Quartus II开发环境入门一、实验目的1、了解QuartusII软件及基本操作2、熟悉图形编辑器Block Builder/Schematic File的设计输入3、掌握电路的编译和适配4、掌握电路仿真与时序分析5、熟悉3/8线译码器工作原理和五人表决器设计二、实验原理1、以3/8线译码器为例,总体思路以EP1C3中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七个彩灯上显示。

2、三、实验步骤主要仪器和设备:计算机,EDA实验箱。

步骤一:1、建立工程,设计输入。

选择菜单“File”→“New Preject Wizard”将设计文件加入工程中:点击下方的“Next” 按钮,在弹出的对话框中点击“File”栏的按钮,将此工程相关的所有VHDL文件加入进此工程(如果有的话)。

Cyclone系列的EP1C3T144C8按下“Next”后,出现仿真工具选择对话框。

不作任何选择。

4、完成设置点击“Next”后,完成工程的设定,点击“finish”。

步骤二:1、选择File/New或点击主菜单中的空白图标,进入新建程序文件状态,选择VHDL file 。

VHDL程序文件的扩展名是:* .vhd程序代码:-- A simple 3 to 8 decoderlibrary ieee;use ieee.std_logic_1164.all;entity decoder isport ( inp: in std_logic_vector(2 downto 0);outp: out std_logic_vector(7 downto 0)); end decoder;architecture behave of decoder isbeginoutp(0) <= '1' when inp = "000" else '0';outp(1) <= '1' when inp = "001" else '0';outp(2) <= '1' when inp = "010" else '0';outp(3) <= '1' when inp = "011" else '0';outp(4) <= '1' when inp = "100" else '0';outp(5) <= '1' when inp = "101" else '0';outp(6) <= '1' when inp = "110" else '0';outp(7) <= '1' when inp = "111" else '0';end behave;步骤三:1、选择菜单“File”→“New ” →“ Schematic File”,即弹出原理图编辑框。

HK-IV型EDA实验箱说明书

第一章HK-IV型EDA实验系统特点介绍该系统由实验机结合可编程技术开发而成。

适用于Altera、Lattice、Xilinx等多种芯片教学实验。

可使用VHDL、Verilog、AHDL、原理图、状态图等多种方式设计。

主系统仅用一根下载电缆,无需增加任何适配板即可对Lattice、Xilinx、Aitera、Vantis、Atmel和Cypress等公司的不同芯核电压的FPGA/CPLD器件进行在系统编程。

为了适应将来市场发展要求,可以进行软件升级以适应更多型号的FPGA/CPLD。

系统可配置多个公司不同逻辑资源、封装的适配板,且系统主板功能及通用下载电路ASIC的硬件具备可升级性。

(1)系统含标准5V、3V、2.5V、1.8V混合工作电压功率输出电路模块,以便可对适配板上不同芯核电压的FPGA/CPLD器件进行实验和开发。

(2)系统含标准低压(3.3V、2.5V、1.8V),下载口可用于对外部不同芯核电压的FPGA和CPLD器件进行编程下载。

(3)含典型EDA实验必配的标准VGA彩显接口,可用于显卡或工控设备开发(可提供VHDL应用演示实例)。

(4)含典型EDA实验必配的PS/2鼠标、键盘接口(可提供VHDL应用演示实例)。

(5)含典型EDA实验必配的RS232串行接口,同可于硬件串行通信电路开发、编码模块开发等(提供VHDL演示实例)。

(6)含典型EDA实验必配的单片机总线接口及与CPLD/FPGA至PC机双向通信接口(可提供VHDL演示实例)。

此实验为学生提供MCS-51汇编语言、VHDL语言、C语言综合应用设计方面的全面锻炼,为学生在电子设计方面的充分发挥提供了可行的平台。

(7)含LED、数码管、扬声器(通过频率控制可奏乐,提供VHDL演示实例)等。

(8)含8个按键、16个开关,供硬件加法器、乘法器、序列检测器、编码器、音乐演奏、脉宽调制、A/D高速采样等设计实验用(提供VHDL演示实例)。

EDA综合实验箱使用手册.

EDA综合实验箱使用说明手册一.系统概述1. 系统结构及说明系统结构如图1.1所示:图1.1 系统结构框图2. 硬件资源 1.1单片机资源◆完全兼容51内核的SST89E516RD,管脚兼容AT89C51,带仿真监控程序◆时钟频率:0~40MHz ◆集成1KBy片内RAM◆64Kbyte + 8Kbyte Flash EEPROM ◆看门狗◆可编程计数器阵列(PCA)◆SPI接口◆I2C接口1.2可编程逻辑器件资源(EP3C10E144)◆10,320逻辑单元(LE)◆46个M9K◆423,936bit RAM◆23个18*18硬件乘法器◆2个锁相环(PLL)◆10个全局时钟网络◆最大94个用户IO口◆最大22组差分接口1.3常用外围设备资源◆4*4矩阵按键◆8*1独立按键◆8个发光二极管◆8位7段数码管◆字符液晶1602◆点阵液晶12864(带字库)◆蜂鸣器◆8K串口存储器(仅单片机模式可用)◆10位高精度AD转化器(仅单片机模式可用)◆12位高精度DA转换器二.操作说明1. 人机交互模块功能说明该模块是本EDA实验箱的人机对话界面,主要实现对本EDA实验箱的模式选择、电压测量、信号输出、频率测量以及系统复位等功能。

其主要部件及功能如表2.1所示:2. 实验箱上电或复位当实验箱初次上电或者按Reset(复位)键,都将进入初始化界面,该界面将显示重庆邮电大学徽标以及实验平台的名称、制作者等信息,随后即自动进入功能选择界面。

如图2.1所示:图2.1 功能选择界面功能1:电压测量能够完成对实验箱上+5V、+3.3V两路电源电压以及外接直流电压(VT)的测量。

功能2:信号输出能够同时产生多路不同频率的方波信号,频率调节范围(1Hz~1MHz)。

功能3:频率测量可以测量外接频率(FT)。

功能4:模式选择实现不同工作模式间的切换。

目前本实验箱共设计有9种不同的工作模式(模式0~模式8),不同模式对应有不同的电路结构,各模式下的电路结构图可参见模式介绍。

EDA实验教程

实验箱的使用说明本实验箱无需添加其它设备,仅需与计算机连接便可进行所有实验。

硬件安装及使用中需要注意的几个步骤如下:1、打开实验箱,检查并核实设备完好及附件齐全;2、检查下载编程电缆标识:不同公司的编程电缆是不同的,如Altera公司的编程电缆出厂时标有Altera字样、Lattice公司的的电缆有两种:一种是数字器件编程电缆,标有Lattice字样;另一种是模拟芯片编程电缆,其上标有PAC字样,其它厂家类似。

使用时一定要注意编程电缆不能混用,否则程序不能正确下载。

同一厂家的CPLD/FPGA芯片的下载电缆是一样的。

3、安装下载编程电缆:确保欲安装的下载电缆与当前实验箱上适配器芯片相一致,然后将其25针的接插头连接到计算机的并行口上,另一端连接到实验箱的JTAG编程座上,并确保电缆两断接触良好。

4、开启实验箱电源,电源指示灯亮。

本电源为5V开关电源,有短路及自恢复等功能。

如电源指示灯不亮,请检查是否已接入220V电源或由其它原因所致。

5、硬件安装结束,并打开实验箱电源,此时便可进行软件编程下载。

程序正常下载时其编程接口旁边的状态指示灯处于闪烁状态,如不能正确下载请检查是硬件问题还是软件设置问题?如不能最终排除故障请急时与我们联系。

6、实验时严禁带电接插,以防损坏电路芯片。

如有异常要急时切断电源并排除故障。

实验设备:计算机EDA试验箱MaxplusII 软件连接导线实验一原理图输入设计方式一、实验目的:1、通过一个简单的 3-8 译码器的设计,让学生掌握原理图输入方式。

2、掌握组合逻辑电路的静态测试方法。

3、初步了解可编程器件设计的全过程。

二、实验步骤:MaxplusII 软件的基本操作与应用(一)设计输入:1、软件的启动:进入 Altera 软件包,打开MAX+plus II 10.0 软件,如图 11所示。

实验二:简单组合逻辑设计一、实验前准备本实验例子使用独立扩展下载板EP1K10_30_50_100QC208(芯片为EP1K100QC208)。

EDA实验指导书_实验指导06_EDA_硬件综合实验

“电子设计自动化(EDA)”实验指导书(六)一、实验课程编码:105009二、实验课程名称:电子设计自动化(EDA)三、实验项目名称:综合硬件实验二(带时分秒按键调整和静态数码管显示的数字钟)四、实验目的1)学会看硬件原理图,2)掌握FPGA硬件开发的基本技能3)培养EDA综合分析、综合设计的能力五、主要设备1)PC机,2)硬件实验箱,3)Max plusII软件开发平台。

六、实验内容1.6个数码管静态显示驱动2.按键模式选择(时\分\秒)与调整控制3.用硬件描述语言(或混合原理图)设计时、分、秒计数器模块、按键控制状态机模块、显示译码模块、顶层模块。

要求使用实验箱右下角的6个静态数码管(DS8C, DS7C, DS4B, DS3B, DS2B, DS1B)显示时、分、秒;要求模式按键和调整按键信号都取自经过防抖处理后的按键跳线插孔。

七、实验步骤1.打开Max plusII ,连接实验箱上的相关硬件资源,如下图1所示。

2.建立新文件,选择文本类型或原理图类型。

3.编写程序。

4.编译5.仿真,加载程序到芯片,观察硬件输出结果(数码管显示)6.结果正确则完成。

若结果不正确,则修改程序,再编译,直到正确。

图1 综合硬件实验二对应的硬件资源连接八、实验结果直接观察实验箱的数码管显示、操作按键进行控制和调整。

数字钟包括正常的时分秒计时,DS2B DS1B.125 H z.25 H z.5 H zH zH zH zH z4 H z56 H z024 H z096 H z6384 H z2768 H z5536 H z50 K H z.5 M H zM H zM H z2 M H z4 M H zHour 00-23 Minute 00-59Second 00-59实验箱右下角的6个静态数码管(DS8C, DS7C, DS4B, DS3B, DS2B, DS1B)显示时、分、秒。

adjust 递增调整时分秒,mode按键循环调整模式。

EDA技术实验指导书

《EDA技术》实验指导书电子信息工程教研室编写第一章EL-SOPC4000实验系统的资源介绍一、系统功能概述EL-SOPC4000实验箱是集EDA 和SOPC 开发为一体的综合性实验箱,它不仅可以独立完成各种EDA 设计,也可以完成多种SOPC开发。

主CPU适配器E-PLAY-SOPC配合EL-SOPC4000底板,可完成各种基本的EDA实验。

在实验板上有丰富的外围扩展资源,有常用的按键,拨码开关,LED灯,蜂鸣器,交通灯,16x16点阵,数码管,4x4矩阵键盘,AD/DA,CAN功能单元,RS232,RS485,可调时钟输出。

实验板上还集成了一个8寸的VGA接口的液晶屏,可完成视频图像的显示。

由于CPU 适配器E-PLAY-SOPC本身具有E_PLAY接口,只需提供电源即可独立完成功能测试,也可控制用户开发的E_PLAY接口模块。

由于EL-SOPC4000底板加入了两路E_LAB外扩接口,可以配合公司现有的多种E_LAB模块,来完成大学生毕业设计、电子设计竞赛、及创新设计,同时该系统也是从事教学及科研的广大教师和工程师们的理想开发工具,具有极高的灵活性,开放性和可开发性。

EL-SOPC4000布局如下图所示:EL-SOPC4000底板资源平面图EL-SOPC4000实验箱是集EDA和SOPC 开发为一体的综合性实验箱,它不仅可以独立完成各种EDA设计,也可以完成多种SOPC开发。

EL-SOPC4000支持的CPU板卡有:具有E_PLAY接口的E-PLAY-SOPC适配器,主芯片采用Altera公司的CycloneII系列E-PLAY-EP235,CycloneIII系列E-PLAY-EP3C25-B、E-PLAY-EP3C80,CycloneIV系列E-PLAY-EP4CE22。

二、系统硬件资源1、EL-SOPC4000实验系统的硬件资源总览☆E-PLAY CPU板接口单元☆ E_LAB模块接口单元(2组)☆ 16个用户IO单元☆ 16个按键单元☆ 16个拨码开关单元☆ 4x4矩阵键盘单元☆ 16X16 LED点阵显示单元☆ 8位数码管显示单元☆ 12个交通灯单元☆蜂鸣器及4个LED声光单元☆ 8位用户LED单元☆可调时钟输出单元☆ RS232 、RS485接口单元☆ 10位串行AD(TLV1570)单元☆ 10位串行DA(TLV5617)单元☆ CAN总线接口单元☆ 8寸VGA接口液晶屏单元(带触摸屏)2、底板资源的具体介绍1)PORT A信号分配PORT B信号分配说明:标有“NC”的引脚,表示没有用到适配器上的引脚;2)E-LAB总线接口底板上的两组E-LAB接口上的信号线完全相同。

EDA实验指导书

实验一QuartusII软件和实验箱控制软件EDA2000使用流程[实验目的]1.掌握CPLD/FPGA的开发软件QuartusII的操作流程;2.掌握实验箱控制软件EDA2000的使用,熟悉EDA2000的实验箱结构。

[实验仪器]PC机1台QuartusII 软件1套EDA2000实验箱一个,并行电缆、串行电缆各一根。

[实验步骤]QuartusII软件使用世界各大FPGA/CPLD生产商都有自己的EDA开发环境,也有专业的第三方EDA软件。

ALTERA公司的QuartusII是Altera公司的第四代EDA集成开发环境,它操作方便、功能强大,提供了原理图输入和HDL语言输入功能,在环境中可以完成编译、查错、设计驱动信号、逻辑功能模拟、时序功能模拟、对FPGA/CPLD芯片编程以及SOPC的设计开发等功能。

下面以V erilog HDL语言输入设计为例,一步一步描述在QuartusII开发环境中如何完成FPGA/CPLD开发的设计流程。

本实验中利用V erilogHDL在FPGA里面设计一个与门,请同学们按照以下步骤操作:a)在e盘新建一个目录e:\fpga\experiment1,用于存放本次实验中的设计文件。

b)按图1-1操作打开QuartusII 7.2软件图1-1c)界面如下图1-2d)点击菜单File–〉New Project Wizard出现如下图,点击Next图1-3e) 在出现的对话框中按下图设置:f)点击Next ,出现如下对话框,本对话框要求加入文件到项目中,由于是新建项目,还没有设计文件,故空着,点击Next 。

项目顶层文件名称,通常与项目名称一致g)选择选择器件:这里的器件就是指每个设计所使用的FPGA或CPLD芯片,ALTERA公司具有代表性的FPGA为FLEX 10K系列的EPFl0K10LC84-4。

具有代表性的CPLD为MAX7000S系列的EPM7128SLC84-15。

《EDA技术与应用》实验指导书(新)

《EDA技术与应用》实验指导书第一部分基础实验实验一 EDA软件的熟悉与使用一、实验目的1.熟悉ALTERA公司EDA设计工具软件Quartus II的使用方法。

2.熟悉EDA技术实验箱的结构与组成。

二、实验原理参考教材Quartus II开发软件的使用方法。

三、实验仪器1.计算机2.EDA技术实验箱四、实验内容1.在教师指导下完成Quartus II软件的安装,熟悉Quartus II软件主要菜单命令功能。

2.熟悉EDA技术实验箱结构、组成,了解各模块的基本作用,了解I/O分布情况。

3.参考1位半加器的设计实例,按照设计流程完成新建项目文件、编译、仿真、分配引脚、编程下载等操作,掌握采用Quartus II软件设计流程。

五、实验报告1.绘制出Quartus II软件设计的详细流程图。

2.描述Quartus II软件是如何进行目标器件选择,I/O分配和锁定引脚的。

3.描述Quartus II软件Help菜单功能,如何有效地使用它。

4.写出EDA技术实验箱的I/O分布情况。

六、思考题在进行一个完整的实验流程时应注意些什么?实验二 1位半加器的设计一、实验目的1.掌握Quartus II软件设计流程。

2.熟悉原理图输入设计方法。

二、实验原理1位半加器可以用一个与门、一个异或门组成。

设加数和被加数分别为a、b,和为so、进位co,则半加器表达式为:co=a and b;so=a xor b。

三、实验仪器1.计算机(预装Quartus II软件)2.EDA技术实验箱。

四、实验内容1.为本项工程设计建立一个文件夹任何一项设计都是一项工程(Project),都必须首先为此工程建立一个放置与此工程相关的文件的文件夹,此文件夹将被EDA软件默认为工作库(Work Library)。

一般不同的设计项目最好放在相应的文件夹中,注意,一个设计项目可以包含多个设计文件。

例如,本项设计的文件夹取名为h_adder,路径为E:\ h_adder。

EDA实验箱实验指导书

实验二流水灯1.实验目的通过本实验让学生进一步了解、熟悉和掌握CPLD/FPGA开发软件的使用方法及VHDL 语言的编程方法;学习简单的时序电路的设计和硬件测试。

2.实验内容本实验的内容是控制实验箱上的发光二极管LED1—LED8,使之实现流水灯显示。

3.实验原理在LED1~LED8引脚上周期性地输出流水数据,即输出的数据依次为11111111、11111110、11111100、11111000、11110000、11100000、11000000、10000000、00000000,如此循环显示,输出数据“0”,表示点亮相应的LED小灯。

为了方便观察,流水的速率控制在2Hz左右。

在核心板上有一个48MHz的标准时钟源,该时钟源与芯片EP2C5的23脚相连。

为了产生2Hz的时钟源,在此调用了分频模块int_div。

4.实验步骤(1)启动Quartus II,建立一个空白工程,然后命名为led_waterflow.qpf。

(2)新建ledwater.vhd源程序文件,源代码如下。

然后进行综合编译。

若在编译过程中发现错误,则找出并更正错误,直到编译成功为止。

生产符号文件ledwater.bsf (File→ Create/_Update → Create Symbol Files for Current File)。

流水灯程序参考LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_Arith.ALL;USE IEEE.STD_LOGIC_Unsigned.ALL;ENTITY ledwater ISPORT(clk: IN STD_LOGIC;led: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END;ARCHITECTURE one OF ledwater ISSIGNAL led_r:STD_LOGIC_VECTOR(8 DOWNTO 0);BEGINled<=led_r(7 DOWNTO 0);PROCESS(clk)BEGINIF clk’event and clk=’1’ THENled_r<=led_r(7 DOWNTO 0) & '0';IF led_r="000000000" THEN --循环完毕吗?led_r<="111111111"; --是,则重新赋初值END IF;END IF;END PROCESS;END;(3)将实验模块库里的int_div.vhd和int_div.bsf拷贝到工程目录下。

康芯GW48EDA实验箱使用介绍

(8) 数码管 1~8/发光管 D1~D16 :也受“多任务重配置”电路控制,它们的连线形式也需参照 第二节的电路图。

(9) 数码管 9~14/发光管 D17~D22 :不受“多任务重配置”电路控制(仅 GW48—GK/PK 型含 此发光管),它们的连线形式和使用方法参考“实验电路结构 NO.5”。

滤波1on即连接滤波电容滤波1103连接pio37与comp72kpio31pio29pio30pio28pio27pio26pio25pio2413141516d7d6d5d4d3d1d0pio37551pfc27complm311vcc10k1212tl0821ain0aout51kr721212commeu2dac0832181710wr1fb11iout1iout212cswr2xfergndvrefvcc20vccd1pio8d2d3d4d5d6d7d8pio9pio10pio11pio12pio15pio14pio13实验电路结构图no5扬声器fpgacpld目标芯片d16d15d14d13d12d11d10d9pio47pio44pio43pio40pio39pio36pio35pio32pio31pio28pio27pio24pio23pio20pio19pio16译码器译码器译码器译码器译码器译码器译码器译码器pio15pio8pio0pio1pio2pio3pio4pio5pio6pio7右侧的ramrom是pio8左侧的ramrom是pio62gndvccpio62pio8pio49ramroma18a19a18a15wepio26pio25pio24pio32pio33pio34pio35pio36pio37pio38pio39pio14pio47pio10pio48pio9pio46pio45pio11pio12pio13pio15pio31pio30pio29pio28pio273231302928272625242322212019181716151413121110vccgnd2708027040270202701027512272562764628128622566264vcca17vccwra14a13a8a9a11oea10cs1d7d6d5d4d3gndd2d1d0a0a1a2a3a4a5a6a7a12a14a15a16附图27实验电路结构图no513d16d15d14d13d12d11d9d8pio47d7pio46d6pio45d5pio44d4pio43d3pio42d2pio41pio40d1no7实验电路结构图扬声器fpgacpld目标芯片pio0pio2pio3pio4pio5pio6pio7单脉冲单脉冲单脉冲pio47pio40pio39pio36pio35p

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA实验箱使用手册第一章 GW48 SOC/EDA 系统使用说明第一节 GW48教学实验系统原理与使用介绍一、GW48系统使用注意事项a :闲置不用GW48 EDA/SOC 系统时,关闭电源,拔下电源插头!!!b :EDA 软件安装方法可参见光盘中相应目录中的中文README.TXT ;详细使用方法可参阅本书或《EDA 技术实用教程》、或《VHDL 实用教程》中的相关章节。

c :在实验中,当选中某种模式后,要按一下右侧的复位键,以使系统进入该结构模式工作。

d :换目标芯片时要特别注意,不要插反或插错,也不要带电插拔,确信插对后才能开电源。

其它接口都可带电插拔(当适配板上的10芯座处于左上角时,为正确位置)。

e :对工作电源为5V 的CPLD (如1032E/1048C 、95108或7128S 等)下载时。

最好将系统的电路“模式”切换到“ b ”,以便使工作电压尽可能接近5V 。

g: GW48详细使用方法可参见《EDA 技术实用教程》配套教学软件*.ppt 。

h:主板左侧3个开关默认向下,但靠右的开关必须打向上(DLOAD ),才能下载。

i:跳线座“SPS ” 默认向下短路(PIO48);右侧开关默认向下(TO MCU )。

j:左下角拨码开关除第4档“DS8使能”向下拨(8数码管显示使能)外,其余皆默认向上拨。

二、GW48系统主板结构与使用方法附图1-1A 为GW48-CK 型EDA 实验开发系统的主板结构图(GW48-GK/PK 型未画出,具体结构说明应该参考实物主板),该系统的实验电路结构是可控的。

即可通过控制接口键SW9,使之改变连接方式以适应不同的实验需要。

因而,从物理结构上看,实验板的电路结构是固定的,但其内部的信息流在主控器的控制下,电路结构将发生变化。

这种“多任务重配置”设计方案的目的有3个:1.适应更多的实验与开发项目;2. 适应更多的PLD 公司的器件;3. 适应更多的不同封装的FPGA 和CPLD 器件。

系统板面主要部件及其使用方法说明如下(请参看相应的实验板板面和附图1-1A )。

以下是对GW48系统主板功能块的注释,但请注意,有的功能块仅GW48-GK 获GW48-PK 系统存在: (1) SW9 :按动该键能使实验板产生12种不同的实验电路结构。

这些结构如第二节的13 张实验电路结构图所示。

例如选择了“NO.3”图,须按动系统板上的SW9键,直至数码管SWG9显示“3”,于是系统即进入了NO.3 图所示的实验电路结构。

附图1-1B 、GW48-GK/PK 系统目标板插座引脚信号图世界上最大的六家FPGA/CPLD厂商几乎所有CPLD、FPGA和所有ispPAC等模拟EDA器件。

第三节的表中已列出多种芯片对系统板引脚的对应关系,以利在实验时经常查用。

(3)J3B/J3A:如果仅是作为教学实验之用,系统板上的目标芯片适配座无须拔下,但如果要进行应用系统开发、产品开发、电子设计竞赛等开发实践活动,在系统板上完成初步仿真设计后,就有必要将连有目标芯片的适配座拔下插在自己的应用系统上(如GWDVP板)进行调试测试。

为了避免由于需要更新设计程序和编程下载而反复插拔目标芯片适配座,GW48系统设置了一对在线编程下载接口座:J3A和J3B。

此接口插座可适用于不同的FPGA/CPLD(注意,1、此接口仅适用于5V工作电源的FPGA和CPLD;2、5V工作电源必须由被下载系统提供)的配置和编程下载。

对于低压FPGA/CPLD,(如EP1K30/50/100、EPF10K30E等,都是 2.5V器件),下载接口座必须是另一座:ByteBlasterMV。

注意,对于GW48-GK/PK,只有一个下载座:ByteBlasterMV,是通用的。

(4)混合工作电压使用:对于低压FPGA/CPLD目标器件,在GW48系统上的设计方法与使用方法完全与5V器件一致,只是要对主板的跳线作一选择(对GW48-GK/PK系统不用跳线):JVCC/VS2:跳线JVCC(GW48—GK/PK型标为“VS2”)对芯片I/O电压3.3V(VCCIO)或5V (VCC)作选择,对5V器件,必须选“5.0V”。

例如,若系统上插的目标器件是EP1K30/50/100或EPF10K30E/50E等,要求将主板上的跳线座“JVCC”短路帽插向“3.3V”一端;将跳线座“JV2”短路帽插向“+2.5V”一端(如果是5V器件,跳线应插向“5.0V”)。

(5)并行下载口:此接口通过下载线与微机的打印机口相连。

来自PC机的下载控制信号和CPLD/FPGA的目标码将通过此口,完成对目标芯片的编程下载。

编程电路模块能自动识别不同的CPLD/FPGA芯片,并作出相应的下载适配操作。

(6)键1~键8 :为实验信号控制键,此8个键受“多任务重配置”电路控制,它在每一张电路图中的功能及其与主系统的连接方式随SW9的模式选择而变,使用中需参照第二节中的电路图。

(7)键9~键12 :实验信号控制键(仅GW48—GK/PK型含此键)此4个键不受“多任务重配置”电路控制,使用方法参考“实验电路结构 NO.5”。

(8)数码管1~8/发光管D1~D16 :也受“多任务重配置”电路控制,它们的连线形式也需参照第二节的电路图。

(9)数码管9~14/发光管D17~D22 :不受“多任务重配置”电路控制(仅GW48—GK/PK型含此发光管),它们的连线形式和使用方法参考“实验电路结构 NO.5”。

(10)“时钟频率选择”P1A/JP1B/JP1C :为时钟频率选择模块。

通过短路帽的不同接插方式,使目标芯片获得不同的时钟频率信号。

对于“CLOCK0”JP1C,同时只能插一个短路帽,以便选择输向“CLOCK0”的一种频率:信号频率范围: 1Hz – 50MHz(对GW48-CK系统)信号频率范围: 0.5Hz – 50MHz(对GW48-GK系统)信号频率范围: 0.5Hz – 100MHz(对GW48-PK系统),由于CLOCK0可选的频率比较多,所以比较适合于目标芯片对信号频率或周期测量等设计项目的信号输入端。

JP1B分三个频率源组,即如系统板所示的“高频组”、“中频组”和“低频组”。

它们分别对应三组时钟输入端。

例如,将三个短路帽分别插于JP1B座的2Hz、1024Hz和12MHz;而另三个短路帽分别插于JP1A座的CLOCK4、CLOCK7和CLOCK8,这时,输向目标芯片的三个引脚:CLOCK4、CLOCK7和CLOCK8分别获得上述三个信号频率。

需要特别注意的是,每一组频率源及其对应时钟输入端,分别只能插一个短路帽。

也就是说,通过JP1A/B的组合频率选择,最多只能提供三个时钟频率。

注意,对于GW48-GK/PK系统,时钟选择比较简单:每一频率组仅接一个频率输入口,如低频端的4个频率通过短路帽,可选的时钟输入口仅为CLOCK2,因此对于GW48-GK/PK,总共只有4个时钟可同时输入FPGA:CLOCK0、CLOCK2、CLOCK5、CLOCK9。

(11)扬声器S1:目标芯片的声讯输出,与目标芯片的“SPEAKER”端相接,即PIO50。

通过此口可以进行奏乐或了解信号的频率。

(12)PS/2接口:通过此接口,可以将PC机的键盘和/或鼠标与GW48系统的目标芯片相连,从而完成PS/2通信与控制方面的接口实验,GW48-GK/PK含另一PS/2接口,参见实验电路结构 NO.5。

(13)VGA视频接口:通过它可完成目标芯片对VGA显示器的控制。

(14) 单片机接口器件:它与目标板的连接方式也已标于主系统板上:连接方式可参见附图2-13。

注意1,对于GW48-GK/PK系统,实验板左侧有一开关,向上拨,将RS232通信口直接与FPGA的PIO31和PIO30相接;向下拨则与89C51单片机的P30和P31端口相接。

于是通过此开关可以进行不同的通信实验,详细连接方式可参见附图2-13。

平时此开关向下打,不要影响FPGA的工作。

注意2,由附图2-13可知,单片机89C51的P3和P1口是与FPGA的PIO66-PIO79相接的,而这些端口又与6数码管扫描显示电路连在一起的,所以当要进行6数码管扫描显示实验时,必须拔去右侧的单片机,并安实验电路结构 NO.5,将拨码开关3,拨为使能,这时LCD停止工作。

(15) RS-232串行通讯接口:此接口电路是为单片机与PC机通讯准备的,由此可以使PC机、单片机、FPGA/CPLD三者实现双向通信。

当目标板上FPGA/CPLD器件需要直接与PC机进行串行通讯时,可参见附图2-13,和实验电路结构图NO.5,将实验板右侧的开关向上打“TO FPGA”,从而使目标芯片的PIO31和PIO30与RS232口相接,即使RS232的通信接口直接与目标器件FPGA的PIO30/PIO31相接。

而当需要使PC机的RS232串行接口与单片机的P3.0和P3.1口相接时,则应将开关向下打“TO MCU”既可(平时不用时也应保持在个位置)。

(16)“AOUT” D/A转换:利用此电路模块(实验板左下侧),可以完成FPGA/CPLD目标芯片与D/A转换器的接口实验或相应的开发。

它们之间的连接方式可参阅“实验电路结构 NO.5”:D/A 的模拟信号的输出接口是“AOUT”,示波器可挂接左下角的两个连接端。

当使能拨码开关8:“滤波1”时,D/A的模拟输出将获得不同程度的滤波效果。

注意,进行D/A接口实验时,需打开左侧第2个开关,获得+/-12伏电源,实验结束后关上此电源。

(17)“AIN0”/“AIN1”:外界模拟信号可以分别通过系统板左下侧的两个输入端“AIN0”和“AIN1”进入A/D转换器ADC0809的输入通道IN0和IN1,ADC0809与目标芯片直接相连。

通过适当设计,目标芯片可以完成对ADC0809的工作方式确定、输入端口选择、数据采集与处理等所有控制工作,并可通过系统板提供的译码显示电路,将测得的结果显示出来。

此项实验首先需参阅第二节的“实验电路结构NO.5”有关0809与目标芯片的接口方式,同时了解系统板上的接插方法以及有关0809工作时序和引脚信号功能方面的资料。

注意:不用0809时,需将左下角的拨码开关的“A/D使能”和“转换结束”打为禁止:向上拨,以避免与其他电路冲突。

ADC0809 A/D转换实验接插方法(如实验电路结构 NO.5图所示):1.左下角拨码开关的“A/D使能”和“转换结束”打为使能:向下拨,即将ENABLE(9)与PIO35相接;若向上拨则禁止,即则使ENABLE(9)←0,表示禁止0809工作,使它的所有输出端为高阻态。

2.左下角拨码开关的“转换结束”使能,则使EOC(7)←PIO36,由此可使目标芯片对ADC0809的转换状态进行测控。