最新4第四讲定点乘法器

定点源码一位乘法器的设计内容结论

定点源码一位乘法器的设计内容结论篇一:设计一个定点源码一位乘法器可以帮助我们更好地理解计算机内部如何进行乘法运算。

本文将介绍一个定点源码一位乘法器的设计方案,包括其基本结构和实现方式,结论是这种乘法器在计算机内部可以实现,并且具有高效的性能。

首先来看乘法器的基本原理。

乘法是将两个数相乘得到的结果存储在两个数的对应位上,然后根据乘积的二进制表示将结果进行位运算得到最终的答案。

对于一位乘法器,其基本操作如下:1. 读取两个数,并将它们存储在一个临时变量中。

2. 对两个数进行位运算,将乘积的对应位设置为1,其他位设置为0。

3. 将结果存储回原来的两倍位置。

下面我们来具体实现一个一位乘法器。

首先,我们需要选择一种编程语言来实现乘法器。

由于一位乘法器只涉及两个数的不同位,因此选择C语言作为实现语言。

接下来,我们需要设计一个乘法器的数据结构。

对于一位乘法器,我们只需要将乘积的二进制表示存储在一个数组中,而不需要存储中间结果。

因此,我们可以使用一个二进制数组来实现一位乘法器。

接下来,我们来实现乘法器的代码。

首先,我们初始化两个数组,一个用于存储乘积的二进制表示,另一个用于存储中间结果。

然后,我们使用位运算来实现乘法操作。

具体地,我们按照以下步骤进行操作:1. 读取两个数。

2. 对两个数进行位运算。

3. 将乘积的对应位设置为1,其他位设置为0。

4. 将结果存储回原来的两倍位置。

下面是完整的代码实现:```c#include <stdio.h>#include <stdlib.h>#define MAX_INT 32767// 乘法器数据结构typedef struct {int value;int bit[2];} 乘积;// 初始化乘积void init_积(乘积*积) {积->value = 0;for (int i = 0; i < 2; i++) {积->bit[i] = 0;}}// 读取两个数int read_nums(乘积*积, int num1, int num2) { 乘积 temp;init_积(&temp);int carry = 0;for (int i = 0; i < 8; i++) {int bit = (num2 >> i) & 1;temp.bit[i] = bit;if (bit) {carry++;}}temp.value = carry ? (temp.value + num1) : num1;return temp.value;}// 位运算void bit_Ops(乘积*积, int num1, int num2, int bit) { if (bit) {积->bit[2 * bit - 1] = num2 & 1;}}// 打印结果void print_result(乘积*积, int num1, int num2) {for (int i = 0; i < 2; i++) {printf("%d ",积->bit[i]);}printf("");}int main() {乘积积1,积2;int num1, num2;printf("请输入两个整数:");scanf("%d%d", &num1, &num2);printf("请输入第一个整数:");scanf("%d", &积1.value);printf("请输入第二个整数:");scanf("%d", &积2.value);printf("请输入第一个整数的位数: ");scanf("%d", &积1.bit[0]);printf("请输入第二个整数的位数: ");scanf("%d", &积2.bit[0]);printf("计算结果为:");printf("%d", read_nums(积1, num1, num2));printf("计算结果的位数:");printf("%d ",积1.bit[2 *积1.bit[0] - 1]);printf(" ");printf("计算结果的进位:");printf("%d ",积2.bit[2 *积2.bit[0] - 1]);printf(" ");return 0;}```根据上面的代码,我们可以得到一位乘法器的基本结构。

最新 《计算机组成原理》之定点运算器的课件设计与开发-精品

摘要:《组成原理》之定点运算器的课件设计与开发利用Flash的强大功能,它集成了文字、图像、声音、动画、视频等多媒体信息,能更好的实现多媒体教学,使学习者加深对所学知识的理解,提高学生学习兴趣和教学效率,同时也能为课件增加生动的效果。

《计算机组成原理》之定点运算器的课件共设计和开发了6个模块:“数据与文字的表示方法”、“定点加减运算”、“定点乘法运算”、“定点除法运算与阵列除法器”、“定点运算器的组成”、“浮点运算方法和浮点运算器”。

关键词:计算机组成原理;定点运算器;Flash;Photoshop 中图分类号:TP393文献标识码:A文章编号:1009-3044(2011)28-6988-02 The Courseware Design and Development for the Fixed-point Arithmetic in the Principle of Computer Organization CHEN Si-si, WANG Feng (College of Physics and Electronic Information Engineering, Wenzhou University, Wenzhou 325035, China) Abstract: The courseware design and development for the fixed-point arithmetic in the Principles of Computer Composition includes six modules: "the representation of data and text", "fixed-point addition and subtraction", "the multiplication of fix-point", "the divide of fix-point and the array of the division", "the composition of the fix-point arithmetic", "the methods of the floating point and the floating arithmetic". Key words: multimedia; constitution principle of computer; fix-point arithmetic; flash 目前,《计算机组成原理》之定点运算器[1-2]的课件仅限于用Powerpoint制作,用这种技术做的PPT很枯燥不能调动学生学习的兴趣,而用Flash制作课件可以生动形象的描述各种教学问题,有效激发学生的学习兴趣,增加教学效果,提高教学效率,具有传统教学所不能比拟的优越性。

《定点乘法器》PPT课件知识讲解

数学特征

N

n1

ai 2i i0

n1

[1 i0 (1 ai )2i ]

an 0 an 1

n1

统一表示为 Nan2n ai2i i0

负权因数

22

计算

例1:已知[X]补=01101, [Y]补=10101, 求它们表示的数值?

23

直接补码阵列乘法

以5位二进制乘法为例。A=(a4)a3a2a1a0 B=(b4)a3a2a1a0

带权输入

XYZ -X -Y -Z

000 001 010 011 100 101 110 111

X Y -Z -X -Y Z

000 001 010 011 100 101 110 111

带权输出

CS -C -S

00 01 01 10 01 10 10 11

C -S -C S

00 01 11 00 11 00 10 11

4

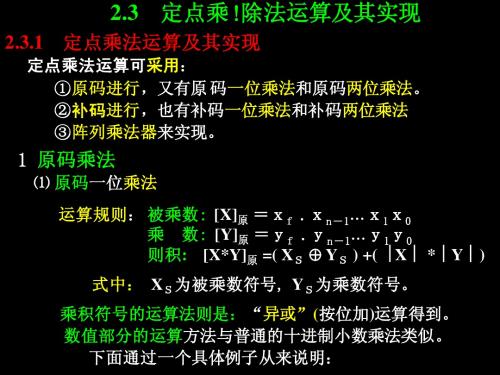

一 定点数原码乘法

1 原码的乘法 基本思想:每次用乘数的一位去乘被乘数。 (1).算法分析 例. 0.1101×1.1011

乘积 P = X × Y 符号 SP= SX⊕SY

5

实例

0.1101

×0.1011 1101

1101 0000 1101

部分积

0.10001111 上符号:1.10001111 问题:1)加数多(由乘数位数决定)。

ai*=ai⊕ECi-1,

0≤i≤n

17

求补器

说明: 按位扫描的方法,进行求补的方法就是从

数的最右端a0开始,,由右向左,直到找出第 一个“1”,ai以左的每一个输入位都求反, 即1变0,0变1。 当控制信号线E为“1”时,启动对2求补的操 作。E为“0”时,输出将和输入相等。 最右端的起始链式输入C-1必须永远置成 “0”。

最新第四讲 定点运算(乘法)精品课件

右移一位 = 0.1{A +0.1[ 0 • A+0.1(A + 0.1A)]}

= 2-1{A +2-1[ 0 • A+2-1(A + 2-1(A+0))]}

第一步 被乘数A + 0

①

第二步 右移(yòu yí) 一 位,得新的部 分积

第三步 部分积 + 被乘数

② ③

…

第八步 右移(yòu yí) 一 位,得结

最后 加[–x]补,校正

第十八页,共41页。

Booth乘法公式(gōngshì)

证明

1)、当被乘数x符号任意,乘数y符号为正时(zhènɡ

shí):

根据[[yx补]]补补码=定= 0x义0.y:.x1y1x22LLyxnn==y2 + x = 2n+1 + x

(mod2)

∴ [x]补 [y]补 = 2n+1 y + x y = 2(y1y2 yn ) + x y

= [ x]补[ y0 + ( y1 y121) + ( y2 21 y2 22 ) + + ( yn 2(n1) yn 2n )]

= [ x]补[( y1 y0 ) + ( y2 y1)21 + + ( yn yn1)2(n1) + (0 yn )2n ]

= [ x]补[( y1 y0 ) + ( y2 y1)21 + + ( yn+1 yn )2n ]

(fú∵hào[[)yxy为]]补=补负[==y时]1x补:.0y.x12y1x=22L1L.yy1xnyn2=L2y+n

y

定点数的乘法运算

定点数的乘法运算定点数是在计算机科学和电子工程领域广泛使用的数值表示方法。

与浮点数相比,定点数更加精确和高效,在很多应用领域中都具有重要的价值。

乘法是数学中最基本和常用的运算之一,在定点数的表示和计算中也扮演着重要的角色。

本文将探讨定点数的乘法运算,以及相关的应用和优化技术。

首先,我们来简单回顾一下定点数的表示方法。

定点数是用固定的小数位数来表示实数的一种方法,通常由整数部分和小数部分组成。

整数部分的位数决定了定点数的整数范围,而小数部分的位数决定了定点数的精度。

定点数可以通过将实数乘以2的n次幂并进行取整来表示,其中n是小数部分的位数。

例如,定点数1.75可以表示为二进制数1.11(.75的二进制表示)。

在定点数的乘法运算中,我们需要考虑几个重要的因素。

首先是溢出问题。

由于定点数的整数范围是有限的,当乘法结果超出了这个范围时,就会发生溢出。

为了解决这个问题,我们可以使用溢出检测和截断技术,确保乘法结果在有效范围内。

另一个重要的因素是精度损失。

由于定点数的小数部分位数是固定的,当两个较大的定点数相乘时,乘积的小数部分位数可能会增加,导致精度损失。

为了减少精度损失,我们可以使用扩展精度技术,通过增加定点数的位数来提高计算的精度。

在实际应用中,定点数的乘法运算具有广泛的应用。

例如,在图像处理领域,定点数的乘法运算用于计算图像的亮度、对比度和色彩等。

在数字信号处理中,定点数的乘法运算用于滤波器的设计和信号的调制等。

此外,定点数的乘法运算还被广泛应用于嵌入式系统和通信系统中,用于实现高效的算法和数据传输。

为了提高定点数的乘法运算的效率和性能,许多优化技术被提出和应用。

其中一个重要的技术是快速乘法算法。

快速乘法算法通过分解乘法操作,降低乘法运算的复杂度,从而提高计算的速度。

另一个优化技术是乘法积累器的使用。

乘法积累器是一种专门设计的硬件电路,能够支持快速的定点数乘法运算,大大提高了计算的效率。

除了乘法运算本身,定点数的乘法还与其他运算密切相关。

43定点乘法运算

解:符号:Zs= Xs⊕Ys = 0⊕1 = 1

CF

部分积

0 0000

+1 1 0 1

乘 数 Y0 1011

0 1101 0 0110

+1 1 0 1 1 0011 1 1001

+0 0 0 0

0 1001

0 0100 +1 1 0 1

1 0001 0 1000

1101 1110 1111 1111

Y=Y补-2=y0+y1·2-1+······+yn·2-n - 2y0 = -y0·20+y1·2-1+······+yn·2-n

两式可合写为:

Y=-y0·20+y1·2-1+······+yn·2-n

11

∵ 2n-1 = 2n - 2n-1

Y =-y0·20+ y1·2-1+ ···+ yn-1·2-(n-1) +yn·2-n = -y0·20 +y1·20 -y1 ·2-1+ ···+ yn-1 ·2-(n-2) -yn-1·2-(n-1) +yn·2-(n-1)-yn·2-n +0·2-n

1101 1011

1101 1101 0000 1101 10001111

X

Y=y3y2y1y0

X·y0 ·20 X·y1 ·21 X·y2 ·22 X·y3 ·23

机算与手算的区别: •多项相加改为两项逐次累 加,只需要普通加法器; •左移改为右移,只需要n 位加法器; •乘数Y与积的低n位共用一 个寄存器,右移后只需判 断y0决定加X或加0

=(y1 -y0) ·20 + (y2 - y1) ·2-1+······ +( yn - yn-1)·2-(n-1) + (0 - yn) ·2-n

定点原码一位乘法器的设计

定点原码一位乘法器的设计定点原码乘法器是一种基本的数字运算电路,用于实现两个定点原码数的乘法运算。

在设计定点原码乘法器时,需要考虑两个关键方面:乘法运算的算法和乘法运算电路的实现。

一、乘法运算的算法设计:1.符号位的处理:定点原码乘法器需要考虑乘法运算的符号位。

根据乘法运算的规则,当两个数的符号位不同时,乘积的符号位为负;当两个数的符号位相同时,乘积的符号位为正。

因此,在乘法运算时,首先需要对两个乘数的符号位进行判断和处理。

2.乘法运算的主体部分:乘法运算的主体部分是通过将两个乘数的每一位进行相乘,并将结果相加得到乘积的每一位。

一般来说,乘法运算可以采用移位和加法的方式来实现。

a.移位操作:在乘法运算中,需要将乘数的每一位与被乘数的每一位相乘,并将结果相加。

因此,首先需要将乘数的每一位与被乘数的每一位相乘,移位操作可以实现该过程。

b.加法操作:乘法运算中,需要将乘数的每一位与被乘数的每一位相乘,得到中间的结果,然后将中间结果相加,得到最终的乘积。

这一步骤可以通过加法器电路来实现。

二、乘法运算电路的实现设计:在设计定点原码乘法器的电路时,需要考虑各个功能模块的实现:1.符号位处理电路:由于定点原码乘法器需要考虑两个乘数的符号位,因此需要设计一个符号位处理电路。

该电路可以根据两个乘数的符号位来判断乘积的符号位,并给出相应的控制信号。

2.移位操作电路:移位操作电路用于实现乘数的每一位与被乘数的每一位相乘。

可以采用多路选择器和移位寄存器来实现。

多路选择器用于选择当前操作的两个数位,移位寄存器用于保存被乘数的每一位。

3.加法器电路:加法器电路用于将乘数的每一位与移位操作电路中移位后的结果相加。

可以采用并行加法器来实现,通过级联多个全加器,实现两个二进制数的加法运算。

4.乘积结果输出电路:乘积结果输出电路用于将最终的乘积输出。

可以通过选择器来选择最后一位的结果,并将结果输出到寄存器中,供后续电路使用。

设计定点原码乘法器的步骤如下:1.分析乘法运算的算法,确定各个功能模块的需求和输入输出信号。

定点乘法运算定点乘法运算(与“乘法”有关的文档共32张)

第一页,共32页。

2.3.3 原码并行乘法

1.串行加法器的优劣分析

• 不需要很多器件,硬件结构简单;

• 速度太慢,执行一次乘法操作的时间至少是加法操

作的n倍;

由于乘法操作大约占全部算术运算的1/3,故采用 高速乘法部件是非常必要的。

第二页,共32页。

2.3.3 原码并行乘法

作用是:将两个操作数A和B在被不带符号的乘法阵列

(核心部件)相乘以前,先变成正整数。

• 算后求补器 作用则是:当两个输入操作数的符号不一致时, 把运算结果变成带符号的数(补码)

第十八页,共32页。

2.3.3 原码并行乘法

运算:

设A=anan-1…a1a0和B=bnbn-1…b1b0均为用定 点表示的(n+1)位带符号整数。 在必要的求补操作以后,A和B的码值输送给n×n位

求每一部分乘积项aibj 的值与p9p8……p0的值。

1 1 0 1 1 = A (2710)

1 0 1 0 1 = B (2110)

11011

00000

11011

00000

+

11011

1000110111=P

第十二页,共32页。

2.3.3 原码并行乘法

[解:]

a4b0=1 a3b0=1 a2b0=0 a1b0=1 a0b0=1 a4b1=0 a3b1=0 a2b1=0 a1b1=0 a0b1=0 a4b2=1 a3b2=1 a2b2=0 a1b2=1 a0b2=0 a4b3=0 a3b3=0 a2b3=0 a1b3=0 a0b3=0 a4b4=1 a3b4=1 a2b4=0 a1b4=1 a0b4=1 P=p9p8p7p6p5p4p3p2p1p0=1000110111 (56710)

计算机组成原理2.3 定点乘法运算

2.3.1 原码乘法

• 图2.5示出了5×5位阵列乘法器的逻 辑电路图 • 图中一位全加器FA中所有被加数项 的排列和前面A×B=P乘法过程中的 被加数矩阵相同 • 不带符号的阵列乘法器逻辑电路图

2.3.1 原码乘法

• 这种乘法器要实现n位×n位时,需要 n(n-1)个全加器和n2个“与”门。 • 该乘法器的总的乘法时间可以估算如 下: • 令Ta为“与门”的传输延迟时间,Tf为 全加器(FA)的进位传输延迟时间,假 定用2级“与非”逻辑来实现FA的进 位链功能,那么我们就有:Ta = Tf = 2T

2.3.1 原码乘法

• 上面CAI演示所示的带求补级的阵列乘 法器既适用于原码乘法,也适用于间 接的补码乘法。 • 在原码乘法中,算前求补和算后求补 都不需要,因为输入数据都是立即可 用的。 • 而间接的补码阵列乘法需要使用三个 求补器

2.3.1 原码乘法

[例17] 设x=+15,y=-13,用带求补器 例 的原码阵列乘法器求出乘积x·y=? [解:]设最高位为符号位,则输入数据为 解 [x]原 =01111 [y]原 = 11101 符号位单独考虑,算前求补级后 |x|=1111,|y|=1101

2.3.1 原码乘法

• 自从大规模集成电路问世以来,出现了各 种形式的流水式阵列乘法器,它们属于并 行乘法器。

4讲 定点数乘法

附加位

说明

0 初始,乘数最后补0

(Pi–2X)2–2; +2[– X]补

1 右移两位 (Pi–X)2–2;+[–X]补

1

右移两位

(Pi–X)2–2 ;+[–X]补

0 右移1位

第4讲

19

第3章—1 定点数乘法运算

四.定点补码2位乘法

解2:[X]补= 1.0011 ,[Y]补= 11.0101(双符号数) [X]补= 111.0011, 2[X]补= 110.0110 [–X]补=000.1101,2[–X]补=001.1010

组合 +0 +[X]补 +[X]补 +2[X]补 +2[-X]补 +[-X]补 +[-X]补 +0

第4讲

18

第3章—1 定点数乘法运算

四.定点补码2位乘法

已知: X= –0.1101 Y= –0.1011,用补码2位乘法求[X•Y]补

方法1 : [X]补= 1.0011,[Y]补= 1.0101,[X]补= 111.0011, 2[X]补=110.0110,[–X]补=000.1101,2[–X]补=001.1010

X正负任意,Y为负数: [X· Y]补=[X]补· (0.Y1Y2…Yn)+[-X]补

采用双符号位,数据和符号位都参与运算;取乘数Y 的数值位放入乘数寄存器运算。

第4讲

11

第3章—1 定点数乘法运算

二. 定点补码1位乘法

已知:X=+0.1101,Y=-0.1011,用补码1位乘的方法求:Z=X*Y。

+[X]补

00 1000

0010

右移1位

+ 00 0000

定点乘法器

定点乘法器设计蒋小龙2002.12.29声明作此资料为本人个人行为,此资料版权为本人所有。

你可以任意使用,但你非经本人允许不得对此资料内容作任何修改。

你因使用此资料所带来任何收益,本人均不染指;因使用此资料所引起的任何不良后果,本人不承担任何形式的责任。

出版物引用,但请注明!蒋小龙 2002.12.29目录声明 (1)0、约定 (5)1、无符号数一位乘法 (7)2、符号数一位乘法 (8)3、布思算法(Booth algorithm) (9)4、高基(High Radix)布思算法 (10)5、迭代算法 (14)6、乘法运算的实现——迭代 (18)7、乘法运算的实现——阵列 (20)8、乘加运算 (24)9、设计示例1 —— 8位、迭代 (26)1、实现方案1 ——一位、无符号 (26)2、实现方案2 ——一位、布思 (33)3、实现方案3 ——二位 (39)10、设计示例2 —— 16位、阵列 (45)11、设计示例3 —— 32位、迭代、阵列 (55)1、实现方案1 ——乘、加一步走 (56)2、实现方案2 ——乘、加两步走 (67)后记 (77)个人介绍 (79)0、约定运算符:+对其两边的数据作加法操作; A + B-从左边的数据中减去右边的数据; A - B-对跟在其后的数据作取补操作,即用0减去跟在其后的数据;- B*对其两边的数据作乘法操作; A * B&对其两边的数据按位作与操作; A & B#对其两边的数据按位作或操作; A # B@对其两边的数据按位作异或操作; A @ B ~对跟在其后的数据作按位取反操作;~ B <<以右边的数据为移位量将左边的数据左移; A << B$将其两边的数据按从左至右顺序拼接; A $ B运算数据:A乘法操作数、位串,位宽为N;B乘法操作数、位串,位宽为M;R累加操作数、位串,位宽为Y;D乘法——累加运算结果、位串,位宽为(M+N)、或Y,取大者;E布思编码;S(加减)运算结果,结果宽度与二源操作数中位宽最大者同;C(无符号数运算)进位;X(符号数运算)扩展位;T考虑了进位(C)或扩展位(X)及结果(S)的结果,即:T = C $ S 或 T = X $ S ;A[n]数据A的第n位;A[m:n]数据A的第m到n位;E<n>第n项编码项、编码值;D n在状态n时,数据D的值;对运算符的约定只在文中论述的时候有效。

定点乘法运算

例2.9:

已知:

小数点的位置: 1)乘数的符号位不参与乘,小数点的位置同部 分积的小数点位置。 2)乘数的符号位参与乘,以部分积和乘数总的 符号位数确定乘积的符号位数(或部分积和乘数 总的小数位数确定乘积的小数位数)。

右移时 左边补 0,因 为是作 绝对值 相加 (即正 数相加) 根据符 号扩展 原理, 应在最 高符号 位前补 0

000.10001111

最后一步移位

2. 原码一位乘法的逻辑实现:

数y

位积

原码一位乘法逻辑结构图

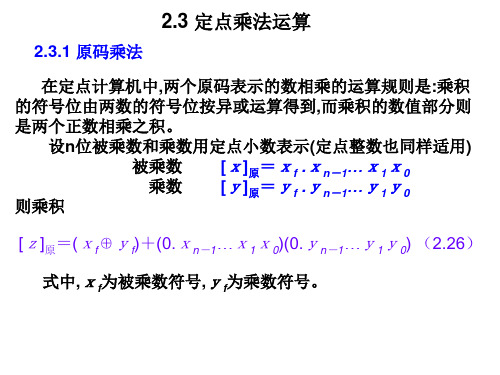

2.3 定点乘法运算

以加法器为核心,通过加法和移位 实现乘、除法运算。

2.3.1 原码一位乘法

1.原码一位乘法的运算规则

求|P|的运算规则:

位积=

ቤተ መጻሕፍቲ ባይዱ

原码一位乘法的算法流程图:

表示乘 数将要被判 断的那一位 为部分积

i表示循环次数

(相加/移位 的次数)

符号扩展:

把一个数的位数进行扩充但其真值不变。 正数的符号扩展:最高符号位之前补0(“0” 表示正号)。 负数的符号扩展:最高符号位之前补1(“1” 表示负号)。 例: =10010011,将其扩展成16位补码。 得: =1111111110010011 例: =00101100,将其扩展成16位补码。 得: =0000000000101100

定点乘除法运算

例3.35:设X=-0.1101,Y=0.1011,即[X]补=11.0011,[Y]补=0.1011 ,[-X]=00.1101 求 设 即 补 补 [X•Y]补. 补 部分积 乘数Y Yi Yi+1 说明 计算过程如下: 计算过程如下

+ 00 0000 00 1101 00 1101 → + 00 0110 00 0000 00 0110 → + 00 0011 11 0011 11 0110 → + 11 1011 00 1101 00 1000 → + 00 0100 11 0011 11 0111 0 0 0 1 0 0 0 1 0 1 右移一位 Y1Y0=10 +[X]补 0 0 1 0 1 0 右移一位 Y2Y1=01 +[-X]补 0 1 0 1 0 1 右移一位 Y3Y2=10 +[X]补 1 0 1 0 1 1 右移一位 Y4Y3=11 +0 0. 1 0 1 1 0 初始值,最后一位补0 Y5Y4=01 +[-X]补

2.硬件快速乘法器实现 硬件快速乘法器实现

利用中大规模集成电路芯片, 利用中大规模集成电路芯片,在一拍节中实现多项 部分积的相加,成为阵列乘法器。 部分积的相加,成为阵列乘法器。

3.3.1 定点数一位乘法 1. 定点原码一位乘

规则:在机器中采用 寄存器来分别存放部分积, 规则 在机器中采用A,B,C寄存器来分别存放部分积,被乘 在机器中采用 寄存器来分别存放部分积 数和乘数 (1)在机器内一次加法操作只能求出两数之和,因此 )在机器内一次加法操作只能求出两数之和, 每求得一个相加数时,就得与上次部分积相加。 每求得一个相加数时,就得与上次部分积相加。 (2)人工计算时,相加数逐次向左偏移一位,由于最 )人工计算时,相加数逐次向左偏移一位, 后的乘积位数是乘数(或被乘数)的两倍.由于在求本 后的乘积位数是乘数(或被乘数)的两倍 由于在求本 次部分积时,前一次部分积的最低位,不再参与运算, 次部分积时,前一次部分积的最低位,不再参与运算, 因此可将其右移一位。相加数可直送而不必偏移, 因此可将其右移一位。相加数可直送而不必偏移,于是 位加法器就可实现两个N位数相乘 用N位加法器就可实现两个 位数相乘。 位加法器就可实现两个 位数相乘。 (3)部分积右移时乘数寄存器同时右移一位,这样可 )部分积右移时乘数寄存器同时右移一位, 以用乘数寄存器的最低位来控制相加数( 以用乘数寄存器的最低位来控制相加数(取被乘数或 ),同时乘数寄存器的最高位可接收部分积右移出来 零),同时乘数寄存器的最高位可接收部分积右移出来 的一位,因此,完成乘法运算后, 寄存器中保存乘积 的一位,因此,完成乘法运算后,A寄存器中保存乘积 的高位部分,乘数寄存器C中保存乘积的低位部分 中保存乘积的低位部分。 的高位部分,乘数寄存器 中保存乘积的低位部分。

定点乘法

xy=x(0.1011) =0.1x+0.00x+0.001x+0.0001x =0.1{x+0.1[0+0.1(x+0.1x)]} -1 -1 -1 -1 =2 {x+2 [0+2 (x+2 x)]} 根据此式,按照式中括号所表达的层次. 根据此式,按照式中括号所表达的层次.从内向外逐 次进行移位累加.每算完一层括号 (部分积),就得到一个 次进行移位累加 每算完一层括号2-1(部分积),就得到一个 每算完一层括号 ), 新的部分积,最后的一个部分积即为乘积. 新的部分积,最后的一个部分积即为乘积 一般而言,设被乘数x,乘数 都是小于1的 位定点正数 乘数y都是小于 位定点正数: 一般而言,设被乘数 乘数 都是小于 的n位定点正数 x=0.x1x2…xn y=0.y1y2…yn 其乘积为 xy=x(0.y1y2…yn) =x(y12-1+y22-2+…+yn2-n) =2-1(y1x+2-1(y2x+2-1(…+2-1(yn-1x+2-1号的运算法则是:同号相乘为正 异号相乘为负 异号相乘为负。 乘积符号的运算法则是:同号相乘为正,异号相乘为负。由于被乘 数和乘数和符号组合只有四种情况( 数和乘数和符号组合只有四种情况 xfyf=00,01,10,11),因此 因此 积的符号可按“异或” 按位加 运算得到。 按位加)运算得到 积的符号可按“异或”(按位加 运算得到。 数值部分的运算方法与普通的十进制小数乘法类似,不过对于 数值部分的运算方法与普通的十进制小数乘法类似 不过对于 用二进制表达式的数来说,其乘法规则更为简单一些 其乘法规则更为简单一些。 用二进制表达式的数来说 其乘法规则更为简单一些。 让我们先用习惯方法求其乘积,其 设x=0.1101,y=0.1011.让我们先用习惯方法求其乘积 其 让我们先用习惯方法求其乘积 过程如下: 过程如下

4定点数乘除运算及实现

解决方案:

(a) 把一次求和的操作,变成逐步累加求部分积的操作 把一次求和的操作,变成逐步累加求部分积 逐步累加求部分积的操作 (b) 将求积过程中左移位积的操作,改为位积不动,而是上次部分积右移的 将求积过程中左移位积的操作,改为位积不动 而是上次部分积右移 位积不动, 上次部分积右移的 操作

手工运算过程

原码两位乘法:基本原理类似:只是从最低位开始,每次 原码两位乘法:基本原理类似:只是从最低位开始, 取两位乘数与被乘数相乘, 取两位乘数与被乘数相乘,得到一次部分 积,与上次部分积相加后右移2。有关原 与上次部分积相加后右移 。有关原 码两位乘法具体操作过程不再 详细讨论

2 补码乘法

∞ 补码一位乘法 补码与真值的关系: ≠ 补码与真值的关系: 例:已知【Y】补= Y0.Y1 Y2‥‥ Yn, 已知【 】 证明真值: =(- =(-Y 证明真值:Y=(- 0)+ ∑ Yi ×2 -i i=1 证明: 证明: ①当 Y ∴0时, Y 0=0 时 则真值Y = (- ) + 0.Y1 Y2‥‥ Yn=∑ Yi ×2 -i (-0) 则真值 . ‥‥ =

计算机内运算的实现方法

[例] 已知 X=- ﹒101,Y=- ﹒110,用原码一位乘法求[X Y ]原=? 例 已知: =- =-0﹒ , =- =-0 , 过程为 解:用原码一位乘法实现X Y过程为: 用原码一位乘法实现 一位乘法实现 过程 ① [X]原=1 ﹒ 101 [Y]原=1 ﹒ 110 ② [X Y ]原 = 1⊕1+ (0﹒ 101) ×(0﹒ 110) ﹒ ﹒ 的过程为: ③ 则(0﹒ 101) ×(0﹒ 110)的过程为: ﹒ ﹒ 的过程为

1 原码乘法

⑴ 原码一位乘法 原码一位 一位乘法 运算规则: 被乘数: 运算规则: 被乘数: [X]原 =xf .xn-1…x1x0 x 乘 数: [Y]原 =yf .yn-1…y1y0 y 则积: 则积 [X*Y]原 =( XS ⊕ YS ) +( X * Y ) 式中: 为被乘数符号, 为乘数符号。 式中: XS为被乘数符号, YS为乘数符号。 乘积符号的运算法则是: 异或” 按位加 运算得到。 按位加)运算得到 乘积符号的运算法则是:“异或”(按位加 运算得到。 数值部分的运算方法与普通的十进制小数乘法类似 方法与普通的十进制小数乘法类似。 数值部分的运算方法与普通的十进制小数乘法类似。 下面通过一个具体例子从来说明: 下面通过一个具体例子从来说明:

定点数的乘法运算

定点数的乘法运算定点数的乘法运算是计算机科学中的一个重要概念,它在各个领域都有着广泛的应用。

本文将从概念、实现以及应用三个方面进行阐述,以便读者能够全面了解定点数的乘法运算。

一、概念定点数是一种表示数值的方式,它将小数点固定在某个位置上。

定点数的乘法运算是指对两个定点数进行相乘的操作。

在定点数的乘法运算中,需要注意保持小数点的位置不变,并对整数部分和小数部分进行相乘,最后将结果进行合并得到最终的乘积。

二、实现定点数的乘法运算可以通过数学方法来实现,也可以通过计算机程序来实现。

数学方法主要是通过手工计算来完成,而计算机程序则是利用计算机的运算能力来进行计算。

在计算机程序中,定点数的乘法运算通常使用位运算来实现。

位运算是一种对二进制数进行操作的方法,它可以高效地进行乘法运算。

计算机程序中的定点数通常使用固定的位数来表示,例如使用16位来表示定点数的整数部分和小数部分。

在进行乘法运算时,先将两个定点数的整数部分和小数部分进行相乘,然后将结果进行合并得到最终的乘积。

三、应用定点数的乘法运算在计算机科学中有着广泛的应用。

它可以用于图像处理、音频处理、视频编码等领域。

在图像处理中,定点数的乘法运算可以用于图像的缩放、旋转、平移等操作。

通过对图像的像素进行定点数的乘法运算,可以实现图像的变换和处理。

在音频处理中,定点数的乘法运算可以用于音频的滤波、均衡器等操作。

通过对音频信号进行定点数的乘法运算,可以实现音频的增强和修复。

在视频编码中,定点数的乘法运算可以用于视频的压缩和编码。

通过对视频的像素进行定点数的乘法运算,可以减少视频的数据量,从而实现视频的高效传输和存储。

总结:定点数的乘法运算是计算机科学中的一个重要概念,它在各个领域都有着广泛的应用。

本文从概念、实现以及应用三个方面进行了阐述,希望读者能够通过本文对定点数的乘法运算有更加全面的了解。

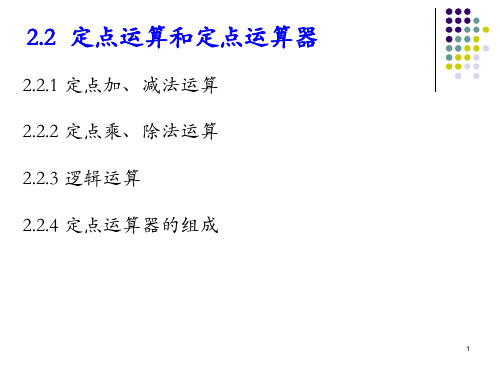

第2章2.2定点运算和定点运算器

∴ x+y= -0.0111

5

2.2.1 定点加、减法运算

2. 补码减法 减去一个数就是加上这个数的负数, [x-y]补=[x+(-y)]补=[x]补+[-y]补 (mod 2)

从[y]补求[-y]补的法则:将[y]补连同符号位“取反且最低位

加1,相当于求负数的补码。 (hw)

【例2-12】 x= -0.1010,y= -0.0011,求 x-y。 【解】 [x]补=1.0110 [y]补=1.1101 [-y]补=0.0011

2)采用硬件实现乘除法运算

3)并行乘除法器

•

从编码角度考虑:乘除由法结果的符ቤተ መጻሕፍቲ ባይዱ位确定比较容易,运算结果的

绝对值和参加运算的数据的符号无关,所以用原码实现也很简单。 但在现代计算机中一般还是采用补码进行乘除法运算

9

2.2.3 逻辑运算

参加逻辑运算的数据称为逻辑数,是不带符号位的二进 数通常用“1” 表示逻辑真,用“0”表示逻辑假 1 逻辑非(取反运算)

操作数的各位按位取反,使每一位0变成1,1变成0

设x=x0x1x2…xn,则逻辑非标记 【解】

x x0 x1x2 xn 【例2-14】 设x=10100010,求 x 。

x =01011101

10

2.2.3 逻辑运算

2 逻辑与 (逻辑乘) • 两个操作数相同位的数据进行按位“与”运算,两个都是1 则结果为1,两个中只要有1个为0结果就是0 一般写成“∧”或“·” • 特点 对任何数据逻辑与0都会变成0,而逻辑与1则保持原有数据 不变;可用于对一个数据的某几位清0,而其他位保持不变 【例2-15】 设x=01011101,y=10011001,求x∧y。 【解】 01011101

3.4 定点运算器

理原成组河南科技大学计算机定点运算器3.4定点数的乘法运算明德笃行博学日新◆加法器及其进位结构◆多功能算术/逻辑运算单元(ALU)◆定点运算器的基本结构1)一位全加器示意图FAA i BiCiCi+1 SiA i 表示被加数的第i位B i 表示加数的第i 位C i 为第i-1位向第i 位产生的进位C i+1 为第i位向第i+1位产生的进位S i 为第i 位产生的和2)全加运算的真值表 输入 输出 A iB iC i S i C i+10 0 0 0 0 0110 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 111113)逻辑表达式S i =A i ⊕B i ⊕C iC i +1=A i B i +B i C i +C i A i1. 一位全加器4)全加器的逻辑结构要实现n位数相加,就要用全加器组成加法器。

根据组成方法的不同有两种:串行加法器和并行加法器。

1)串行加法器仅用一位全加器,使用移位寄存器从低位到高位串行地提供操作数,分n次进行相加,实现两个n位数相加。

缺点:分n次进行,速度慢。

(现实中很少使用)2)并行加法器用n个全加器按照一定的连接方式,将两个n位数同时送到这些全加器,通过一次计算完成两个n位数的相加。

关键问题:各个数位上进位的产生方式—串行进位和并行进位1.串行进位的并行加法器将n个全加器按照串联的方法,从低位到高位逐位依次将低位的进位输出端连接到高位全加器的进位输入端上,就形成n位串行进位的并行加法器。

串行进位的并行加法器特点:进位信号是逐级产生的。

1)进位产生公式C i+1=A i B i+B i C i+C i A i=A i B i+(A i⊕B i)C i G i=A i B i (进位产生函数)P i=A i⊕B i (进位传递函数)C i+1=G i+P i C i1)进位产生公式以四位加法器为例:C 1=G0+P0C0C 2=G1+P1C1=G1+P1(G0+P0C0)C 3=G2+P2C2=G2+P2(G1+P1(G0+P0C0))C 4=G3+P3C3=G3+P3 (G2+P2(G1+P1(G0+P0C0)))结论:四个进位输出信号,仅由Gi、Pi及最低位的C0决定,与低位进位无关C 1C 2 C 3 C 4P 3 G 3P 2 G 2G i++++C 0P iP 1 G 1 0P 0 四位先行进位部件CLAAi BiAi Bi3)先行进位加法器采用先行进位逻辑部件产生进位信号,然后再送去求和的加法器称为先行进位加法器。

组成第四讲--乘除法运算

河北经贸大学

信息技术学院

河北经贸大学

信息技术学院

计算机组成原理

加减交替法

但由于要恢复余数,使除法迚行过程的步数不固 定,因此控制比较复杂。实际中常用不恢复余数 现不够减,则不必恢复余数,根据余数符号,可以 继续往下运算,因此步数固定,控制简单。

法,又称加减交替法。其特点是运算过程中如出

相结合的方法部分积右移时,乘数寄存器同时

件结构,采用串行的1位乘法方案,而多次执行

“加法、移位”操作来实现。这种方法并不需要 很多器件。然而串行方毕竟太慢,不能满足科学

技术对 高速乘法所提出的要求。由于大规 模集成电路的发展和实际计算的需要,硬件乘 法器应运而生。

河北经贸大学

乘数[Y]原=Y0· Y1…Yn-1Yn

乘积[Z]=(X0⊕Y0)· (0.X1…Xn1Xn)(0.Y1…Yn-1Yn) 式中,X0为被乘数符号,Y0为乘数符号。

河北经贸大学

信息技术学院

计算机组成原理

设X=0.1101,Y=0.1011,让我们先用习惯方法求 其乘积,其过程如下: 0.1101 (X) × 0.1011 (Y) -------------------1101 1101 0000 + 1101 -------------------0.10001111 (Z)

信息技术学院

计算机组成原理

河北经贸大学

信息技术学院

计算机组成原理

河北经贸大学

信息技术学院

计算机组成原理

河北经贸大学

信息技术学院

计算机组成原理

河北经贸大学

信息技术学院

计算机组成原理

补码一位乘法 有的机器为方便加减法运算,数据以补码形

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

直接补码乘法:输入输入是补码,输出是补码。 变量的补码→乘积的补码

15

求补器(间接补码乘法)

C-1=0, Ci=ai+Ci-1

ai*=ai⊕ECi-1,

0≤i≤n

16

求补器

说明: 按位扫描的方法,进行求补的方法就是从

(1)分步乘法:每次将一位乘数所对应的部分 积与原部分积的累加和相加,并移位。

(2)设置寄存器: A:存放部分积累加和、乘积高位 B:存放被乘数 C:存放乘数、乘积低位

(3)设置初值: A = 00.0000 B = X = 00.1101 C = Y = 11.1011

6

早期的串行1位乘法(已淘汰)

数的最右端a0开始,,由右向左,直到找出第 一个“1”,ai以左的每一个输入位都求反, 即1变0,0变1。 当控制信号线E为“1”时,启动对2求补的操 作。E为“0”时,输出将和输入相等。 最右端的起始链式输入C-1必须永远置成 “0”。

17

求补器(间接补码乘法)

延迟估计 一个(n+1)位带符号的数求补,所需的总时 间延迟为 tTC=n·2T+5T=(2n+5)T

25

直接补码阵列器逻辑图

26

小结

掌握乘法的运算规律,原码与补码的规则。 掌握带符号的阵列乘法器的逻辑电路。 了解直接补码并行乘法的运算。

27

此课件下载可自行编辑修改,仅供参考! 感谢您的支持,我们努力做得更好!谢谢

a4b1 a3b1 a2b1 a1b1 a0b1

a4b2 a3b2 a2b2 a1b2 a0b2

a4b3 a3b3 a2b3 a1b3 a0b3

a4b4 a3b4 a2b4 a1b4 a0b4

p9 p8 p7

p6 p5

p4

p3

p2

p1

p0 =P

9

不带符号原码的阵列乘法器

10

不带符号的阵列乘法器

乘法器要实现n位×n位时,需要n(n-1)个全加器和n2个“与”门

(a4b0) a3b0 a1b0 a1b0 a0b0

(a4b1) a3b1 a2b1 a1b1 a0b1

(a4b2) a3b2 a2b2 a1b2 a0b2

(a4b3) a3b3 a2b3 a1b3 a0b3

a4b4 (a3b4) (a2b4) (a1b4) (a0b4)

p9 p8

p7

p6

p5

p4 p3 p2 p1

11

2 不带符号原码的阵列乘法器

12

延迟估计

n位×n位不带符号的阵列乘法器总的乘法

时间为:

tm=Ta+(n-2)×6T+3T+(n-1)×Tf+3T =T+(n-1)×6T+(n-1)×2T

=(8n-7)T

13

带符号原码阵列乘法器

14

3 带符号的阵列乘法器(补码形式)

请考虑用补码进行乘法计算的时候,运算过程应 该是怎样的?

n1

统一表示为 Nan2n ai2i i0

负权因数

21

计算

例1:已知[X]补=01101, [Y]补=10101, 求它们表示的数值?

22

直接补码阵列乘法

以5位二进制乘法为例。A=(a4)a3a2a1a0 B=(b4)a3a2a1a0

(a4) a3 a2 a1 a0 =A

×) (b4) b3 b2 b1 b0 =B

18

带符号阵列乘法器(间接补码乘法)

讨论间接 补码乘法?

19

比较带符号阵列乘法器

结论:补码方式比原码方式计算时间长。 阵列乘法结构取决于其所用数并行乘法(关键是符号位)

数学特征

N

n1

ai 2i i0

n1

[1 i0 (1 ai )2i ]

an 0 an 1

4第四讲定点乘法器

教学要求

掌握原码、补码的乘法运算规则,并进行 相关的计算。

深刻理解不带符号阵列乘法器,带符号阵 列乘法器的运算原理。

理解混合型加法器实现并行补码乘法的原 理。

2

教学重点

混合型加法器 直接补码并行乘法

3

一 定点数原码乘法

1 原码的乘法 基本思想:每次用乘数的一位去乘被乘数。 (1).算法分析 例. 0.1101×1.1011

乘积 P = X × Y 符号 SP= SX⊕SY

4

实例

0.1101

×0.1011 1101

1101 0000 1101

部分积

0.10001111 上符号:1.10001111 问题:1)加数多(由乘数位数决定)。

关)。2)加数的位数多(与被乘数、乘数位数有

改进:将一次相加改为分步累加。 5

1 早期的串行1位乘法(已淘汰)

X Y -Z -X -Y Z

000 001 010 011 100 101 110 111

带权输出

CS -C -S

00 01 01 10 01 10 10 11

C -S -C S

00 01 11 00 11 00 10 11

SXYZXYZXYZXYZ CXYYZZX

SXYZXYZXYZXYZ CXYYZXZ

p0

23

一般化的全加器

类型

0类 加法器

1类 加法器

2类 加法器

3类 加法器

逻辑符号

操作

X Y +) Z CS

X Y +)-Z C(-S)

-X -Y +) Z (-C)S

-X -Y +) -Z (-C)(-S)

24

全加器 0类 3类

真 值 表

1类 2类

真 值 表

带权输入

XYZ -X -Y -Z

000 001 010 011 100 101 110 111

存在的问题 这种方法并不需要很多器件。然而串行方

法太慢。 解决办法 大规模集成电路问世以来,出现了各种形式

的流水式阵列乘法器,它们属于并行乘法器。

8

2 不带符号原码的阵列乘法器

以m=n=5为例

a4

a3

a2 a1 a0 =A

×

b4

b3

b2 b1 b0 =B

a4b0 a3b0 a2b0 a1b0 a0b0