扫频信号发生器

超声波发生器具有扫频功能

集成化与微型化技术

将超声波发生器与其他功能模块集成,实现更小体积、更轻重量, 便于携带和集成。

应用领域拓展

01

医疗领域

利用超声波发生器的扫频功能,开发新型医疗设备,如超声成像仪、超

声治疗仪等,提高医疗诊断和治疗的准确性和效率。

02

无损检测领域

02

超声波发生器的扫频功能

扫频范围

扫频范围

超声波发生器的扫频范围是指其输出频率的可调整范围。一般来说,扫频范围 越宽,其应用范围就越广泛。常见的扫频范围为数十赫兹到数百千赫兹。

频率稳定性

频率稳定性是指超声波发生器在扫频过程中输出频率的稳定性。频率稳定性越 高,其输出信号的波形失真越小,能够更好地满足不同应用的需求。

信号处理

利用扫频功能可以实现对信号的频率分析和处理,如滤波、 傅里叶变换等。这种应用场景常见于通信、雷达、声呐等 领域。

振动控制

通过控制超声波发生器的扫频范围和模式,可以对物体的 振动进行精确控制,如减震、隔振等。这种应用场景常见 于机械、航空、汽车等领域。

无损检测

利用非线性扫频模式可以对材料进行无损检测和评估,如 超声成像、裂纹检测等。这种应用场景常见于工业、医疗、 军事等领域。

通过调整超声波的频率,可以适应不同厚度的材 料检测,满足多种应用场景的需求。

扫频技术可以适应不同的检测对象,包括金属、 玻璃、塑料等不同类型的材料。

提高工作效率

01

扫频功能可以快速完成检测任务,提高工作效率。

02

通过自动调整超声波的频率,可以减少手动调整的 步骤和时间,从而提高工作效率。

03

扫频技术可以同时检测多个位置或多个对象,缩短 了检测时间,提高了工作效率。

2扫频仪

返回

21

(3)测频率特性和增益

按图连接

设备连接示意图

22

返回

扫频仪的两种输出电缆

23

调节图形幅度

•调节输出衰减,注意,这里改变的是被测设备输入 信号的大小 •调节Y轴增益旋钮(只改变显示)。 读出曲线上3dB处的宽度即为3dB带宽。 *如被测设备中含有检波器(如测鉴频特性曲线), 则用直通电缆。 测增益 采用比较法。先用75欧姆电阻代替图七中的被测 电路,输出衰减调至0dB,或10dB,将屏上显示调到 适当位置例如3格,换上被测电路,保持显示旋钮不 动,调节输出衰减,使屏上图形与原来同高,则第 二次衰减的dB数就为该电路的增益。

•该信号经低通滤波器滤波形成菱形频标。

12

菱形频标

13

BT3-G主要技术指标

• • • • • • • • • • • • 扫频范围:1~300MHz。 扫频宽度:全扫频:1~300MHz,中心频率150MHz。 窄扫频:最大频偏≥100MHz,最小频偏≤1MHz,1~300MHz连续 可调。 点频:1~300MHz连续可调,输出正弦波。 扫频非线性:不大于1:1.2。 输出电压:0.5V(3.33mw)±10%。 输出平坦度:1~300MHz范围内,0dB衰减时全频段优±0.25dB。 输出衰减器:0~70dB,1dB步进。 输出阻抗:75Ω。 频率标记:内频率标记:50MHz、10MHz、1MHz复合菱形标记。 外频率标记:仪器外频标记输入端输入约6dBm的10~300MHz正弦 波信号,外接频标灵敏度优于300mV。 输入阻抗:470KΩ。

仪器 介绍(2)

频率特性测试仪

1

一、简介

• 名称:频率特性测试仪,简称扫频仪。

• 用途:用于调测设备的频率特性,例如调测调 谐放大器、滤波器、有源或无源网络的幅频特性 (频率响应曲线)得到带宽、增益 、带内不平度 等参数;调测鉴频器的S曲线等。

电子测量3.5 -3.6扫频、脉冲信号发生器2

脉冲信号发生器

二、脉冲信号发生器的分类

脉冲信号发生器是专门用来产生脉冲波形的信号源, 它可用于 测试视频放大器、宽带电路的振幅特性和过渡特性, 逻辑元件的开 关速度以及示波器的检定与测试等。

的频率,测量相应的输出电压值。

扫频信号发生器

振幅比(相位差)

正弦信号源 (改变频率)

图1 点频法测量系统的幅频特性

扫频信号发生器

特点:准确度较高,原理简单,但操作繁琐费时, 频率间隔较大,易遗漏某些特性突变点,且任何改 变都将导致重新测量。

扫频信号源或振荡器是指能提供频率可自动连续变 化的正弦波信号源。

三角波扫描信号:

us

uo ui

幅频特性

t

扫描信号

t

扫频信号

t

扫频信号发生器

和点频法相比,扫频法具有以下优点: (1) 可实现网络的频率特性的自动或半自动测量。 (2) 由于扫频信号的频率是连续变化的,因此所得到的 被测网络的频率特性曲线也是连续的。 (3) 点频法是人工逐点改变输入信号的频率,速度慢, 得到的是被测电路稳态情况下的频率特性曲线。扫频测量法是 在一定扫描速度下获得被测电路的动态频率特性。

扫频、脉冲信号发生器

2019/8/28

扫频信号发生器

扫频信号发生器

扫频信号发生器是一种输出信号的频率随时间在一 定范围内反复变化的正弦信号发生器,它是频率特 性测试仪(扫频仪)的核心,主要用于直接测量各种 网络的频率响应特性。

扫频信号发生器

正弦稳态下的系统函数或传输函数N(jω)反映了该 系统激励与响应间的频率关系,即

实验一、微波测量基础知识实验报告

实验一、微波测量基础知识班级:核32 姓名:杨新宇学号:2013011806 同组成员:杨宗谕一、实验目的(1)了解和掌握信号发生器使用及校准。

(2)了解微波测量系统的基本组成和工作原理。

(3)掌握常用微波测量系统各器件的调整和使用方法。

(4)频率计(波长表)校准。

(5)了解和掌握测量线使用方法二、实验原理及系统组成1、微波信号源图1是微波信号源的基本框图。

通常由微波信号源、微波测量装置和指示器三部分组成。

它负责提供一定频率和功率的微波信号。

同低频信号源一样,其信号可以是连续波也可以是调制波,工作方式有点频、扫频两种状态工作。

微波信号源被广泛应用的类型主要有以下两种:(1)标准信号发生器标准信号发生器其输出信号的频率、功率和调制系数可在一定范围内调节(有时调制系数可以固定不变),并能准确读数且屏蔽良好。

它能做到输出微波信号准确已知,并能精细调节,特别是能将信号功率连续衰减到毫瓦、微瓦级电平,根据不同用途可具有不同的调制方式。

(2)扫频信号发生器扫频信号发生器是能产生扫频信号的微波信号源,它能从所需频率范围的一端连续地“扫变”到另一端,所以能直接得到各个频率上的测量结果,在示波器或者记录仪上立即显示出所需要的频率特性曲线。

本实验采用的微波源是YM1123 标准信号发生器,工作在等幅模式下。

2、微波测量装置微波测量装置如图2 所示。

主要包括驻波测量线、调配元件、待测元件和辅助元件(如短路器、衰减器、匹配负载、移相器等)。

3、指示器部分指示器是用于显示测量信号特性的仪表,如直流电流表、测量放大器、功率计、示波器、数字频率计、频率计(波长表)等。

4、元件基本原理及作用信号源:本次实验采用YM1123标准信号发生器作为信号源,测量时工作在等幅模式,非测量时工作在其他模式,具体原理见本节第一部分。

数字频率计:由于信号源显示的频率不准,所以要用一个数字频率计来进行频率校准。

后面的频率值均为数字频率计的示数。

同轴波导转换:将同轴线和后面的矩形波导连接起来,将同轴线中的TEM波转变成要测量的微波信号。

用扫频仪观测被测电路或设备的频率特性

用扫频仪观测被测电路或设备的频率特性、测量增益对电路或电器设备进行频率特性的观测及增益的测量,实际中通常可采用频率特性测试仪即“扫频仪”,因此这里简单的对扫频仪原理及使用方法进行介绍。

根据测试目的、测试电路不同,所采用的扫频仪的类型也不同,本实验采用的是BT-3C型扫频仪。

1.扫频仪基本原理扫频仪的全称是频率特性扫描测试仪,也称扫频仪,是集扫频信号发生器、频标信号发生器、示波器于一体的信号通道专用检测和调试仪器。

主要由扫频振荡器、频标发生器、放大显示电路、电源等几部分组成。

频标电路产生1MHz、10MHz频标,用开关切换1MHz、10MHz 以及外频标三档,当开关扳向外频标时,可由外频标插座送入标准信号频率。

既可用于检测黑白、彩色电视机高频调谐器、图像通道的频率特性,调试电视伴音鉴频曲线和视频放大特性曲线,还可用于测试各种有源、无源四端网络及其它接收设备的高频放大器、宽带放大器、滤波器、陷波器的幅频特性或中心频率。

2.面板上各旋钮、插孔的作用这里以BT3C扫频仪为例介绍使用方法。

其面板及各控制旋钮如图7所示。

电源开关:用于开/关电源。

灰度调节:调整显示波形的亮度聚焦:调整光点聚焦,使扫描线清晰度最好。

频标选择:有1MHz、10MHz和外接三档,根据测试内容和方式进行选择。

当开关扳向外频标时,可由外频标插座送入标准信号频率。

频标幅度:调整频标幅度信号的大小。

外频标入:从外部输入频标信号,这时频标选择应置于外接档。

扫频信号输出:扫频信号的输出插孔,通过输出电缆连接被测电路输入端。

Y轴位移:调整波形位置上下移动。

输出衰减:(粗调)有10、20、30、40、50、60、70、80(dB)八档,调整输出扫频信号的电压幅度。

输出衰减:(细调) 有0、1、2、3、4、5、6、7、8、9(dB)九档,配合输出衰减粗调使用。

Y轴输入:插接检测探头,馈入来自被测电路输出端的检测信号。

Y轴增益:可均匀调整波形幅度的大小,配合Y轴衰减使用。

信号发生器扫频主要用途

信号发生器扫频主要用途信号发生器是一种用来产生各种不同频率、不同形式的电信号的仪器,它在电子测试和研发中扮演着非常重要的角色。

扫频是信号发生器的一个主要功能,主要用于频率响应测试、频谱分析和网络分析等应用。

下面将详细介绍信号发生器扫频的主要用途。

首先,信号发生器扫频常用于频率响应测试。

频率响应测试是指通过改变电路或系统输入信号的频率,来测量输出信号随频率变化的情况。

通过信号发生器的扫频功能,可以产生一系列频率连续变化的信号,从而对被测设备或系统的频率响应进行全面的测试。

例如,在音频设备的测试中,可以使用信号发生器扫频并输入不同频率的信号,然后测量输出信号的幅度和相位,以评估音频设备在不同频率下的性能。

其次,信号发生器扫频还可用于频谱分析。

频谱分析是指通过对输入信号进行频谱分解,将其分解为不同频率的成分,并显示在频谱图上。

信号发生器扫频功能可以提供一系列频率连续变化的信号,使得频谱分析仪可以对不同频率下的信号进行分析。

通过分析不同频率下信号的幅度和相位,可以获取信号的频谱信息,进而判断信号的频率成分、噪声水平、谐波失真等特性,为频谱分析提供了必要的信号源。

此外,信号发生器扫频还可用于网络分析。

网络分析主要用于测试和分析电路或系统中的传输特性。

通过信号发生器的扫频功能,可以提供一系列连续变化的频率信号作为输入,然后通过在被测网络上接收输出信号,并测量其幅度和相位,从而得到被测网络的传输特性。

在无线通信领域,例如对天线、滤波器、放大器等进行测试时,常需要使用信号发生器扫频,并与频谱分析仪或网络分析仪等仪器配合使用,进行各项测试指标的测量。

此外,信号发生器扫频还可用于频率合成和信号调制等应用。

频率合成是指通过对不同频率的信号进行叠加来产生一个新的频率信号。

信号发生器扫频功能可以提供连续变化的频率信号,通过对这些信号进行合成,可以得到复杂的频率信号,满足不同应用需求。

而信号调制是指通过改变信号的某些特性(如频率、幅度、相位等)来传输信息。

扫频仪使用

12341234575 671 1123高频电子技术实验室实用扫频仪都采用令回扫期扫频振荡器停振的办法。

即来自电源变压器次级,未经移相的电压加到负脉冲形成电路,形成的负脉冲加到扫频振荡器,使其在回扫期无扫频信号输出,因而电子束将仅在水平扫描信号作用下,沿水平轴返回,在荧光屏上显示出一条零电平的水平基线。

这种方法不仅去掉了多余的回扫曲线,同时这条水平基线正好用作被测频率特性曲线的参考基线(零值线),给观测带来方便。

(六)频标电路为了充分发挥使用扫频仪的简便,迅速和直观的优点,还必须在被显示的频率特性曲线上附加频率标记,即利用“频标”来确定曲线上任一点所对应的频率值。

BT3型扫频仪采用差频的方法来获得频标。

工作原理可用图6-3予以说明。

暂不考虑谐波发生器,在频标混频器里象一切非线性电路工作一样,频率稳定度很高的1MHz(或10MHz)晶振信号和扫频信号混频,结果将产生差频输出。

扫频信号的频率在f min到f max范围内反复扫变,当扫频信号的频率自f min向晶振频率接近时,频差越来越小;当频率扫变到等于晶振频率时,产生零拍差频;而340.52901 75道G301左半管放大,频标信号被直接送到G301右半管放大。

这两个信号经混合放大后,输出一对互补信号。

在送给一对Y轴偏转板前,可由“影象极性”开关来改变屏幕上所显示曲线的正负极性。

G303是扫描基线箝位管。

调节“Y轴位置”旋钮,可使扫描基线沿Y轴方向上、下移动。

示波管的水平偏转系统,由于未采用锯齿波扫描,被大大简化了。

X轴偏转板信号是直接来自相移网络的一对互补的50Hz正弦信号。

“坐标亮度”旋钮用来控制荧光屏四个角的指示灯,左旋旋钮,两个对角的黄灯亮,使透明坐标测量板上的标尺刻度易于观察;右旋旋钮,另两个对角的红灯亮,有利于图象拍摄。

三、扫频仪的使用(一)面板装置BT-3型扫频仪的面板如图6-5所示。

1.显示部分(1)电源、辉度旋钮该控制装置是一只带开关的电位器,兼电源开关的辉度旋钮两种作用。

信号发生器的使用

图8-6 扫频信号发生器

• 6、标准信号发生器频率合成式信号发生器 • 如图8-7所示为标准信号发生器的外观图。这种发生器的 信号不是由振荡器直接产生,而是以高稳定度石英振荡器 作为标准频率源,利用频率合成技术形成所需之任意频率 的信号,具有与标准频率源相同的频率准确度和稳定度。 输出信号频率通常可按十进位数字选择,最高能达11位数 字的极高分辨力。频率除用手动选择外还可程控和远控, 也可进行步级式扫频,适用于自动测试系统。直接式频率 合成器由晶体振荡、加法、乘法、滤波和放大等电路组成, 变换频率迅速但电路复杂,最高输出频率只能达1000兆赫 左右。用得较多的间接式频率合成器是利用标准频率源通 过锁相环控制电调谐振荡器(在环路中同时能实现倍频、 分频和混频),使之产生并输出各种所需频率的信号。这 种合成器的最高频率可达26.5吉赫。高稳定度和高分辨力 的频率合成器,配上多种调制功能(调幅、调频和调相), 加上放大、稳幅和衰减等电路,便构成一种新型的高性能、 可程控的合成式信号发生器,还可作为锁相式扫频发生器。

• 图8-7 标准信号发生器

• •

二、信号发生器的面板介绍 信号发生器的种类很多,在这里主要以SP-1642B函数信号发生器为例来介绍。 如图8-8所示为SP-1642B函数信号发生器的前面板实物外观图。 如图8-9所 示为SP-1642B函数信号发生器的后面板实物外观图。

• •

1、信号发生器前面板 SP-1642B函数信号发生器的前面板结构示意图如图8-10所示,图中标号部件 的名称和功能介绍见表8-10所示。

3、函数信号发生器操作

• 图8-16 方波波形输出设置

•

图8-19 正玄波输出效果

图8-22衰减40dB设置

图8-10 SP-1642B函数信号发生器的前面板结构示意图

信号发生器的使用条件及操作规程

信号发生器的使用条件及操作规程信号发生器的使用条件信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

各种波形曲线均可以用三角函数方程式来表示。

能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路被称为函数信号发生器。

一、信号发生器的分类:1、正弦信号发生器:正弦信号紧要用于测量电路和系统的频率特性、非线性失真、增益及灵敏度等。

按频率覆盖范围分为低频信号发生器、高频信号发生器和微波信号发生器;按输出电平可调整范围和稳定度分为简易信号发生器(即信号源)、标准信号发生器(输出功率能精准地衰减到—100分贝毫瓦以下)和功率信号发生器(输出功率达数十毫瓦以上);按频率更改的方式分为调谐式信号发生器、扫频式信号发生器、程控式信号发生器和频率合成式信号发生器等。

2、高频信号发生器:频率为100千赫~30兆赫的高频、30~300兆赫的甚高频信号发生器。

一般接受LC调谐式振荡器,频率可由调谐电容器的度盘刻度读出。

紧要用途是测量各种接收机的技术指标。

输出信号可用内部或外加的低频正弦信号调幅或调频,使输出载频电压能够衰减到1微伏以下。

3、微波信号发生器:从分米波直到毫米波波段的信号发生器。

信号通常由带分布参数谐振腔的超高频三极管和反射速调管产生,但有渐渐被微波晶体管、场效应管和耿氏二极管等固体器件取代的趋势。

仪器一般靠机械调谐腔体来更改频率,每台可覆盖一个倍频程左右,由腔体耦合出的信号功率一般可达10毫瓦以上。

4、扫频和程控信号发生器:扫频信号发生器能够产生幅度恒定、频率在限定范围内作线性变化的信号。

在高频和甚高频段用低频扫描电压或电流掌控振荡回路元件(如变容管或磁芯线圈)来实现扫频振荡;在微波段早期接受电压调谐扫频,用更改返波管螺旋线电极的直流电压来更改振荡频率,后来广泛接受磁调谐扫频,以YIG铁氧体小球作微波固体振荡器的调谐回路,用扫描电流掌控直流磁场更改小球的谐振频率。

扫频信号发生器有自动扫频、手控、程控和远控等工作方式。

扫频信号发生器及扫频仪讲解

LC IM

IM

C

75MHz

10f0oMHz

150MHz

92.5MHzΔf 107.5MHz

3.频标产生的原理 现以1MHz频标为例进行说明频标产生的原理 。

99.98MHz 100MHz 100.02MHz

1MHz振荡信号 的100次谐波

(a)

图8.6 频标的形成过程

(b) 图8.7 加有频标的波形

均用锯齿波电压,其

正程产生扫频信号,

逆程停止扫频,亮点

回扫,如图a所示。

f0

图b实用正弦波做扫

描电压时,其上升边

产生扫频信号,下降

边形成基线。

扫频振荡器的频率根据被测网络的中心频率f0范围进 行调解的,应使被测曲线的中心频率移至屏幕中央。

2 单元电路

1、扫频信号发生器

要求扫频信号源具有以下功能:

①能产生频率做线性变化的扫频信号; ②这个扫频信号的输出是等幅的,且具有一定的

单元电路工作原理

1.扫频单元

•扫频宽度与扫频线性通常是矛盾的,一般在保证 扫频线性情况下通过电路扩展频带来解决。

290MHZ

1MHZ~75MHZ ±7.5MHZ

289MHZ~215MHZ ±7.5MHZ

中心频率和扫频范围

BT-3型扫频仪工作时是以某中心频率为中心进行扫频的。

现以第Ⅱ波段为例说其工作情况,中心频率是人工手调振荡回 路中的可变电容C,例如图中调到100MHz。扫频是扫描电流IM 作用于调制线圈LC使振荡频率在100MHz中心频率的基础上产 生±7.5MHz 的频偏,即扫频范围最大只有15MHz。

扫频仪工作原理

1 组成原理框图

扫频仪主要由

两部分组成:

扫频仪工作原理

扫频仪工作原理

扫频仪是一种常用的测试仪器,用于测量不同频率范围内的信号参数。

其工作原理基于数学和电子学的原理。

首先,扫频仪通过内部的信号发生器产生一个特定频率的信号。

这个信号将通过扫频仪的输出接口发送出去。

然后,扫频仪通过内部的混频器将被测量的信号和信号发生器的信号进行混频。

混频器将产生频率的差值,也就是被测量信号与信号发生器信号之间的频率差。

接下来,混频器的输出信号将被输入到一个带宽较窄的滤波器中。

这个滤波器通常是一个可调的带通滤波器,用于选择特定的频率范围。

随后,滤波器的输出信号将被输入到一个放大器中,以增强信号的强度,以便于后续的处理。

最后,放大器的输出信号将被输入到一个检测器中。

检测器将对信号进行解调,将其转换成可测量的电压或功率。

通过改变信号发生器的频率,重复上述过程,扫频仪可以扫描整个频率范围,并测量不同频率下的信号参数。

最常见的参数包括信号的幅度(功率)、相位、频率等。

扫频仪通过测量不同频率下的信号参数,可以用于分析信号的频谱特性、检测频率响应、测量滤波器的传递特性等应用。

其

工作原理的关键在于利用混频和滤波来选择特定的频率范围,以及通过放大和检测来测量信号参数。

模电实验——常用电子仪器的使用

实验1.11.1 示波器的使用示波器的使用示波器是一种用途十分广泛的电子测量仪器。

它能把电信号变换成看得见的图像,便于人们研究电信号的变化过程。

利用示波器能观察各种不同信号幅度随时间变化的波形曲线,还可以用它测试各种不同的电量,如电压、电流、频率、相位差、幅度等等。

示波器分模拟式和数字式两种。

模拟示波器的显示装置是电子管,而数字示波器的核心是高速微处理器。

数字示波器功能强,能存储波形,目前正在取代模拟示波器。

但模拟实验所用的GOS-60为模拟示波器。

示波器很重要的一个技术参数是信号带宽信号带宽信号带宽,即测量信号的频带宽度。

GOS-60能测试的波形的最高频率为20MHz 。

相同功能的示波器,带宽越高,价格也越贵。

1. 示波器的基本结构及原理此部分参看实验指导书第3到第5页。

2.2.示波器的面板示波器的面板示波器的操作主要就是调节其面板上的各种按键和旋钮,使屏幕出现清晰稳定的信号波形。

示波器不论什么样的,其面板是有共性的,学习时主要是掌握这些共性的东西,要记住英文名。

图1.1 示波器左下方面板图1.1中,左侧起为:CAL 校准信号、INTEN 辉度调节旋钮、FOCUS 聚焦调节旋钮、TRACE ROCATION 轨迹旋转(当水平轨迹与刻度线不平行时,用螺丝刀调整)、POWER 按键。

示波器一般都自带一个内部的校准信号 “CAL ”输出,该校准信号的幅度、周期是已知并且是固定不变的,一般是频率为1KHz ,峰峰值V P-P 为2V 的方波信号。

用它可以判断示波器自身工作是否正常。

图1.2 示波器右侧上方面板图1.2的左侧HORIZONTAL水平方向区域,调整波形的X轴参数。

常用的为:POSITION水平位置旋钮TIME/DIV扫描时间旋钮:表示显示屏上水平一大格(即1cm)对应的时间间隔×10 MAG按键:按下,信号水平方向放大10倍SWP. V AR.扫描微调校准旋钮:测量信号周期频率时,要顺时针拧到底。

音频扫频信号发生器使用说明书

音频扫频信号发生器操作指导书编号:SYTF-SYGW0201-2009-01/0仪器名称音频扫频信号发生器仪器型号YE1311B使用工位IQC 附属工具喇叭转接口工装一、仪器面板介绍:1.电源开关2.输出正极3.输出负极4.电压调节5.扫描时间6.起始频率调节7.起始频率档 8.停止频率调节9.停止频率档 10.对数输出信号11.线性输出信号 12.自动挡13.手动档 14.手动输出频率旋钮控制面板二、使用说明:1.把电源开关打到“1”位置,打开仪器。

2.根据喇叭的规格书,算出正常工作的电压。

然后使用电压调节旋钮来调节电压。

3.根据喇叭规格书设定起始频率。

先按下起始频率档的按钮,然后旋转起始频率调节旋钮来设定起始频率。

停止频率的设定与起始频率的设定相同。

4.信号输出方式:选择对数形式来检验。

图一5.输出正极接在喇叭正极上,输出负极接在喇叭负极上。

选择自动挡来检验喇叭的音质是否存在问题。

连接如图一所示。

6.当喇叭的接口需要转接口的时候,我们使用如右图所示的工装,其中1档位是无信号输出,2档位是双输出,3是右侧输出,4是左侧输出。

这样可以检验左右两个喇叭的音质是否正常。

7.当检测喇叭的共振频率的时候,选择手动档,然后调节手动输出频率旋钮来调节输出频率,当震动最大时的频率就是被测喇叭的共振频率。

8.测试完成之后关机。

注意事项:1、每次开机后都要对音频扫频信号发生器参数进行确认,查看参数是否符合要求。

2、连接电路时应尽量避免发生短路。

第1页共1页。

扫频试验操作方法

扫频试验操作方法

扫频试验是一种常用的测试方法,用于测量材料、设备或系统对不同频率的输入信号的响应。

以下是扫频试验的一般操作方法:

1. 准备测试设备:根据需要选择合适的扫频仪、信号发生器、待测设备等。

2. 连接设备:将扫频仪、信号发生器和待测设备依次连接,确保信号传输无误。

3. 设置参数:根据试验需求,设置扫频仪和信号发生器的参数。

包括起始频率、结束频率、扫频速率、输入信号幅度等。

4. 开始试验:点击启动按钮,开始进行扫频试验。

扫频仪会依次输出不同频率的信号给待测设备,记录下其响应。

5. 数据收集:根据实际需求,在试验过程中及时记录下待测设备的响应数据。

可以使用计算机、数据采集器等设备进行数据收集和存储。

6. 数据分析:根据收集到的数据,进行后续的数据分析和处理。

包括频率响应曲线的绘制、降噪、滤波等操作。

7. 结果评估:根据数据分析结果,评估待测设备在不同频率下的性能,并得出相应的结论。

8. 报告撰写:根据试验结果,撰写试验报告,记录试验过程、数据分析结果、结论等。

需要注意的是,具体的扫频试验操作方法可能会因测试设备的不同而有所区别。

在进行实际操作前,建议先仔细阅读设备的操作手册,了解并掌握相关的操作步骤和注意事项。

信号发生器汇总

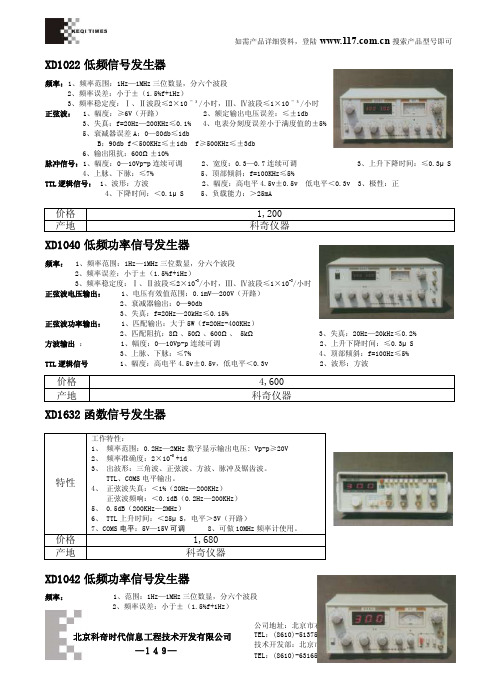

如需产品详细资料,登陆 搜索产品型号即可XD1022低频信号发生器频率:1、频率范围:1Hz —1MHz 三位数显,分六个波段2、频率误差:小于±(1.5%f+1Hz )3、频率稳定度:Ⅰ、Ⅱ波段≤2×10ˉ³/小时,Ⅲ、Ⅳ波段≤1×10ˉ³/小时正弦波: 1、幅度:≥6V(开路) 2、额定输出电压误差:≤±1db3、失真:f=20Hz —200KHz≤0.1%4、电表分刻度误差小于满度值的±5%5、衰减器误差A :0—80db≤1dbB :90db f <500KHz≤±1db f≥500KHz≤±3db 6、输出阻抗:600Ω±10%脉冲信号:1、幅度:0—10Vp-p 连续可调 2、宽度:0.3—0.7连续可调 3、上升下降时间:≤0.3μS4、上脉、下脉:≤7%5、顶部倾斜:f=100KHz≤5%TTL 逻辑信号: 1、波形:方波 2、幅度:高电平4.5v±0.5v 低电平<0.3v 3、极性:正4、下降时间:<0.1μS5、负载能力:>25mAXD1040低频功率信号发生器频率: 1、频率范围:1Hz —1MHz 三位数显,分六个波段2、频率误差:小于±(1.5%f+1Hz )3、频率稳定度:Ⅰ、Ⅱ波段≤2×10-3/小时,Ⅲ、Ⅳ波段≤1×10-3/小时正弦波电压输出: 1、电压有效值范围:0.1mV —200V (开路)2、衰减器输出:0—90db3、失真:f=20Hz —20kHz≤0.15%正弦波功率输出: 1、匹配输出:大于5W (f=20Hz-400KHz )2、匹配阻抗:8Ω、50Ω、600Ω、 5k Ω3、失真:20Hz —20kHz≤0.2%方波输出 : 1、幅度:0—10Vp-p 连续可调 2、上升下降时间:≤0.3μS3、上脉、下脉:≤7%4、顶部倾斜:f=100Hz≤5%TTL 逻辑信号 1、幅度:高电平4.5v±0.5v,低电平<0.3v 2、波形:方波XD1632函数信号发生器XD1042低频功率信号发生器频率: 1、范围:1Hz —1MHz 三位数显,分六个波段2、频率误差:小于±(1.5%f+1Hz )3、频率稳定度:Ⅰ、Ⅱ波段≤2×10-3/小时,Ⅲ、Ⅳ波段≤1×10-3/小时正弦波电压输出 1、电压有效值范围:0.1mV —6V (开路)2、衰减器输出:0—90db3、失真:f=20Hz —200MHz≤0.1%正弦波功率输出 1、匹配输出:大于10W (f=20Hz —200KHz )2、匹配阻抗:8Ω—30Ω3、失真:20Hz —200MHz≤0.15%方波输出 1、幅度:0—10Vp-p 连续可调 2、上升下降时间:≤0.3μS3、上脉、下脉:≤7%4、顶部倾斜:f=100KHz≤5%TTL 逻辑信号 1、波形:方波 2、幅度:高电平4.5v±0.5v,低电平<0.3 vTFG2015A 任意波信号发生器TFG5010V 脉冲时间信号发生器脉冲特征:同步脉冲,单脉冲,双脉冲,正极性,负极性,正向,反向,内触发,外触发,手动触发,支流偏移波形特征:脉冲波,时间间隔,正弦波,方波脉冲波方波升降时间:<20ns时间特征:时间范围:50ns~600s分辨率:五位数字精度:±(5×10ˉ5 To+10ns)幅度特性:幅度范围:100mV~20Vpp(高阻) 分辨率:20mV或1‰精度:±(1%Vo+分辨率)输出特点:主输出:脉冲波,正弦波,方波。

扫频信号源电路图与工作原理.

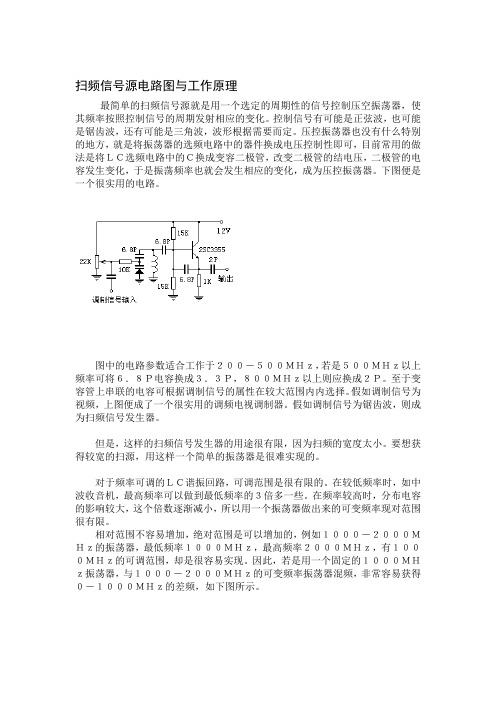

扫频信号源电路图与工作原理最简单的扫频信号源就是用一个选定的周期性的信号控制压空振荡器,使其频率按照控制信号的周期发射相应的变化。

控制信号有可能是正弦波,也可能是锯齿波,还有可能是三角波,波形根据需要而定。

压控振荡器也没有什么特别的地方,就是将振荡器的选频电路中的器件换成电压控制性即可,目前常用的做法是将LC选频电路中的C换成变容二极管,改变二极管的结电压,二极管的电容发生变化,于是振荡频率也就会发生相应的变化,成为压控振荡器。

下图便是一个很实用的电路。

图中的电路参数适合工作于200-500MHz,若是500MHz以上频率可将6.8P电容换成3.3P,800MHz以上则应换成2P。

至于变容管上串联的电容可根据调制信号的属性在较大范围内内选择。

假如调制信号为视频,上图便成了一个很实用的调频电视调制器。

假如调制信号为锯齿波,则成为扫频信号发生器。

但是,这样的扫频信号发生器的用途很有限,因为扫频的宽度太小。

要想获得较宽的扫源,用这样一个简单的振荡器是很难实现的。

对于频率可调的LC谐振回路,可调范围是很有限的。

在较低频率时,如中波收音机,最高频率可以做到最低频率的3倍多一些。

在频率较高时,分布电容的影响较大,这个倍数逐渐减小,所以用一个振荡器做出来的可变频率现对范围很有限。

相对范围不容易增加,绝对范围是可以增加的,例如1000-2000MHz的振荡器,最低频率1000MHz,最高频率2000MHz,有1000MHz的可调范围,却是很容易实现。

因此,若是用一个固定的1000MHz振荡器,与1000-2000MHz的可变频率振荡器混频,非常容易获得0-1000MHz的差频,如下图所示。

说起来容易,想起来更容易,倘若真的需要这样一套装置,设计制作的工作量也还是不小的。

对于产品设计,这点儿工作量倒不算什么,但对于爱好者实验来说有点儿不合算。

好在有不少成品可以利用,例如电视机的UHF本振,起码能保证(470+38)MHz────(860+38)MHz的电控可调范围;卫星接收机的调谐解调器本振频率绝对可调范围更大,大部分能保证(850+480)MHz────(2250+480)MHz的电控可调范围。

微波实验三微带谐振器品质因数的扫频实验

实验三微带谐振器品质因数的扫频实验—实验目的1、了解微波扫频测量的工作原理及特点。

2、掌握扫频测量微带谐振器Q值的方法。

二实验原理1.扫频测量的原理扫频技术是六十年代发展起来的测量技术,具有宽带、快速、连续、直观等优点,和传统的点频测量技术相比,速度可提高成百倍;而且能全面反映被测器件的频率特性,能迅速确定各种因素对整个微波电路频率特性的影响程度,因此,它已成为设计、研制微波元件的有力手段。

虽然,点频测试精度较高,但近年来,随着测试设备和方法的改进,扫频测试精度已达到可与点频测量相当的水平。

目前大多数微波参量,如反射(或驻波)、衰减(或插入损耗)、频率(或波长)、功率、相位、噪声等都可以采用扫频技术加以测量,其频率上限国内已达18GHzo尽管扫频测量系统的门类繁多,但一个扫频测量系统基本上由扫频信号发生器、微波宽带元件、显示和指示器三部分组成。

其组成可由图3-1来表示。

图37扫频系统的组成扫频信号发生器在测量中是信号产生部分,是整个测量系统的心脏。

它能提微波源__________ 谐振腔 ___________ 功率检测器图3-2测量谐振腔功率传输特性的方框图当微波振荡源的频率逐渐改变时,由于谐振腔的特性,随着改变,它与频率的关系曲线如图3-3所示。

归一化传输功率P(f) 传输到负载的功率将供符合测量需要的扫频信号、驱动显示器X轴的扫描信号和对X轴(时间轴)进行频率定度的频率标记。

通常的扫频信号发生器有返波管振荡器和固态扫频振荡器两种。

微波宽带元件在扫频测试系统中应具有良好的宽带特性,即在整个扫频范围内均具有平坦响应,主要有定向耦合器、晶体管检波器、固定衰减器等。

显示和指示器是用来显示、记录或指示检波后的低频信号。

在扫频测量系统中有时还要使用一种专用的音频放大器,为了放大微弱的被测信号。

2.谐振腔Q值的测量品质因数Q是表征微波谐振系统的一个重要的技术参量,品质因素Q描述了谐振系统频率选择性的优劣及电磁能量损耗程度。

扫频仪介绍

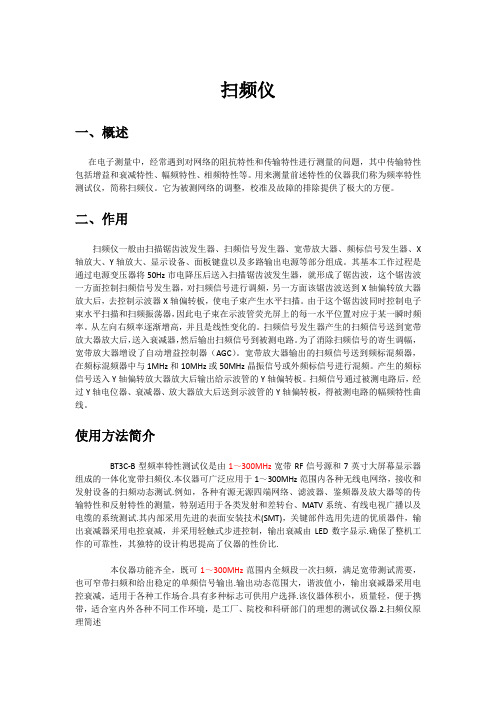

扫频仪一、概述在电子测量中,经常遇到对网络的阻抗特性和传输特性进行测量的问题,其中传输特性包括增益和衰减特性、幅频特性、相频特性等。

用来测量前述特性的仪器我们称为频率特性测试仪,简称扫频仪。

它为被测网络的调整,校准及故障的排除提供了极大的方便。

二、作用扫频仪一般由扫描锯齿波发生器、扫频信号发生器、宽带放大器、频标信号发生器、X 轴放大、Y轴放大、显示设备、面板键盘以及多路输出电源等部分组成。

其基本工作过程是通过电源变压器将50Hz市电降压后送入扫描锯齿波发生器,就形成了锯齿波,这个锯齿波一方面控制扫频信号发生器,对扫频信号进行调频,另一方面该锯齿波送到X轴偏转放大器放大后,去控制示波器X轴偏转板,使电子束产生水平扫描。

由于这个锯齿波同时控制电子束水平扫描和扫频振荡器,因此电子束在示波管荧光屏上的每一水平位置对应于某一瞬时频率。

从左向右频率逐渐增高,并且是线性变化的。

扫频信号发生器产生的扫频信号送到宽带放大器放大后,送入衰减器,然后输出扫频信号到被测电路。

为了消除扫频信号的寄生调幅,宽带放大器增设了自动增益控制器(AGC)。

宽带放大器输出的扫频信号送到频标混频器,在频标混频器中与1MHz和10MHz或50MHz晶振信号或外频标信号进行混频。

产生的频标信号送入Y轴偏转放大器放大后输出给示波管的Y轴偏转板。

扫频信号通过被测电路后,经过Y轴电位器、衰减器、放大器放大后送到示波管的Y轴偏转板,得被测电路的幅频特性曲线。

使用方法简介BT3C-B型频率特性测试仪是由1~300MHz宽带RF信号源和7英寸大屏幕显示器组成的一体化宽带扫频仪.本仪器可广泛应用于1~300MHz范围内各种无线电网络,接收和发射设备的扫频动态测试.例如,各种有源无源四端网络、滤波器、鉴频器及放大器等的传输特性和反射特性的测量,特别适用于各类发射和差转台、MATV系统、有线电视广播以及电缆的系统测试.其内部采用先进的表面安装技术(SMT),关键部件选用先进的优质器件,输出衰减器采用电控衰减,并采用轻触式步进控制,输出衰减由LED数字显示.确保了整机工作的可靠性,其独特的设计构思提高了仪器的性价比.本仪器功能齐全,既可1~300MHz范围内全频段一次扫频,满足宽带测试需要,也可窄带扫频和给出稳定的单频信号输出.输出动态范围大,谐波值小,输出衰减器采用电控衰减,适用于各种工作场合.具有多种标志可供用户选择.该仪器体积小,质量轻,便于携带,适合室内外各种不同工作环境,是工厂、院校和科研部门的理想的测试仪器.2.扫频仪原理简述该扫频仪仪器由扫描发生器产生20ms周期的锯齿波及方波,一路送X偏转电路供水平显示扫描用,另一路送扫描控制电路,进行信号变换.扫频方式选择等线性变换电路将从控制电路来的0~10V锯齿波电压.通过二极管网络进行变换,产生一非线性电压送到扫频振荡器,以抵消变容二极管产生的频率变换非线性.在扫频振荡器里,一个固频振荡源和一个扫频振荡源输出的正弦波信号经混频后产生1~300MHz的差频信号,并加以放大后反馈给宽带放大器放大.该放大器是一个优良的带ALC电路的宽带放大器,输出平坦度优于±0.25dB,放大后的信号一路经衰减器输出至面板输出端口,同时从宽带放大器输出电平给AGC电路以实现输出一个平坦的稳幅输出的扫频信号.一路送给频标发生器.在频标发生器中由晶体振荡器及分频产生的信号与馈人的扫频信号混频后产生差拍的菱形标记,经叠加后变换输出.扫频方式选择控制扫频振荡器的扫频变换,频标选择实现频标的组合.Y前置放大器由Y衰减选择开关选择X1、X10使用,接受从被测件检出的信号,送Y偏转电路放大后送显示器显示结果.衰减控制电路对电控衰减器输出的RF信号幅度进行控制,其范围是0~79dB,方便使用.3.扫频仪主要技术指标参数(1)有效频率范围:1—300MHz.(2)扫频方式:全扫,窄扫,点频.(3)中心频率:窄扫中心频率在1~300MHz范围内连续可调.(4)扫频宽度.全扫:优于300MHz.窄扫:±1-20MHz连续可调.点频:1~300MHz连续可调.(5)输出阻抗:75Ω(6)稳幅输出平坦度:1~300MHz范围内优于±0.35dB.(7)扫频线性:相邻10MHz线性比优于1.(8)输出衰减.粗衰减10dBX7步进,误差优于±2%A±0.5dB.细衰减1dBX9步进,误差优于±0.5dB.电控,数字显示.(9)标记种类、幅度.菱形标记:给出5010、1MHz间隔三种菱形标记.外频率标记:仪器外频标记输入端输入约6dBm的10~300MHz正弦波信号.(10)水平显示:水平幅度在0.5~1.2倍屏幕范围内连续可调,位移量大于2格.(11)工作电压:AC220±10%,50Hz±5%.(12)仪器功耗:约50W.4.扫频仪仪器的应用测量和检查(13)仪器的基本操作和检查:先接上电源,打开电源开关②,将衰减器⑧、⑨置零,扫频功能。

037音频扫频信号发生器使用说明书

当设置始点频率时,先按下始点频率开关,然后调节始点频率调 节钮。

⑾

输出频率显示 窗口

显示当前的输出频率值。

⑿ 手动扫频开关 当设置手动扫频时,先按下此开关。

⒀ 自动扫频开关 当设置自动扫频时,先按下此开关。

⒁ 终点频率开关 当设置终点频率时,先按下此开关。

⒂ 始点频率开关 当设置始点频率时,先按下此开关。

1 IQC 进料检验用。

设备名称

设备图片:

2 制程分析检验用。 17

3 维修用。

设备操作作业指导书

音频扫频信号发生器

设备型号DFFra bibliotek1615 14 13

12

11

文件编号

TL/QMC-PE-037

版/次

B/0

面板操作说明 编 名称 号 ① 电源开关

编制日期

2012-09-03

使用说明

压下时开,放开时关。

②

⒃ 耳机开关

当需要进行耳机等小信号测试时,可以按下此开关使输出电压衰 减原来的 1/4 左右,从功率输出插座输出纯真的小功率信号,更 适合耳机的纯音测试。

⒄

输出电压显示 窗口

显示当前的功率输出端口电压值。

⒅ 蜂鸣器

当功率输出过载时,蜂鸣器报警。

编制

审核

批准

邓遥

始、终点。先按下始点开关,调节始点 1

2

频率调节钮,使所显示的频率为所要求

的终点频率。再按下终点开关同上调节

终点频率调节钮并达到所需要的终点

频率。设置完毕后,应注意终点的频率

必须大于终点的频率,否则将停止扫

频。

3.根据扬声器的参数要求调节输出电压调节旋 钮,参照输出电压显示窗口实时显示的输出电 压值,设置好输出电压。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

扫频信号发生器的设计

一、设计任务

扫频技术是电子测量中的一种重要技术,广泛用于调频放大器、宽频带放大器、各种滤波器、鉴相器以及其他有源或无源网络的频率特性的测量。

所以我的设计任务是采用DDS 来设计扫频信号发生器,在KX2C5F+板上实现逻辑综合、时序仿真及功能验证,得到最终的所需要的信号。

二、设计原理

1、扫频技术的原理

将正弦信号加入线性时不变系统,其稳态响应是与输入信号相同频率的正弦量,但它的幅值和相位则决定于具体系统的动态特性。

为此,就需要分析在正弦信号作用下,一定频率范围内系统的输出量和输入量的幅值比和相位的变化规律,即系统的频率特性。

一个系统输出量与输入量之比称为频率响应函数。

即:

())()

(ωωωU Y H =

其中,频率响应的模A(ω)=∣H(ω)∣是表征输出与输入的幅度之比,称为系统的幅频特性。

频率响应的相位φ(ω)= ∠H(ω)是表征输出与输入的相位之差,称为系统的相频特性。

为了测量系统的频率响应,可以采用扫频的方法。

采用扫频的方法通常需要利用扫频信号发生器产生一定频率范围的扫频信号,并将这一信号加到被测系统的输入端。

同时,测出该系统对应的扫频输出。

则测出的输出信号与对应的输入信号幅度之比就是系统的幅频特性。

输出信号与对应的输入信号的相位之差就是系统的相频特性。

2、DDS 实现原理

DDS (Direct Digital Synthesizer )即直接数字合成器,是一种新型的频率合成技术。

具有较高的频率分辨率,可以实现快速的频率切换,并且i 改变时能够保持相位的连续,很容易实现频率、相位和幅度的数字调控。

DDS 中主要包括频率控制寄存器、相位累加器和正弦计算器3部分。

其中,频率控制寄存器用来装载并寄存输入的频率控制字加,得到正弦波的相位值;正弦计算器则计算数字化正弦波的幅度。

DDS 输出的一般是数字化的正弦波,因此还需经过D /A 转换器和低通滤波器才能得到一个可用的模拟信号。

DDS 所产生的是固定频率的信号,其频率控制字FSW 与输出信号,fout

和参考频率的fc 之间的关系为:

N clk

FSW f 2

.f out = 扫频信号源只需在DDS 原理图的基础上增加频率累加器,每来一个时钟脉冲,频率累加器根据起始频率和频率增量产生瞬时频率,然后经过相位累加器运算输出扫频信号的瞬时相位,以此相位值寻址正弦值存储表,通过查表得到与相位值对应的幅度量化值;在下个周期来临时,频率累加器一方面将在上一个时钟周期作用后所产生的新的频率数据反馈到频率加法器的输入端,以使频率加法器继续累加,频率累加的瞬时值与上一个周期相位累加器反馈到相位加法器输入端的数据累加,然后再依此周期累加的相位值重新寻址正弦值存储表,得到对应的幅度量化值。

扫频信号源需要给定起始频率fstart 终止频率fstop 和每个周期的频率增量△f ,扫频信号源的起始频率控制字start_fsw 、终止频率控制字stop_fsw 和频率增量控制字inc_fsw 分别为:

clk N

start f f fsw start 2_= clk

N

stop f f fsw 2_stop = clk

N

f f fsw 2_inc ∆=

三、设计方案

1、频率累加器

即为计数器,程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

use ieee.std_logic_unsigned.all;

entity cnt32 is

port(clk:in std_logic;

data:in std_logic_vector(31 downto 0);

dout:out std_logic_vector(31 downto 0)); end cnt32;

architecture a of cnt32 is

begin

process(clk)

variable q:std_logic_VECTOR(31 downto 0);

begin

if clk'event and clk='1'then

if q<128 then q:=q+16;

else q:=data;

end if;

end if;

dout<=q;

end process;

end a;

输出dout 即为频率控制字,并且

;16_=fsw start ;128_=fsw stop

;16_=fsw inc

根据公式N clk FSW f 2

.f out =

,可算出=start f 0.16MHZ ,25.1=stop f MHZ 2、相位累加器

相位累加器由加法器和寄存器构成。

(1)32位加法器ADDER32,由LPM_ADD_SUB 宏模块构成,设置 了2级流水线结构,使其在时钟控制下有更高的运算速度和输入数据的 稳定性。

(2)32位寄存器DFF32,由LPM_FF 宏模块担任。

ADDER32与DFF32 构成的相位累加器其低十位A[9..0]作为波形数据rom 的地址。

3、正弦函数rom

正弦波形数据rom 模块sin_rom 的地址线和数据线位宽都是10位,其 中的一个周期的正弦数据有1024 个,每个数据有10位。

Rom 中的MIF 数据文件我是使用的mif_maker 获得的。

最终设计完成的顶层文件见下图:

四、下载及测试结果

因为我所设计的是信号发生器,所以需要使用嵌入式逻辑分析仪来进行下载,产生仿真波形。

逻辑分析仪的采样部件可以随设计文件一并下载于目标芯片中,用以捕捉目标芯片内部系统节点处的信息或总线上的数据流,而且不影响原硬件系统的正常工作。

逻辑分析仪的使用有以下几个步骤:

1.新建一个SignalTap II Logic Analyzer File

2.调入待测信号

3.SignalTap II 参数设置,输入工作时钟信号Clock,在Sample Depth栏选择

采样深度为8K位。

4.保存文件

5.编译下载

6.启动SignalTap II进行采样与分析,得到如下图的采样信号

扫频信号仿真波形

五、总结

这次课程设计,我独立的完成了扫频信号发生器的设计。

开始对扫频信号是一无所知,通过看书,、上网查阅资料等方式,对扫频信号有了具体的了解,并

且对设计有了初步想法,于是设计出了最开始的框图,然后去找老师进行交流讨论,老师认为我的设计大体上可以使用,还需要注意一点细节。

我先在宿舍中完成各个模块的设计,并进行了仿真,但到了实验室中,使用板子以及逻辑分析仪进行下载采样,开始得到的波形与所要的结果相去甚远,通过该波形看出在有的正弦周期内采样点太少,导致输出的波形有正常的正弦波但还有其他杂乱的波形,我想可能是频率字有时取得太大,而导致频率太大而取样的点太少,所以减小了频率增加控制字和终止频率,通过几次改变,最终得到了理想的输出波形。

在完成这次课程设计之后其实还是挺高兴的,在实验室呆了整整一天,最终成功地完成了我的设计。

六、参考文献

《现代电子技术》2008年14期《基于FPGA的扫频信号源的研究与设计》EDA技术实用教程。