《集成电路设计原理》试卷及答案课件

集成电路设计原理2006年春季A卷

集成电路设计原理2006年春季A卷哈尔滨工业大学(威海) 2005 /2006 学年春季学期集成电路设计原理试题卷(A )考试形式(开、闭卷):闭答题时间: 120 (分钟)本卷面成绩占课程成绩 70 %一、填空题(每题1分,共15分)1. 在MOS 电流镜电路中沟道长度选择大一些有利于_______(增大、减小)电流源的输出电阻和减小__________________效应对输出电流的影响。

2. 在N 阱CMOS 集成电路中,n 阱作为___________管的衬底,一般接________电位。

3. NMOS 传输门不能很好地传输__________电平, 其W/L 越大,导通电阻越,传输速度越。

4. 有比电路是指输出低电平与输入管和负载管的____________之比有关。

5. 集成电路中的元器件因为要做在同一个衬底上,因此不同于分离器件,会存在。

6. 写出考虑沟道调制效应时MOS 管工作在饱和区的漏极电流公式。

7. 采用全定制(full-custom)方法设计的集成电路集成度(高、低),适用于(通用、专用)集成电路芯片的设计。

姓名: 班级:学号:遵守考试纪律注意行为规范8.一个DAc工作时的参考电压为V ref,接收n位的数字信号(b1b2…. b n),最低有效位用LSB表示,则LSB等于,其分辨率为,量化噪声最大为。

二、(共15分)右图是一N阱CMOS工艺电路的版图。

1.画出对应的电路图(7分);2.分析电路功能,写出逻辑表达式(2分);3.按工艺流程的先后顺序,写图中所用到的光刻掩膜版名称,并在图中选择典型图形标明(6分)。

AFB C三、(共8分)下图中V in为一模拟集成电路的一输入端,为其画出采用MOS 管形式的抗静电保护电路,阐述其工作原理并说明对保护管尺寸有何要求(8分);V SS1.说明TTL电路单管逻辑门级联时的三问题(3分);2.简述ECL电路和I2L电路的特点(4分);3.阐述CMOS电路中抗闩锁设计的重要性(3分)。

《集成电路设计(第2版)》习题答案1-5章

9. MOSFET 存在哪些二阶效应?分别是由什么原因引起的? P.70-73 沟道长度调制效应,体效应,亚阈值效应 10.说明 MOSFET 噪声的来源、成因及减小的方法。 噪声来源:热噪声和闪烁噪声。热噪声是由沟道内载流子的无规则热运动造成的,可通 过增加 MOS 管的栅宽和偏置电流减少热噪声。闪烁噪声是由沟道处二氧化硅与硅界面上电 子的充放电引起的,增加栅长栅宽可降低闪烁噪声。

CH3

1. 写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。 意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。外延方法: 液态生长,气相外延生长,金属有机物气相外延生长 2.写出掩膜在 IC 制造过程中的作用,比较整版掩膜和单片掩膜的区别,列举三种掩膜的制 造方法。P28,29 3.写出光刻的作用,光刻有哪两种曝光方式? 作用: 把掩膜上的图形转换成晶圆上的器 件结构。曝光方式有接触与非接触两种。 4.X 射线制版和直接电子束直写技术替代光刻技术有什么优缺点? X 射线(X-ray)具有比可见光短得多的波长,可波长很短,分辨率很高 5. 说出半导体工艺中掺杂的作用,举出两种掺杂方法,并比较其优缺点。 热扩散掺杂和离子注入法。与热扩散相比,离子注入法的优点如下:1.掺杂的过程可通 过调整杂质剂量与能量来精确控制杂质分布。2.可进行小剂量的掺杂。3.可进行极小深度的 掺杂。4.较低的工业温度,故光刻胶可用作掩膜。5.可供掺杂的离子种类较多,离子注入法 也可用于制作隔离岛。缺点:价格昂贵,大剂量注入时,半导体晶格会遭到严重破坏且难以 恢复 6.列出干法和湿法氧化法形成 SiO2 的化学反应式。 干氧 Si O2 SiO2 湿氧 Si 2 H 2 O SiO2 2 H 2

怎样的条件下金属与半导体形成肖特基接接触区半导体重掺杂可实现欧姆接触金属与掺杂半导体接触形成肖特基接触4

集成电路设计原理考核试卷

4.描述模拟集成电路与数字集成电路在设计原则和实现技术上的主要区别,并给出一个实际应用中模拟集成电路的例子。

标准答案

一、单项选择题

1. B

2. B

3. D

4. D

5. B

6. D

7. C

8. C

9. B

10. D

17.在集成电路设计中,以下哪些方法可以提高电路的抗干扰能力?( )

A.采用差分信号传输

B.使用屏蔽技术

C.增加电源滤波器

D.提高工作频率

18.以下哪些类型的触发器在数字电路中常见?( )

A. D触发器

B. JK触发器

C. T触发器

D. SR触发器

19.以下哪些技术可以用于提高集成电路的数据处理速度?( )

3.以下哪些是数字集成电路的基本组成部分?( )

A.逻辑门

B.触发器

C.寄生电容

D.晶体管

4.以下哪些技术可以用于提高集成电路的频率?( )

A.减小晶体管尺寸

B.采用高介电常数材料

C.增加电源电压

D.优化互连线设计

5.在CMOS工艺中,以下哪些结构可以用来实现反相器?( )

A. PMOS晶体管

B. NMOS晶体管

11. C

12A

16. B

17. A

18. A

19. C

20. B

二、多选题

1. ABD

2. AB

3. AD

4. AB

5. AB

6. AB

7. ABCD

8. AB

9. ABCD

10. AC

11. ABC

10微电子《集成电路设计原理》试卷(B卷)

(增大、减小、

命题人

题号

线

陈初侠

一Байду номын сангаас

统分人

二 三

复核人

四

V,Y3=

V。

得分 一、填空题: (共 30 分)

10. (6 分) 写出下列电路输出信号的逻辑表达式: Y1= Y2=

VDD C B A

;

得分

评卷人

;C2=

。

VDD C4 C3 C2 C1

考试时间

VDD A

P4 P3

订

1.(2 分)

考场(教室)

3.CMOS 反相器中的 NMOS 管和 PMOS 管是增强型还是耗尽型,为什么?

线

得分

评卷人

四、分析设计题: (共 38 分)

考试时间

订

4.简述传输门阵列的优缺点。

1.(12 分)标准 0.13 m CMOS 工艺,PMOS 管 W/L= 0.26 m / 0.13

m ,栅氧厚度为 tox 2.6nm ,室温下空穴迁移率 n 80 cm2 /

班级

第 2 页 共 3 页(B 卷)

2. (12 分)如图所示,M1 和 M2 两管串联,且 VB VG VT VA ,请问: 1) 若都是 PMOS,它们各工作在什么状态? 2) 证明两管串联的等效导电因子是

Keff K1K2 /( K1 K2 ) 。

3. (14 分)设计一个 CMOS 两输入或非门,要求在最坏情况下输 出上升时间和下降时间不大于 0.5ns。已知,CL=1pF,VDD=5V,

' VTN=0.8V,VTP=-0.9V,采用 0.6μm 工艺,有 K N 120 106 A / V 2 ,

湖南大学物电院集成电路试卷及答案 (7)

评卷人

一、简答题 1. 使用超 β 晶体管作运放的输入管,对运放的性能有何影响? 2. CMOS 电路是否在任何情况下均为微功耗电路?为什么? 3. 什么是失调?产生失调的主要原因是什么? 4. 横向 PNP 管的版图结构为什么总是采用集电区包围发射区的方式? 5. 衡量一个逻辑电路静态特性的优劣主要有那三方面的指标?

考试中心填写:

湖南大学课程考试试卷

… … … … … … … … … … … … … … … … … … … 装 订 ( 答 题 不 得 超 过 此

课题名称: 集成电路原理;试卷编号: H(开卷) 考试时间:120 分钟

题号 应得分 实得分 一 二 三 四 五 六 七 八 九 十 总分 100 评分:

二、画出 COMS 倒相器的剖面结构,分析产生锁定效应的原因,并指出消除 锁定效应的主要措施

线 ):

三、画出 CMOS 倒相器原理图,定性作出其电压传输特性曲线,推导其上升 时间和下降时间。

四、分析、论述

… … …

某公司生产的运算放大器其开环电压增益存在正负半周不对称的问题, 1: 试分析主要原因。 2:TTL 输入晶体管为什么采用长脖基区的版图结构? 3:CMOS 又称为互补对称 MOS,是否意味着其倒相器设计时,N 管和 P 管的版图结构也必须对称?

:

第 1 页(共 3 页)

五、分析图示基准源电路的工作原理,指出电路中每一个元件的作用,并总结 其性能特点。

六、分析图示电路的工作原理,指出每个元件的作用,并给出逻辑关系。

第 2 页(共 3 页)

七、图示 µA741 偏置电路,分析电路原理,指出每个元件的作用。

第 3 页(共 3 页)

半导体集成电路考试题目与参考答案

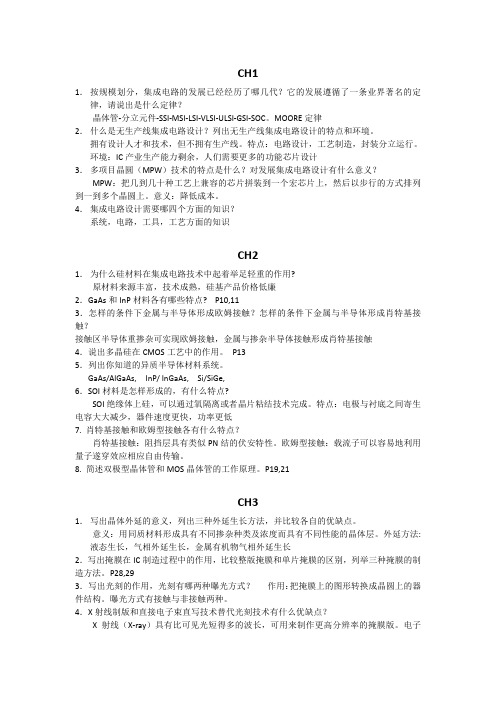

第一部分考试试题第0章绪论1.什么叫半导体集成电路?2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写?3.按照器件类型分,半导体集成电路分为哪几类?4.按电路功能或信号类型分,半导体集成电路分为哪几类?5.什么是特征尺寸?它对集成电路工艺有何影响?6.名词解释:集成度、wafer size、die size、摩尔定律?第1章集成电路的基本制造工艺1.四层三结的结构的双极型晶体管中隐埋层的作用?2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。

3.简单叙述一下pn结隔离的NPN晶体管的光刻步骤?4.简述硅栅p阱CMOS的光刻步骤?5.以p阱CMOS工艺为基础的BiCMOS的有哪些不足?6.以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法。

7. 请画出NPN晶体管的版图,并且标注各层掺杂区域类型。

8.请画出CMOS反相器的版图,并标注各层掺杂类型和输入输出端子。

第2章集成电路中的晶体管及其寄生效应1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。

2.什么是集成双极晶体管的无源寄生效应?3. 什么是MOS晶体管的有源寄生效应?4. 什么是MOS晶体管的闩锁效应,其对晶体管有什么影响?5. 消除“Latch-up”效应的方法?6.如何解决MOS器件的场区寄生MOSFET效应?7. 如何解决MOS器件中的寄生双极晶体管效应?第3章集成电路中的无源元件1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些?2.集成电路中常用的电容有哪些。

3. 为什么基区薄层电阻需要修正。

4. 为什么新的工艺中要用铜布线取代铝布线。

5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。

第4章TTL电路1.名词解释电压传输特性 开门/关门电平 逻辑摆幅 过渡区宽度 输入短路电流 输入漏电流静态功耗 瞬态延迟时间 瞬态存储时间 瞬态上升时间 瞬态下降时间瞬时导通时间2. 分析四管标准TTL 与非门(稳态时)各管的工作状态?3. 在四管标准与非门中,那个管子会对瞬态特性影响最大,并分析原因以及带来那些困难。

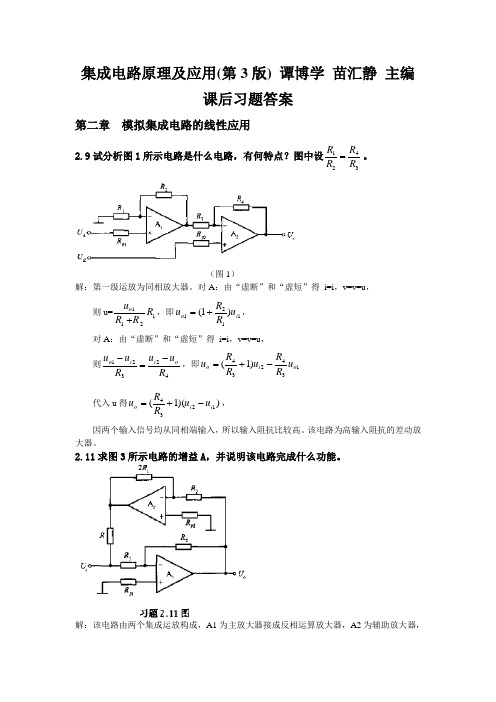

集成电路原理及应用课后答案

6.4如图1所示,当分别取如下两组参数时,试分别求出该电路的G,,等参数。

(1)R=R=24kΩ,C=940pF,C=470pF,R=。

(2)R=7.3kΩ,R=39.4kΩ,C=C=0.047F,R=4kΩ,R=20kΩ。

(图6.4)

解:由电路得:

则当取⑴参数时:

当取⑵参数时: ,

因两个输入信号均从同相端输入,所以输入阻抗比较高。该电路为高输入阻抗的差动放大器。

2.11求图3所示电路的增益A,并说明该电路完成什么功能。

解:该电路由两个集成运放构成,A1为主放大器接成反相运算放大器,A2为辅助放大器,A2也接成反相放大器,利用A2对A1构成正反馈,是整个电路向信号源索取的电流极少。

解:电路图如下所示:

选择巴特沃斯型滤波器

则 又

令R=R=R, C=C=C取C=0.1F则R=160Ω,

又 ,则=1.586

又 取R=58.6KΩ,则R=100KΩ。

2.16设计一个运算电路,要求运算关系为u=20 。

解:此题设计方法较多,此只列举几种仅供参考

方法一:将求和电路的输出作为积分电路的输入,则积分电路的输出即为u;

方法二:将积分电路的输出作为求和电路的输入,则求和电路的输出即为u;

方法三:反相积分求和电路再加一个倒相器;

方法四:利用同相积分求和电路。

当u<0时,VD截止,VD导通,

对A:u=(1+ )u,对A:u=u=u,

此时u= (R+R 1)u

当 (R+R )=1时,完成全波整流功能;由于为同相输入,故该电路输入电阻较高。

3.8 设计一个能实现图4所示曲线的二极管函数变换器。

(习题3.8图)

《集成电路设计原理》试卷及答案

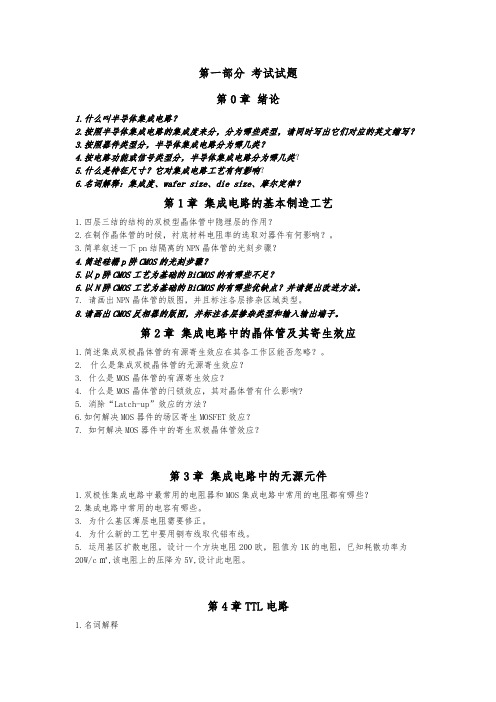

电科《集成电路原理》期末考试试卷一、填空题1.(1分) 年,第一次观测到了具有放大作用的晶体管。

2.(2分)摩尔定律是指 。

3.集成电路按工作原理来分可分为 、 、 。

4.(4分)光刻的工艺过程有底膜处理、涂胶、前烘、 、 、 、 和去胶。

5.(4分)MOSFET可以分为 、 、 、 四种基本类型。

6.(3分)影响MOSFET 阈值电压的因素有: 、 以及 。

7.(2分)在CMOS 反相器中,V in ,V out 分别作为PMOS 和NMOS 的 和 ; 作为PMOS 的源极和体端, 作为NMOS 的源极和体端。

8.(2分)CMOS 逻辑电路的功耗可以分为 和 。

9.(3分)下图的传输门阵列中5DD V V =,各管的阈值电压1T V V =,电路中各节点的初始电压为0,如果不考虑衬偏效应,则各输出节点的输出电压Y 1= V ,Y 2= V ,Y 3= V 。

DD 13210.(6分)写出下列电路输出信号的逻辑表达式:Y 1= ;Y 2= ;Y 3= 。

AB Y 1AB23二、画图题:(共12分)1.(6分)画出由静态CMOS电路实现逻辑关系Y ABD CD=+的电路图,要求使用的MOS管最少。

2.(6分)用动态电路级联实现逻辑功能Y ABC=,画出其相应的电路图。

三、简答题:(每小题5分,共20分)1.简单说明n阱CMOS的制作工艺流程,n阱的作用是什么?2.场区氧化的作用是什么,采用LOCOS工艺有什么缺点,更好的隔离方法是什么?3.简述静态CMOS 电路的优点。

4.简述动态电路的优点和存在的问题。

四、分析设计题:(共38分1.(12分)考虑标准0.13m μ CMOS 工艺下NMOS 管,宽长比为W/L=0.26/0.13m m μμ,栅氧厚度为2.6ox t nm =,室温下电子迁移率2220/n cm V s μ=,阈值电压T V =0.3V,计算 1.0GS V =V 、0.3DS V =V 和0.9V 时D I 的大小。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

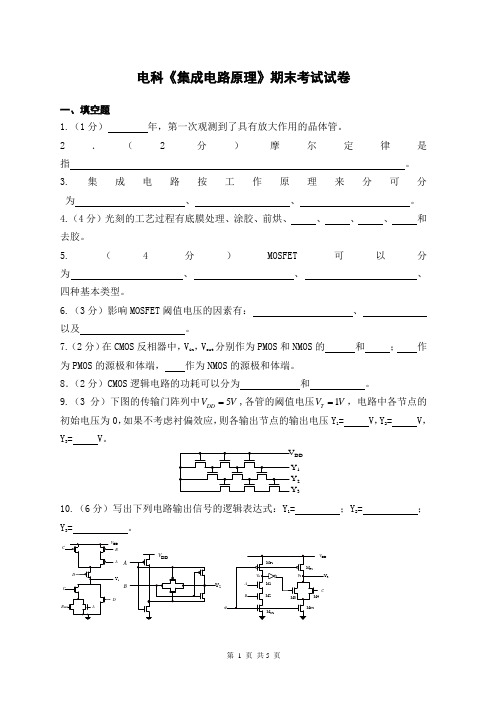

电科《集成电路原理》期末考试试卷一、填空题1.(1分) 年,第一次观测到了具有放大作用的晶体管。

2.(2分)摩尔定律是指 。

3.集成电路按工作原理来分可分为 、 、 。

4.(4分)光刻的工艺过程有底膜处理、涂胶、前烘、 、 、 、 和去胶。

5.(4分)MOSFET 可以分为 增强型NMOS ,耗尽型NMOS ,增强型PMOS ,耗尽型PMOS___四种基本类型。

6.(3分)影响MOSFET 阈值电压的因素有: 、 以及 。

7.(2分)在CMOS 反相器中,V in ,V out 分别作为PMOS 和NMOS 的 栅极, 和 漏极 ; VDD , 作为PMOS 的源极和体端, ,GND 作为NMOS 的源极和体端。

8.(2分)CMOS 逻辑电路的功耗可以分为 和 。

9.(3分)下图的传输门阵列中5DD V V =,各管的阈值电压1T V V =,电路中各节点的初始电压为0,如果不考虑衬偏效应,则各输出节点的输出电压Y 1= 4 V ,Y 2= 3 V ,Y 3= 3 V 。

DD 13210.(6分)写出下列电路输出信号的逻辑表达式:Y 1= ;Y 2= ;Y 3= 。

AB Y 1AB23二、画图题:(共12分)1.(6分)画出由静态CMOS电路实现逻辑关系Y ABD CD=+的电路图,要求使用的MOS管最少。

2.(6分)用动态电路级联实现逻辑功能Y ABC=,画出其相应的电路图。

三、简答题:(每小题5分,共20分)1.简单说明n阱CMOS的制作工艺流程,n阱的作用是什么?2.场区氧化的作用是什么,采用LOCOS工艺有什么缺点,更好的隔离方法是什么?3.简述静态CMOS电路的优点。

4.简述动态电路的优点和存在的问题。

四、分析设计题:(共38分1.(12分)考虑标准0.13m μ CMOS 工艺下NMOS 管,宽长比为W/L=0.26/0.13m m μμ,栅氧厚度为2.6ox t nm =,室温下电子迁移率2220/n cm V s μ=,阈值电压T V =0.3V,计算 1.0GS V =V 、0.3DS V =V 和0.9V 时D I 的大小。

已知:148.8510/o F cm ε-=⨯, 3.9ox ε=。

2.(12分)如图所示,M1和M2两管串联,且B G T A V V V V <-<,请问: 1) 若都是NMOS ,它们各工作在什么状态? 2) 若都是PMOS ,它们各工作在什么状态?3) 证明两管串联的等效导电因子是eff K =1212/()K K K K +。

3.(14分)设计一个CMOS 反相器,要求在驱动10fF 外部负载电容的情况下,输出上升时间和下降时间都不能大于40ps ,并要求最大噪声容限不小于0.55V 。

针对0.13m μ工艺,已知:0.30TN V V =,0.28TP V V =-,2220/n cm V s μ=,276/p cm V s μ=, 2.6ox t nm =,148.8510/o F cm ε-=⨯, 3.9ox ε=, 1.2DD V V =,ln14.33=2.66,ln14=2.64。

《集成电路原理》期末考试试卷 参考答案一、填空题:(共30分)1.(1分)1947 2.(2分)集成电路中的晶体管数目(也就是集成度)大约每18个月翻一番 3.(3分)数字集成电路,模拟集成电路,数模混合集成电路 4.(4分)曝光,显影,坚膜,刻蚀 5.(4分)增强型NMOS ,耗尽型NMOS ,增强型PMOS ,耗尽型PMOS 6.(3分)栅电极材料,栅氧化层的质量和厚度,衬底掺杂浓度 7.(2分)栅极,漏极,VDD ,GND 8.(2分)动态功耗,静态功耗 9.(3分)4,3,2 10.(6分)()A B C D ++,AB AB +,AB C +二、画图题:(共12分)1.(6分) 2.(6分)Y3三、简答题:(每小题5分,共20分)1.答:n 阱CMOS 的制作工艺流程:1.准备硅片材料;2.形成n 阱;3.场区隔离;4.形成多晶硅栅;5.源漏区n+/p+注入;6.形成接触孔;7.形成金属互连;8.形成钝化层。

n 阱的作用:作为PMOS 管的衬底,把PMOS 管做在n 阱里。

2.答:场区氧化的作用:隔离MOS 晶体管。

LOCOS 工艺的缺点:会形成鸟嘴,使有源区面积比版图设计的小。

更好的隔离方法:浅槽隔离技术。

3.答:1.是一无比电路,具有最大的逻辑摆幅;2.在低电平状态不存在直流导通电流;3.静态功耗低;4.直流噪声容限大;5.采用对称设计获得最佳性能。

4.答:动态电路的优点:1.减少了MOS 管数目,有利于减小面积;2.减小了电容,有利于提高速度;3.保持了无比电路的特点。

动态电路存在的问题:1.靠电荷存储效应保存信息,影响电路的可靠性;2.存在电荷分享、级联、电荷泄漏等问题;3.需要时钟信号控制,增加设计复杂性。

四、分析设计题:(共38分)1.(12分)解:计算MOSFET 导电因子β:142073.98.85100.26()()220584.1()2.6100.13ox n ox n ox W W C A V L t L εεβμμμ---⨯⨯===⨯⨯=⨯ 4分 当 1.0GS V =V(>T V =0.3V)、0.3DS V =V(<0.7GS T V V V -=)时,NMOS 管处于线性区,线性区电流为:21[()]96.3765()2D GS T DS DS I V V V V A βμ=--= 4分当 1.0GS V =V(>T V =0.3V)、0.9DS V =V(>0.7GS T V V V -=)时,NMOS 管处于饱和区,饱和区电流为:2()143.1045()2D GS T I V V A βμ=-= 4分2.(12分)解:1) 设中间节点为C 。

分析知当电压满足V B < V G - V T < V A 时,在电路达到稳态之后,M1和M2都导通。

于是对M1而言,有GS V 0T V ->,即 Vc < V G -V T 。

又V G - V T < V A ,即GS V DS T V V >-,故M1工作于饱和区。

而对M2而言,有GS V T DS V V ->,故M2工作于线性区。

3分 2) 依据NMOSFET 和PMOSFET 的电压反转对称性知,若两管都是PMOSFET ,则M1工作于线性区,M2工作于饱和区。

3分3) 取一例证明。

以此题中的NMOSFET 和给定的偏压为例,两个NMOS 管等效为一个NMOS 管后,依V B < V G - V T < V A 知该等效管应工作于饱和区。

故对M1、M2和等效管Meff 有:21122222()[()()]()D G T C D G T B G T C Deff eff G T B I K V V V I K V V V V V V I K V V V ⎧=--⎪=-----⎨⎪=--⎩则有1212DeffD D effI I I K K K +=由1D I =2D I =Deff I 知: 12111eff K K K += 即K eff = K 1 K 2 / (K 1 + K 2) 6分3.(14分)解:先考虑瞬态特性要求:由()20.1 1.9212(1)0.1(1)0.280.2331.2ln TPPDDPPPPLP DDr r C r K V V V t αααααττ----=-=+===⎧⎡⎤⎪⎣⎦⎪⎪⎨⎪⎪⎪⎩()20.1 1.9212(1)0.1(1)0.30.251.2ln TNNDDNNNNLN DDf f C f K VV V t αααααττ----=-=+===⎧⎡⎤⎪⎣⎦⎪⎪⎨⎪⎪⎪⎩(4分)得424.0810/PKA V-=⨯,424.2210/NKA V-=⨯ (2分)而0OXOX11()()2211()()22OXPPPPPOXOXNNnNnOXWWK C LL tWWK C LL tεεμμεεμμ====⎧⎪⎪⎨⎪⎪⎩(2分)代入相关参数可得()8.09() 2.89PNW LW L==⎧⎪⎨⎪⎩,即{1.0520.376PNm mWWμμ== (2分)考察噪声容限:由it0.607V V == (2分)得:{0.6070.550.5930.55NLMitNLMDDitVV V VVV V V V==>=-=> (2分)所以所设计的CMOS 反相器符合题意要求,即{1.0520.376PNm mWWμμ==。