电子设计自动化(EDA)期末必考题目汇总

eda期末考试复习题

eda期末考试复习题EDA期末考试复习题一、选择题(每题2分,共20分)1. EDA(Electronic Design Automation)是指:A. 电子设计自动化B. 电子数据交换C. 电子文档自动化D. 电子设备自动化2. 在EDA工具中,用于设计和仿真数字逻辑电路的软件是:A. MATLABB. VHDLC. SPICED. AutoCAD3. 下列哪个不是硬件描述语言(HDL)?A. VerilogB. VHDLC. C++D. SystemVerilog4. FPGA(Field-Programmable Gate Array)是一种:A. 可编程逻辑器件B. 微处理器C. 存储器D. 网络设备5. 在VHDL中,以下哪个关键字用于定义实体?A. entityB. architectureC. processD. package6. 以下哪个是模拟电路设计中常用的EDA工具?A. Quartus IIB. ModelSimC. CadenceD. Xilinx ISE7. 以下哪个不是数字电路设计中的基本逻辑门?A. ANDB. ORC. NOTD. XOR8. 在VHDL中,以下哪个是并行赋值语句?A. ifB. caseC. loopD. when9. 在EDA设计流程中,仿真验证的目的是:A. 检查电路是否能正常工作B. 检查电路的物理尺寸C. 检查电路的功耗D. 检查电路的散热性能10. 以下哪个不是EDA设计流程中的步骤?A. 电路设计B. 仿真验证C. 版图设计D. 电路测试二、填空题(每空2分,共20分)11. 在VHDL中,用于定义端口的关键字是________。

12. FPGA的编程方式包括________和________。

13. 一个完整的EDA设计流程通常包括________、________、________、________和________。

14. 在数字电路设计中,________是一种用于描述电路行为的建模方式。

EDA习题集

《电子设计自动化(EDA)》习题集第一章、EDA技术概述一、填空题1、一般把EDA技术的发展分为 、、 三个阶段。

2、EDA设计流程包括 、 、、 四个步骤。

3、EDA的设计验证包括 、 、 三个过程。

4、EDA的设计输入包括 、 、 。

5、当前最流行的并成为IEEE标准的硬件描述语言包括和 。

6、将硬件描述语言转化为硬件电路的重要工具软件称为 。

二、单项选择题1、VHDL语言属于 描述语言。

A.普通硬件 B. 行为 C. 高级D. 低级2、基于硬件描述语言HDL的数字系统设计目前最常用的设计方法为A. 自底向上B. 自顶向下C. 积木式D. 顶层3、在EDA工具中,能将硬件描述语言转化为硬件电路的重要工具软件称为A.仿真器 B. 综合器 C. 适配器 D.下载器4、在EDA工具中,能完成目标系统器件上布局软件称为A.仿真器 B. 综合器 C. 适配器 D.下载器 第2章、大规模可编程逻辑器件 一、填空题1、集成度是集成电路一项重要的指标,可编程逻辑器件按集成密度可分为 和 两类。

2、可编程逻辑器件的编程方式可分为 和 两类。

3、基于EPROM、E2PROM和快闪存储器件的可编程器件,在系统断电后编程信息 。

4、基于SRAM结构的可编程器件,在系统断电后编程信息 。

5、CPLD器件中至少包括 、 、 三种结构。

6、FPGA的三种可编程电路分别是 、、 三种结构。

7、根据逻辑功能块的大小不同,可将FPGA分为和 两类;据FPGA内部连线结构的不同,可将FPGA分为 和 两类;据FPGA采用的开关元件不同,可将FPGA分为 和 两类.8、目前常见的可编程逻辑器件的编程和配置工艺包括基于 、基于 和基于 三种编程工艺。

二、 单项选择题1、在下列可编程逻辑器件中,不属于高密度可编程逻辑器件的是A. EPLDB. CPLDC. FPGAD. PAL2、在下列可编程逻辑器件中,属于易失性器件的是A. EPLDB. CPLDC. FPGAD. PAL3、在自顶向下的设计过程中,描述器件总功能的模块一般称为A.底层设计 B. 顶层设计 C. 完整设计 D. 全面设计4、边界扫描测试技术主要解决 的测试问题A.印制电路板 B. 数字系统 C. 芯片 D. 微处理器 三、 简答题1、CPLD和FPGA有什么差异?在实际应用中各有什么特点?第3章、VHDL编程基础一、填空题1、VHDL设计实体的基本结构由 、、 、 和 等部分组成。

eda期末考试试题及答案

eda期末考试试题及答案EDA期末考试试题及答案一、选择题(每题2分,共20分)1. EDA(电子设计自动化)主要应用于以下哪个领域?A. 机械设计B. 建筑设计C. 电子电路设计D. 软件开发答案:C2. 在EDA软件中,以下哪个不是常见的设计流程?A. 原理图设计B. 电路仿真C. 手动布线D. 封装设计答案:C3. 下列哪个不是EDA工具的组成部分?A. 原理图编辑器B. PCB布局工具C. 3D建模软件D. 仿真分析工具答案:C4. 在EDA设计中,PCB指的是什么?A. 印刷电路板B. 个人计算机C. 程序控制板D. 功率控制板答案:A5. 以下哪个是EDA设计中常用的文件格式?A. .txtB. .pdfC. .schD. .jpg答案:C...(此处省略其他选择题)二、简答题(每题10分,共30分)1. 简述EDA设计流程的主要步骤。

答案:EDA设计流程通常包括原理图设计、电路仿真、PCB布局、布线、封装设计、测试与验证等步骤。

2. 解释什么是PCB布线,并说明其重要性。

答案:PCB布线是指在印刷电路板上将电子元件的引脚通过导电路径连接起来的过程。

布线的重要性在于它直接影响电路的性能、可靠性和生产成本。

3. 描述电路仿真在EDA设计中的作用。

答案:电路仿真在EDA设计中用于模拟电路在不同条件下的行为,帮助设计者预测电路的性能,优化设计,并在实际制造之前发现潜在的问题。

三、计算题(每题15分,共30分)1. 给定一个简单的RC电路,计算其时间常数τ。

答案:时间常数τ是电容C和电阻R的乘积,即τ = R * C。

2. 假设一个电路的输入信号频率为1kHz,计算其周期T。

答案:周期T是频率f的倒数,即T = 1/f = 1/1000Hz = 1ms。

四、设计题(20分)设计一个简单的放大器电路,并使用EDA工具绘制其原理图。

答案:(此处应有原理图,但无法提供图像,故省略)五、论述题(20分)论述在现代电子设计中,EDA工具的重要性及其对设计流程的影响。

EDA期末必考选择题及答案

老师发话了。

EDA考试题目:大题第一题考奇数分频,名称解释考:SOPC,期中考的TTL和coms的连接方式不考大题第一题考奇数分频,名称解释考:SOPC,期中考的TTL和coms的连接方式不考1、IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为____A___。

A .软IP B.固IP C.硬IP D.都不是2、综合是EDA设计流程的关键步骤,在下面对综合的描述中,___D_是错误的。

A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的)。

3、大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是_C。

A.FPGA是基于乘积项结构的可编程逻辑器件;B.FPGA是全称为复杂可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

4、进程中的变量赋值语句,其变量更新是___A__。

A.立即完成;B.按顺序完成;C.在进程的最后完成;D.都不对。

5、VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述__D__。

A.器件外部特性;B.器件的综合约束;C.器件外部特性与内部功能;D.器件的内部功能。

6、不完整的IF语句,其综合结果可实现_A___。

A. 时序逻辑电路B. 组合逻辑电路C. 双向电路D. 三态控制电路7、在VHDL语言中,下列对时钟边沿检测描述中,错误的是___D____。

EDA期末复习题试题

复习题(开卷)一、填空题与简答题1、ASIC的中文含义是:专用集成电路。

2、在VHDL中主要有哪三种重载现象参数类型的重载;参数数目的重载;函数返回类型的重载。

3、简单可编程逻辑器件的主要有PROM、PLA、PAL、GAL4、CPLD内部含有多个逻辑单元块,每个逻辑单元块相当于一个GAL器件:5、在设计中,常常采用的设计方法有直接设计方法、自顶向下和自底向上的设计方法。

6、CPLD的一般采用“与-或阵列”结构。

7、一个完整的VHDL程序包括库、程序包、实体、结构体和配置五个部分。

8、PLD的中文含义是:可编程逻辑器件。

9、“与-或”结构的可编程逻辑器件主要由四部分构成:输入电路、可编程“与”阵列、可编程或阵列、输出电路10、FPGA的一般采用“查找表”结构。

11.VHDL的全拼Very high speed integrated Hardware Description Language12.子程序有即过程(PROCEDURE)、函数〔FUNCTION〕两种类型。

13、CPLD的中文含义是复杂可编程逻辑器件。

14、复杂可编程逻辑器件的主要有CPLD 和FPGA 。

15、FPGA的中文含义是现场可编程门阵列。

16.CPLD的基本结构看成由可编程逻辑宏单元可编程I/O控制模块和可编程内部连线组成。

17.FPGA由可编程逻辑块(CLB)、可编程互连单元(I/O)和可编程互连三种可编程电路和一个SRAM结构的配置存储单元组成。

18.EDA:电子设计自动化B:逻辑阵列块20.ESB:嵌入式系统块21.FAST TRACK:快速通道22.同步:各个逻辑单元共用一个时钟23.信号与变量使用时有何区别?答:(1)值的代入形式不同。

(2)变量值可以送给信号,信号值不能送给变量。

(3)信号是全局量,变量是局部量。

(4)操作过程不同。

24.VHDL语言在结构上分为哪几部分?答:VHDL语言在结构上一般分为实体(ENTITY)与结构体(ARCHITECTURE)两大部分。

(完整word版)EDA期末考试试卷及答案

第1页(共5页)班级 学号 姓名密 封 线 内 不 得 答 题一、单项选择题(30分,每题2分) 1.以下关于适配描述错误的是 BA .适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件B .适配所选定的目标器件可以不属于原综合器指定的目标器件系列C .适配完成后可以利用适配所产生的仿真文件作精确的时序仿真D .通常,EDAL 软件中的综合器可由专业的第三方EDA 公司提供,而适配器则需由FPGA/CPLD 供应商提供2.VHDL 语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。

A .器件外部特性B .器件的综合约束C .器件外部特性与内部功能D .器件的内部功能 3.下列标识符中, B 是不合法的标识符。

A .State0B .9moonC .Not_Ack_0D .signall4.以下工具中属于FPGA/CPLD 集成化开发工具的是 DA .ModelSimB .Synplify ProC .MA TLABD .QuartusII 5.进程中的变量赋值语句,其变量更新是 A 。

A .立即完成B .按顺序完成C .在进程的最后完成D .都不对6.以下关于CASE 语句描述中错误的是 AA .CASE 语句执行中可以不必选中所列条件名的一条B .除非所有条件句的选择值能完整覆盖CASE 语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语句>”C .CASE 语句中的选择值只能出现一次D . WHEN 条件句中的选择值或标识符所代表的值必须在表达式的取值范围7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A .STD_LOGIC_ARITH B .STD_LOGIC_1164C .STD_LOGIC_UNSIGNEDD .STD_LOGIC_SIGNED8.基于EDA 软件的FPGA / CPLD 设计流程为:原理图/HDL 文本输入→ A →综合→适配→时序仿真→编程下载→硬件测试。

eda期末考试题目及答案

eda期末考试题目及答案一、选择题(每题2分,共20分)1. EDA(电子设计自动化)的主要功能是什么?A. 电路设计B. 电路仿真C. 电路测试D. 所有以上选项2. 在EDA中,HDL指的是什么?A. 高级设计语言B. 硬件描述语言C. 硬件开发语言D. 硬件描述逻辑3. 下列哪个不是EDA工具的主要组成部分?A. 原理图编辑器B. 仿真器C. 编译器D. 汇编器4. 在EDA中,FPGA代表什么?A. 现场可编程门阵列B. 固定可编程门阵列C. 功能可编程门阵列D. 快速可编程门阵列5. 以下哪个是EDA设计流程中的必要步骤?A. 原理图绘制B. 电路板布局C. 焊接D. 电路测试二、填空题(每空2分,共20分)6. 常见的EDA软件有______、______和______。

答案:Cadence, Altium Designer, Mentor Graphics7. 在EDA中,______是一种用于设计和验证数字电路的图形化编程语言。

答案:VHDL8. EDA工具可以帮助工程师进行______和______。

答案:设计优化,性能分析9. 与ASIC相比,FPGA的优点是______和______。

答案:灵活性高,开发周期短10. 在EDA设计中,布局和布线是实现______的关键步骤。

答案:电路板物理结构三、简答题(每题10分,共30分)11. 简述EDA在现代电子设计中的重要性。

答案:EDA在现代电子设计中的重要性体现在它能够提高设计效率,降低成本,缩短产品上市时间,同时提高设计的可靠性和可维护性。

12. 解释什么是仿真,并说明在EDA设计流程中仿真的作用。

答案:仿真是一种模拟实际电路在不同条件下行为的技术。

在EDA 设计流程中,仿真用于验证设计的正确性,预测电路的性能,以及发现潜在的问题,从而在实际制造之前进行必要的修改。

13. 描述FPGA与ASIC在应用上的主要区别。

答案:FPGA是一种可编程的硬件,可以在设计完成后重新配置,适用于需要快速原型开发和灵活设计调整的场景。

电子设计自动化(eda)期末考试试题及答案

任课教师教研室主任签名教学院长签名成绩统计表题号一二三四五六七八合计得分阅卷人考生姓名:____________ 学号___________ 专业班级一、判断题(10分)(1)适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,产生最终的下载文件()(2)硬IP提供设计的最终阶段产品:掩模。

()(3)MAX7000的一个LAB由16个宏单元的阵列组成。

()(4)FPGA是基于查找表结构的器件。

()(5)在QUARTUSⅡ中,工作文件夹允许是根目录。

( )(6)STD_LOGIC中,‘0’,‘1’,‘Z’,‘W’可以综合。

()(7)在case语句中允许有相同选择值的条件句出现。

()(8)在vhdl中常量具有全局性。

()(9)在vhdl中变量可在结构体和进程中定义和使用。

()(10)在进程中同一信号有多个赋值源,实际完成赋值的是最接近begin 的信号。

()二、简答题(15分)1、简述fpga/cpld的设计流程。

(5分)2、在vhdl中端口模式有那几种?并说明数据流动方向。

(4分)3、简述一般状态机的结构及各部分的作用。

(6分)三、改错;找到5处错误并改正(10分)LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY CNT4 ISPORT ( CLK : IN STD_LOGIC ;Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) )END ;ARCHITECTURE bhv OF CNT ISSIGNAL Q1 : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS (CLK)BEGINIF CLK'EVENT AND CLK THENQ1 <= Q1 + 1 ;END PROCESS ;Q <= Q1 ;END bhv;四、设计,要求写出完整的vhdl代码。

(65分)1、16位硬件加法器,要求有进位输入和进位输出。

电子设计自动化(eda)期末考试试题及答案

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLKTHEN

Q1<=Q1+1;

ENDPROCESS;

Q<=Q1;

ENDbhv;

四、设计,要求写出完整的vhdl代码。(65分)

1、16位硬件加法器,要求有进位输入和进位输出。(15分)

2、七段数码管译码显示电路设计(数码管共阳极接法)(12分)

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYADDER16IS

PORT(CIN:INSTD_LOGIC;

A:INSTD_LOGIC_VECTOR(15DOWNTO0);

B:INSTD_LOGIC_VECTOR(15DOWNTO0);

Sห้องสมุดไป่ตู้OUTSTD_LOGIC_VECTOR(15DOWNTO0);

IFCLK'EVENTANDCLK='1'THEN

Q1<=Q1+1;

ENDIF;

ENDPROCESS;

Q<=Q1;

ENDbhv;

每个2分

四、设计,要求写出完整的vhdl代码。(65分)

1、16位硬件加法器,要求有进位输入和进位输出。(15分)

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

(9)在vhdl中变量可在结构体和进程中定义和使用。()

(10)在进程中同一信号有多个赋值源,实际完成赋值的是最接近begin的信号。()

二、简答题(15分)

1、简述fpga/cpld的设计流程。(5分)

2、在vhdl中端口模式有那几种?并说明数据流动方向。(4分)

EDA期末试卷及答案

EDA期末试卷及答案B.综合的输出是一个网表,包括逻辑门和它们之间的连接关系;C.综合的目的是将高层次的抽象设计转化为低层次的逻辑电路;D.综合只能在设计输入完成后进行,不能在设计实现和实际设计检验阶段进行。

一、填空题1.EDA技术的发展可分为MOS时代、CMOS时代和ASIC三个阶段。

2.EDA设计流程包括设计输入、设计实现、实际设计检验和下载编程四个步骤。

3.EDA设计输入主要包括图形输入、HDL文本输入和状态机输入。

4.时序仿真是在设计输入完成之后,选择具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为功能仿真。

5.VHDL的数据对象包括变量、常量和信号,它们是用来存放各种类型数据的。

6.设计结束后必须进行仿真,以检查设计文件的正确性。

7.EDA方式设计实现的电路设计文件最终可以编程下载到FPGA和CPLD芯片中,完成硬件设计和验证。

8.MAX+PLUS的文本文件类型是“.vhd”。

9.在PC上利用VHDL进行项目设计时,不允许在根目录下进行,必须在根目录为设计建立一个工程目录(即文件夹)。

10.VHDL源程序的文件名应与实体名相同,否则无法通过编译。

二、选择题:11.在EDA工具中,能完成在目标系统器件上布局布线软件称为“适配器”。

12.执行MAX+PLUSⅡ的“TimingAnalyzer”命令可以精确分析设计电路输入与输出波形间的延时量。

13.VHDL常用的库是“XXX”。

14.“PROCESS语句”既是并行语句又是串行语句。

15.在VHDL中,用语句“clock’EVENT AND clock=’0’”表示clock的下降沿。

16.IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为“胖IP”。

17.综合是EDA设计流程的关键步骤,在下面对综合的描述中,“综合只能在设计输入完成后进行,不能在设计实现和实际设计检验阶段进行”是错误的。

EDA期末考试卷及参考答案

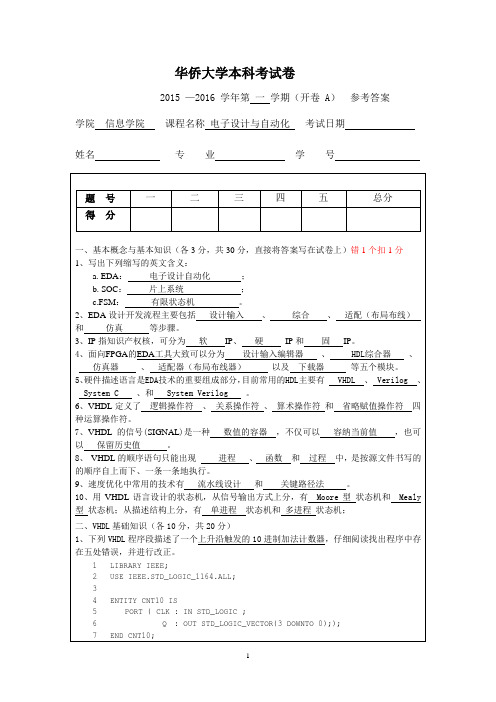

华侨大学本科考试卷2015 —2016 学年第一学期(开卷 A)参考答案学院信息学院课程名称电子设计与自动化考试日期姓名专业学号题号一二三四五总分得分一、基本概念与基本知识(各3分,共30分,直接将答案写在试卷上)错1个扣1分1、写出下列缩写的英文含义:a. EDA:电子设计自动化;b. SOC:片上系统;c.FSM:有限状态机。

2、EDA设计开发流程主要包括设计输入、综合、适配(布局布线)和仿真等步骤。

3、IP指知识产权核,可分为软IP、硬IP和固IP。

4、面向FPGA的EDA工具大致可以分为设计输入编辑器、 HDL综合器、仿真器、适配器(布局布线器)以及下载器等五个模块。

5、硬件描述语言是EDA技术的重要组成部分,目前常用的HDL主要有 VHDL 、 Verilog 、 System C 、和 System Verilog 。

6、VHDL定义了逻辑操作符、关系操作符、算术操作符和省略赋值操作符四种运算操作符。

7、VHDL的信号(SIGNAL)是一种数值的容器,不仅可以容纳当前值,也可以保留历史值。

8、VHDL的顺序语句只能出现进程、函数和过程中,是按源文件书写的的顺序自上而下、一条一条地执行。

9、速度优化中常用的技术有流水线设计和关键路径法。

10、用VHDL语言设计的状态机,从信号输出方式上分,有 Moore型状态机和 Mealy 型状态机;从描述结构上分,有单进程状态机和多进程状态机;二、VHDL基础知识(各10分,共20分)1、下列VHDL程序段描述了一个上升沿触发的10进制加法计数器,仔细阅读找出程序中存在五处错误,并进行改正。

1 LIBRARY IEEE;2 USE IEEE.STD_LOGIC_1164.ALL;34 ENTITY CNT10 IS5 PORT ( CLK : IN STD_LOGIC ;6 Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0););7 END CNT10;8 ARCHITECTURE bhv OF CNT10 IS9 VARIABLE Q1 : STD_LOGIC_VECTOR(3 DOWNTO 0);10 BEGIN11 PROCESS (CLK) BEGIN12 IF CLK’EVENT AND CLK=’0’ BEGIN13 IF Q1 < 9 THEN14 Q1 <= Q1 + 1 ;15 ELSE16 Q1 <= (OTHERS => '0');17 END IF;18 END IF;19 END PROCESS;20 Q <= Q1;21 END bhv;各2分答:程序订正修改如下第3行:增加“USE IEEE.STD_LOGIC_UNSIGED.ALL;”语句第6行:删除其中一个错误的“;”,改为“Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));”第9行:Q1应定义为信号量,其中“VARIABLE”改为“SIGNAL”第12行:因为是上升沿触发,其中“CLK=’0’”改为“CLK=’1’”第12行:行末尾“BEGIN”改为“THEN”2、阅读下列VHDL程序段,画出相应的原理图(RTL级),并简要说明电路功能。

电子设计自动化考试试题

电子设计自动化考试试题一、选择题(共 20 题,每题 3 分)1、以下哪种软件是常用的电子设计自动化(EDA)工具?()A AutoCADB PhotoshopC Altium DesignerD Microsoft Word2、在 EDA 中,用于原理图绘制的工具通常不包括()A 导线绘制工具B 元件库管理工具C 布线规则设置工具D 3D 模型生成工具3、电子设计中,以下哪种文件格式常用于保存 PCB 布局?()AdocBpdfCschDpcb4、 EDA 软件中的仿真功能主要用于()A 查看设计的外观效果B 预测电路的性能和功能C 计算元件的成本D 生成生产文件5、在PCB 布线中,以下哪种布线方式有利于减少信号干扰?()A 直角布线B 45 度角布线C 随意布线D 曲线布线6、对于复杂的数字电路设计,通常采用的设计方法是()A 自底向上B 自顶向下C 随机设计D 模仿已有设计7、 EDA 工具中的库文件包含了()A 元件符号和封装B 电路原理图C PCB 布局图D 仿真结果8、以下哪种 EDA 工具常用于集成电路设计?()A ProtelB CadenceC MultisimD Eagle9、在进行 PCB 设计时,电源层和地层的设置主要是为了()A 提高布线效率B 增强信号稳定性C 便于元件布局D 节省板材空间10、电子设计自动化中,DRC 检查的目的是()A 检查设计的美观性B 检查设计是否符合规则C 计算布线长度D 评估电路性能11、以下哪种元件在 EDA 库中通常需要自定义?()A 电阻B 电容C 集成电路芯片D 二极管12、对于高速数字电路设计,以下哪个因素最为关键?()A 元件布局B 布线长度C 电源稳定性D 信号完整性13、 EDA 软件中的布线策略通常不包括()A 最短路径布线B 最小电阻布线C 最小电容布线D 最大电流布线14、在原理图设计中,网络标号的作用是()A 标注元件参数B 表示信号连接C 区分不同元件D 增加原理图的可读性15、以下哪种 EDA 工具支持硬件描述语言(HDL)设计?()A ProteusB PADSC Quartus IID KiCAD16、进行 PCB 设计时,过孔的主要作用是()A 连接不同层的导线B 安装元件C 增强电路板强度D 标注电路板信息17、电子设计自动化中,以下哪种文件用于制造 PCB 板?()A 原理图文件B PCB 文件C 网络表文件D 仿真文件18、在 EDA 中,用于模拟电路仿真的工具通常是()A SPICEB ModelSimC ISED Vivado19、以下哪种情况可能导致 EDA 软件中的布线失败?()A 元件布局不合理B 布线规则设置过松C 电路板尺寸过大D 电源电压过高20、对于多层 PCB 板设计,内层通常用于()A 信号层B 电源层和地层C 元件层D 丝印层二、填空题(共 10 题,每题 2 分)1、 EDA 软件中,常用的原理图绘制快捷键有_____、_____等。

eda期末考试试卷

eda期末考试试卷一、选择题(每题2分,共20分)1. EDA技术中,以下哪个不是数字信号处理的步骤?A. 信号采集B. 信号分析C. 信号存储D. 信号合成2. 在EDA设计中,以下哪个不是FPGA的组成部分?A. 可编程逻辑单元B. 输入输出单元C. 存储单元D. 微处理器核心3. 以下哪个不是VHDL语言的基本数据类型?A. 整数B. 实数C. 布尔D. 字符串4. 在EDA设计中,以下哪个不是并行逻辑设计的特点?A. 并行处理B. 顺序执行C. 快速响应D. 高度集成5. 在数字电路设计中,以下哪个不是触发器的功能?A. 存储信息B. 信号放大C. 状态保持D. 逻辑运算6. 在EDA设计中,以下哪个不是仿真软件的主要功能?A. 电路设计B. 功能验证C. 性能分析D. 电路测试7. 在数字电路设计中,以下哪个不是逻辑门的基本类型?A. 与门B. 或门C. 非门D. 异或门8. 在EDA设计中,以下哪个不是硬件描述语言的主要特点?A. 行为描述B. 数据流描述C. 结构描述D. 软件描述9. 在数字电路设计中,以下哪个不是状态机的设计步骤?A. 状态定义B. 状态转换C. 输出定义D. 信号放大10. 在EDA设计中,以下哪个不是时序逻辑电路的特点?A. 依赖于时间B. 依赖于输入C. 有记忆功能D. 状态可变二、填空题(每空1分,共20分)1. EDA技术的核心是__________,它使得设计者可以在计算机上完成从电路设计到仿真的全过程。

2. 在数字电路设计中,__________是一种常用的电路优化技术,它可以减少电路的功耗和提高电路的运行速度。

3. VHDL语言中,__________关键字用于定义信号的初始值。

4. 在EDA设计中,__________是一种常用的电路测试技术,它可以检测电路的逻辑错误和时序错误。

5. 在数字电路设计中,__________是一种常用的电路设计方法,它通过将电路分解为多个子模块来简化设计过程。

eda期末考试试卷

eda期末考试试卷EDA期末考试试卷一、选择题(每题2分,共20分)1. EDA是指:A. 电子设计自动化B. 电子数据交换C. 电子文档分析D. 电子设备应用2. 在EDA工具中,用于绘制电路原理图的软件通常被称为:A. PCB DesignerB. Schematic CaptureC. Logic SimulatorD. Layout Editor3. 下列哪个不是数字逻辑门的基本类型:A. ANDB. ORC. NOTD. XOR4. 以下哪个是EDA工具中用于模拟电路行为的软件:A. VHDLB. VerilogC. RTL SimulatorD. PCB Router5. 在设计一个数字电路时,以下哪项不是设计流程的一部分:A. 需求分析B. 原理图绘制C. 电路板设计D. 手工焊接6. FPGA代表:A. 现场可编程门阵列B. 固定门阵列C. 通用门阵列D. 专用集成电路7. 在VHDL或Verilog中,以下哪个关键字用于定义一个过程:A. processB. moduleC. functionD. package8. 以下哪个是EDA工具中用于生成电路板布局的软件:A. Schematic CaptureB. Layout EditorC. PCB DesignerD. Logic Simulator9. 在数字电路设计中,同步设计和异步设计的主要区别在于:A. 使用的逻辑门类型B. 电路的复杂性C. 时钟信号的使用D. 电路的功耗10. 下列哪个不是常用的PCB设计软件:A. Altium DesignerB. EagleC. KiCadD. MATLAB二、简答题(每题10分,共30分)1. 简述EDA工具在电子设计过程中的作用和重要性。

2. 解释什么是信号完整性,并讨论它在高速电路设计中的重要性。

3. 描述一个典型的数字电路设计流程,并解释每个步骤的目的。

三、计算题(每题15分,共30分)1. 给定一个简单的数字逻辑电路,包含两个输入A和B,一个输出Y。

eda期末考试题及答案

eda期末考试题及答案EDA期末考试题及答案一、选择题(每题2分,共20分)1. EDA代表的是:A. 电子设计自动化B. 电子数据交换C. 电子文档管理D. 电子设备分析答案:A2. 在EDA中,HDL指的是:A. 高级硬件描述语言B. 硬件描述语言C. 硬件设计语言D. 硬件开发语言答案:B3. 下列哪个不是EDA工具的常见功能?A. 仿真B. 布局C. 布线D. 编程答案:D4. FPGA代表的是:A. 现场可编程门阵列B. 固定可编程门阵列C. 功能可编程门阵列D. 快速可编程门阵列答案:A5. VHDL是一种:A. 编程语言B. 硬件描述语言C. 数据库语言D. 操作系统答案:B6. 以下哪个是EDA软件的典型应用?A. 网页设计B. 游戏开发C. 电子电路设计D. 办公自动化答案:C7. 在EDA设计流程中,综合是指:A. 将设计从逻辑级别转换为门级别B. 将设计从门级别转换为晶体管级别C. 将设计从晶体管级别转换为物理布局D. 将设计从物理布局转换为最终产品答案:A8. 下列哪个是EDA设计中的错误?A. 功能错误B. 语法错误C. 布局错误D. 所有选项都是答案:D9. 以下哪个不是EDA设计中的测试类型?A. 功能测试B. 性能测试C. 压力测试D. 代码测试答案:D10. 在EDA中,后仿真分析是指:A. 在仿真之前进行的分析B. 在仿真之后进行的分析C. 在仿真过程中进行的分析D. 不进行任何分析答案:B二、简答题(每题10分,共30分)1. 请简述EDA在电子设计中的重要性。

答案:EDA(电子设计自动化)是现代电子设计不可或缺的工具,它允许设计师使用软件工具来设计和验证电子系统,从而提高设计效率,减少错误,加快产品上市时间,并且可以设计出更复杂、更高性能的电子系统。

2. 描述一下在EDA设计流程中,仿真的作用是什么?答案:在EDA设计流程中,仿真是一个关键步骤,它允许设计师在实际制造电路之前验证设计的功能和性能。

EDA期末考试试题

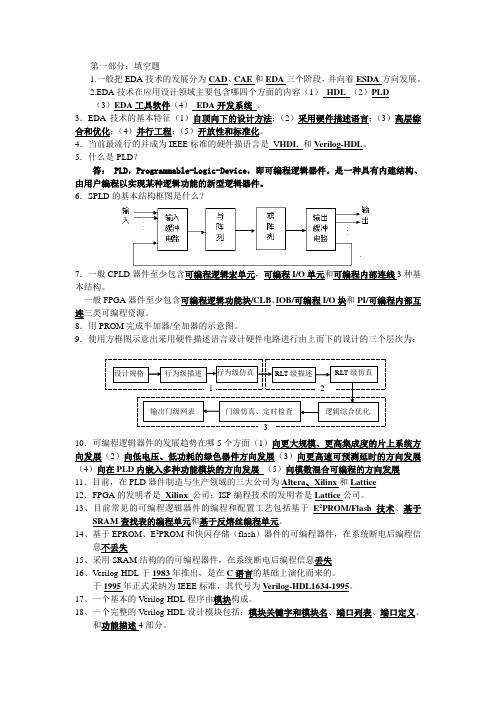

第一部分:填空题1.一般把EDA技术的发展分为CAD、CAE和EDA三个阶段,并向着ESDA方向发展。

2.EDA技术在应用设计领域主要包含哪四个方面的内容(1)HDL (2)PLD(3)EDA工具软件(4)EDA开发系统。

3.EDA技术的基本特征(1)自顶向下的设计方法;(2)采用硬件描述语言;(3)高层综合和优化;(4)并行工程;(5)开放性和标准化。

4.当前最流行的并成为IEEE标准的硬件描语言是V HDL和Verilog-HDL。

5.什么是PLD?答: PLD,Programmable-Logic-Device,即可编程逻辑器件。

是一种具有内建结构、由用户编程以实现某种逻辑功能的新型逻辑器件。

6.SPLD的基本结构框图是什么?7.一般CPLD器件至少包含可编程逻辑宏单元,可编程I/O单元和可编程内部连线3种基本结构。

一般FPGA器件至少包含可编程逻辑功能块/CLB、IOB/可编程I/O块和PI/可编程内部互连三类可编程资源。

8.用PROM完成半加器/全加器的示意图。

9.使用方框图示意出采用硬件描述语言设计硬件电路进行由上而下的设计的三个层次为:10.可编程逻辑器件的发展趋势在哪5个方面(1)向更大规模、更高集成度的片上系统方向发展(2)向低电压、低功耗的绿色器件方向发展(3)向更高速可预测延时的方向发展(4)向在PLD内嵌入多种功能模块的方向发展(5)向模数混合可编程的方向发展11.目前,在PLD器件制造与生产领域的三大公司为Altera、Xilinx和Lattice 12.FPGA的发明者是Xilinx公司;ISP编程技术的发明者是Lattice公司。

13、目前常见的可编程逻辑器件的编程和配置工艺包括基于E2PROM/Flash技术、基于SRAM查找表的编程单元和基于反熔丝编程单元。

14、基于EPROM、E2PROM和快闪存储(flash)器件的可编程器件,在系统断电后编程信息不丢失15、采用SRAM结构的的可编程器件,在系统断电后编程信息丢失16、V erilog-HDL于1983年推出,是在C语言的基础上演化而来的。

FPGA大学电子设计自动化(EDA)期末试题

FPGA大学电子设计自动化(EDA)期末试题标准答案与评分细则(卷面总分:80分)一.名词解释(2分×6题)(评分标准:给出正确英文的2分/题,仅给中文解释1分/题)1.EDA:Electronic Design Automation2. FPGA:Field Programmable Gate-Array3. ASIC:Application Specific Integrated Circuit4. SOC:System On a Chip5. DSP:Digital Signal Processor/Processing6.VHDL:VHSIC (Very High Speed Integrated Circuit) Hardware Description Language二.填空题(每空1分,共18分)(评分标准:填写正确1分/空)1. VHDL程序的5个组成部分分别为:实体(Entity)、构造体(Architecture)、配置(Configuration)、包集合(Package)、库(Library)。

2. VHDL中操作符“&”的具体名称是:并置运算符,它的基本功能是:用于位的连接,即低位宽组成高位宽数据。

3. VHDL描述行为的语句中有并行语句和顺序语句之分。

只能当顺序语句使用的描述语句有很多,试列举出其中三种:IF语句、CASE 语句、FOR循环语句(或:WHILE循环语句、无条件循环LOOP语句)。

4.Active-HDL软件工具编程设计录入方法最基本的三种:HDE (或:HDL编辑器、HDL Editor)、BDE(或:模块图编辑、Block Diagram Editor)、FSM(或:状态图编辑器、State Diagram Editor)。

5.VHDL的并行信号赋值语句,除了常见的一般信号赋值语句(如:C<=A and B;)外,还有两种形式,它们分别是:条件信号赋值语句(或:条件型)、选择信号赋值语句(或:选择型)。

无敌超强EDA期末压题

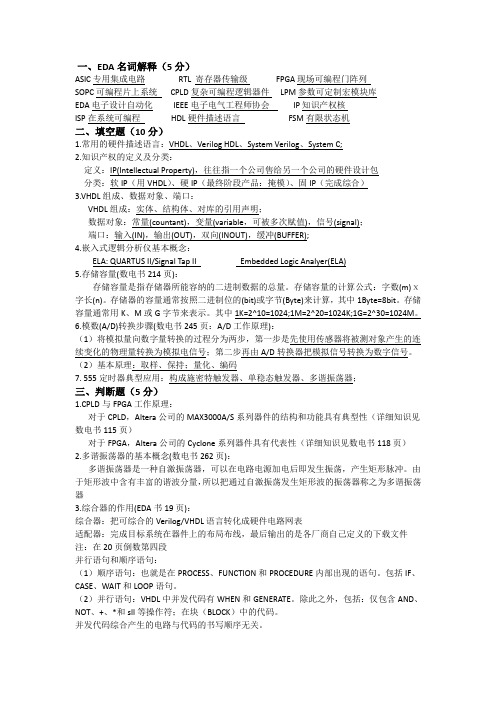

一、EDA名词解释(5分)ASIC 专用集成电路RTL 寄存器传输级FPGA 现场可编程门阵列SOPC可编程片上系统CPLD 复杂可编程逻辑器件LPM 参数可定制宏模块库EDA 电子设计自动化 IEEE电子电气工程师协会 IP 知识产权核ISP在系统可编程HDL硬件描述语言FSM有限状态机二、填空题(10分)1.常用的硬件描述语言:VHDL、Verilog HDL、System Verilog、System C;2.知识产权的定义及分类:定义:IP(Intellectual Property),往往指一个公司售给另一个公司的硬件设计包分类:软IP(用VHDL)、硬IP(最终阶段产品:掩模)、固IP(完成综合)3.VHDL组成、数据对象、端口:VHDL组成:实体、结构体、对库的引用声明;数据对象:常量(countant),变量(variable,可被多次赋值),信号(signal);端口:输入(IN),输出(OUT),双向(INOUT),缓冲(BUFFER);4.嵌入式逻辑分析仪基本概念:ELA: QUARTUS II/Signal Tap II Embedded Logic Analyer(ELA)5.存储容量(数电书214页):存储容量是指存储器所能容纳的二进制数据的总量。

存储容量的计算公式:字数(m)ⅹ字长(n)。

存储器的容量通常按照二进制位的(bit)或字节(Byte)来计算,其中1Byte=8bit。

存储容量通常用K、M或G字节来表示。

其中1K=2^10=1024;1M=2^20=1024K;1G=2^30=1024M。

6.模数(A/D)转换步骤(数电书245页:A/D工作原理):(1)将模拟量向数字量转换的过程分为两步,第一步是先使用传感器将被测对象产生的连续变化的物理量转换为模拟电信号;第二步再由A/D转换器把模拟信号转换为数字信号。

(2)基本原理:取样、保持;量化、编码7. 555定时器典型应用:构成施密特触发器、单稳态触发器、多谐振荡器;三、判断题(5分)1.CPLD与FPGA工作原理:对于CPLD,Altera公司的MAX3000A/S系列器件的结构和功能具有典型性(详细知识见数电书115页)对于FPGA,Altera公司的Cyclone系列器件具有代表性(详细知识见数电书118页)2.多谐振荡器的基本概念(数电书262页):多谐振荡器是一种自激振荡器,可以在电路电源加电后即发生振荡,产生矩形脉冲。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子设计自动化期末必考题目汇总

1、EDA的英文拼写:electronic design automation

2、Eda的设计方法:两种一种为由底向上的设计方法即传统的设计方法,一种是自顶向下的设计方法即现代设计方法。

3、自顶向下分为三个阶段:系统设计、系统的综合优化、系统的实现

4、系统的设计流程主要包括:系统的功能分析、系统的结构设计、系统的描述、系统的功能仿真。

5、适配器:结构综合器,功能是将由综合器产生的网表文件配置与指定的目标器件中,使之产生最终的下载文件中。

6、FPGA芯片对应的是:sof文件,CPLD芯片对应的是pof文件

7、FPLD:现场可编程逻辑器件,FPGA:现场可编程门阵列,CPLD:复杂现场可编程逻辑阵列

8、可编程逻辑器件分为:FPGA和CPLD其中CPLD断电后不丢失。

9、基于乘积项的PLD分为三部分:宏单元、PIA、I/O控制板10、quartus软件的波形文件名为.vwf

11、VHDL语言的特点:

(1)、VHDL是工业标准的文本格式语言。

(2)、具有强大的描述能力。

(3)、VNDL能同时支持方针和综合。

(4)、VHDL语言是并发执行的语句

(5)、VHDL支持结构化设计和top-down设计方法(6)、VHDL的描述与工艺无关

12、STD-logic型数据能够在数字器件中实现的只有四种即“-”、“0”、“1”、“z”但这并不表明其他5种值不存在,这9种值对于VHDL的行为仿真都有重要意义。

13、用户自定义的数据类型:枚举类型、整数类型、数组类型(所有的值必须一样)、记录类型(值得类型可以不一样)、事件类型、实数类型。

14、数据类型转换分为两种:类型转换函数方式、直接类型转15、换方式常量说明语句所允许的设计单元有:实体,结构体、程序包、块、进程、子程序

16信号与变量的区别:

(1)、赋值语句的不同,信号赋值用“《=”而变量为“:=”

(2)、通常变量的值可以给信号赋值但信号的值却不能给变量赋值

(3)、信号时全局量而变量是局部量

(4)、信号可以作为进程的敏感信号,而变量不可以作为进程的敏感信号

(5)、操作过程不同

17、运算操作符分为:逻辑操作符、关系操作符、算术操作符、和并置操作符

18、逻辑操作符左右两边的数据类型必须相同。

19、VNDL语言基本结构:

库的调用

程序包的调用

实体说明

结构体

配置

20、说明语句:用于对结构内部使用的信号、常量、数据类型、函数等进行定义。

21、设计进程需要注意几个方面:

(1)、在进程中只能设置顺序语句

(2)、进程的激活必须由敏感信号表中定义的任一敏感信号的变化来启动

(3)、信号是多个进程间的通信线

(4)、进程是重要的建模工具

22、过程和函数的区别:函数的返回值只是函数的本身,一次只能返回一个值。

过程返回值在过程参数表中,一次可以返回多个值。

23、重载函数:VHDL语言允许以相同的函数名定义的函数。

重载过程:两个或两个以上有相同过程名而参数数量及数据类型却不完全相同的过程称为重载过程。

24、VHDL程序设计常用的库:IEEE库,SID库,WORK库。

25、VHDL语言有三种描述方式:行为描述方式、数据流描述方式、结构描述方式。

为了能够兼顾整个设计的功能、资源。

性能几个方面因素通常混合使用这三种描述方式。

26、时序逻辑电路控制信号还包括两个重要的信号:同步控制信号

(上面)和异步控制信号(下面)。

27、。