版图设计实验

本科生课-集成电路版图设计-实验报告

西安邮电大学集成电路版图设计实验报告学号:XXX姓名:XX班级:微电子XX日期:20XX目录实验一、反相器电路的版图验证1)反相器电路2)反相器电路前仿真3)反相器电路版图说明4)反相器电路版图DRC验证5)反相器电路版图LVS验证6)反相器电路版图提取寄生参数7)反相器电路版图后仿真8)小结实验二、电阻负载共源放大器版图验证9)电阻负载共源放大器电路10)电阻负载共源放大器电路前仿真11)电阻负载共源放大器电路版图说明12)电阻负载共源放大器电路版图DRC验证13)电阻负载共源放大器电路版图LVS验证14)电阻负载共源放大器电路版图提取寄生参数15)电阻负载共源放大器电路版图后仿真16)小结实验一、反相器电路的版图验证1、反相器电路反相器电路由一个PMOS、NPOS管,输入输出端、地、电源端和SUB 端构成,其中VDD接PMOS管源端和衬底,地接NMOS管的漏端,输入端接两MOS管栅极,输出端接两MOS管漏端,SUB端单独引出,搭建好的反相器电路如图1所示。

图1 反相器原理图2、反相器电路前仿真通过工具栏的Design-Create Cellview-From Cellview将反相器电路转化为symbol,和schemetic保存在相同的cell中。

然后重新创建一个cell,插入之前创建好的反相器symbol,插入电感、电容、信号源、地等搭建一个前仿真电路,此处最好在输入输出网络上打上text,以便显示波形时方便观察,如图2所示。

图2 前仿真电路图反相器的输入端设置为方波信号,设置合适的高低电平、脉冲周期、上升时间、下降时间,将频率设置为参数变量F,选择瞬态分析,设置变量值为100KHZ,仿真时间为20u,然后进行仿真,如果仿真结果很密集而不清晰可以右键框选图形放大,如图3所示。

图3 前仿真结果3、反相器电路版图说明打开之前搭建好的反相器电路,通过Tools-Design Synthesis-Laout XL新建一个同cell目录下的Laout文件,在原理图上选中两个MOS管后在Laout中选择Create-Pick From Schematic从原理图中调入两个器件的版图模型。

LDMOS版图设计实验_第三次实验报告

半导体功率器件与智能功率IC实验学生姓名:田瑞学号:201422030143指导教师:乔明一、实验室名称:211楼803 工作站二、实验项目名称:半导体功率器件与智能功率IC实验——LDMOS器件版图设计实验三、实验原理:首先,设计版图的基础便是电路的基本原理,以及电路的工作特性,硅加工工艺的基础、以及通用版图的设计流程,之后要根据不同的工艺对应不同的设计规则,一般来说通用的版图设计流程为:1.制定版图规划记住要制定可能会被遗忘的特殊要求清单2.设计实现考虑特殊要求及如何布线创建组元并对其进行布3.版图验证执行基于计算机的检查和目视检查,进行校正工作最终步骤工程核查以及版图核查版图参数提取与后仿真完成这些之后需要特别注意的是寄生参数噪声以及布局等的影响,具体是电路而定,在下面的实验步骤中会体现到这一点。

IC设计与制造的主要流程四、实验目的:掌握版图设计的基本理论。

掌握版图设计的常用技巧。

掌握定制集成电路的设计方法和流程。

熟悉Cadence Virtuoso Layout Edit软件的应用学会用Cadence软件设计版图、版图的验证以及后仿真熟悉Cadence软件和版图设计流程,减少版图设计过程中出现的错误。

五、实验内容:结合LDMOS的版图文件,完成LDMOS器件的版图绘制。

六、实验器材(设备、元器件):CADENCE软件七、实验步骤:LDMOS的版图文件nwell 16400 8000pwell1 10 7000pwell2 70 34003550 40504220 45204740 49905250 54705770 59206350 8000poly 20400 18005000 7400nimplant 20400 74007700 8000pimplant 10 7700omicont 20300 07000900 7600metal 20 20004800 8000nitride 20 06006300 8000八、实验数据及结果分析:整体版图版图下部分别为:源端pad,漏端pad以及栅极pad九、实验结论:通过实验,了解LDMOS器件的版图设计,熟悉CADENCE软件的使用。

版图设计实验

电子科技大学成都学院实验报告册课程名称:集成电路版图设计姓名:学号:院系:专业:教师:年月日实验一:LDO的版图设计一、实验目的:1、掌握并熟练使用Cadence软件。

2、学会将版图划分模块并掌握每个模块的功能。

3、掌握版图设计过程中的匹配原则与注意事项。

4、掌握常见dummy器件及其应遵守的规则。

5、掌握布局布线的规则。

6、掌握并熟练运用DRC和LVS验证方法及解决错误的方法。

二、实验原理和内容:版图设计本质是将搭建好的电路图更深层的展现,在版图设计里,将是用原理图更直观的展现电路图中的各个元器件的连接,匹配、以及布局等。

将版图分成小模块来分别实现会让版图的布局更清晰,让其他人更能直观的了解版图的各个模块的关联,能够减少相应的工作量。

利用Cadence软件的功能搭建电路图,进行DRC检查能够检查并指出我们的版图中存在的连线间隔和连接是否正确;LVS能检查出设计规格错误和版图与原理图是否一致的错误,能够保证我们设计的版图能够真正的实现我们所需要的电路图的功能。

三、实验步骤:1、打开temilen,进入CSMC所在文件夹路径,输入virtuoso &,回车,打开cadence软件(如图1-1所示)。

(图1-1)打开cadence软件2、进入Cadence软件创建库文件:。

点击File菜单,出现下拉菜单,选命令File->New->Library...(如图1-2所示)。

(图1-2)创建库3、在新建的库中添加Cell文件(如图1-3所示)。

(图1-3)添加Cell4、进入新建的Cell文件中,添加元器件并修改器件参数,调入Cell中(如图1-4所示)。

(图1-4)添加元器件5、针对电路图先进行模块化,先画电流镜。

(1).由图1-5-1(a)的电路图知道,这是规格为W=10U,L=8U,M=(1,1)的PMOS 电流镜并且他们的S极与背栅相连,1个PMOS的G极与D极连接画出其版图如图1-5-1(b)所示,由于是PMOS所以最后应在GT层画阱。

数字电路版图设计

3.1 图层板 图层板工具条如图4所示

L-Edit产生的工艺图层的数目是没有限制的。这些图层显示在图 层板中。每一个图层都由一个小方块的图标来代表。各个图标以颜 色和花纹来相互区分。当把鼠标箭头放在某个图标上时,在状态栏 上显示该图层的名称(同时也会在鼠标箭头附近弹出图层名称)。 图层有选中与非选中之分。在任何时间只能选中一个图层,被 选中的图层称为当前图层。当前图层的名称显示在图层板上方的图 层显示框内,选中的图层的图标被小黑框标识。当用绘图工具绘图 时,只能在当前图层上绘制图形。绘制的图形的颜色和花纹与该图 层的图标相同。

数字电路版图设计( 实验五 数字电路版图设计(LEDIT) )

集成电路设计通常需要经历三个阶段:系统设计、 电路设计和版图设计。版图设计是IC设计的重要一环, 这也是IC设计的最后一个环节。版图编辑一般只能在 大型计算机和工作站上进行,因而硬件造价高,操作 复杂,维护困难。当然对于规模不是很大的电路,也 有一些微机版的版图编辑软件可以采用。在微机上使 用最为普通的是Tanner Tools中的L-Edit。其设计结 果的输出格式通常为标准的CIF格式,版图可以人工 布局布线,也可以根据电路设计完成后生成的EDIF 格式网表和利用标准单元库自动完成布局布线。 本实验就是利用版图编辑软件L-Edit来完成集成电路 的版图设计与编辑,使学生能够掌握集成电路版图设 计与编辑的基本知识与技能。

图3 L-Edit的用户界面

L-Edit的用户界面有以下元素: 1. 菜单栏(在标题栏下面); 2. 标准工具条(Standard toolbar); 3. 编辑工具条(Editing toolbar); 4. 绘图工具条(Drawing toolbar); 5. 验证工具条(Verification toolbar); 6. 布图布线工具条(Place and route toolbar); 7. 图层板(Layer palette); 8. 状态栏(Status Bar); 9. 鼠标键条(Mouse button bar); 10. 定位器(Locator); 11. 版图区(Layout area); 12. 命令行界面(Command line interface)。

集成电路版图设计实验心得

集成电路版图设计实验心得实验心得,总结:集成电路版图设计是由基本门电路搭建组合而成的大型复杂电路,如果对其中的关键参数不了解就无法进行相应的设计,更别说自己能够将它做好。

因此,我们有必要掌握集成电路设计的相关知识与技术,熟悉相关工具软件,学会使用电子技术手段和方法来完成芯片功能设计、版图绘制以及相关的技术文档编写等。

下面介绍下此次课程实验的主要内容:一、简单的 CMOS 逻辑模块设计1. CMOS 器件及工作原理二极管:当没有加上反向偏压时,为导通状态,正向导通;在加上反向偏压后,反向阻断,变为截止状态,且耗尽所有能量;当两端都接上负载时,电流经过负载电阻降为0,同时功耗降到最小。

二极管有如下特性:(1)结电容,很小(约10^-9法拉,正常情况下为0.7左右)。

(2)特性曲线是一条垂直于管子轴线的一条曲线。

在静态工作点附近,当二极管加上反向电压后,它可以看成一个一端开路另外一端短路的普通二极管;在整个工作区内它几乎处于完全饱和状态,其电流随着电压增大而迅速增大;实验心得,总结:集成电路版图设计是由基本门电路搭建组合而成的大型复杂电路,如果对其中的关键参数不了解就无法进行相应的设计,更别说自己能够将它做好。

因此,我们有必要掌握集成电路设计的相关知识与技术,熟悉相关工具软件,学会使用电子技术手段和方法来完成芯片功能设计、版图绘制以及相关的技术文档编写等。

下面介绍下此次课程实验的主要内容:一、简单的 CMOS 逻辑模块设计1. CMOS 器件及工作原理二极管:当没有加上反向偏压时,为导通状态,正向导通;在加上反向偏压后,反向阻断,变为截止状态,且耗尽所有能量;当两端都接上负载时,电流经过负载电阻降为0,同时功耗降到最小。

二极管有如下特性:(1)结电容,很小(约10^-9法拉,正常情况下为0.7左右)。

(2)特性曲线是一条垂直于管子轴线的一条曲线。

在静态工作点附近,当二极管加上反向电压后,它可以看成一个一端开路另外一端短路的普通二极管;在整个工作区内它几乎处于完全饱和状态,其电流随着电压增大而迅速增大;当电压减小到某一值后,电流突然减少,并且这个电流的值为管子特性曲线的斜率,但仍保持原来的电流值不变,在管子轴线上电流不再是一条直线,管子的阻抗发生了翻转,导致其电流迅速下降。

实验三 中国地图制图(点线面符号设计)

实验三中国地图制图(点线面符号设计)一实验介绍实验目的:制作一幅中国的普通地图。

寻找网上的成熟的中国地图版图等进行模仿,根据实验二搜集到的矢量数据进行数据准备;再根据地图学符号理论,结合具体的中国地图编制,选择投影系统、编制底图要素、专题数据要素、注记要素。

进行符号设计、图例设计等。

软件准备:ARCGIS10.2(ARCMAP)ARCVIEW3.3实验数据:世界、中国矢量数据二上机操作(一)专业软件准备1、ARCGIS安装及破解(二)矢量数据下载参看实验二所搜集的世界及中国矢量数据集(三)中国地图制图1、网上百度搜集中国地图的资料,观察中国地图的特点。

本实验以国家测绘局公开出版中国传统地图为例进行说明。

经过详细的观察,结合所学地图学知识可以得出以下方面:1)版图设计该图采用了传统的横版,南海诸岛部分采用了变比例尺,多版设计。

图例和分版分别位于左右下方两边,支持了整个中国图形,保持了视觉的平衡性。

图名位于左上角图框外,便于系列中国地图的后续设计,具有明显地图集的特征。

2)投影设计该图的经线呈现向北极汇聚,纬线向赤道凸出,为典型的圆锥投影方式。

经线110度为直线,可以判断出来是中央经线。

第一纬线第二纬线的位置需要查参数确定之。

大致判断兰伯特投影可以初步满足需要。

该图标注了经纬度格网,用色为浅灰,与地图白色底色对比较好,既有区分度,又有协调性,不显突兀。

对南北回归线进行了标注。

3)图框设计采用了简单的双图框设计,边框内填充经纬度信息,有类似舞台式效果。

4)底图设计使用了世界地图及海陆分布为底图,对中国周边国家和地区进行了描述。

陆地为白色,海洋为浅蓝;整图色系淡雅,简略,以白色系为主,略冷淡。

5)数据图层及符号分析该地图需要1世界地图国家面、世界国家首都点、世界河流、湖泊线,面2中国国界线、南海断线省界线、省会点、河流线,湖泊面3北京点重点表示红五角星表示4注记海洋注记外国国名首都标注(中文)中国省名省会名。

D锁存器版图设计实验报告(DOC)

第一章:绪论1.1 简介1.1.1 集成电路集成电路版图设计是电路系统设计与集成电路工艺之间的中间环节。

通过集成电路版图设计,将立体的电路系统转变为二维平面图形。

利用版图制作掩模板,就可以由这些图形限定工艺加工过程,最终还原为基于半导体材料的立体结构。

以最基本的MOS器件为例,工艺生产出的器件应该包含源漏扩散区、栅极以及金属线等结构层。

按照电路设计的要求,在版图中用不同图层分别表示这些结构层,画好各个图层所需的图形,图形的大小等于工艺生产得到的器件尺寸。

正确摆放各图层图形之间的位置关系,绘制完成的版图基本就是工艺生产出的器件俯视图。

器件参数如MOS管的沟道尺寸,由电路设计决定,等于有源区与栅极重叠部分的尺寸。

其他尺寸由生产工艺条件决定,不能随意设定。

在工艺生产中,相同结构层相连即可导电,而不同结构层之间是由氧化层隔绝的,相互没有连接关系,只有制作通孔才能在不同结构层之间导电。

与工艺生产相对应的版图中默认不同图层之间的绝缘关系,因此可以不必画氧化层,却必须画各层之间的通孔。

另外,衬底在版图设计过程中默认存在,不必画出。

而各个N阱、P阱均由工艺生产过程中杂质掺杂形成,版图中必须画出相应图形。

1.1.2 版图设计基本知识版图设计是创建工程制图(网表)的精确的物理描述的过程,而这一物理描述遵守由制造工艺、设计流程以及仿真显示为可行的性能要求所带来的一系列约束。

版图设计得好坏,其功能正确与否,必须通过验证工具才能确定。

版图的验证通常包括三大部分:设计规则检查(DRC)、电学规则检查(ERC)和版图与电路图对照(LVS)。

只有通过版图验证的芯片设计才进行制版和工艺流片。

设计规则的验证是版图与具体工艺的接口, 因此就显得尤为重要, Cadence 中进行版图验证的工具主要有dracula和diva。

Dracula 为独立的验证工具, 不仅可以进行设计规则验证(DRC) , 而且可以完成电学规则验证(ERC)、版图与电路验证(LV S)、寄生参数提取(L PE) 等一系列验证工作, 功能强于Diva。

集成电路版图设计 画反相器 实验报告

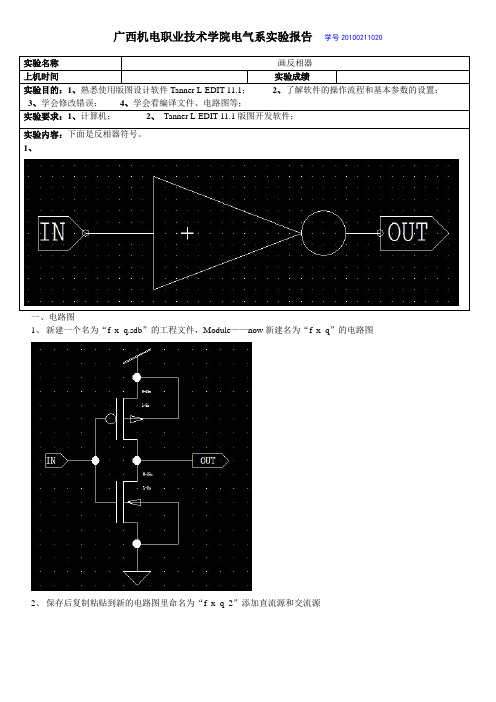

广西机电职业技术学院电气系实验报告学号20100211020实验名称画反相器上机时间实验成绩实验目的:1、熟悉使用版图设计软件Tanner L-EDIT 11.1;2、了解软件的操作流程和基本参数的设置;3、学会修改错误;4、学会看编译文件、电路图等;实验要求:1、计算机;2、Tanner L-EDIT 11.1版图开发软件;实验内容:下面是反相器符号。

1、一、电路图1、新建一个名为“f_x_q.sdb”的工程文件,Module——now新建名为“f_x_q”的电路图2、保存后复制粘贴到新的电路图里命名为“f_x_q_2”添加直流源和交流源3、保存后设置瞬时仿真最大值为1ns 仿真长度为400ns4、输出信号输入端(IN)和信号输出端(out)的瞬时波形得下图5、开始仿真6、相同方法输入信号换成直流信号,命名为“f_x_q_3”二、版图1、打开L-Edit软件新建名为F_X_Q.tdb的文件再里头新建元件有PB(basecontactn)、NB(basecontactn)、PMOS、NMOS、IN(输入端)、OUT(输出端)、PB(basecontactn)NB(basecontactn)PMOSNMOSIN(输入端)OUT(输出端)2、以上元件都要进行DRC错误检查,因为out端少了金属一层,所以提示会出错。

3、新建元件F_X_Q导入以上所有元件并画地和电源并连线,加入节点名称,如下图4、检查没有错误后创建仿真文件。

得按要求添加周期为100ns高电平保持时间为50ns高低跳变时间为5ns幅度电位为0~5v的交流源Va 总电源5v的直流源vvdd加入仿真长度和时间1ns 400ns三、进行电路图和版图的一致性对比结果:。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子科技大学成都学院(微电子技术系)实验报告书课程名称:版图设计实验学号:1140720524姓名:王灿教师:赖广升2013 年12 月25 日实验一快速电压比较器的电路图设计一、实验目的1)学会使用cadence中的virtuoso软件;2)学会如何用virtuoso画出设计的电路图;3)学会如何改正画电路图中出现的错误。

二、实验仪器设备计算机,Cadence软件三、实验原理和内容在cadence软件中画出电路图可用于检验画出的版图是否满足所需的设计需求。

四、实验步骤1)打开virtuoso,如图1-1到1-4图1-1图1-2图1-3图1-4 2)建立一个电路图工程,如图2-1图2-13)选择工程类型,如图3-1图3-14)按I,调用需要的器件并设置器件参数,如图4-1图4-15)按P,调用需要的端口并命名,如图5-1图5-1 6)按W,依据图纸连接电路,如图6-1图6-1 7)保存电路图并检查五、实验数据************************************************************************ * auCdl Netlist:** Library Name: 222* Top Cell Name: 1140720524* View Name: schematic* Netlisted on: Dec 30 14:43:58 2013*************************************************************************.EQUATION*.SCALE METER*.MEGA.PARAM*.GLOBAL vss!+ vcc!*.PIN vss!*+ vcc!************************************************************************ * Library Name: 222* Cell Name: 1140720524* View Name: schematic************************************************************************.SUBCKT 1140720524 V-_SENSE VBG_H VBIAS1 VD4_EN VD4_OUT*.PININFO V-_SENSE:I VBG_H:I VBIAS1:I VD4_EN:I VD4_OUT:OMNM3 net17 net11 net16 vss! NN W=4u L=2u m=2MNM1 VD4_OUT net17 net16 vss! NN W=4u L=4u m=1MNM0 net11 net11 net16 vss! NN W=4u L=2u m=2MNM2 net16 VD4_EN vss! vss! NN W=5u L=600n m=1MPM6 net16 V-_SENSE net20 net20 NP W=12u L=1u m=3MPM5 net17 net20 net13 net13 NP W=6u L=2u m=2MPM4 net11 VBG_H net13 net13 NP W=6u L=2u m=2MPM3 VD4_OUT VD4_EN vcc! vcc! NP W=3u L=600n m=1MPM2 VD4_OUT VBIAS1 vcc! vcc! NP W=4u L=4u m=1MPM7 net20 VBIAS1 vcc! vcc! NP W=2u L=5u m=4MPM0 net13 VBIAS1 vcc! vcc! NP W=2u L=4u m=1.ENDS六、结果及分析电路图并无连接错误。

1)明白的cadence的virtuoso的基本操作;2)学会了如何在virtuoso中画出电路图;3)知道了在画图过程中易出现的错误,并学会了改正这些错误。

实验二短路保护的版图设计一、实验目的1)学会使用cadence中的virtuoso软件;2)学会如何用virtuoso画出设计的版图;3)学会改正画版图中出现的错误。

二、实验仪器设备Cadence软件三、实验原理和内容在cadence软件中画出可以用于给予工厂成片的版图。

四、实验步骤1)打开virtuoso建立一个版图的工程,如图1-1到1-2图1-12)画出对应电路图的版图模块,如图2-1到2-3模块1:偏置MOS管图2-1-1图2-1-2 模块2:差分对图2-2-1图2-2-2 模块3:电流镜图2-3-1图2-3-2 4)测试版图的RDC,如图3-1到3-3图3-1图3-2图3-3 5)检查版图的LVS,如图4-1到4-2图4-1图4-2图4-3图4-4五、实验数据* SPICE NETLIST***************************************.SUBCKT mn_6** N=4 EP=0 IP=0 FDC=0*.SEEDPROM.ENDS*************************************** .SUBCKT mp_3** N=5 EP=0 IP=0 FDC=0*.SEEDPROM.ENDS*************************************** .SUBCKT mp_7** N=5 EP=0 IP=0 FDC=0*.SEEDPROM.ENDS*************************************** .SUBCKT mp_1** N=5 EP=0 IP=0 FDC=0*.SEEDPROM.ENDS***************************************.SUBCKT mp_0** N=5 EP=0 IP=0 FDC=0*.SEEDPROM.ENDS***************************************.SUBCKT 1140720524 VD4_EN VD4_OUT VBG_H VSS! VBIAS1 VCC! V-_SENSE** N=12 EP=7 IP=91 FDC=24M0 VD4_OUT VD4_EN VCC! VCC! NP L=6e-07 W=3e-06 AD=3.6e-12 AS=3.6e-12 PD=8.4e-06 PS=8.4e-06 $X=4760 $Y=-2885 $D=3M1 VD4_OUT VBIAS1 VCC! VCC! NP L=4e-06 W=4e-06 AD=4.8e-12 AS=4.8e-12 PD=1.04e-05 PS=1.04e-05 $X=20520 $Y=-3275 $D=3M2 VCC! VBIAS1 8 VCC! NP L=4e-06 W=2e-06 AD=2.4e-12 AS=2.4e-12 PD=6.4e-06 PS=6.4e-06 $X=48385 $Y=14295 $D=3M3 VCC! VBIAS1 6 VCC! NP L=5e-06 W=2e-06 AD=1.3e-12 AS=2.4e-12 PD=3.3e-06 PS=6.4e-06 $X=37115 $Y=-3175 $D=3M4 6 VBIAS1 VCC! VCC! NP L=5e-06 W=2e-06 AD=1.3e-12 AS=1.3e-12 PD=3.3e-06 PS=3.3e-06 $X=43415 $Y=-3175 $D=3M5 VCC! VBIAS1 6 VCC! NP L=5e-06 W=2e-06 AD=1.3e-12 AS=1.3e-12 PD=3.3e-06 PS=3.3e-06 $X=49715 $Y=-3175 $D=3M6 6 VBIAS1 VCC! VCC! NP L=5e-06 W=2e-06 AD=2.4e-12 AS=1.3e-12 PD=6.4e-06 PS=3.3e-06 $X=56015 $Y=-3175 $D=3M7 6 V-_SENSE 9 6 NP L=1e-06 W=1.2e-05 AD=7.8e-12 AS=1.44e-11 PD=1.33e-05 PS=2.64e-05 $X=48225 $Y=30340 $D=3M8 9 V-_SENSE 6 6 NP L=1e-06 W=1.2e-05 AD=7.8e-12 AS=7.8e-12 PD=1.33e-05 PS=1.33e-05 $X=48225 $Y=32640 $D=3M9 6 V-_SENSE 9 6 NP L=1e-06 W=1.2e-05 AD=1.44e-11 AS=7.8e-12 PD=2.64e-05 PS=1.33e-05 $X=48225 $Y=34940 $D=3M10 3 3 3 8 NP L=2e-06 W=6e-06 AD=0 AS=5e-12 PD=0 PS=9.66667e-06 $X=15395 $Y=14870 $D=3M11 8 6 3 8 NP L=2e-06 W=6e-06 AD=3.9e-12 AS=3.9e-12 PD=7.3e-06 PS=7.3e-06 $X=18695 $Y=14870 $D=3M12 4 VBG_H 8 8 NP L=2e-06 W=6e-06 AD=3.9e-12 AS=3.9e-12 PD=7.3e-06 PS=7.3e-06 $X=21995 $Y=14870 $D=3M13 4 4 4 8 NP L=2e-06 W=6e-06 AD=0 AS=5e-12 PD=0 PS=9.66667e-06 $X=25295 $Y=14870 $D=3M14 4 4 4 8 NP L=2e-06 W=6e-06 AD=0 AS=5e-12 PD=0 PS=9.66667e-06 $X=9345 $Y=28600 $D=3M15 8 VBG_H 4 8 NP L=2e-06 W=6e-06 AD=3.9e-12 AS=3.9e-12 PD=7.3e-06 PS=7.3e-06 $X=12645 $Y=28600 $D=3M16 3 6 8 8 NP L=2e-06 W=6e-06 AD=3.9e-12 AS=3.9e-12 PD=7.3e-06 PS=7.3e-06 $X=15945 $Y=28600 $D=3M17 3 3 3 8 NP L=2e-06 W=6e-06 AD=0 AS=5e-12 PD=0 PS=9.66667e-06 $X=19245$Y=28600 $D=3M18 9 3 VD4_OUT VSS! NN L=4e-06 W=4e-06 AD=4.2e-12 AS=4.2e-12 PD=1.01e-05 PS=1.01e-05 $X=8390 $Y=46060 $D=0M19 VSS! VD4_EN 9 VSS! NN L=6e-07 W=5e-06 AD=5.25e-12 AS=5.25e-12 PD=1.21e-05 PS=1.21e-05 $X=24175 $Y=45855 $D=0M20 9 4 4 VSS! NN L=2e-06 W=4e-06 AD=2.6e-12 AS=4.2e-12 PD=5.3e-06 PS=1.01e-05 $X=48240 $Y=45405 $D=0M21 3 4 9 VSS! NN L=2e-06 W=4e-06 AD=2.6e-12 AS=2.6e-12 PD=5.3e-06 PS=5.3e-06 $X=51540 $Y=45405 $D=0M22 9 4 3 VSS! NN L=2e-06 W=4e-06 AD=2.6e-12 AS=2.6e-12 PD=5.3e-06 PS=5.3e-06 $X=54840 $Y=45405 $D=0M23 4 4 9 VSS! NN L=2e-06 W=4e-06 AD=4.2e-12 AS=2.6e-12 PD=1.01e-05 PS=5.3e-06 $X=58140 $Y=45405 $D=0.ENDS*************************************************************************************************************** * auCdl Netlist:** Library Name: 222* Top Cell Name: 1140720524* View Name: schematic* Netlisted on: Dec 30 14:43:58 2013*************************************************************************.EQUATION*.SCALE METER*.MEGA.PARAM*.GLOBAL vss!+ vcc!*.PIN vss!*+ vcc!************************************************************************ * Library Name: 222* Cell Name: 1140720524* View Name: schematic************************************************************************.SUBCKT 1140720524 V-_SENSE VBG_H VBIAS1 VD4_EN VD4_OUT*.PININFO V-_SENSE:I VBG_H:I VBIAS1:I VD4_EN:I VD4_OUT:OMNM3 net17 net11 net16 vss! NN W=4u L=2u m=2MNM1 VD4_OUT net17 net16 vss! NN W=4u L=4u m=1MNM0 net11 net11 net16 vss! NN W=4u L=2u m=2MNM2 net16 VD4_EN vss! vss! NN W=5u L=600n m=1MPM6 net16 V-_SENSE net20 net20 NP W=12u L=1u m=3MPM5 net17 net20 net13 net13 NP W=6u L=2u m=2MPM4 net11 VBG_H net13 net13 NP W=6u L=2u m=2MPM3 VD4_OUT VD4_EN vcc! vcc! NP W=3u L=600n m=1MPM2 VD4_OUT VBIAS1 vcc! vcc! NP W=4u L=4u m=1MPM7 net20 VBIAS1 vcc! vcc! NP W=2u L=5u m=4MPM0 net13 VBIAS1 vcc! vcc! NP W=2u L=4u m=1.ENDS六、结果及分析LVS与RDC跑出的结果无错误,说明版图没有连接错误而且版图结构与电路图走线相匹配。