实验七设计基本触发器

数字电路实验指导书

实验一集成逻辑门电路逻辑功能的测试一、实验目的1.熟悉数字逻辑实验箱的结构、基本功能和使用方法。

2.掌握常用非门、与非门、或非门、与或非门、异或门的逻辑功能及其测试方法。

二、实验器材1.数字逻辑实验箱DSB-3 1台2. 万用表 1只3.元器件: 74LS00(T065) 74LS04 74LS55 74LS86 各一块导线若干三、实验说明1.数字逻辑实验箱提供5 V + 0.2 V的直流电源供用户使用。

2.连接导线时,为了便于区别,最好用不同颜色导线区分电源和地线,一般用红色导线接电源,用黑色导线接地。

3.实验箱操作板部分K0~K7提供8位逻辑电平开关,由8个钮子开关组成,开关往上拨时,对应的输出插孔输出高电平“1”,开关往下拨时,输出低电平“0”。

4.实验箱操作板部分L0~L7提供8位逻辑电平LED显示器,可用于测试门电路逻辑电平的高低,LED亮表示“1”,灭表示“0”。

四、实验内容和步骤1.测试74LS04六非门的逻辑功能将74LS04正确接入面包板,注意识别1脚位置,按表1-1要求输入高、低电平信号,测出相应的输出逻辑电平。

表1-1 74LS04逻辑功能测试表2.测试74LS00四2输入端与非门逻辑功能将74LS00正确接入面包板,注意识别1脚位置,按表1-2要求输入高、低电平信号,测出相应的输出逻辑电平。

3.测试74LS55 二路四输入与或非门逻辑功能将74LS55正确接入面包板,注意识别1脚位置,按表1-3要求输入信号,测出相应的输出逻辑电平,填入表中。

(表中仅列出供抽验逻辑功能用的部分数据)4.测试74LS86四异或门逻辑功能将74LS86正确接入面包板,注意识别1脚位置,按表1-4要求输入信号,测出相应的输出逻辑电平。

五、实验报告要求1.整理实验结果,填入相应表格中,并写出逻辑表达式。

2.小结实验心得体会。

3.回答思考题若测试74LS55的全部数据,所列测试表应有多少种输入取值组合?实验二集成逻辑门电路的参数测试一、实验目的1.掌握TTL和CMOS与非门主要参数的意义及测试方法。

数字系统设计d触发器

数字系统设计d触发器

数字系统设计D触发器是数字电路中常用的基本元件之一,它可以将输入信号在时钟上升沿时锁存,输出信号在时钟下降沿时更新。

下面我们来详细了解一下D触发器的相关知识。

1. D触发器的基本结构

D触发器由两个与非门和一个反馈路径组成。

其中,一个与非门的输入端连接时钟信号,另一个与非门的输入端连接D输入信号,输出端连接反馈路径,反馈路径的输出端连接第一个与非门的另一个输入端。

这样,当时钟信号上升沿来临时,D输入信号就会被锁存到反馈路径中,输出端会输出相应的信号。

2. D触发器的应用

D触发器在数字电路中有着广泛的应用,例如,它可以被用来实现计数器、寄存器、状态机等电路。

在计数器中,D触发器可以被用来记录输入脉冲的数量;在寄存器中,D触发器可以被用来存储数据;在状态机中,D触发器可以被用来记录当前状态。

3. D触发器的特点

D触发器有着以下几个特点:

(1)D触发器具有较高的稳定性和可靠性,可以在高速数字电路中使用。

(2)D触发器的输出信号只在时钟下降沿时更新,可以有效地避免由于信号传输延迟而导致的错误。

(3)D触发器的反馈路径可以实现电路的锁存功能,可以在数字电路中实现各种复杂的逻辑运算。

4. D触发器的扩展

D触发器可以通过添加预置和清零功能来扩展其功能。

预置和清零功能可以使D触发器在特定条件下自动将输出信号设置为高电平或低电平,从而实现更加复杂的数字电路设计。

总的来说,数字系统设计D触发器是数字电路中非常重要的基本

元件,它可以实现锁存、计数、存储等多种功能。

了解D触发器的基本结构、应用、特点以及扩展,对于数字电路的设计和实现都有着重要的意义。

钟控d触 发器设计实验原理

钟控d触发器设计实验原理

钟控D触发器是数字集成电路中的一种重要组成部分,它由六个与非门组成,包括两个基本的RS触发器、时钟控制电路和数据输入电路。

当不向D触发器施加任何时钟输入或在时钟信号的负边沿(下降沿)期间,输出不会发生变化,它将在输出Q处保留其先前的值。

如果时钟信号为高

电平(更准确地说是上升沿/正边沿)并且如果D输入为高电平,则输出也

为高电平,如果D输入为低电平,则输出将变为低的。

因此,在存在时钟

信号的情况下,输出Q跟随输入D。

此外,D触发器也称为维持-阻塞边沿D触发器,由三个SR NAND锁存器构成。

输入级由两个锁存器组成,输出级由一个锁存器组成。

在输入级,数据输入连接到其中的一个NAND锁存器,时钟信号(CLK)并行连接到两

个SR锁存器。

以上内容仅供参考,如需更准确全面的信息,建议查阅相关的专业书籍或咨询专业人士。

实验 触发器设计

实验8 触发器设计一、实验目的:通过本实验了解数据库触发器的概念,掌握触发器完整性设计方法。

二、实验原理触发器(Trigger)是用户定义在关系表上的一类由事件驱动的特殊过程,由服务器自动激活可以进行更为复杂的检查和操作,具有更精细和更强大的数据控制能力。

创建触发器语法格式CREATE TRIGGER <触发器名>{BEFORE | AFTER} <触发事件> ON <表名>FOR EACH ROW[WHEN <触发条件>]<触发动作体>触发时间:Before, AFTER触发事件:insert,update, delete删除触发器:drop trigger <触发器名>显示创建触发器脚本>show create trigger <触发器名>>show triggers;三、实验内容及方法实验平台操作系统:win7,数据库管理平台:mysql5.6或者mysql8,实验用数据库:老师提供的数据库脚本TradeDBSQL.txt(一)触发器应用于数据库完整性设计实体完整性-PK参照完整性-FK用户定义完整性1.参照完整性级联约束在订单表Orders(主表)与订单细节表OrderDetails(副表)中实现更新、删除级联是通过下列方式实现的foreign key(OrderID) references Orders (OrderID)on delete cascade on update cascade用下面的更新、删除触发器实现上面的更新、删除级联1)更新级联触发器orderd_updDELIMITER %% /* 用%% 代替; 作为命令结束符*/Create trigger orderd_upd /* 创建触发器名为orderd_upd */after update on Orders /* 在表orders 上建立更新后触发器*/for each row /* 对于每一行*/begin/* 在表orders上更新后自动更新OrderDetails 表*/ update OrderDetails set OrderID = new.OrderID where OrderID=old.OrderID; end %%特别要注意new,old 的区别old 表示更新前的一行记录(for each row)new 表示更新为新的数据的一行记录。

课程设计jk触发器

课程设计jk触发器一、课程目标知识目标:1. 学生能理解JK触发器的原理,掌握其功能与应用;2. 学生能描述JK触发器的真值表,了解触发器的状态转换过程;3. 学生了解数字电路中触发器的作用,认识到JK触发器在计数器等电路中的应用。

技能目标:1. 学生能够运用所学知识,设计简单的基于JK触发器的数字电路;2. 学生通过实验,掌握JK触发器的测试方法,提高动手实践能力;3. 学生能够运用逻辑分析仪等工具,分析JK触发器的工作状态,培养问题解决能力。

情感态度价值观目标:1. 学生在探索JK触发器过程中,培养对电子技术的兴趣,激发创新意识;2. 学生通过小组合作,培养团队协作精神,提高沟通能力;3. 学生认识到数字电路在现代科技中的重要作用,增强社会责任感。

课程性质:本课程为电子技术基础课程,以理论教学和实践操作相结合的方式进行。

学生特点:学生为初中二年级学生,对电子技术有一定的基础知识,好奇心强,喜欢动手操作。

教学要求:注重理论与实践相结合,强调学生的动手实践能力,培养创新精神和团队协作能力。

通过本课程的学习,使学生能够掌握JK触发器的相关知识,为后续学习数字电路打下基础。

教学过程中,将目标分解为具体的学习成果,便于教学设计和评估。

二、教学内容1. 理论知识:- JK触发器的定义、工作原理及特点;- JK触发器的真值表及状态转换图;- JK触发器在数字电路中的应用,如计数器等。

2. 实践操作:- 使用逻辑门电路搭建JK触发器;- 测试JK触发器的工作状态,分析实验结果;- 设计简单的基于JK触发器的数字电路。

3. 教学大纲安排:- 第一课时:介绍JK触发器的概念、原理及特点,讲解真值表;- 第二课时:分析JK触发器的状态转换过程,举例说明其应用;- 第三课时:实践操作,搭建JK触发器电路,进行测试与分析;- 第四课时:小组合作,设计数字电路,巩固所学知识。

教材章节:本教学内容参考《电子技术基础》第四章第三节“触发器及其应用”。

实验七multisim数字电路原理图设计

电子线路设计软件课程设计报告实验内容:实验七multisim数字电路原理图设计一、实验目的1、认识并了解multisim的元器件库;2、学会使用multisim绘制电路原理图;3、学会使用multisim里面的各种仪器分析数字电路;二、Multisim10 的菜单栏1.File菜单该菜单主要用于管理所创建的电路文件,对电路文件进行打开、保存等操作,其中大多数命令和一般Windows应用软件基本相同,这里不赘述。

下面主要介绍Multisim 10.0的特有命令:●Open Samples:可打开安装路径下的自带实例;●New Project,Open Project,Save Project和Close Project:分别对一个工程文件进行创建、打开、保存和关闭操作。

一个完整的工程包括原理图、PCB文件、仿真文件、工程文件和报告文件;●Version Control:用于控制工程的版本。

用户可以用系统默认产生的文件名或自定义文件名作为备份文件的名称对当前工程进行备份,也可恢复以前版本的工程;●Print Options:包括两个子菜单,Print Circuit Setup子菜单为打印电路设置选项;Print Instruments子菜单为打印当前工作区内仪表波形图选项。

2.Edit菜单“编辑”菜单下的命令主要用于在绘制电路图的过程中,对电路和元件进行各种编辑操作。

一些常用操作,例如,复制,粘贴等和一般Windows应用程序基本相同,这里不再赘述。

下面介绍一些Multisim10.0特有的命令。

●Delete Multi-Page:从多页电路文件中删除指定页。

执行该项操作一定要小心,尽管使用撤销命令可恢复一次删除操作,但删除的信息无法找回;●Paste as Subcricuit:将剪贴板中已选的内容粘贴成电子电路形式;●Find:搜索当前工作区内的元件,选择该项后可弹出对话框,其中包括要寻找元件的名称、类型及寻找的范围等;●Graphic Annotation:图形注释选项,包括填充颜色、类型、画笔颜色、类型和箭头类型;●Order:安排已选图形的放置层次;●Assign to Layer:将已选的项目(例如,REC错误标志、静态指针、注释和文本/图形)安排到注释层;●Layer Setting:设置可显示的对话框;●Orientation:设置元件的旋转角度;●Title Black Position:设置已有的标题框的位置;●Edit Symbol/Title Block:对已选定的图形符号或工作区内的标题框进行编辑。

实验七 触发器

学号

姓名

规定时间

20分钟

成绩

教师签名

触发器

一、实验目的及要求:

1、熟悉并验证触发器的逻辑功能。

2、掌握RS和JK触发器的使用方法和逻辑功能的测试方法。

二、实验仪器:

数字电子技术实验板、数字万用表

三、实验内容及步骤

1、测试双JK触发器74LS73逻辑功能(20分)。

图174LS73引脚图

表1JK触发器的逻辑功能

0

1

CP=1时,T=1,触发器Q端为1翻为0, 端由0翻为1,翻转一次;CP=0时,T触发器处于维持状态

1

1

J

K

CP

Qn

Qn+1

功能说明

0

0

↓

0

0

保持

1

1

0

1

↓

0

0

置“0”

1

0

1

0

↓

0

1

置“1”

1111来自↓01

必翻

1

0

2.触发器的转换

1将JK触发器转化成D触发器,画出改造电路图(30分),并完成表2(10分)。

K连接非门 =K

J、K连接J=K

表2D触发器的逻辑功能

D

CP

Qn

Qn+1

功能说明

0

10

0

0

D=0,与非门D输出为1,与非门C输出为0,则Qn+1=0

CP=0是触发器不工作

1

1

1

10

0

1

D=1,与非门D输出为0,与非门C输出为1,则Qn+1=1

CP=0时,触发器不工作

1

1

触发器集成电路设计Cadence软件模拟仿真

专业综合技能训练报告——JK触发器的设计一、实验目的:1、熟悉UNIX的概念与基本操作;2、掌握Cadence软件的基本操作;3、了解Schematic设计环境4、掌握原理图的设计方法5、熟悉前仿真参数设置和仿真步骤6、学会验证仿真结果二、实验原理1、JK触发器的构造及功能:触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序电路的最基本逻辑单元。

本次是用MOS器件设计一个JK触发器,通过JK 触发器的功能设计电路图,再转换为MOS 器件的电路。

触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序电路的最基本逻辑单元。

触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

由于采用的电路结构形式不同,触发信号的触发方式也不一样。

根据触发方式触发器可分为电平触发、脉冲触发和边沿触发。

电平触发方式结构简单、触发速度快。

在时钟信号有效电平期间(CLK=1 或CLK=0),触发器总是处于可翻转状态,输入信号的变化都会引起触发器状态的变化。

在时钟信号无效电平期间,触发器状态保持不变。

因此,在时钟信号有效电平宽度较宽时,触发器会连续不停地翻转。

如果要求每来一个CLK 脉冲触发器仅翻转一次的话,则对时钟脉的有效电平的宽度要求极为苛刻,所以实际中应用并不广泛。

边沿触发方式的特点是:触发器只在时钟跳转时刻发生翻转,而在C=1 或C=0 期间,输入端的任何变化都不影响输出。

主从型JK 触发器:由主从型JK 触发器转换的各种功能的触发器都属于主从触发方式。

这种触发方式的工作特点是:克服了在CLK 有效电平期间多次翻转现象,具有一次翻转特性。

就是说,在CLK 有效电平期间,主触发器接受了输入信号发生一次翻转后,主触发器状态就一直保持不变,也不再随输入信号J.K的变化而变化。

一次翻转特性有利有弊:利在于克服了空翻现象;弊是带来了抗干扰能力差的问题。

d触发器实验报告

d触发器实验报告D触发器实验报告引言:D触发器是数字电路中常用的一种时序电路元件,其具有存储和传输数据的功能。

本实验旨在通过搭建和测试D触发器电路,加深对该元件的理解,并验证其工作原理。

实验目的:1. 了解D触发器的基本原理和功能;2. 掌握D触发器的搭建方法;3. 验证D触发器在不同输入条件下的工作特性。

实验器材:1. 数字电路实验箱;2. 7400系列集成电路芯片;3. 电压源、示波器等实验设备。

实验步骤:1. 搭建D触发器电路:根据实验箱上的示意图,连接集成电路芯片,将D触发器电路搭建好。

2. 输入电路设计:设计一个简单的输入电路,用于改变D触发器的输入值。

可以使用开关、按钮或者信号发生器等。

3. 测试触发器的工作特性:a. 设置输入为低电平,记录输出状态;b. 将输入切换为高电平,观察输出状态是否发生变化;c. 连续改变输入电平,观察输出是否跟随变化。

4. 测量触发器的时序特性:a. 使用示波器测量D触发器的输入和输出波形;b. 记录并分析触发器的延时时间、上升/下降时间等参数。

实验结果与分析:通过实验,我们得到了D触发器在不同输入条件下的工作特性。

在输入为低电平时,输出保持不变;当输入切换为高电平时,输出状态发生改变。

这说明D 触发器具有存储和传输数据的功能。

同时,我们还测量了触发器的时序特性,得到了一些重要的参数。

讨论与总结:D触发器是数字电路中重要的时序元件,广泛应用于计算机、通信等领域。

通过本次实验,我们深入理解了D触发器的工作原理和特性。

同时,我们也发现了一些问题和改进的空间,例如触发器的响应时间较长,可以尝试优化电路设计以提高性能。

结语:通过本次实验,我们成功搭建和测试了D触发器电路,并验证了其工作原理。

这对于我们进一步理解数字电路和时序电路的原理和应用具有重要意义。

希望通过今后的实验和学习,我们能够更深入地探索和应用这些知识,为科学技术的发展做出贡献。

(完整word版)实验7:使用触发器加强完整性 实验报告

CREATETRIGGERtri6

ONToys

AFTERUPDATE

AS

DECLARE@avgrateMONEY

DECLARE@maxrateMONEY

SELECT@avgrate=AVG(mToyRate)FROMToys

SELECT@maxrate=MAX(mToyRate)FROMToys

1.创建触发器,当修改Orders表中某行数据的mShippingCharges和mGiftWrapCharges时,要修改相应行的总价mTotalCost,以保证结果的正确性。

2.创建after触发器,禁止删除ToysBrand表中的记录。

3.创建Instead of触发器,禁止删除ToysBrand表中的记录。

ROLLBACKTRAN

END

8.

--创建视图

er(

cCandidateCode,vFirstName,vLastName,siTestScore,

cContractRecruiterCode,cName)

AS

andidateCode,vFirstName,vLastName,siTestScore,

IFUPDATE(mShippingCharges)ORUPDATE(mGiftWrapCharges)

BEGIN

DECLARE@change1MONEY

DECLARE@change2MONEY

SELECT@change1=mShippingCharges+mGiftWrapCharges

FROMinserted

7.对Shipment表进行插入操作或者修改操作时,应保证dShipmentDate小于当前日期。

8.对于Recruitment数据库,创建一个视图名为vwCandidateContractRecruiter,其中包含了外部候选人(ExternalCandidate表)的代码,姓名,测试成绩,以及其对应的合同招聘人员(ContractRecruiter表)的代码和名称。并对该视图进行更新,修改外部候选人代码为‘000049’的候选人,更改其测验成绩为87分,并更改相对应的合同招聘人员的名称为‘Roger Federal’。通过创建一个触发器使得能对该视图直接通过下面的Update语句进行更新。

RS触发器

基本触发器的设计预备知识:RS触发器是一种基本的触发器一触发器1触发器的概念触发器:具有记忆功能的基本逻辑电路,能存储二进制信息(数字信息)。

触发器有二个基本特性:( 1 )有两个稳态,可分别表示二进制数码 0 和 1 ,无外触发时可维持稳态;触发器的两个稳定状态①Q=1,通常将Q端作为触发器的状态。

若Q端处于高电平,就说触发器是1状态;②Q=0,Q端处于低电平,就说触发器是0状态;Q端称为触发器的原端或1端,端称为触发器的非端或0端。

( 2 )外触发下,两个稳态可相互转换(称翻转),已转换的稳定状态可长期保持下来,这就使得触发器能够记忆二进制信息,常用作二进制存储单元。

(3 )触发器的分类:根据逻辑功能不同:RS触发器、D触发器、JK触发器、T触发器和触发器等。

触发方式不同:电平触发器、边沿触发器和主从触发器等。

电路结构不同:基本RS触发器,同步触发器、维持阻塞触发器、主从触发器和边沿触发器。

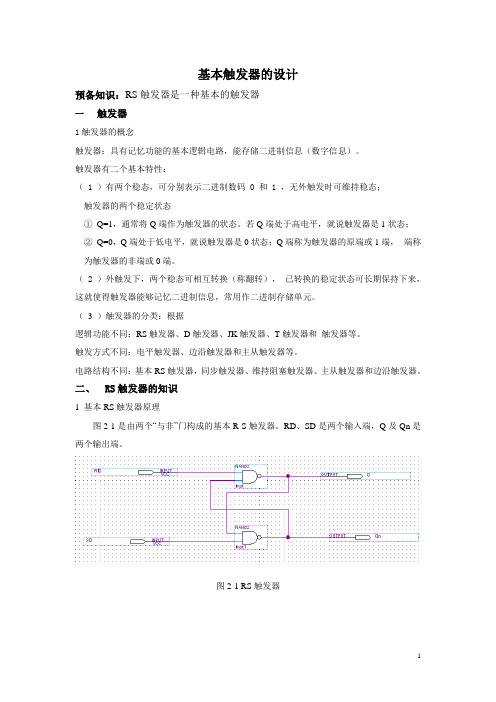

二、RS触发器的知识1 基本RS触发器原理图2-1是由两个“与非”门构成的基本R-S触发器。

RD、SD是两个输入端,Q及Qn是两个输出端。

图2-1 RS触发器2 稳定状态正常工作时,触发器的Q 和Qn 应保持相反,因而触发器具有两个稳定状态:① Q=1,Qn=0。

通常将Q 端作为触发器的状态。

若Q 端处于高电平,就说触发器是1状态; ② Q=0,Qn=1。

Q 端处于低电平,就说触发器是0状态;Q 端称为触发器的原端或1端,Qn 端称为触发器的非端或0端。

3 真值表R-S 触发器的逻辑功能,可以用输入、输出之间的逻辑关系构成一个真值表(或叫功能表)来描述。

① 当RD=0,SD=1时,不论触发器的初始状态如何,Qn 为1,由于“与非”门2的输入全是1,Q 端应为0。

称触发器为状态,R D 为置0端② 当RD =1,SD =0时,不论触发器的初始状态如何,Q 为1,从而使Qn 为0。

称触发器为1状态,SD 置1端。

触发器设计实验的心得体会

触发器设计实验的心得体会触发器是数字电路中一种重要的组件,它可以在特定的时刻检测输入信号,并产生相应的输出信号。

在进行触发器设计的实验中,我学到了许多宝贵的经验和知识。

以下是我对这次实验的心得体会:首先,在实验之前,我对触发器的工作原理进行了充分的了解。

触发器是一种存储器件,它可以在时钟的边缘沿(上升沿或下降沿)时对输入值进行检测,并在满足特定条件时改变输出状态。

通过深入研究触发器的工作原理,我能够更好地理解实验中使用的各种触发器电路。

其次,在实验过程中,我意识到了设计的重要性。

触发器的设计需要考虑许多因素,如输入和输出的电压范围、时钟频率、逻辑功能等。

在设计触发器电路时,我需要根据具体的要求和限制,选择正确的逻辑门、电子元件和布局,以确保电路的性能和可靠性。

此外,我还学会了使用仿真软件进行电路设计和验证,这在实验之后的分析和修正中起到了很大的帮助作用。

此外,我还注意到了实验过程中的一些常见问题。

例如,触发器输入信号的时序关系可能会对电路的正确性产生影响。

一些特定的触发器类型,如JK触发器和D触发器,需要特定的输入信号序列来改变状态。

若输入信号的时序有误,可能导致触发器无法按预期的方式工作。

因此,在实验中,我学会了仔细检查信号的时序和电平,以确保触发器按照设计的逻辑来工作。

另外,我还学到了电路性能评估和优化的重要性。

触发器的性能可以通过多个参数进行评估,如响应时间、噪声容限、功耗等。

在实验中,我学会了使用性能评估工具来量化电路的性能,并通过调整电路结构、参数和时钟频率等方法来优化触发器设计。

这个过程不仅提高了我对触发器电路性能的理解,还培养了我的分析和问题解决能力。

最后,这次实验让我明白了团队合作的重要性。

触发器设计并非一项单独的任务,它通常需要多个人的协作和配合。

在实验中,我和我的同学一起合作,共同讨论问题、设计电路和进行实验。

通过团队合作,我们能够共享知识和经验,相互帮助和支持,最终完成了一个优秀的触发器设计实验。

D触发器的设计范文

D触发器的设计范文D触发器是一种基本的数字逻辑电路元件,以存储和改变信息的形式对输入信号进行处理。

它是数字电路设计中的重要组成部分,广泛应用于计算机、通信系统、控制系统等数字电子产品中。

D触发器的设计包括逻辑功能设计、电路设计等方面,下面将从这两个方面对D触发器的设计进行详细介绍。

1.逻辑功能设计首先,需要确定D触发器的输入和输出信号。

D触发器的输入信号一般分为时钟信号、数据输入信号和复位信号,输出信号即为存储器单元的输出信号。

然后,根据D触发器的逻辑功能特性进行设计。

D触发器的逻辑功能可以通过以下几个方面来设计:1.1时钟控制:D触发器的数据输入信号只有在时钟信号的控制下才能进行存储和更新。

因此,在设计时需要明确时钟信号的作用和控制条件,确保只有在时钟脉冲的上升沿或下降沿才能更新输出信号。

1.2数据存储:D触发器的主要作用是存储输入信号。

在设计时需要确定输入信号的存储方式,是直接存储还是经过逻辑运算后再存储。

同时,还需要考虑存储数据的位数,以适应不同的应用场景和需求。

1.3复位功能:D触发器一般还具有复位功能,用于清除存储的数据。

在设计时需要确定复位信号的作用和控制条件,确保在复位信号有效时能够清除存储的数据。

1.4输出控制:D触发器的输出信号可以通过逻辑门实现不同的输出控制功能。

在设计时需要确定输出信号的控制方式,以满足不同的应用需求。

2.电路设计2.1电路结构:D触发器常见的电路结构有SR触发器、JK触发器、T触发器等。

在设计时需要根据应用需求和电路复杂度等因素选择适合的电路结构,以实现稳定可靠的电路功能。

2.2元件选型:在设计D触发器的电路时,需要选择合适的元件,包括逻辑门、触发器芯片等。

元件的选型需要考虑其性能、价格、可靠性等因素。

2.3电路连线:D触发器的电路连线需要按照逻辑功能设计的要求进行。

在设计时需要合理规划电路连线的路径,保证信号的传输和连接的可靠性。

除了逻辑功能设计和电路设计外,D触发器的设计还需要进行仿真和验证。

基本逻辑门逻辑实验

实验一、基本逻辑门逻辑实验1、实验器件:74LS00 1片,74LS28 1片2、实验内容:(1)测试二输入四与非门74LS00一个与非门的输入和输出之间的逻辑关系。

(2)测试二输入四或非门74LS28一个或非门的输入和输出之间的逻辑关系。

(3)用与非门实现与门、或门的逻辑关系。

3、实验要求:设计电路,写出逻辑表达式,列出真值表,进行数据分析。

实验二、三态门实验1、实验器件:74LS00 1片,74LS125 1片,万用表2、实验内容:(1)74LS125三态门的输出负载为74LS00一个与非门输入端。

74LS00同一个与非门的另一个输入端接低电平,测试74LS125三态门三态输出、高电平输出、低电平输出的电压值。

同时测试74LS125三态输出时74LS00输出值。

(2)74LS125三态门的输出负载为74LS00一个与非门输入端。

74LS00同一个与非门的另一个输入端接高电平,测试74LS125三态门三态输出、高电平输出、低电平输出的电压值。

同时测试74LS125 三态输出时74LS00输出值。

3、实验要求:画出电路图,自己设计数据记录表格,添入所测数据,作出数据分析。

实验三、数据选择器实验1、实验器件:74LS153 1片,示波器2、实验内容:测试74LS153中一个4选1数据选择器的逻辑功能。

四个数据输入引脚C0—C3分别接实验箱上的5 MHz、1 MHz、500 KHz、100 KHz脉冲源。

改变数据选择引脚B、A和使能端G的电平,产生8种不同的组合。

观测每种组合下数据选择器的输出波形。

3、实验要求:自己画出电路图,设计数据记录表格,添入所测数据,作出数据分析。

实验四、译码器实验1、实验器件:74LS139 1片2、实验内容:测试74LS139中一个2—4译码器的逻辑功能。

四个译码输出引脚Y0—Y3接电平指示灯。

改变引脚G、B、A的电平。

观测并记录指示灯的显示状态。

3、实验要求:画出电路图,自己设计数据记录表格,添入所测数据,作出数据分析。

FPGA程序设计实验报告 JK触发器

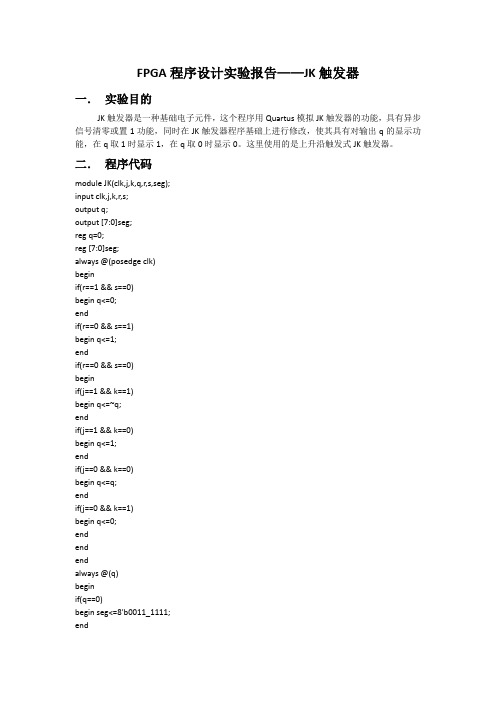

FPGA程序设计实验报告——JK触发器一.实验目的JK触发器是一种基础电子元件,这个程序用Quartus模拟JK触发器的功能,具有异步信号清零或置1功能,同时在JK触发器程序基础上进行修改,使其具有对输出q的显示功能,在q取1时显示1,在q取0时显示0。

这里使用的是上升沿触发式JK触发器。

二.程序代码module JK(clk,j,k,q,r,s,seg);input clk,j,k,r,s;output q;output [7:0]seg;reg q=0;reg [7:0]seg;always @(posedge clk)beginif(r==1 && s==0)begin q<=0;endif(r==0 && s==1)begin q<=1;endif(r==0 && s==0)beginif(j==1 && k==1)begin q<=~q;endif(j==1 && k==0)begin q<=1;endif(j==0 && k==0)begin q<=q;endif(j==0 && k==1)begin q<=0;endendendalways @(q)beginif(q==0)begin seg<=8'b0011_1111;endif(q==1)begin seg<=8'b0000_0110;endendendmodule三.仿真结果对程序进行编译仿真之后,得到以下结果:仿真结果说明:对于上升沿式JK触发器,仅在上升沿到来是触发改变q的取值。

r和s是两个异步信号输入端,在r取1,s取0时,无论j,k输入端如何,q始终取0。

在r取0,s取1时,无论j,k输入端如何,q始终取1。

在r和s都取0时,触发器正常工作,其q值取决于上升沿到来时的j,k以及之前一个周期的q值。

时序逻辑电路实验报告

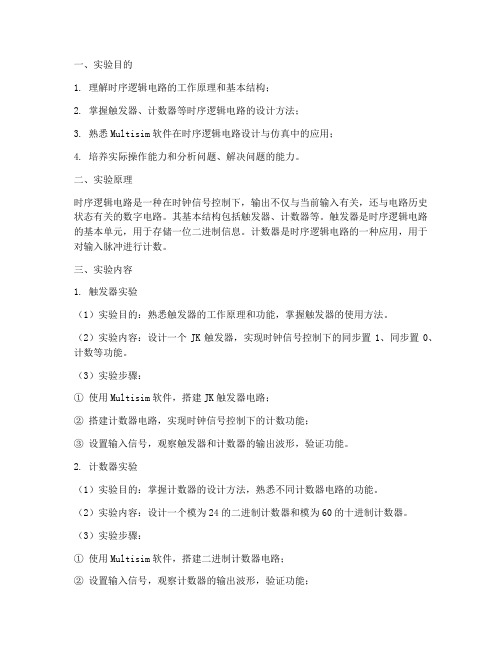

一、实验目的1. 理解时序逻辑电路的工作原理和基本结构;2. 掌握触发器、计数器等时序逻辑电路的设计方法;3. 熟悉Multisim软件在时序逻辑电路设计与仿真中的应用;4. 培养实际操作能力和分析问题、解决问题的能力。

二、实验原理时序逻辑电路是一种在时钟信号控制下,输出不仅与当前输入有关,还与电路历史状态有关的数字电路。

其基本结构包括触发器、计数器等。

触发器是时序逻辑电路的基本单元,用于存储一位二进制信息。

计数器是时序逻辑电路的一种应用,用于对输入脉冲进行计数。

三、实验内容1. 触发器实验(1)实验目的:熟悉触发器的工作原理和功能,掌握触发器的使用方法。

(2)实验内容:设计一个JK触发器,实现时钟信号控制下的同步置1、同步置0、计数等功能。

(3)实验步骤:① 使用Multisim软件,搭建JK触发器电路;② 搭建计数器电路,实现时钟信号控制下的计数功能;③ 设置输入信号,观察触发器和计数器的输出波形,验证功能。

2. 计数器实验(1)实验目的:掌握计数器的设计方法,熟悉不同计数器电路的功能。

(2)实验内容:设计一个模为24的二进制计数器和模为60的十进制计数器。

(3)实验步骤:① 使用Multisim软件,搭建二进制计数器电路;② 设置输入信号,观察计数器的输出波形,验证功能;③ 使用Multisim软件,搭建十进制计数器电路;④ 设置输入信号,观察计数器的输出波形,验证功能。

四、实验结果与分析1. 触发器实验实验结果显示,设计的JK触发器能够实现同步置1、同步置0、计数等功能。

在计数过程中,触发器的输出波形符合预期,验证了JK触发器的功能。

2. 计数器实验实验结果显示,设计的模为24的二进制计数器和模为60的十进制计数器均能实现预期的计数功能。

在计数过程中,计数器的输出波形符合预期,验证了计数器电路的功能。

五、实验总结本次实验通过设计、搭建和仿真时序逻辑电路,掌握了触发器、计数器等时序逻辑电路的设计方法,熟悉了Multisim软件在时序逻辑电路设计与仿真中的应用。

试验七微程序控制器的实现试验

实验七微程序控制器的实现实验一、实验目的和要求1、掌握时序信号发生电路组成原理。

2、掌握微程序控制器的设计思想和组成原理。

3、掌握微程序的编制、写入,观察微程序的运行。

二、实验内容1、实验原理实验所用的时序电路原理如图7-1所示,可产生4个等间隔的时序信号TS1~TS4,其中SP为时钟信号,由实验机上时钟源提供,可产生频率及脉宽可调的方波信号。

学生可根据实验要求自行选择方波信号的频率及脉宽。

为了便于控制程序的运行,时序电路发生器设计了一个启停控制触发器UN1B,使TS1~TS4信号输出可控。

图中“运行方式”、“运行控制”、“启动运行”三个信号分别是来自实验机上三个开关。

当“运行控制”开关置为“运行”,“运行方式”开关置为“连续”时,一旦按下“启动运行”开关,运行触发器UN1B的输出QT一直处于“1”状态,因此时序信号TS1~TS4将周而复始地发送出去;当“运行控制”开关置为“运行”,“运行方式”开关置为“单步”时,一旦按下“启动运行”开关,机器便处于单步运行状态,即此时只发送一个CPU周期的时序信号就停机。

利用单步方式,每次只运行一条微指令,停机后可以观察微指令的代码和当前微指令的执行结果。

另外,当实验机连续运行时,如果“运行方式”开关置“单步”位置,也会使实验机停机。

2、微程序控制电路与微指令格式①微程序控制电路微程序控制器的组成见图7-2,其中控制存储器采用3片E2PROM 2816芯片,具有掉电保护功能,微命令寄存器18位,用两片8D触发器74LS273(U23、U24)和一片4D触发器74LS175(U27)组成。

微地址寄存器6位,用三片正沿触发的双D触发器74LS74(U14~U16)组成,它们带有清“0”端和预置端。

在不进行判别测试的情况下,T2时刻打入微地址寄存器的内容即为下一条微指令地址。

当T4时刻进行测试判别时,转移逻辑满足条件后输出的负脉冲通过强置端将某一触发器置为“1”状态,完成地址修改。

实验七 触发器及其应用实验

实验七触发器及其应用实验一、实验概述本实验是通过使用74LS00、74LS74和74LS76来实现RS触发器、D触发器、JK 触发器以及T触发器的功能。

二、实验目的1、掌握基本RS、JK、T和D触发器的逻辑功能2、掌握集成触发器的功能和使用方法3、熟悉触发器之间相互转换的方法三、实验预习要求1、复习有关触发器内容,熟悉有关器件的管脚分配2、列出各触发器功能测试表格3、参考有关资料查看74LS00、74LS74和74LS76的逻辑功能四、实验原理在实际的数字系统中往往包含大量的存储单元,而且经常要求他们在同一时刻同步动作,为达到这个目的,在每个存储单元电路上引入一个时钟脉冲(CLK)作为控制信号,只有当CLK到来时电路才被“触发”而动作,并根据输入信号改变输出状态。

把这种在时钟信号触发时才能动作的存储单元电路称为触发器,以区别没有时钟信号控制的锁存器。

触发器具有两个稳定状态,用以表示逻辑状态“1”和“0”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存贮器件,是构成多种电路的最基本逻辑单元。

1、RS触发器RS触发器是构成其它各种功能触发器的基本组成部分。

又称为基本RS触发器。

结构是把两个与非门或者或非门G1、G2的输入、输出端交叉连接,如图7.4-1所示。

图7.4-1 RS触发器2、D触发器D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路,如图7.4-2所示。

在数字系统和计算机中有着广泛的应用。

触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

JK触发器是数字电路触发器中的一种基本电路单元,如图7.4-3所示。

JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验七设计基本触发器一、实验准备

该实验不需要使用七个模块组中的功能单元,所以拨码开关状态;拨码开关MODEL_SEL5-8全置于“OFF状态,以使用JTAG下载方式,这里用户可根据自己所用的下载线来选择适当的下载方式。

矚慫润厲钐瘗睞枥庑赖賃軔朧。

二、实验目的

熟悉利用Quartusll开发数字电路的基本流程和Quartusll软件的相关操作,

介绍Quartusll的软件,掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,下载等基本操作。

了解VHDL或原理图设计方法与定制IP模块的思想。

掌握基本触发器的设计思路及工作原理

三、实验原理

通过开关分别输入单bit的数据,并用开关作为控制信号,实现置位和复位。

将

T触发器的结果分别在2个LED上显示。

聞創沟燴鐺險爱氇谴净祸測樅。

四、实验内容

1、用VHDL语言设计D触发器和T触发器;注意时钟要用到分频电路。

2、用Quartusll软件进行编译,仿真,下载到实验平台进行验证。

五、设计原理框图

六、引脚分配情况

D A21

CLK P25

CLR F6

P SET B21

QT AA11

Q AC10

MODEL SEL1-3 均置于“OFF

D触发器和

Q,QT 为D 触发器和T 触发器的输出信号,分别对应平台上的 LED0和LED7。

CLR,PSET 为高电平清零和置位信号, CLK 为时钟信号。

残骛楼諍锩瀨濟溆塹籟婭骤東。

七、结果分析

波形仿真

如上所述,Q,QT 作为D 触发器和T 触发器的输出信号,分别对应平台

CLR,PSET 为高电平清零和置位信号, CLK 为时 这里简单列出波形图, 实际可以自己加上其他的

八、VHDL 源程序代码

--D flip flop

library IEEE;

use IEEE.std_logic_1164.all;

ENTITY DFFL OP IS

PORT ( D: in STD_LOGIC;

CLK,CLR, PSET: in STD_LOGIC;-- 时钟,清零,置位

Q: out STD LOGIC --输出

);

END DFFL OP;

ARCHITECTURE FFA OF DFFL OP IS

BEGIN

P ROCESS(CLK ,P SET,CLR) BEGIN

Q<='1';

ELSIF CLR='1' THEN Q<='0';

ELSIF CLK'EVENT AND CLK='1' THEN

Name CLK CLR £ FS ET G QT Value a 11.£5 ] B

B B

B

B

B

]ps ISO. 0 ILS 11.25 ns

-J ______________

-rLZFLZFLFLJnLJn_J^

4S0 0 ns

从上图可以看出, 上的LED0和LED7,正确对应了结果。

钟信

号,都实现了相应的功能, 限于篇幅, 信号进行仿真。

酽锕极額閉镇桧猪訣锥顧荭钯。

--输入

IF P SET='1' THEN --异步置位

--异步7冃零

Q<=D;

END IF;

END PROCESS;

END FFA;

--- T flip flop

LIBRARY IEEE;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY TFFLOP IS

PORT (

T: in STD_LOGIC; -- 输入

CLK: in STD_LOGIC; --- 时钟

QT: OUT STD_LOGIC -输出

);

END TFFLOP;

ARCHITECTURE FFB OF TFFLOP IS

SIGNAL Q_S:STD_LOGIC;

BEGIN

PROCESS(CLK,T)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF T='1' THEN

Q_S<=NOT Q_S;

ELSE

Q_S<=Q_S;

END IF;

END IF;

QT<=Q_S;

END PROCESS;

END FFB;

-- 分频电路,平台提供的频率为50MHZ, 进行分频,便于观察!library IEEE; use IEEE.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity dividef is

port (

CLK : in std_logic;

CLK_D: out std_logic

); end entity;

architecture DIVIDE_

arch of dividef is

signal COUNT :

std_logic_vector (18 downto 0 ); begin

PROCESS(CLK)

BEGIN

if clk'event and clk='1' then

IF COUNT<"1111111111111111111" then

COUNT<=COUNT+1;

ELSE COUNT<="0000000000000000000";

END IF;

END IF;

END PROCESS;

PROCESS(COUNT)

BEGIN

IF COUNT="1111111111111111111" THEN

CLK_D<='1';

ELSE CLK_D<='0';

END IF;

END PROCESS;

end architecture;

---此处附上JK 触发器的代码,实现步骤相同,可进行参考library IEEE;

use IEEE.std_logic_1164.all;

ENTITY JKFF IS

PORT (

J,K: in STD_LOGIC; CLK,CLR,PSET: in

STD_LOGIC;

Q,QB: out STD_LOGIC

);

END JKFF;

ARCHITECTURE FFC OF JKFF IS

SIGNAL Q_S,QB_S:STD_LOGIC;

BEGIN

PROCESS(PSET,CLR,J,K,CLK)

BEGIN

IF PSET='1' THEN

Q_S<='1';

QB_S<='1';

ELSIF CLR='1' THEN

Q_S<='0';

QB_S<='1'; -- PSET=1,CLR=1 输出应该不确定ELSIF CLK'EVENT AND CLK='1' THEN

IF j='0' AND K='1' THEN

Q_S<='0'; QB_S<='1';

ELSIF j='1' AND K='0' THEN Q_S<='1';

QB_S<='1';

ELSIF j='1' AND K='1' THEN

Q_S<=not Q_S;

QB_S<=not QB_S;

END IF;

END IF;

Q<=Q_S;

QB<=QB_S;

END PROCESS;

END FFC;。