实验七 触发器解读

数字逻辑实验报告:触发器及其作用

数字逻辑实验报告:触发器及其作用一、实验目的1. 学习触发器的基本概念、类型及其工作原理;2. 掌握触发器的电路实现方法;3. 掌握使用触发器进行时序逻辑设计的方法。

二、实验原理触发器(Flip-flop)是数字逻辑电路中最基本的存储元件。

它可以在电路中实现数据的存储、时序的生成、状态的转移等功能。

触发器从功能上分为两大类:时序逻辑触发器和状态逻辑触发器。

时序逻辑触发器是指根据输入信号的时序变化来激发触发器输出端口状态变化的触发器,常见的有SR触发器、D触发器和JK触发器等。

状态逻辑触发器是指触发器的输出值与输入值中的某些形式的关系有关,常见的有T触发器和R-S触发器等。

此实验主要介绍SR触发器、D触发器、JK触发器的实现及其作用。

1. SR触发器SR触发器也称为RS触发器,它的英文全称是Set-Reset Flip-flop。

SR触发器的输入有两个:S、R。

当S=1,R=0时,Q输出为1;当S=0,R=1时,Q输出为0;当S=R=1时,Q的状态就不确定了。

具有这个不确定状态的原因是因为在SR触发器中,S和R是可以同时为1的,这种情况会导致电路出现失效或过度充电的问题,故SR触发器不常用。

2. D触发器D触发器是指数据存储触发器,它有一个数据输入信号D,其输出信号Q与输入信号D同步,并且保持输出信号状态不变。

当时钟信号CK上升时,D触发器将数据D储存在内部存储器中,当时钟信号CK下降时,存储器中的数据被保持不变。

D触发器还具有一个反相输出信号Q',它与输出信号Q恰好相反。

3. JK触发器JK触发器是指一种利用J和K两个输入信号来控制输出状态的电路。

当J=K=0时,JK触发器不动;当J=1,K=0时,JK触发器转换到置“1”状态;当J=0,K=1时,JK触发器转换到复位“0”状态;当J=K=1时,JK触发器的状态与上一状态相反。

这里需要注意的是,当J=K=1时,JK触发器可以作为一个数字计数器或频率分带器使用。

数电实验报告触发器及其应用(共10篇)

数电实验报告触发器及其应用(共10篇)1、实验目的:掌握触发器的原理和使用方法,学会利用触发器进行计数、存储等应用。

2、实验原理:触发器是一种多稳态数字电路,具有存储、计数、分频、时序控制等功能。

常见的触发器有RS触发器、D触发器、T触发器、JK触发器等。

RS触发器是由两个交叉互连的反相器组成的,它具有两个输入端R(复位)和S(置位),一个输出端Q。

当输入R=1,S=0时,Q=0;当输入R=0,S=1时,Q=1;当R=S=1时,无法确定Q的状态,称为禁态。

JK触发器是将RS触发器的两个输入端合并在一起而成,即J=S,K=R,当J=1,K=0时,Q=1;当J=0,K=1时,Q=0;当J=K=1时,Q反转。

JK触发器具有启动、停止、颠倒相位等功能。

D触发器是由单个输入端D、输出端Q和时钟脉冲输入端组成的,当时钟信号上升沿出现时,D触发器的状态发生改变,如果D=1,Q=1;如果D=0,Q=0。

T触发器只有一个输入端T和一个输出端Q,在每个时钟脉冲到来时,T触发器执行T→Q操作,即若T=1,则Q取反;若T=0,则Q保持不变。

触发器可以组成计数器、分频器、存储器、状态机等各种数字电路,被广泛用于计算机、控制系统等领域。

3、实验器材:数码万用表、示波器、逻辑分析仪、CD4013B触发器芯片、几个电阻、电容、开关、信号发生器等。

4、实验内容:4.1 RS触发器测试利用CD4013B芯片来测试RS触发器的功能,在实验中将RS触发器的输入端分别接入CD4013B芯片的端子,用示波器观察输出端的波形变化,并记录下输入输出关系表格,来验证RS触发器的工作原理。

具体实验步骤如下:将CD4013B芯片的端子按如下接线方式连接:RST1,2脚接入+5V电源,C1个100nF的电容与单位时间5 ns的外部时钟信号交替输入接口CLK,以模拟器件为master时,向器件提供单个时钟脉冲。

测试时选择适宜的数据输入,R1和S2另一端程+5V,S1和R2另一端连接接地GND,用万用表测量各端电压,电容缓存的电压。

触发器认知实习报告

触发器认知实习报告一、前言触发器是数字电路中常见的一种基本电路,它能够在输入信号发生变化时产生输出信号的跃变。

本次实习的主要任务是理解和掌握触发器的工作原理,以及如何设计和实现触发器。

二、实习内容和过程实习的第一步是了解触发器的基本概念和分类。

触发器可以根据其工作原理和功能特点分为多种类型,如同步触发器、异步触发器、边沿触发器、计数触发器等。

在实习过程中,我通过阅读相关资料和教材,对触发器的分类和工作原理有了深入的了解。

接下来,我进行了触发器的设计和实现。

首先,我选择了同步触发器作为实习对象,因为它是最常见的一种触发器,其原理也比较简单。

我使用电路设计软件,根据同步触发器的电路图,设计出了一个同步触发器的电路。

然后,我使用实验设备,搭建了同步触发器的实验电路,并进行了实验验证。

通过实验,我进一步理解了同步触发器的工作原理和特性。

在设计同步触发器的基础上,我又进一步设计了异步触发器和边沿触发器。

异步触发器的工作原理与同步触发器不同,它不需要时钟信号的控制,而是根据输入信号的变化来产生输出信号的跃变。

边沿触发器则是一种特殊的触发器,它只能在输入信号的边沿时刻产生输出信号的跃变。

通过设计和实现这两种触发器,我对触发器的理解和掌握更加深入。

三、实习成果和收获通过本次实习,我深入理解了触发器的基本概念、分类和工作原理,掌握了触发器的设计和实现方法。

同时,我也通过实验验证了触发器的特性和性能,提高了自己的实验能力和动手能力。

实习过程中,我也发现了一些问题,如触发器的稳定性和抗干扰性等。

这些问题需要我在今后的学习和研究中进一步深入探讨和解决。

四、对未来工作的建议通过本次实习,我对触发器有了更深入的理解和掌握。

在今后的学习和工作中,我将继续深入研究触发器的相关理论和应用,提高自己的专业素养和技能水平。

同时,我也将注重实践能力的培养,不断丰富自己的实验经验和实践能力。

总之,本次实习是一次非常有意义的实践过程,我对触发器的理解和掌握有了很大的提高。

触发器专项讲解课件

业务逻辑触发器可以提高业务的效率和 准确性,减少人为干预和错误。

04

触发器的优缺点

触发器的优点

01

02

03

04

高效性

触发器在满足特定条件时自动 执行,无需用户手动干预,提

高了处理效率。

一致性

触发器可以确保在多个地方执 行相同的操作,保持数据的一

致性。

简化操作

通过触发器,可以将一系列复 杂的操作简化为简单的规则,

方便用户管理。

预防性操作

触发器可以在数据变更之前或 之后立即执行某些操作,例如 验证、日志记录或数据同步。

触发器的缺点

性能影响

触发器在数据变更时需 要额外执行,可能会对 数据库性能产生一定影

响。

复杂性增加

触发器使得数据库操作 变得更为复杂,增加了

维护和调试的难度。

难以管理

大量的触发器可能导致 管理混乱,使得跟踪和

触发器可以与事务处理相关联,确保 数据的完整性和一致性。

03

触发器的使用场景

数据库操作中的触发器

数据库触发器是一种特殊的存储过程,它会在数据库表上执行特定操作 时自动执行。例如,当在表中插入、更新或删除记录时,触发器可以自 动执行相应的操作。

数据库触发器可以用于实现数据完整性束缚、自动日志记录、数据校验 等功能。通过在触发器中编写逻辑,可以确保数据在修改时遵循特定的

定义与功能

触发器是一种数据库对象,用于响应表事件,而视图是基于SQL 查询的结果集的可视化表。

触发时机

触发器在特定表事件产生时自动执行,而视图用于查询数据。

执行方式

触发器是自动执行的,而视图是查询数据时使用的对象。

07

触发器应用案例分析

触发器的实验原理

触发器的实验原理咱先得知道啥是触发器呢。

简单来说呀,触发器就像是一个超级警觉的小卫士。

你想啊,在一个电路的小世界里,或者在数据库这个大仓库里,它就在那静静地等着某个特定的事情发生。

就好比你在门口放了个小铃铛,只要有人一推门,铃铛就响,这个铃铛就有点像触发器的感觉呢。

在电路里呀,触发器是有自己独特的结构的。

它是由好多电子元件组合起来的。

比如说有逻辑门这些小家伙。

逻辑门就像是一群有着自己小脾气的小精灵。

它们有的只让电流通过的时候说“是”,有的则是在电流没有的时候说“是”,这些小精灵们互相配合着,就构建出了触发器的基本框架。

当输入的电信号有了某种变化的时候,就像你给这些小精灵们一个暗号一样,它们就会按照之前设定好的规则,让触发器的输出发生改变。

比如说从低电平变成高电平,或者反过来。

这就好像是小铃铛响了之后,屋里的小狗就开始汪汪叫,有了一个连锁的反应。

再说说数据库里的触发器。

数据库就像是一个超级大的信息宝库,里面存着各种各样的数据,就像宝藏一样。

那触发器在这呢,就是一个超级警觉的管理员。

比如说,当你在这个数据库里插入了一条新的数据,就像是你往宝库里放了一个新的宝贝。

这个时候,触发器就会被触发啦。

它可能会去检查这条新数据是不是符合某些规则。

要是不符合呢,它就会像个小管家一样,跳出来说“不行不行,这个数据有点问题呢。

”然后可能会阻止这个数据的插入,或者对这个数据进行一些修改,让它变得符合要求。

这就像是宝库有自己的规矩,不是啥东西都能随便放进去的。

那触发器是怎么知道什么时候该干活呢?这就涉及到触发的条件啦。

在电路里,这个条件可能是电压达到了某个值,或者是电流的变化方式符合了设定的模式。

就像是小铃铛只有在门被推开到一定角度的时候才会响。

在数据库里呢,这个触发条件可能是对某个表进行了特定的操作,像插入、删除或者修改数据。

这就像是宝库的管理员规定了,只有在有人拿了某个特定的宝物或者往某个特定的地方放宝物的时候,他才会出来检查。

(完整word版)实验7:使用触发器加强完整性 实验报告

CREATETRIGGERtri6

ONToys

AFTERUPDATE

AS

DECLARE@avgrateMONEY

DECLARE@maxrateMONEY

SELECT@avgrate=AVG(mToyRate)FROMToys

SELECT@maxrate=MAX(mToyRate)FROMToys

1.创建触发器,当修改Orders表中某行数据的mShippingCharges和mGiftWrapCharges时,要修改相应行的总价mTotalCost,以保证结果的正确性。

2.创建after触发器,禁止删除ToysBrand表中的记录。

3.创建Instead of触发器,禁止删除ToysBrand表中的记录。

ROLLBACKTRAN

END

8.

--创建视图

er(

cCandidateCode,vFirstName,vLastName,siTestScore,

cContractRecruiterCode,cName)

AS

andidateCode,vFirstName,vLastName,siTestScore,

IFUPDATE(mShippingCharges)ORUPDATE(mGiftWrapCharges)

BEGIN

DECLARE@change1MONEY

DECLARE@change2MONEY

SELECT@change1=mShippingCharges+mGiftWrapCharges

FROMinserted

7.对Shipment表进行插入操作或者修改操作时,应保证dShipmentDate小于当前日期。

8.对于Recruitment数据库,创建一个视图名为vwCandidateContractRecruiter,其中包含了外部候选人(ExternalCandidate表)的代码,姓名,测试成绩,以及其对应的合同招聘人员(ContractRecruiter表)的代码和名称。并对该视图进行更新,修改外部候选人代码为‘000049’的候选人,更改其测验成绩为87分,并更改相对应的合同招聘人员的名称为‘Roger Federal’。通过创建一个触发器使得能对该视图直接通过下面的Update语句进行更新。

触发器实验报告

触发器实验报告一、实验目的本次实验的主要目的是深入了解触发器的工作原理和功能,通过实际操作和观察,掌握触发器在数字电路中的应用和特性。

二、实验原理触发器是一种具有记忆功能的基本逻辑单元,它能够在特定的输入条件下改变状态,并保持该状态直到接收到新的输入信号。

常见的触发器类型包括 SR 触发器、JK 触发器、D 触发器等。

以 D 触发器为例,其工作原理基于时钟信号的控制。

当时钟信号上升沿(或下降沿)到来时,D 输入端的数据被传送到输出端 Q。

三、实验设备与材料1、数字电路实验箱2、 74LS74(D 触发器芯片)3、示波器4、逻辑分析仪5、导线若干四、实验步骤1、按照实验电路图,在数字电路实验箱上连接好 D 触发器的引脚。

2、将 D 输入端分别连接到高电平(1)和低电平(0),观察时钟信号作用下 Q 输出端的变化。

3、使用示波器监测时钟信号和 Q 输出端的波形,记录并分析。

4、利用逻辑分析仪对触发器的输入和输出信号进行采集和分析,进一步验证其工作特性。

五、实验数据与结果在实验过程中,我们记录了以下数据:当 D 输入端为高电平时,在时钟信号的上升沿,Q 输出端变为高电平;当 D 输入端为低电平时,在时钟信号的上升沿,Q 输出端变为低电平。

通过示波器观察到的时钟信号和 Q 输出端的波形显示,Q 输出端的变化与时钟信号的上升沿和 D 输入端的电平状态相对应,符合 D 触发器的工作原理。

逻辑分析仪采集到的数据也进一步证实了触发器的正确工作。

六、实验分析与讨论1、从实验结果可以看出,D 触发器能够准确地在时钟信号的控制下存储和传输数据,具有稳定可靠的特性。

2、在实际应用中,触发器常用于存储二进制数据、实现计数器、移位寄存器等功能。

3、实验中可能存在的误差主要包括连接线路的接触不良、实验仪器的精度限制等。

但总体来说,实验结果能够清晰地反映出触发器的工作原理和性能。

七、实验结论通过本次触发器实验,我们成功地验证了 D 触发器的工作原理和特性。

实验报告 触发器

实验报告触发器实验报告:触发器引言:触发器是数字电路中常见的重要元件,它可以存储和控制信号的传输。

本实验旨在通过实际搭建触发器电路,了解其工作原理和应用。

一、实验目的本实验的目的是通过实际搭建触发器电路,掌握触发器的工作原理、特性和应用。

二、实验器材和原理2.1 实验器材:- 电路实验板- 电源- 电压表- 电流表- 逻辑门芯片- 连接线2.2 实验原理:触发器是一种存储器件,可以存储和控制信号的传输。

它由多个逻辑门组成,根据输入信号的不同,可以分为RS触发器、D触发器、JK触发器和T触发器等多种类型。

三、实验步骤3.1 搭建RS触发器电路首先,将两个逻辑门芯片连接在电路实验板上,一个作为RS触发器的输入端,另一个作为输出端。

然后,将电源和适当的电阻连接到逻辑门芯片上,以提供所需的电压和电流。

最后,根据电路图连接连线,搭建完整的RS触发器电路。

3.2 检验和调试电路在搭建好电路后,使用电压表和电流表检验电路的电压和电流是否正常。

如果有异常,需要及时排除故障。

然后,通过改变输入信号,观察输出信号的变化。

根据实验结果,对电路进行调试,确保触发器的正常工作。

3.3 测试触发器的特性在调试完电路后,可以进行一些实验来测试触发器的特性。

例如,可以通过改变输入信号的频率和占空比,观察输出信号的变化。

还可以通过改变逻辑门芯片的类型,比较不同类型触发器的性能差异。

四、实验结果和分析通过实验,我们可以得到触发器的工作特性和性能数据。

根据实验结果,我们可以分析触发器的优缺点,以及在数字电路设计中的应用。

五、实验总结触发器作为数字电路中的重要元件,在现代电子技术中得到了广泛应用。

通过本实验,我们深入了解了触发器的工作原理、特性和应用。

同时,我们也学会了搭建触发器电路、调试电路和分析实验结果的方法。

六、实验心得通过本次实验,我深刻认识到了触发器在数字电路中的重要性。

触发器可以存储和控制信号的传输,是数字电路中的核心部件之一。

物理学实验讲义——单稳态触发器与施密特触发器

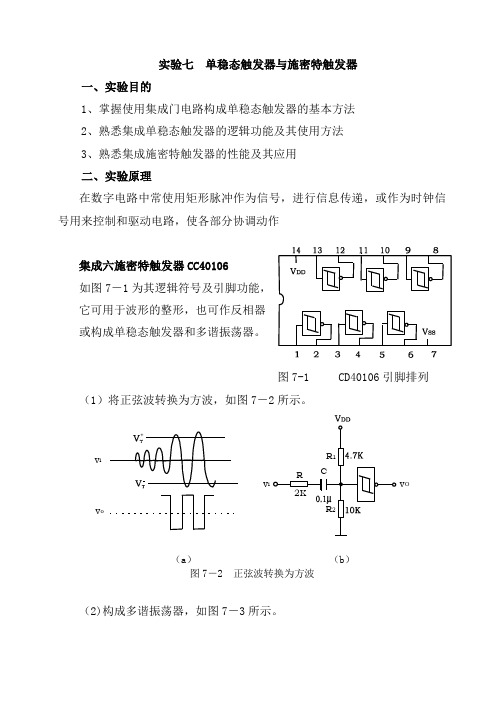

实验七单稳态触发器与施密特触发器一、实验目的1、掌握使用集成门电路构成单稳态触发器的基本方法2、熟悉集成单稳态触发器的逻辑功能及其使用方法3、熟悉集成施密特触发器的性能及其应用二、实验原理在数字电路中常使用矩形脉冲作为信号,进行信息传递,或作为时钟信号用来控制和驱动电路,使各部分协调动作集成六施密特触发器CC40106如图7-1为其逻辑符号及引脚功能,它可用于波形的整形,也可作反相器或构成单稳态触发器和多谐振荡器。

图7-1 CD40106引脚排列(1)将正弦波转换为方波,如图7-2所示。

v iv ov i v O(a)(b)图7-2 正弦波转换为方波(2)构成多谐振荡器,如图7-3所示。

v o图7-3 多谐振荡器(3)构成单稳态触发器图7-4(a)为下降沿触发;图7-4(b)为上升沿触发。

v i vOV DDv i v OV SS(a)(b)图7-4 单稳态触发器三、实验设备与器件1、数字实验箱2、信号发生器3、示波器4、万用表5、CD40106 2CK15电位器、电阻、电容若干四、实验内容1、按图7-2接线,构成整形电路,输入信号可由信号发生器提供,图中串联的2K电阻起限流保护作用。

信号发生器输出信号:正弦信号、频率1KHZ,调节信号电压4V(Vpp)和7V(Vpp)。

用示波器CH1、CH2分别观察Vi和Vo 的波形,表在下表画出但输入信号为7V(Vpp)时Vi和Vo的波形。

(设置CH1:垂直灵敏度:2V 时间灵敏度:200us)(设置CH2:垂直灵敏度:2V 时间灵敏度:200us)2、为避免实验接线影响,先将信号发生器、示波器、芯片CD40106和实验箱所有接线去掉。

按图7-3接线,用示波器观测输出波形,测定振荡频率。

五、实验报告:总结单稳态触发器及施密特触发器的特点及其应用。

实验七--触发器

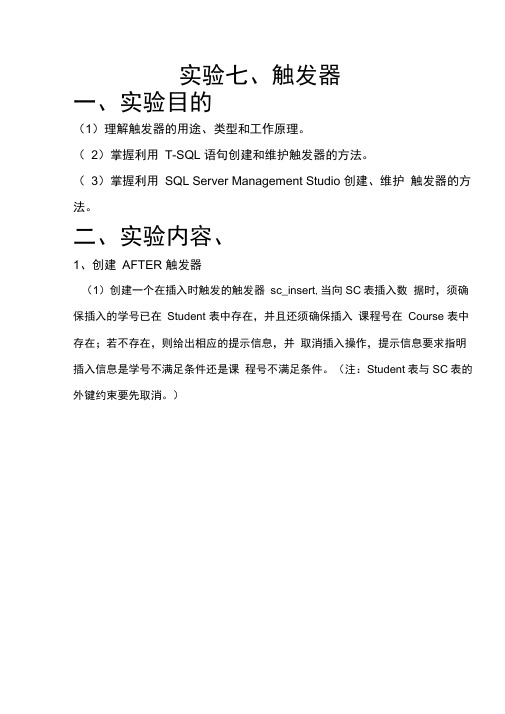

实验七、触发器一、实验目的(1)理解触发器的用途、类型和工作原理。

(2)掌握利用T-SQL 语句创建和维护触发器的方法。

(3)掌握利用SQL Server Management Studio 创建、维护触发器的方法。

二、实验内容、1、创建AFTER 触发器(1)创建一个在插入时触发的触发器sc_insert,当向SC表插入数据时,须确保插入的学号已在Student 表中存在,并且还须确保插入课程号在Course 表中存在;若不存在,则给出相应的提示信息,并取消插入操作,提示信息要求指明插入信息是学号不满足条件还是课程号不满足条件。

(注:Student表与SC表的外键约束要先取消。

)if exists (select name from sysobjects where name= ' ir.3ert R注二d type= *TR*) drap trigger sc_±nserE50crea匸隹trigger 3C_insercon scfor inser匸S3declare @sro varchar < 10 ^cno varcrzar 10:select ^snc-sno,@cno^cnofrom INSERTEDi3L XL T J皂5C 丄.已T J S'(select snofrom studentwhere @3no=snokeginpr^ 口匸L学号不存在!Trollback tranerd|—ELSE PRINT r0K'else if nci匸C!xz-Bt3 select enofrom coursewhere @cno=cnobeginrcllbaclr tran匚工二口匸,课程号不存在! 1endgo(2) 为Course表创建一个触发器Course_del,当删除了Course表中的一条课程信息时,同时将表SC中相应的学生选课记录也删除。

数电实验报告 触发器

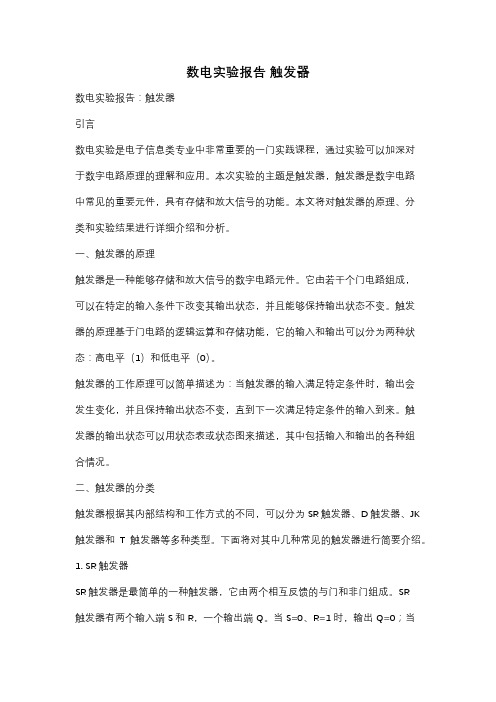

数电实验报告触发器数电实验报告:触发器引言数电实验是电子信息类专业中非常重要的一门实践课程,通过实验可以加深对于数字电路原理的理解和应用。

本次实验的主题是触发器,触发器是数字电路中常见的重要元件,具有存储和放大信号的功能。

本文将对触发器的原理、分类和实验结果进行详细介绍和分析。

一、触发器的原理触发器是一种能够存储和放大信号的数字电路元件。

它由若干个门电路组成,可以在特定的输入条件下改变其输出状态,并且能够保持输出状态不变。

触发器的原理基于门电路的逻辑运算和存储功能,它的输入和输出可以分为两种状态:高电平(1)和低电平(0)。

触发器的工作原理可以简单描述为:当触发器的输入满足特定条件时,输出会发生变化,并且保持输出状态不变,直到下一次满足特定条件的输入到来。

触发器的输出状态可以用状态表或状态图来描述,其中包括输入和输出的各种组合情况。

二、触发器的分类触发器根据其内部结构和工作方式的不同,可以分为SR触发器、D触发器、JK 触发器和T触发器等多种类型。

下面将对其中几种常见的触发器进行简要介绍。

1. SR触发器SR触发器是最简单的一种触发器,它由两个相互反馈的与门和非门组成。

SR触发器有两个输入端S和R,一个输出端Q。

当S=0、R=1时,输出Q=0;当S=1、R=0时,输出Q=1;当S=0、R=0时,输出状态保持不变;当S=1、R=1时,输出状态不确定。

2. D触发器D触发器是一种常用的触发器,它具有单一输入端D和输出端Q。

D触发器的输出状态与输入D的电平保持一致,即当D=0时,Q=0;当D=1时,Q=1。

D 触发器可以用于存储和传输数据,在时序电路中起到重要的作用。

3. JK触发器JK触发器是一种综合性能较好的触发器,它由两个输入端J和K、一个时钟端CLK和一个输出端Q组成。

JK触发器的输出状态可以由J、K和CLK的不同组合来控制,具体规律可以通过真值表或状态图来描述。

JK触发器在时序电路中常用于频率分频、计数等应用。

触发器及其应用的实验原理

触发器及其应用的实验原理实验目的本实验旨在通过实际操作与观察,学习和理解触发器的原理和应用。

通过实验,我们可以掌握触发器的工作原理、稳态和转态的概念,并能够灵活运用触发器解决实际问题。

实验器材1.74LS74触发器芯片 x 12.电路实验板 x 13.LED灯 x 24.电压源 x 15.连接线若干实验原理触发器是一种用于存储和放大数字信号的电子元件。

在数字电路中,触发器被广泛应用于时序电路和存储器等关键部分。

触发器可以根据输入信号的变化,在一定条件下产生稳态输出。

触发器的输出可以作为下一级触发器的输入,从而构成复杂的逻辑电路。

常见的触发器有RS触发器、D触发器、JK触发器和T触发器等。

本实验中,我们将使用74LS74触发器芯片,它是一种常见的双D触发器芯片。

触发器有两个稳态,分别是清零稳态(也称为复位稳态)和置位稳态(也称为设定稳态)。

其转态变化取决于输入信号的变化和特定的触发条件。

触发条件可以通过输入的极性选择和时钟脉冲确定。

实验步骤1.将74LS74触发器芯片插入电路实验板的指定位置。

2.将两个LED灯分别连接到触发器芯片的输出引脚,其中一个用于显示Q输出,另一个用于显示Q’输出。

3.连接电压源,将正极连接到芯片的Vcc引脚,将负极连接到芯片的地(GND)引脚。

4.使用连接线将触发器芯片的时钟脉冲引脚(CLK)连接到电路实验板上的一个按钮。

5.使用连接线将触发器芯片的复位引脚(CLR)连接到电路实验板上的另一个按钮。

6.分别使用连接线将两个D触发器的输入引脚(D)分别连接到电路实验板上的两个开关。

7.按下时钟按钮,观察LED灯的状态变化。

8.按下复位按钮,观察LED灯的状态是否恢复初始状态。

实验结果分析通过实验观察,我们可以得出以下结论: 1. 当输入信号D为高电平时,触发器芯片74LS74的Q输出为高电平,Q’输出为低电平。

2. 当输入信号D为低电平时,触发器芯片74LS74的Q输出为低电平,Q’输出为高电平。

触发器实验报告

触发器实验报告一、实验目的本次实验的主要目的是深入理解触发器的工作原理和功能,通过实际操作和观察,掌握触发器在数字电路中的应用,以及其对信号的存储和转换作用。

二、实验原理触发器是一种具有记忆功能的基本逻辑单元,能够在时钟脉冲的作用下存储二进制数据。

常见的触发器类型包括 D 触发器、JK 触发器和SR 触发器等。

D 触发器在时钟脉冲的上升沿(或下降沿)将输入的数据传送到输出端。

JK 触发器则根据输入的J、K 信号和时钟脉冲来改变输出状态。

SR 触发器则由置位(S)和复位(R)信号控制输出。

三、实验设备与材料1、数字电路实验箱2、示波器3、集成电路芯片(如 74LS74、74LS112 等)4、导线若干四、实验步骤1、 D 触发器实验将 74LS74 芯片插入实验箱的插槽中。

按照芯片引脚图连接电路,将 D 输入端连接到逻辑电平开关,时钟输入端连接到脉冲信号源,输出端 Q 和 Q'连接到发光二极管。

改变D 输入端的电平,观察在时钟脉冲作用下输出端的状态变化。

2、 JK 触发器实验插入 74LS112 芯片。

连接电路,将 J、K 输入端连接到逻辑电平开关,时钟输入端连接到脉冲信号源,输出端连接到发光二极管。

改变 J、K 输入端的电平组合,观察在时钟脉冲作用下输出端的状态变化。

3、 SR 触发器实验选取合适的 SR 触发器芯片,如 74LS279。

按照引脚图连接电路,将 S、R 输入端连接到逻辑电平开关,输出端连接到发光二极管。

改变 S、R 输入端的电平,观察输出端的状态变化。

五、实验结果与分析1、 D 触发器当 D 输入端为高电平时,在时钟脉冲的上升沿,输出端 Q 变为高电平,Q'变为低电平;当D 输入端为低电平时,在时钟脉冲的上升沿,输出端 Q 变为低电平,Q'变为高电平。

这表明 D 触发器能够在时钟脉冲的控制下,将输入的数据准确地传输到输出端。

2、 JK 触发器当 J=1,K=0 时,在时钟脉冲的作用下,输出端 Q 置位为高电平;当 J=0,K=1 时,输出端 Q 复位为低电平;当 J=K=0 时,输出端保持原状态不变;当 J=K=1 时,输出端在时钟脉冲作用下翻转。

触发器的认识和应用实验报告

触发器的认识和应用实验报告实验目的:1. 了解触发器的概念和工作原理;2. 掌握触发器的基本应用方法。

实验器材:1. 电路模拟软件;2. 电源模块;3. 电阻、电容、开关等元件。

实验原理:触发器是一种电子元件,用于存储和处理数字信号。

它可以改变输入信号的状态,并在特定条件下触发输出信号的改变。

常见的触发器有RS触发器、D触发器、JK触发器和T触发器等。

实验步骤:1. RS触发器实验:a. 连接RS触发器的RS输入端分别与两个开关和两个电阻相连;b. 连接RS触发器的输出端与LED灯;c. 设计不同的输入信号,观察输出信号的变化。

2. D触发器实验:a. 连接D触发器的D输入端与开关和电阻相连;b. 连接D触发器的时钟输入端和复位输入端;c. 连接D触发器的输出端与LED灯;d. 设计不同的输入信号和时钟信号,观察输出信号的变化。

3. JK触发器实验:a. 连接JK触发器的J、K输入端与开关和电阻相连;b. 连接JK触发器的时钟输入端和复位输入端;c. 连接JK触发器的输出端与LED灯;d. 设计不同的输入信号和时钟信号,观察输出信号的变化。

4. T触发器实验:a. 连接T触发器的T输入端与开关和电阻相连;b. 连接T触发器的时钟输入端和复位输入端;c. 连接T触发器的输出端与LED灯;d. 设计不同的输入信号和时钟信号,观察输出信号的变化。

实验结果:通过观察不同触发器的输入和输出信号,可以发现触发器具有存储和处理数字信号的功能。

不同触发器的输出信号在特定条件下发生变化,可以实现各种逻辑功能的实现。

实验结论:触发器是一种重要的数字电路元件,具有存储和处理信号的功能。

通过设计不同的输入信号和时钟信号,可以实现各种逻辑功能的实现。

在数字电路设计和逻辑控制方面,触发器是必不可少的元件之一。

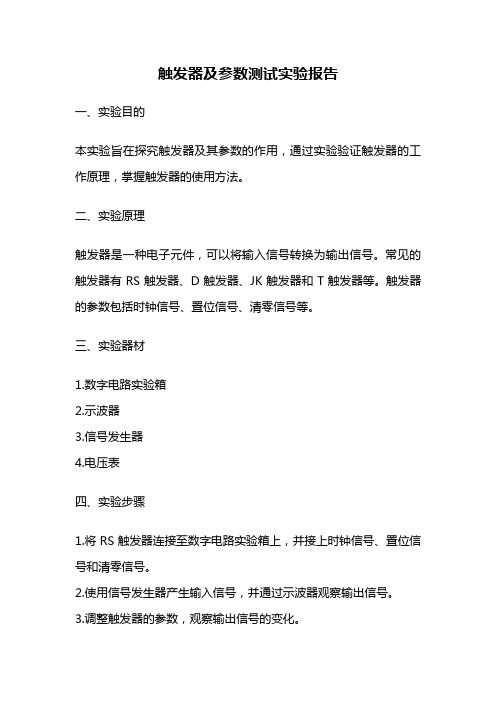

触发器及参数测试实验报告

触发器及参数测试实验报告

一、实验目的

本实验旨在探究触发器及其参数的作用,通过实验验证触发器的工作原理,掌握触发器的使用方法。

二、实验原理

触发器是一种电子元件,可以将输入信号转换为输出信号。

常见的触发器有RS触发器、D触发器、JK触发器和T触发器等。

触发器的参数包括时钟信号、置位信号、清零信号等。

三、实验器材

1.数字电路实验箱

2.示波器

3.信号发生器

4.电压表

四、实验步骤

1.将RS触发器连接至数字电路实验箱上,并接上时钟信号、置位信号和清零信号。

2.使用信号发生器产生输入信号,并通过示波器观察输出信号。

3.调整触发器的参数,观察输出信号的变化。

4.重复以上步骤,测试D触发器、JK触发器和T触发器的工作原理及参数作用。

五、实验结果

通过实验,我们发现不同类型的触发器具有不同的工作原理和参数作用。

例如,RS触发器可以通过置位信号和清零信号来控制输出信号的状态,而D触发器可以通过时钟信号来控制输出信号的状态。

同时,我们还发现触发器的参数设置不当会导致输出信号的错误。

六、实验结论

触发器是一种重要的电子元件,可以将输入信号转换为输出信号。

不同类型的触发器具有不同的工作原理和参数作用,需要根据实际需求进行选择和设置。

在使用触发器时,需要注意参数设置的正确性,以确保输出信号的准确性和稳定性。

七、实验总结

本实验通过实际操作,深入了解了触发器的工作原理和参数作用,掌握了触发器的使用方法。

同时,我们还发现实验过程中需要注意实验器材的正确连接和参数设置的正确性,以确保实验结果的准确性和可靠性。

触发器的逻辑功能测试实验报告

一、实验目的

1.掌握JK 触发器和T 触发器的逻辑功能。

2.熟悉触发器的应用。

二、 实验原理

上图为74LS112芯片,共有16根管脚,其中含有两个功能相同的JK 触发器。

芯片第16号管脚需要接+5V 直流电压源;8号管脚需要接地(GND )。

一号触发器:1号管脚为触发器的时钟信号输入端CP ;2、3号分别为触发器的信号输入端K 、J ;4号管脚为置位端SD (SET );15号管脚为复位端RD (RESET );5号管脚为输出端Q ;6号管脚为反相输出端Q 。

二号触发器:13号管脚为触发器的时钟信号输入端CP ;11、12号分别为触发器的信号输入端J 、K ;10号管脚为置位端SD (SET );14号管脚为复位端RD (RESET );9号管脚为输出端Q ;7号管脚为反相输出端Q 。

在仿真软件中,可找到相对应的芯片。

1

2

3

4

5

678

9

10

11

12

13

14VCC

GND

15

16

1CP 1K 1J 1SD

1Q 1Q 2J

2K

2Q

1RD 2CP

2Q

2SD 2RD 1

2

74LS112

3.观察T触发器输出波形

将JK触发器接成T触发器,接到逻辑开关,CP端输入方波信号,频率为1KHz,幅度为5V RMS,用示波器观察Q端波形。

示波器CH1接输出Q,CH2接方波信号。

逻辑表达式:

n+1n n Q=TQ+TQ

当逻辑开关分别为0和1时,示波器的波形分别为?为0时

为1时。

实验七触发器功能测试与仿真

现代电子技术

实验报告

实验名称:

指导老师:

学生班级:

学生:

学生学号:

实验七触发器功能测试与仿真

一、实验目的

1、熟悉和掌握各触发器在Multsim10软件中所处的位置。

2、熟悉和掌握各触发器的作用及功能,以及它们的测试及仿真。

3、进一步熟悉Multisim软件。

二、实验设备

安装有Multsim10软件的个人电脑

三、实验容

1、基本RS触发器逻辑功能测试与仿真

2.5 V 数据如下:

数据分析:

基本RS触发器的特性方程:

2、JK触发器逻辑功能测试与仿真

JK触发器的逻辑功能表:

JK触发器的特性方程:

实验结果分析:

3、T触发器逻辑功能测试与仿真

T触发器的逻辑功能表:

T触发器的特性方程:

Q n+1 =T n Q+T Q n =T⊕Q n

实验结果分析:

当T=0时,J=K=0,触发器保持不变;当T=1时,J=K=1,每来一个CP脉冲,触发器翻转一次,实现了T触发器的逻辑功能。

4、D触发器逻辑功能测试与仿真

+

D触发器的特性方程:

Q n+1=D

实验结果分析:

D触发器是利用维持线和阻塞线,将触发器的触发器翻转控制在CP上升沿瞬间,触发器的输出只与CP上升沿瞬间D的信号有关。

5、T’触发器逻辑功能测试与仿真

T’触发器的逻辑功能表:

T’触发器的特性方程:

Q

Q n+1=n

实验结果分析:。

实验七rs触发器和jk触发器

实验七 RS触发器和JK触发器一、实验目的1. 掌握RS触发器特性和设计方法;2. 掌握JK触发器特性和设计方法。

二、实验要求1. 上机前要作好充分准备,预习实验。

2. 实验完成后,写出详细实验报告。

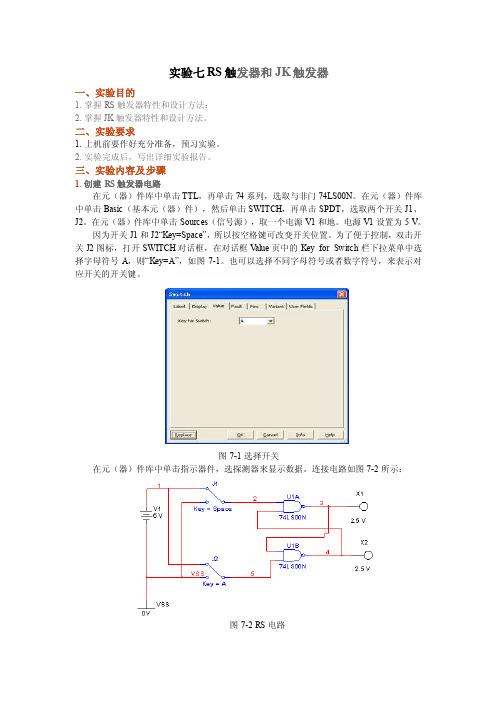

三、实验内容及步骤1. 创建RS触发器电路在元(器)件库中单击TTL,再单击74系列,选取与非门74LS00N。

在元(器)件库中单击Basic(基本元(器)件),然后单击SWITCH,再单击SPDT,选取两个开关J1、J2。

在元(器)件库中单击Sources(信号源),取一个电源V1和地。

电源V1设置为5 V。

因为开关J1和J2“Key=Space”,所以按空格键可改变开关位置。

为了便于控制,双击开关J2图标,打开SWITCH对话框,在对话框V alue页中的Key for Switch栏下拉菜单中选择字母符号A,则“Key=A”,如图7-1。

也可以选择不同字母符号或者数字符号,来表示对应开关的开关键。

图7-1 选择开关在元(器)件库中单击指示器件,选探测器来显示数据。

连接电路如图7-2所示:图7-2 RS电路2. 观测输出通过两个开关改变输入数据,按对应的开关的开关键符号,即可改变开关位置,从而改变输入数据,电源V1和地分别表示数据1和0。

探测器亮表示数据为“1”,探测器灭表示数据为“0”。

当触发器的输入R=0、S=1时,触发器的输出Q=0、=1。

只要不改变开关J6、J7的状态,RS触发器的输出和Q将保持不变。

取其他输入数据,即可列出RS触发器真值表。

RS触发器真值表如表7-1所示:表7-1 RS电路真值表3. 创建JK触发器电路JK触发器是数字电路触发器中的一种电路单元。

JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。

在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。

由JK触发器可以构成D触发器和T触发器。

在元(器)件库中单击TTL,再单击74系列,选中JK触发器7473N。

数电实验报告触发器

数电实验报告触发器触发器是数字电路中常用的一种元件,它可以存储和传输信息。

在数电实验中,触发器是一个非常重要的实验内容。

本文将介绍触发器的基本概念、工作原理以及实验过程中的一些注意事项。

一、触发器的基本概念触发器是一种能够在特定条件下改变输出状态的电路元件。

它可以存储一个比特的信息,并根据输入信号的变化来改变输出信号的状态。

触发器有很多种类,其中最常见的是D触发器、JK触发器和SR触发器。

二、触发器的工作原理触发器的工作原理可以用时序图来表示。

以D触发器为例,它有两个输入端(D和CLK)和两个输出端(Q和Q')。

当CLK信号上升沿到来时,D触发器会根据D端的输入信号来改变Q端的输出状态。

如果D端为高电平,那么Q端将保持高电平;如果D端为低电平,那么Q端将保持低电平。

三、实验过程中的注意事项在进行触发器实验时,需要注意以下几点:1. 选择合适的电源电压和电阻:触发器的工作电压范围一般在3V到15V之间,因此在实验中需要选择适当的电源电压。

此外,为了保证电路的稳定性,还需要选择合适的电阻值。

2. 连接正确的电路:触发器实验中,需要将触发器与其他元件(如开关、电源等)正确连接起来。

如果连接错误,可能会导致触发器无法正常工作。

3. 使用合适的测试仪器:在实验中,可以使用示波器、逻辑分析仪等测试仪器来观察触发器的输入输出信号波形。

这样可以更加直观地了解触发器的工作状态。

4. 注意触发器的时序关系:触发器的输出状态是根据输入信号的变化来决定的,因此在实验中需要注意触发器的时序关系。

例如,在D触发器实验中,需要在CLK信号上升沿到来之前,将正确的输入信号D输入到触发器中。

四、实验结果及分析在进行触发器实验后,可以通过观察示波器或逻辑分析仪上的波形图来分析触发器的工作状态。

根据波形图,可以判断触发器是否正常工作,并进一步分析其性能指标,如响应时间、稳定性等。

五、实验应用及展望触发器在数字电路中有广泛的应用。

数电实验报告_触发器

一、实验目的1. 理解触发器的概念和基本原理;2. 掌握触发器的逻辑功能和应用;3. 熟悉触发器电路的搭建和调试方法;4. 通过实验验证触发器的功能和应用。

二、实验原理触发器是一种具有记忆功能的电子电路,能够存储一个二进制信息。

它根据输入信号的变化,在一定的条件下可以改变其输出状态,从而实现数据的存储和传递。

触发器是数字电路中的基本单元,广泛应用于计数器、寄存器、存储器等数字系统中。

触发器主要分为两大类:电平触发器和边沿触发器。

电平触发器在输入信号保持一定电平期间,输出状态才会发生变化;而边沿触发器仅在输入信号的跳变沿处改变输出状态。

常见的触发器有RS触发器、D触发器、JK触发器和T触发器等。

以下分别介绍这些触发器的原理和逻辑功能。

1. RS触发器:由两个与非门交叉耦合而成,具有两个输入端(S、R)和两个输出端(Q、Q')。

当S=0,R=1时,触发器置1;当S=1,R=0时,触发器置0;当S=0,R=0时,触发器保持原状态;当S=1,R=1时,触发器处于不确定状态。

2. D触发器:由一个与非门和两个反相器组成,具有一个输入端(D)和两个输出端(Q、Q')。

当输入信号D变化时,触发器的输出状态随之变化,即D=1时,Q=1;D=0时,Q=0。

3. JK触发器:由两个与非门交叉耦合而成,具有两个输入端(J、K)和两个输出端(Q、Q')。

当J=K=0时,触发器保持原状态;当J=1,K=0时,触发器置1;当J=0,K=1时,触发器置0;当J=K=1时,触发器翻转。

4. T触发器:由一个与非门和两个反相器组成,具有一个输入端(T)和两个输出端(Q、Q')。

当T=1时,触发器翻转;当T=0时,触发器保持原状态。

三、实验内容及步骤1. 触发器电路搭建:根据实验原理,搭建RS触发器、D触发器、JK触发器和T触发器电路。

2. 触发器功能测试:通过改变输入信号,观察输出端Q的逻辑信号及其下一逻辑状态,验证触发器的逻辑功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验七、触发器

一、实验目的

(1)理解触发器的用途、类型和工作原理。

(2)掌握利用T-SQL语句创建和维护触发器的方法。

(3)掌握利用SQL Server Management Studio创建、维护触发器的方法。

二、实验内容、

1、创建AFTER触发器

(1)创建一个在插入时触发的触发器sc_insert,当向SC表插入数据时,须确保插入的学号已在Student表中存在,并且还须确保插入课程号在Course表中存在;若不存在,则给出相应的提示信息,并取消插入操作,提示信息要求指明插入信息是学号不满足条件还是课程号不满足条件。

(注:Student表与SC表的外键约束要先取消。

)

(2)为Course表创建一个触发器Course_del,当删除了Course表中的一条课程信息时,同时将表SC中相应的学生选课记录也删除。

(3)在Course表中添加一个平均成绩avg_modify,当SC表中某学

生的成绩发生变化时,则Course表中的平均成绩也能及时相应发生改变。

(4)测试上述三个触发器。

2、创建INSERTED OF 触发器

(1)创建一视图student_view,包含学号、姓名、课程号、课程名、成绩等属性,在student_view上创建一个触发器grade_modify,当对student_view中的学生的成绩进行修改时,实际修改的是SC中的相应记录。

(2)在Student表中插入一个getcredit字段(记录学生所获学分的情况),创建一个触发器ins_credit,当更改(注:含插入时)SC表中的学生成绩时,如果新成绩大于等于60分,则该生可获得这门课的学分,如果新成绩小于60分,则该生未能获得这门课的学分。

(3)测试上述两个触发器。

3、使用T-SQL语句管理和维护触发器

(1)用系统存储过程sp_helptrigger查看触发器grade_modify的相关信息。

(2)使用sp_helptext查看触发器grade_modify中的定义内容。

(3)使用select语句查看触发器grade_modify的定义内容。

(4)用系统存储过程sp_depends查看触发器grade_modify的相关性(即该触发器涉及哪些基本表)。

(5)将sc_insert触发器改为instead of触发器,实现的功能不变。

(6)将触发器sc_insert删除。

4、使用SQL Server Management Studio管理触发器

(1)在SQL Server Management Studio中重新创建刚删除的触发器sc_insert。

(2)查看触发器sc_insert的内容。

(3)删除触发器sc_insert。