EDA作业

EDA习题

第一章绪论作业1、EDA的英文全称是什么?EDA的中文含义是什么?答:EDA的英文全称是Electronic Design Automation;中文含义是电子设计自动化。

5、FPGA和CPLD各包含几个基本组成部分?答:FPGA和CPLD均包含三个部分:可编程逻辑单元阵列、可编程互连、可编程I/O单元。

CPLD内部的可编程逻辑单元以乘积项阵列为主,而FPGA内部采用LUT加寄存器结构。

6、FPGA和CPLD各有什么特点?二者在存储逻辑信息方面有什么区别?在实际使用中,在什么情况下选用CPLD?在什么情况下选用FPGA?答:特点:CPLD内部的可编程逻辑单元以乘积项阵列为主,触发器数量相对FPGA要少,规模和复杂度较低。

FPGA内部采用LUT加寄存器结构,触发器数量多,规模和复杂度较高。

在存储逻辑信息方面,CPLD主要采用PROM存储信息;FPGA主要采用SRAM存储信息。

在实际使用中,一般规模逻辑设计,以控制功能为主的情况下优先选用CPLD。

对于复杂逻辑设计,需要存储大量数据的情况下优先选用FPGA。

10、对于目标器件为FPGA/CPLD的VHDL设计,其工程设计包括几个主要步骤?每步的结果是什么?答:主要设计步骤:(1)设计输入:采用HDL语言、原理图、状态图等方式,结果为设计的源代码。

(2)逻辑综合:将RTL级描述转换为优化过的具有特定工艺的门级实现,产生网表文件。

(3)目标器件的布线/适配:将综合器产生的网表文件映射到目标器件中,产生最终的下载文件。

(4)目标器件的编程/下载,得到具有特定功能的电路。

(5)硬件仿真、测试,11、名称解释逻辑综合、逻辑适配、行为仿真、功能仿真、时序仿真答:逻辑综合:将RTL级描述转换为优化过的具有特定工艺的门级实现,即网表文件。

逻辑适配:将综合器产生的网表文件映射到目标器件中,产生最终的下载文件。

行为仿真:将源程序直接送到VHDL仿真器中所进行的仿真。

功能仿真:将综合后的网表文件送到VHDL仿真器中所进行的仿真。

福师20秋《EDA技术》在线作业一

(多选题)1: 按照处理的HDL语言类型,仿真器可以分为()。

A: Verilog HDL仿真器

B: VHDL HDL仿真器

C: 混合仿真器

正确答案: A,B,C

(多选题)2: 用PLD器件实现设计的优势有哪些()?

A: 周期短

B: 投入少

C: 风险小

D: 对于成熟的设计往往采用PLD

正确答案: A,B,C

(多选题)3: 目前常用的硬件描述语言为:()。

A: Verilog

B: VHDL

C: 和 VC

D: VB

正确答案: A,B

(多选题)4: 常用的综合工具有哪些()。

A: FPGA Express

B: FPGA compiler

C: Synplify Pro

正确答案: A,B,C

(多选题)5: 目前的EDA技术主要特点有哪些()。

A: 使用普及

B: 应用广泛

C: 工具多样

D: 软件功能强大

正确答案: A,B,C,D

(多选题)6: ASIC电路特点描述正确的是()。

A: 周期长

B: 投入高

C: 功耗低

D: 省面积

正确答案: A,B,C,D

(多选题)7: 下面哪些是专业提供PLD器件厂商()。

A: Xilinx

B: Altera

C: Lattice。

eda作业

eda一、如图1所示,电路为二级电压串联负反馈的放大电路,其中Vs为V AC/SOURCE,其属性设置为默许值。

三极管Q2N3904的模型参数为默许值。

试用EWB软件作如下的分析:(1)求直流工作点;(2)求无负反馈(即无电阻Rf)时的输入电阻、输出电阻、电压增益和上限截止频率;(3)当电阻Rf别离为6.2kΩ、15kΩ和30kΩ时的反馈深度,并总结反馈深度对放大电路性能的阻碍。

(25分)Re1300Rb420kRs 200Rf6.2kVcc12VdcCe210uCe110uR55kQ2Q2N3904Cb22.2uRb3300kVoutQ1Q2N3904Vs1Vac 0VdcCb12.2uVinRe2680Rb1300kCb32.2u Re3820Rc15.1kR2b20kRc25.1kIb=1.11uA, Ic=126.121uA, Uce=11.242;图二Ui=986.856mV, Ii=77.076uA, Uo=3.118V; Ri=Ui/Ii=986.856mV/77.076uA=12.8K。

Uo1=5.193V;Ro=(Uo1/Uo-1)*R5=3.4KA=Uo/Ui=3.118V/986.856mV=3.15;Af=2.462V/987.371mV=2.5Af=2.803V/987.371mV=2.8Af=2.947V/986.945mV=3反馈深度1+AF=A/Af;由上可得:Af减小二级电压串联负反馈:Ri=Ri/(1+Af);Ro=Ro*(1+Af);使的Ri减小Ro增大;二、设计题。

设计一个水温操纵系统。

(40分)大体要求:一升水由1kW的电炉加热,要求水温能够在必然范围内由人工设定,并能在环境温度降低时实现自动调整,以维持设定的温度大体不变。

达到的性能指标:①温度设定范围:40~90℃,最小区分度为1℃;②操纵精度:温度操纵的静态误差≤1℃;③用十进制数码显示实际水温;④能打印实测水温值;⑤具有通信能力,可接收其他数据设备发来的命令,或将结果传送到其他数据设备。

EDA实验课程大作业报告:设计制作一个用于十字路口的交通灯控制器

交通灯控制器设计一.系统功能设计要求设计制作一个用于十字路口的交通灯控制器,要求如下:(1)南北和东西方向各有一组红、绿、黄灯来指挥交通,持续时间分别为25S,20S,和5S。

(2)当有特殊情况(如消防车、救护车等)时,两个方向均为红灯亮,计时停止。

(3)当特殊情况结束后,控制器恢复原来状态,继续正常运行。

(4)用两组数码管,以倒计时方式显示两个方向允许通行或禁止通行的时间。

二.设计原理1.交通灯控制器的状态转换根据题目要求将将红绿灯的状态转换列成如下表:2.设计方案1)由于交通灯需要使用2位7段LED数码管指示通行剩余时间,故采用LED动态扫描方式显示当前时间。

频率设定CLK1k对应的频率为50MHZ。

2)控制模块是交通灯的核心,主要控制交通灯按工作顺序自动变换,同时控制倒计时模块工作,每当倒计时回零时,控制模块接收到一个计时信号,从而控制交通灯进入下一个工作状态。

3)每个方向有一组2位倒计时器模块,用以显示该方向交通灯剩余的点亮时间。

4)显示模块由两部分组成,一是由七段数码管组成的倒计时显示器,每个方向两个七段数码管;二是由发光二极管代替的交通灯,每个方向3个发光二极管。

三.变量符号说明其中,CLK1K为系统时钟信号输入端,SN为禁止通行信号输入通行信号输入端,light0为东西红灯信号输出端,light1为东西黄灯信号输出端,light2为东西绿灯信号输出端,light3为南北红灯信号输出端,light4为南北黄灯信号输出端,light5为南北绿灯信号输出端,led1、led2、led3、led4为数码管地址选择信号输出端。

四.代码说明library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity Hongld ISport (clk1k,SN:in std_logic; --SN紧急情况led1, led2, led3, led4 :out std_logic_vector (6 downto 0);--显示管显示时间用light:out std_logic_vector (5 downto 0)); --红绿黄灯end Hongld;architecture traffic1 of Hongld ISsignal S:std_logic_vector (1 downto 0); --状态signal DXT:std_logic_vector(7 downto 0):=X"01"; --东西方向时间signal NBX:std_logic_vector(7 downto 0):=X"01"; --南北方向时间signal ART,AGT,AYT,BRT,BGT,BYT: std_logic_vector(7 downto 0); --红绿黄灯信号signal temp: integer range 0 to 49999999; --产生1s计数器时计数signal clk: std_logic;beginART<="00100101";AGT<="00100000";AYT<="00000100";BRT<="00100101";BGT<="00100000";BYT<="00000100";process(clk1k) -- 选频率为50MHZ beginif (clk1k'event and clk1k='1') thenif temp=49999999 thentemp<=0;clk<='1';elsetemp<=temp+1;clk<='0';end if;end if;end process;process(clk,DXT,NBX) --状态转换进程beginif clk'event and clk ='1' thenif(DXT ="00000001")OR (NBX = "00000001") then S<=S+1;else S<=S;end if; --状态转换结束end if;end process;process (clk,SN,S) --倒计时模块beginif SN = '1' then DXT<=DXT; NBX<=NBX;elseif clk'event and clk='1' thenif (DXT="0000000") OR (NBX="00000000") thencase S ISwhen "00"=>DXT<=ART; NBX<=BGT; --南北红灯、东西绿灯when "01"=>NBX<=BYT; --南北红灯、东西黄灯when "10"=>DXT<=AGT; NBX<=BRT; --南北绿灯、东西红灯when "11"=>DXT<=AYT; --南北黄灯、东西红灯when others=>NULL;end case;end if;if DXT/="00000000" thenif DXT(3 downto 0)= "0000" thenDXT(3 downto 0)<="1001";DXT(7 downto 4)<=DXT(7 downto 4)-1;else DXT(3 downto 0)<=DXT(3 downto 0)-1;DXT(7 downto 4)<=DXT(7 downto 4);end if;end if;if NBX/="00000000" thenif NBX(3 downto 0)="0000" thenNBX(3 downto 0)<="1001";NBX(7 downto 4)<=NBX(7 downto 4)-1;else NBX(3 downto 0)<=NBX(3 downto 0)-1;NBX(7 downto 4)<=NBX(7 downto 4);end if;end if;end if;end if;end process; --倒计时模块结束process(DXT,NBX,S,SN) --显示模块begincase NBX(3 downto 0) iswhen "0000"=>led1<="1000000";when "0010"=>led1<="0100100"; when "0011"=>led1<="0110000"; when "0100"=>led1<="0011001"; when "0101"=>led1<="0010010"; when "0110"=>led1<="0000010"; when "0111"=>led1<="1111000"; when "1000"=>led1<="0000000"; when "1001"=>led1<="0010000"; when others=>led1<="1111111"; end case;case NBX(7 downto 4) iswhen "0000"=>led2<="1000000"; when "0001"=>led2<="1111001"; when "0010"=>led2<="0100100"; when "0011"=>led2<="0110000"; when "0100"=>led2<="0011001"; when "0101"=>led2<="0010010"; when "0110"=>led2<="0000010"; when "0111"=>led2<="1111000"; when "1000"=>led2<="0000000"; when "1001"=>led2<="0010000"; when others=>led2<="1111111"; end case;case DXT(3 downto 0) iswhen "0000"=>led3<="1000000"; when "0001"=>led3<="1111001"; when "0010"=>led3<="0100100"; when "0011"=>led3<="0110000"; when "0100"=>led3<="0011001"; when "0101"=>led3<="0010010"; when "0110"=>led3<="0000010"; when "0111"=>led3<="1111000"; when "1000"=>led3<="0000000"; when "1001"=>led3<="0010000"; when others=>led3<="1111111"; end case;case DXT(7 downto 4) iswhen "0000"=>led4<="1000000"; when "0001"=>led4<="1111001"; when "0010"=>led4<="0100100";when "0100"=>led4<="0011001";when "0101"=>led4<="0010010";when "0110"=>led4<="0000010";when "0111"=>led4<="1111000";when "1000"=>led4<="0000000";when "1001"=>led4<="0010000";when others=>led4<="1111111";end case;if SN ='1' then light<="001001";elsecase S ISwhen "00"=>light<="010001";when "01"=> light <="100001";when "10"=> light <="001010";when "11"=> light <="001100";when others=>NULL;end case;end if;end process;end traffic1;五.仿真波形图仿真时序波形图。

19春福师《EDA技术》在线作业二

(多选题)1: 综合有哪几种形式()。

A: RTLB: 逻辑综合C: 将逻辑门表示转换到版图表示标准解答:(多选题)2: 基于FPGA/CPLD器件的数字系统设计流程包括哪些阶段()。

A: 设计输入B: 综合C: 布局布线D: 仿真和编程标准解答:(多选题)3: 目前的EDA技术主要特点有哪些()。

A: 使用普及B: 应用广泛C: 工具多样D: 软件功能强大标准解答:(多选题)4: ASIC电路特点描述正确的是()。

A: 周期长B: 投入高C: 功耗低D: 省面积标准解答:(多选题)5: 下面哪些是专业提供第三方EDA软件工具的公司()。

A: CadenceB: MentorC: SynopsysD: Synplicity标准解答:(多选题)6: IP核一般分为哪几种()。

A: 硬核B: 固核C: 软核D: 以上全不对标准解答:(多选题)7: 衡量仿真器性能的重要指标有哪些()。

A: 仿真速度B: 仿真的准确性C: 仿真的易用性标准解答:(多选题)8: 按照处理的HDL语言类型,仿真器可以分为()。

A: Verilog HDL仿真器B: VHDL HDL仿真器C: 混合仿真器标准解答:(多选题)9: SPLD器件分为几类()。

A: PROMB: PLAC: PALD: GAL标准解答:(多选题)10: 常用的综合工具有哪些()。

A: FPGA ExpressB: FPGA compilerC: Synplify Pro标准解答:(判断题)11: 布局布线为将综合生成的电路逻辑网表映射到具体的目标器件中实现,并产生最终的可下载文件的过程。

A: 错误B: 正确标准解答:(判断题)12: 仿真器按对设计语言的不同处理方式分为两类:编译型仿真器和解释型仿真器。

A: 错误B: 正确标准解答:(判断题)13: 如果只需要在上电和系统错误时进行复位操作,采用异步复位方式比同步复位方式好。

A: 错误B: 正确标准解答:(判断题)14: Synplify是一种FPGA/CPLD的逻辑综合工具。

eda技术作业参考答案.doc

5-14library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity div is port(clk,RESET: in std_logic;outl,out2:out std_logic);end div;architecture div_16 of div issignal ent: std_logic_vector(3 downto 0);beginprocess(clk)beginif reset=T thencnt<=u OOOO n;elsif (clk'event and clk=T) then cnt<=cnt+T;end if;end process;outl<=T when cnt=15 else 'O';--不等out2<=cnt(3); -正负脉宽相等end div_16;5-11library ieee;use ieee.std_logic_l 164.all;entity s_machine is port(clk:in std_logic;din:in std_logic_vector( 1 downto 0); dout:out std_logic_vector( 1 downto 0));end s_machine;architecture a of s_machine istype state is (s0,sl,s2);signal current_state,next_state:state;beginprocess(din,curret_state) -次态译码器与输出译码器描述begincase current_state iswhen sO =>讦(din = "00") then next_state <= sO; doutv="00'';elsif (din = "01") then next_state <= s2; dout<=,,10,?;elsif (din = TO") then next_state <= s2; dout<=,,lF,;end if;when si =>if (din = “00") then next_state <= si; doutv="00''; elsif(din = "01") then next_state <= sO; doutv=''00"; elsif(din = TO") then next_state <= s2; dout<=,,10,?; end if;when s2 =>讦(din = "00") then next_state <= s2; doutv="00''; elsif(din = "01") then next_state <= si; doutv="00''; elsif(din = TO") then next_state <= sO; doutv=''00"; end if;end case;End process;process(clk) -状态寄存器描述beginif (clk?event and clk== '1') then current_state<=next_state;end if;End process;End a;5-10(1)entity h_sub isport (x, y: in BIT ;diff, sub_out: out bit);end h_sub; Architecture A of h_sub isbegindiff <= x xor y; sub_out <= not X and Y;end A;ENTITY F_SUB ISPORT(X, Y, SUB_IN: IN BIT;DIFF, SUB_OUT: OUT BIT);ENDF_SUB;ARCHITECTURE ART OF F_SUB ISCOMPONENT H_SUBPORT(X, Y: IN BIT;DIFF, SUB_OUT: OUT BIT);END COMPONENT;SIGNAL SI, S2, S3: BIT;BEGINUl: H_SUB PORT MAP (X=>X, Y=>Y, DIFF=>S1, SUB_OUT=>S2);U2 : H_SUB PORT MAP (X=>S1 , Y=>SUB_IN ,DIFF=>DIFF, SUB_OUT=>S3);SUB_OUT<=S2 OR S3;END ARCHITECTURE ART;⑵.entity f^sub isport ( x, y, sub_in: in bit;diff, sub_out: out bit);end f_sub;architecture func of 匚sub isbeginprocess(x, y, sub_in)variable con: bit_vector(l downto 0);variable com: bit_vector(2 downto 0);begincom:= x & y & sub_in;if (com = “000") then con := “00";elsif (com = "Oil") then con := "01";elsif (com 二"100") then con :二"10";elsif (com 二"101") then con := "00";elsif (com = T10") then con := “00";else con := T1";end if;diff <= con(l); sub_out <= con(0);end process;end func;⑶entity subtracter isport ( a, b : in bit_vector(7 dowto 0);sub_in : in bit;diff: out bit_vector(7 dowto 0); sub_out: out bit); end subtracter;architecture stru of subtracter iscomponent H_subport ( x, y, sub_in: in bit; diff, sub_out: out bit);end component; signal sub: bit_vector(8 downto 0); begingO: for I in 0 to 7 generateu_inst: H_subbport map(a(i), b(i),sub(i),diff(i), sub(i+l));end generate;sub(0) <= sub_in;sub_out <=sub(8);end stru;5-8library IEEE:use IEEE. Std _logic_ 1164.all:use IEEE. STD_LOGIC _UNSIGNED.all:entity seq_gen isport(CIK, RESET: in STD_LOGIC:Y0: out STD_LOGIC_vector(9 downto 0)):End seq_gen;Architecture rtl of seq_gen isSignal CNT: STD_LOGIC_VECTOR(3 downto 0);beginprocess(CLK, RESET)begin〜 ifRESET=,l,thenCNT v=''0000";Elsif CLK'event and CLK=T thenIfcnt="1001''thenCNTv=”000";elseCNT<=CNT +T;End if;End if;End process ;With CNT SelectY0<=,,000000000F, when ” 0000”,“0000000010” when " 0001”,“0000000100” when ” 0010”,“0000001000” when ” 0011”,“0000010000” when ” 0100”,^^0000100000^^ when ” 0101”,“0001000000” when ” 0110”,“0010000000” when ” 0111”,4<010*******,? when ” 1000”,T 000000000’' when others ;end rtl;5-7library IEEE;use IEEE.Std _logic_ 1164.all;use IEEE.std_logic_unsigned.al 1; entity counter isport(clk,rst,ml,m0:in std_logic;y:out std_logic_vector (4 downto 0));End counter;Architecture rtl of counter isSignal sei: std_logic_vector (1 downto 0);Signal per,ent: std_logic_vector (4 downto 0);beginsel<=ml&mO;With sei Selectperv=”1001(F when “0(F,"OOOll" when “01",,,0100r, when TO","00101" when others;process(reset,clk)beginif reset=T thencnt<=n00000n;elsif (clk'event and clk=r)thenif ent = pre thencnt<=H00000u;elsecnt<=cnt+T;end if;end if;end process;y<=cnt;end rtl;2-1判断下列标示符是否合法,如果有误指出原因:16#OFA#, 10#12F#, 8#7989#, 8#356#, 2#0101010#, 74HC245,\74HC574\, CLR/RESET, \IN, 4/SCLKX, DI00% 16#OFA#10#12F# 8#7989# 8#356# 2#0101010# 以上不合法,不能以数字开头和存在#符号。

EDA作业

EDA作业1.三人表决电路设计输入用拨码开关sw1-sw8输出用LED显示。

LED引脚定义(8bit LEDs)set_location_assignment PIN_AB20 -to led_down[0]set_location_assignment PIN_AD24 -to led_down[1]set_location_assignment PIN_AB23 -to led_down[2]set_location_assignment PIN_AB18 -to led_down[3]set_location_assignment PIN_Y21 –to led_down[4]set_location_assignment PIN_AD16 -to led_down[5]set_location_assignment PIN_U24 –to led_down[6]set_location_assignment PIN_T23 –to led_down[7]8位拨码开关定义(8bit Switch)set_location_assignment PIN_AA16 -to sw[0]set_location_assignment PIN_Y13 -to sw[1]set_location_assignment PIN_W10 -to sw[2]set_location_assignment PIN_V10 -to sw[3]set_location_assignment PIN_Y11 -to sw[4]set_location_assignment PIN_V13 -to sw[5]set_location_assignment PIN_V24 -to sw[6]set_location_assignment PIN_AB15 -to sw[7]实验5:分频器设计一:设计一个分频器,首先对系统时钟分频,形成2Hz的信号,然后依次点亮8个LED,形成流水灯。

19春福师《EDA技术》在线作业一

(多选题)1: 按照处理的HDL语言类型,仿真器可以分为()。

A: Verilog HDL仿真器B: VHDL HDL仿真器C: 混合仿真器标准解答:(多选题)2: 用PLD器件实现设计的优势有哪些()?A: 周期短B: 投入少C: 风险小D: 对于成熟的设计往往采用PLD标准解答:(多选题)3: 目前常用的硬件描述语言为:()。

A: VerilogB: VHDLC: 和 VCD: VB标准解答:(多选题)4: 常用的综合工具有哪些()。

A: FPGA ExpressB: FPGA compilerC: Synplify Pro标准解答:(多选题)5: 目前的EDA技术主要特点有哪些()。

A: 使用普及B: 应用广泛C: 工具多样D: 软件功能强大标准解答:(多选题)6: ASIC电路特点描述正确的是()。

A: 周期长B: 投入高C: 功耗低D: 省面积标准解答:(多选题)7: 下面哪些是专业提供PLD器件厂商()。

A: XilinxB: AlteraC: LatticeD: Micsoftware标准解答:(多选题)8: 常用的集成FPGA/CPLD开发工具有哪些()。

A: MAX+plus IIB: Quartus IIC: ISED: ispLEVER标准解答:(多选题)9: TOP-down设计一般分为哪几个层次()。

A: 系统级B: 功能级C: 门级D: 开关级标准解答:(多选题)10: 状态机常用的编码方式有()。

A: 顺序编码B: 格雷编码C: 约翰逊编码D: 一位热码标准解答:(判断题)11: 数字设计流程中的设计输入的表达方式一般有原理图方式和HDL文本方式两种。

A: 错误B: 正确标准解答:(判断题)12: IP核中的软核与生产工艺无关,不涉及物理实现,为后续设计留有很大空间。

A: 错误B: 正确标准解答:(判断题)13: 有限状态机可以认为是组合逻辑和寄存器逻辑的特殊组合。

EDA作业

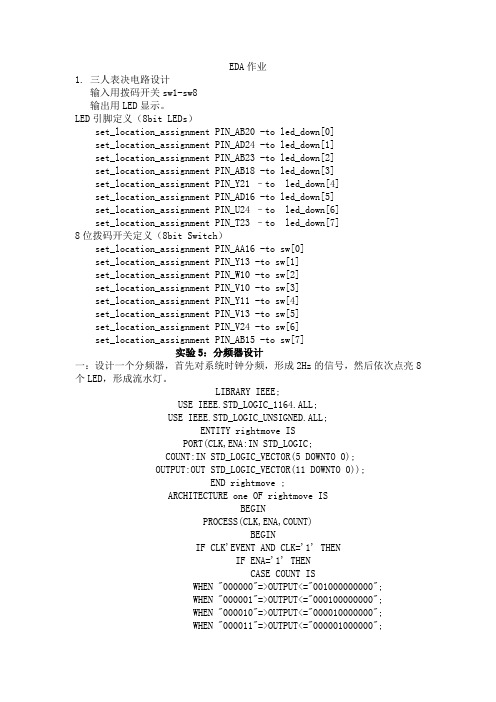

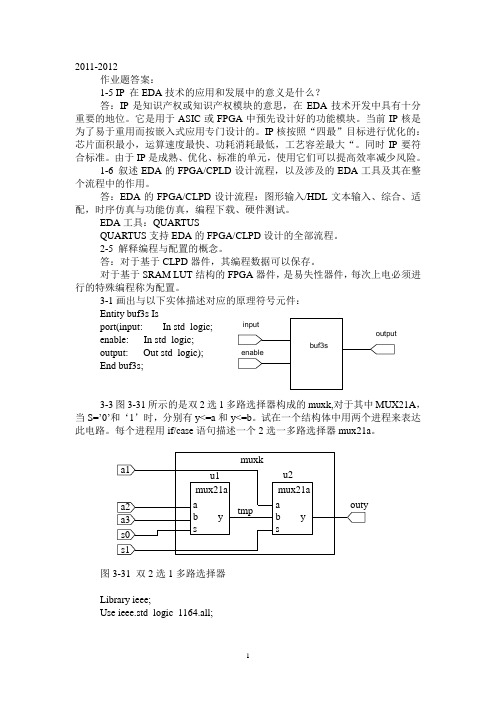

数字电路与逻辑设计(EDA)作业1.画出下例实体描述对应的原理图符号元件:ENTITY buf3s IS -- 实体1:三态缓冲器PORT (input : IN STD_LOGIC ; -- 输入端enable : IN STD_LOGIC ; -- 使能端output : OUT STD_LOGIC ) ; -- 输出端END buf3x ;ENTITY mux21 IS --实体2: 2选1多路选择器 PORT (in0, in1, sel : IN STD_LOGIC;output : OUT STD_LOGIC);END ENTITY mux22.图中所示的是4选1多路选择器,试分别用IF_THEN语句和CASE语句的表达方式写出此电路的VHDL程序。

选择控制的信号s1和s0为STD_LOGIC_VECTOR类型;当s1='0',s0='0';s1='0',s0='1';s1='1',s0='0'和s1='1',s0='1'分别执行y<=a、y<=b、y<=c、y<=d。

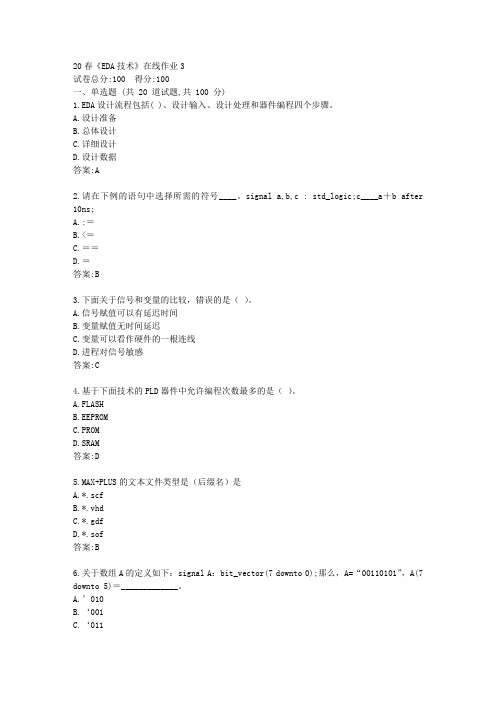

Library ieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entitymux4_1isport(s:instd_logic_vector(1 downto 0);a,b,c,d:instd_logic;y:out std_logic);endmux4_1;architecture arc of mux4_1issignal s1,s0:std_logic;begins1<=s(1);s0<=s(0);process(s1,s0)beginif(s1='0' and s0='0') then y<=a;elsif(s1='0' and s0='1') then y<=b;elsif(s1='1' and s0='0') then y<=c;elsif(s1='1' and s0='1') then y<=d;else null;end if;end process;end arc;libraryieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entitymux4_1isport(s:instd_logic_vector(1 downto 0);a,b,c,d:instd_logic;y:out std_logic);endmux4_1;architecture arc of mux4_1isbeginprocess(s)begincase s iswhen "00" => y<=a;when "01" => y<=b;when "10" => y<=c;when "11" => y<=d;when others => null;end case;end process;end arc;3.图中所示的是双2选1多路选择器构成的电路MUXK,对于其中MUX21A,当s='0'和'1'时,分别有y<='a'和y<='b'。

EDA作业二

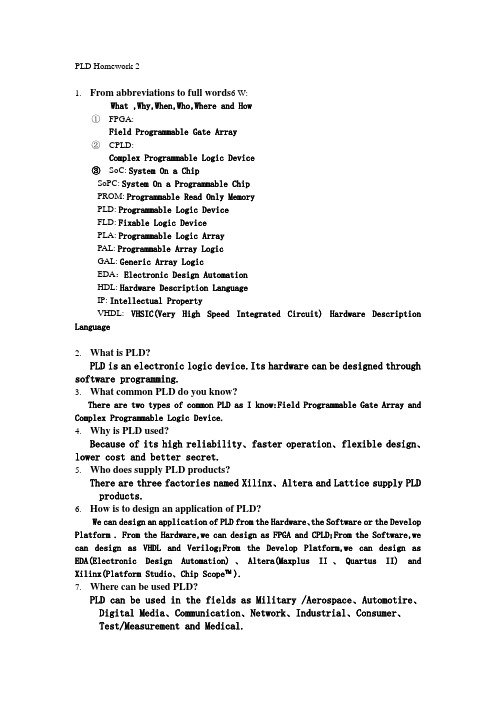

PLD Homework 21.From abbreviations to full words6 W:What ,Why,When,Who,Where and How①FPGA:Field Programmable Gate Array②CPLD:Complex Programmable Logic Device③SoC: System On a ChipSoPC: System On a Programmable ChipPROM: Programmable Read Only MemoryPLD: Programmable Logic DeviceFLD: Fixable Logic DevicePLA: Programmable Logic ArrayPAL: Programmable Array LogicGAL: Generic Array LogicEDA:Electronic Design AutomationHDL: Hardware Description LanguageIP: Intellectual PropertyVHDL: VHSIC(Very High Speed Integrated Circuit) Hardware Description Language2.What is PLD?PLD is an electronic logic device.Its hardware can be designed throughsoftware programming.3.What common PLD do you know?There are two types of common PLD as I know:Field Programmable Gate Array andComplex Programmable Logic Device.4.Why is PLD used?Because of its high reliability、faster operation、flexible design、lower cost and better secret.5.Who does supply PLD products?There are three factories named Xilinx、Altera and Lattice supply PLDproducts.6.How is to design an application of PLD?We can design an application of PLD from the Hardware、the Software or the Develop Platform . From the Hardware,we can design as FPGA and CPLD;From the Software,we can design as VHDL and Verilog;From the Develop Platform,we can design as EDA(Electronic Design Automation)、Altera(Maxplus II、Quartus II) and Xilinx(Platform Studio、Chip Scope™).7.Where can be used PLD?PLD can be used in the fields as Military /Aerospace、Automotire、Digital Media、Communication、Network、Industrial、Consumer、Test/Measurement and Medical.8.What is definition of FLD?FLD is an electronic logic device.Its logic circuit is fixable with one or one set function,can not be update after to be producted.9.What features of FLD do you know?As I know,FLD has the features as follows:Fixable Logic Circuit、Simple Desgin、Faster Operation、Lower cost for simple function、Inflexible solution and Less secret.10.What classification of PLD is known in integrated gates? Show some devices.PLD Can be divided into Simple PLD and Complex PLD. Simple PLD has PROM PLAPAL and GAL. Complex PLD has CPLD and FPGA.11.What classification of PLD is known in Programming?①Fuse Device②Autifuse Device③EPROM④EEPROM⑤SRAM⑥Flash12.What is definition of HDL?HDL is Handware Description Language.It is a software programming language to model some hardware.。

微波电路eda作业(1)

丁启程 No.20120291700091、编写微带线分析和综合程序,并计算:1)基片厚度0.127mm,相对介电常数2.2的50欧姆微带线的宽度;2)基片相对介电常数6.15的微带线,W/h在0.5-10.0之间变化时,特性阻抗Z0的曲线。

要求:1)程序流程图;2)程序代码及注释;3)运行结果解:微带线综合函数:流程图如图输入Z0,h,s判断Z0<44-s是,窄微带线否,宽微带线输出结果程序代码:function w=zonghe(z0,h,s)%z0 表示微带线的特性阻抗;h为基片厚度,相对介电常数sif z0<44-sd=59.95*pi^2/(z0*sqrt(s));r=2/pi*((d-1)-log(2*d-1))+(s-1)/(pi*s)*(log(d-1)+.293-0.517/s); Else%宽微带情况,w为微带宽度h1=z0*sqrt(2*(s+1))/119.9+.5*(s-1)/(s+1)*(log(pi/2)+log(4/pi)/s);%窄微带情况r=(exp(h1)/8-1/(s*exp(h1)))^(-1);endw=r*h;运行结果:输入:w=zonghe(50,.127,2.2)输出:w=0.4954微带线分析函数:流程图如下:输入r,s计算介质的特性阻抗计算有效介电常数计算微带线特性阻抗输出结果程序代码:function Z=analyze(r,s)% r=w/h;%宽高比%计算无色散微带均匀媒质微带线阻抗f=6+(2*pi-6)*exp(-(30.666./r).^0.7528);z01=376.73/(2*pi)*log(f./r+sqrt(1+(2./r).^2));%计算有效介电常数ea=1+1/49*log((r.^4+(r/52).^2)./(r.^4+.432))+log(1+(r/18.1).^3)/18.7; b=.564*((s-0.9)/(s+3))^053;s1=(s+1)/2+(s-1)/2*(1+10./r).^(a*b);%计算微带的特性阻抗z0=z01./sqrt(s1);Z=z0;调用程序:clc;clear all;closer=0.5:0.05:10;s=6.15;y=analyze(r,s);plot(r,y)xlabel('w/h')ylabel('Z0')运行结果:2、设一晶体管的S11和S22的测试值分别为:试用单向化等效电路模型分别求出其输入和输出等效电路(要求在6GHz处精确匹配,测试系统的特性阻抗为50Ω)。

EDA作业1-秒表

EDA作业一--秒表循环一、设计任务及要求1. 设计数码管显示的秒表。

2. 能够准确的计时并显示。

3. 开机显示00.00.00。

4. 用户可以随时清零、暂停、计时。

5. 最大记时59.59.99分钟,最小精确到0.01秒。

二、设计总体框图秒表计时器常常用于体育竞赛及各种其他要求有较精确时间的各领域中。

其中启/停开关的使用方法与传统的机械计时器相同,即按一下启/停开关,启动计时器开始计时,再按一下启/停开关计时终止。

而复位开关可以在任何情况下使用,即使在计时过程中,只要按一下复位开关,计时应立即终止,并对计时器清零。

具体框图见附录一。

三、硬件电路设计与程序设计本设计采用模块化设计,共分为顶层文件、控制毫秒模块(msecond)、控制秒模块(second)、控制分钟模块(minute)、LED模块(alert)、数码管扫描模块(zhishi)、分频器模块(fenpin)六个模块。

其中LED模块可以去掉,不影响秒表正常运行以下对各个模块一一描述。

1、分频器模块系统的输入时钟为4100HZ,用来驱动显示电路;同时输入时钟通过41分频,可以产生100HZ的频率来驱动计数电路,即为0.01秒,程序见附录二。

2.控制毫秒模块对这个功能模块用一个进程语句描述。

clk、reset和调秒的setsec(暂停\启动)为输入信号程序见附录二。

3.控制秒模块程序见附录二4.控制分模块程序见附录二5.数码管模块该模块的功能是选择个计数端口来的数据,当相应的数据到来时数据选择器选择器数据后输出给数码管,并由数码管显示。

程序见附录二四、编译仿真下面使用Quartus II对本设计进行编译和仿真。

首先创建工程,使用文本编辑器输入本设计的所有模块的源程序,把G-1DE.vhd设为顶层文件。

把本设计中的所有设计文件添加进工程后,先对每个模块进行编译纠错,然后把各个模块连接在一起保存然后在全程编译,通过之后就可以进行仿真。

先进行软件仿真每一部分的仿真从略,下面只说明系统的整体仿真波形。

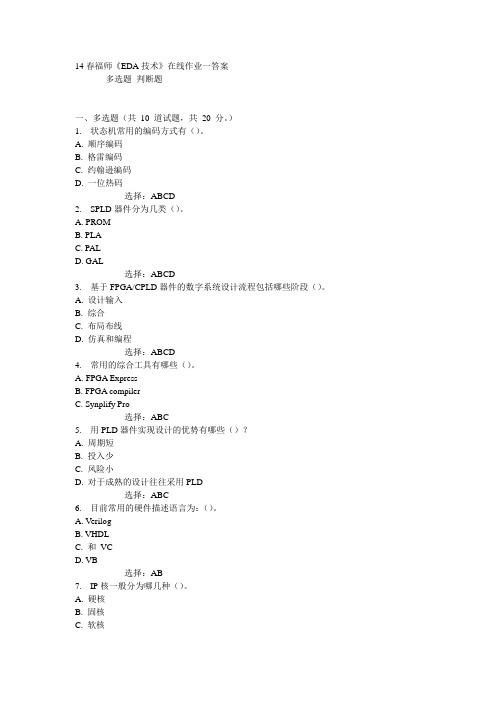

14春福师《EDA技术》在线作业一答案

14春福师《EDA技术》在线作业一答案

多选题判断题

一、多选题(共10 道试题,共20 分。

)

1. 状态机常用的编码方式有()。

A. 顺序编码

B. 格雷编码

C. 约翰逊编码

D. 一位热码

-----------------选择:ABCD

2. SPLD器件分为几类()。

A. PROM

B. PLA

C. PAL

D. GAL

-----------------选择:ABCD

3. 基于FPGA/CPLD器件的数字系统设计流程包括哪些阶段()。

A. 设计输入

B. 综合

C. 布局布线

D. 仿真和编程

-----------------选择:ABCD

4. 常用的综合工具有哪些()。

A. FPGA Express

B. FPGA compiler

C. Synplify Pro

-----------------选择:ABC

5. 用PLD器件实现设计的优势有哪些()?

A. 周期短

B. 投入少

C. 风险小

D. 对于成熟的设计往往采用PLD

-----------------选择:ABC

6. 目前常用的硬件描述语言为:()。

A. Verilog

B. VHDL

C. 和VC

D. VB

-----------------选择:AB

7. IP核一般分为哪几种()。

A. 硬核

B. 固核

C. 软核。

EDA应用大作业《串行通信》

四川工程职业技术学院电子信息工程09-1班《EDA应用》大作业串行通信第3组:杨国勋、李开宏、彭国明2011.10目录一、设计任务 (1)二、硬件设计 (1)1、硬件电路图 (1)2、整体模块 (2)三、软件设计 (2)1、主程序模块 (2)2、发送模块 (5)3、接收模块 (7)四、实验结果 (9)五、开发工具 (10)1、硬件 (10)2、软件 (10)六、项目总结 (10)1、遇到的问题 (10)2、解决的办法 (10)七、参考文献 (10)一、设计任务综合运用所学基本知识,通过在FPGA开发板子完成与计算机进行RS232串口通信,计算机上的软件可以使用串口通信调试软件进行数据发送或接收数据。

根据设计要求,应把系统分成4个模块来完成,这四个模块分别是:时钟模块(向系统各部分提供各种频率的时钟信号)收发模块(进行串行通信的发送和接收)显示模块(显示通信的数据格式)控制模块(控制系统的工作)二、硬件设计1、硬件电路图2、整体模块三、软件设计1、主程序模块module uart_test(clock,key,rdata,wen,sdata,seg,dig);input clock; //系统时钟(48MHz) input[2:0] key; //按键输入(KEY1~KEY3) input[7:0]rdata; //接收到的数据output wen; //发送数据使能output[7:0]sdata; //要发送的数据output[7:0]seg; //数码管段码输出output[7:0]dig; //数码管位码输出//I/O寄存器reg[7:0]sdata;reg[7:0]seg;reg[7:0]dig;//内部寄存器reg[16:0]count; //时钟分频计数器reg[2:0]dout1,dout2,dout3,buff; //消抖寄存器reg[1:0] cnt; //数码管扫描计数器reg[3:0]disp_dat; //数码管扫描显存reg div_clk; //分频时钟wire[2:0]key_edge; //按键消抖输出//时钟分频部分always @(posedge clock)beginif (count < 17'd120000)begincount <= count + 1'b1;div_clk <= 1'b0;endelsebegincount <= 17'd0;div_clk <= 1'b1;endend//按键消抖部分always @(posedge clock)beginif(div_clk)begindout1 <= key;dout2 <= dout1;dout3 <= dout2;endend//按键边沿检测部分always @(posedge clock)beginbuff <= dout1 | dout2 | dout3;endassign key_edge = ~(dout1 | dout2 | dout3) & buff;//2位16进制数输出部分always @(posedge clock) //按键1 beginif(key_edge[0])sdata[7:4] <= sdata[7:4] + 1'b1;endalways @(posedge clock) //按键2beginif(key_edge[1])sdata[3:0] <= sdata[3:0] + 1'b1;endassign wen = key_edge[2]; //按键3//数码管扫描显示部分always @(posedge clock) //定义上升沿触发进程beginif(div_clk)cnt <= cnt + 1'b1;endalways @(posedge clock)beginif(div_clk)begincase(cnt) //选择扫描显示数据2'd0:disp_dat = sdata[7:4]; //第一个数码管2'd1:disp_dat = sdata[3:0]; //第二个数码管2'd2:disp_dat = rdata[7:4]; //第七个数码管2'd3:disp_dat = rdata[3:0]; //第八个数码管endcasecase(cnt) //选择数码管显示位2'd0:dig = 8'b01111111; //选择第一个数码管显示2'd1:dig = 8'b10111111; //选择第二个数码管显示2'd2:dig = 8'b11111101; //选择第七个数码管显示2'd3:dig = 8'b11111110; //选择第八个数码管显示endcaseendendalways @(disp_dat)begincase(disp_dat) //七段译码4'h0:seg = 8'hc0; //显示04'h1:seg = 8'hf9; //显示14'h2:seg = 8'ha4; //显示24'h3:seg = 8'hb0; //显示34'h4:seg = 8'h99; //显示44'h5:seg = 8'h92; //显示54'h6:seg = 8'h82; //显示64'h7:seg = 8'hf8; //显示74'h8:seg = 8'h80; //显示84'h9:seg = 8'h90; //显示94'ha:seg = 8'h88; //显示a4'hb:seg = 8'h83; //显示b4'hc:seg = 8'hc6; //显示c4'hd:seg = 8'ha1; //显示d4'he:seg = 8'h86; //显示e4'hf:seg = 8'h8e; //显示f endcaseendendmodule2、发送模块module send(clk,clkout,Datain,TXD,TI,WR);input WR;input [7:0]Datain; //发送的一字节数据input clk;output clkout;output TXD,TI; //串行数据,发送中断reg[9:0]Datainbuf,Datainbuf2; //发送数据缓存reg WR_ctr,TI,txd_reg;reg [3:0]bincnt; //发送数据计数器reg [15:0] cnt;wire clk_equ;parameter cout = 5000;/*************波特率发生进程****************************/ always@(posedge clk)beginif(clk_equ)cnt = 16'd0;elsecnt=cnt+1'b1;endassign clk_equ = (cnt == cout);assign clkout = clk_equ;/*************读数据到缓存进程****************************/ always@(posedge clk)beginif(WR)beginDatainbuf={1'b1,Datain[7:0],1'b0};//读入数据,并把缓存组成一帧数据,10位WR_ctr = 1'b1; //置开始标志位endelse if(TI==0)WR_ctr = 1'b0;end/*************主程序进程****************************/ always@(posedge clk)beginif(clk_equ)beginif(WR_ctr==1||bincnt<4'd10) //发送条件判断,保证发送数据的完整性beginif(bincnt<4'd10)begintxd_reg = Datainbuf2[0]; //从最低位开始发送Datainbuf2 = Datainbuf>>bincnt; //移位输出bincnt = bincnt+4'd1; //发送数据位计数TI = 1'b0;endelsebincnt = 4'd0;endelsebegin //发送完毕或者处于等待状态时TXD和TI为高txd_reg = 1'b1;TI = 1'b1;endendendassign TXD = txd_reg; //TXD连续输出endmodule3、接收模块module rec(clk,clkout,Dataout,RXD,RI);input clk,RXD;output clkout,RI;output [7:0] Dataout; //并行数据输出reg StartF,RI;reg [9:0] UartBuff; //接收缓存区reg [3:0]count,count_bit;reg [15:0] cnt;reg [2:0]bit_collect; //采集数据缓存区wire clk_equ,bit1,bit2,bit3,bit;parameter cout = 312;//时钟是48M所以16*9600的分频数为312.5,这里取整数/*************波特率发生进程****************************/ always@(posedge clk)beginif(clk_equ)cnt = 16'd0;elsecnt=cnt+1'b1;endassign clk_equ = (cnt == cout);assign clkout = clk_equ;assign bit1 = bit_collect[0]&bit_collect[1]; assign bit2 = bit_collect[1]&bit_collect[2]; assign bit3 = bit_collect[0]&bit_collect[2]; assign bit = bit1|bit2|bit3;always@(posedge clk)beginif(clk_equ)beginif(!StartF) //是否处于接收状态beginif(!RXD)begincount = 4'b0; //复位计数器count_bit = 4'b0;RI = 1'b0;StartF = 1'b1;endelse RI = 1'b1;endelsebegincount = count+1'b1; //位接收状态加1if(count==4'd6)bit_collect[0] = RXD; //数据采集if(count==4'd7)bit_collect[1] = RXD; //数据采集if(count==4'd8)beginbit_collect[2] = RXD; //数据采集UartBuff[count_bit] = bit;count_bit = count_bit+1'b1;//位计数器加1if((count_bit==4'd1)&&(UartBuff[0]==1'b1))//判断开始位是否为0beginStartF = 1'b0; //标志开始接收endRI = 1'b0; //中断标志位低endif(count_bit>4'd9) //检测是否接收结束beginRI = 1'b1; //中断标志为高标志转换结束StartF = 1'b0;endendendendassign Dataout = UartBuff[8:1]; //取出数据位endmodule四、实验结果(1) 在工作状态下,若用户按下K1按键,则数码管1上的数字加 1(0~F循环);(2) 在工作状态下,若用户按下K2按键,则数码管2上的数字加 1(0~F循环);(3) 在工作状态下,若用户按下K3按键,则把数码管1和2上的数字通过串口发送到串口调试软件的接收窗口;(4) 在工作状态下,若用户通过串口调试软件在发送窗口发送数字,则在数码管7和8上显示相应的数字。

电子科大20新上《EDA技术》在线作业3_

(单选题)1: 下面哪种语句不是并行语句

A: wait语句

B: process语句

C: 块语句

D: 生成语句

正确答案: A

(单选题)2: VHDL程序基本结构包括

A: 实体、子程序、配置

B: 实体、结构体、配置、函数

C: 结构体、状态机、程序包和库

D: 实体、结构体、程序包和库

正确答案: D

(单选题)3: 仿真是对电路设计的一种()检测方法。

A: 直接的

B: 间接的

C: 同步的

D: 异步的

正确答案: B

(单选题)4: 常用的硬件描述语言有

A: VHDL、Verilog、c语言

B: ABEL、c++

C: VHDL、Verilog、ABEL

D: 汇编语言、ABEL、VHDL

正确答案: C

(单选题)5: 在VHDL中,用语句( )表示检测clock的上升沿。

A: clock'EVENT

B: clock'EVENT AND clock='1'

C: Clok='0'

D: clock'EVENT AND clock='0'

正确答案: B

(单选题)6: VHDL常用的库是

A: IEEE

B: STD

C: WORK

D: PACKAGE

正确答案: A

(单选题)7: 一般把EDA技术的发展分为CAD、CAE和()三个阶段。

A: CAM。

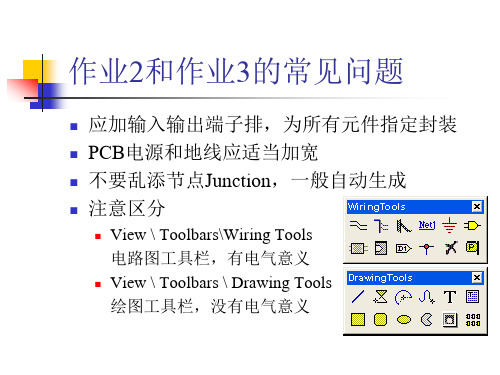

EDA作业2和作业3的常见问题

2)装入元件封装库Add / Remove

3) PCB环境设置:Design \ Options,Tools \ Preferences

绘制PCB的设计步骤

4)装入网络表Design / Load Nets,*.NET

若有错,回到原理图.SCH,修改后重新生成网络表,再装入 Design \ Rules,单击Placement页——默认 自动布局:Tools \ Auto Placement \ Auto Placer 手工布局:①移动把焊盘放到栅格上;②旋转或翻转;③按 下键盘上的g键调整栅格;④手工调整板框的尺寸Edit / Move / Drag,删除尺寸标注,选择Mechanical4,放置尺寸标注 Desginator中的文本习惯朝上或朝左 Part值最好放在元器件中

绘制原图的设计步骤

1)在Windows下新建一文件夹 2)创建一个新的设计数据库

启动Protel 99 SE系统进入设计环境 File\New,更改数据库文件名.ddb,改变数据库文件保存目录 File\New,选中Document Folder,新建文件夹SCH、PCB File\New,选中Schematic Document,更改文件名.sch,双击该 图标,进入设计环境 Design / Options:更改图纸尺寸设置,默认B→A4

9)其他操作

10)存盘打印

绘制PCB的设计步骤

1)向导生成电路板,规划电路板和电气定义

File\New,选择Wizards,双击Printed Circuit Board Wizard图标 设定板卡的Width、Height、四个切角的大小、安装孔 设置板卡的一些相关的产品信息 设置最小的导线尺寸、过孔直径和导线间的安全距离 路径:C:\Program Files \ Design Explorer99 SE \ Library \ PCB 默认元件封装库:\Generic FootPrints\Advpcb.ddb\PCB Footprints.lib 装载端子排元件封装库:\ Connectors 表贴元件封装库:\ IPC Footprints

eda作业题答案

2011-2012作业题答案:1-5 IP 在EDA技术的应用和发展中的意义是什么?答:IP是知识产权或知识产权模块的意思,在EDA技术开发中具有十分重要的地位。

它是用于ASIC或FPGA中预先设计好的功能模块。

当前IP核是为了易于重用而按嵌入式应用专门设计的。

IP核按照“四最”目标进行优化的:芯片面积最小,运算速度最快、功耗消耗最低,工艺容差最大“。

同时IP要符合标准。

由于IP是成熟、优化、标准的单元,使用它们可以提高效率减少风险。

1-6 叙述EDA的FPGA/CPLD设计流程,以及涉及的EDA工具及其在整个流程中的作用。

答:EDA的FPGA/CLPD设计流程:图形输入/HDL文本输入、综合、适配,时序仿真与功能仿真,编程下载、硬件测试。

EDA工具:QUARTUS当Entity muxk1 Isport(a1,a2,a3,s0,s1: In std_logic;outy: Out std_logic); End muxk1;Architecture abmux Of muxk1 IsSignal tmp: std_logic;Beginp1: process (a2,a3,s0)BeginCase s0 isWhen …0‟ => tmp <= a2;When …1‟ => tmp <= a3;When others => Null;End Case;End process;p2: Process (a1,tmp,s1)BeginCase s1 isWhen …0‟ => outy <= a1;When …1‟ => outy <= tmp;When others => Null;End Case;End Process;End abmux;Library ieee;Use ieee.std_logic_1164.all;Entity muxk isPort(a1,a2,a3,s0,s1: In Std_logic;outy: Out Std_logic); End muxk;Architecture abmux Of muxk isSignal tmp: Std_logic;Beginp1: Process (a2,a3,s0)BeginIf s0='1' Thentmp <= a2;Elsetmp <= a3;End If;End Process;p2: Process (a1,tmp,s1)BeginIf s1='1' Thenouty <= a1;Elseouty<= tmp;End if;End Process;End abmux;3-12 分别给出图3-20所示的6个RTL图的VHDL 描述,注意其中的D 触发器和锁存器的表述。

电科21春《EDA技术》在线作业3【标准答案】

20春《EDA技术》在线作业3

试卷总分:100 得分:100

一、单选题 (共 20 道试题,共 100 分)

1.EDA设计流程包括( )、设计输入、设计处理和器件编程四个步骤。

A.设计准备

B.总体设计

C.详细设计

D.设计数据

答案:A

2.请在下例的语句中选择所需的符号____。

signal a,b,c : std_logic;c____a+b after 10ns;

A.:=

B.<=

C.==

D.=

答案:B

3.下面关于信号和变量的比较,错误的是()。

A.信号赋值可以有延迟时间

B.变量赋值无时间延迟

C.变量可以看作硬件的一根连线

D.进程对信号敏感

答案:C

4.基于下面技术的PLD器件中允许编程次数最多的是()。

A.FLASH

B.EEPROM

C.PROM

D.SRAM

答案:D

5.MAX+PLUS的文本文件类型是(后缀名)是

A.*.scf

B.*.vhd

C.*.gdf

D.*.sof

答案:B

6.关于数组A的定义如下:signal A:bit_vector(7 downto 0);那么,A=“00110101”,A(7 downto 5)=_____________。

A.’010

B.‘001

C.‘011。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.简单PLD器件包括哪几种类型的器件?他们之间有什么相同点和

不同点?

答:PLD器件一般可分为4种:PROM、PLA、PAL、GAL器件

相同点:

简单PLD的典型结构是由与非门阵列、或门阵列组成,能够以“积之和”

的形式实现布尔逻辑函数,因为其任意一个组合逻辑都可以用“与或”表达式来描述,所以能够完成大量的组合逻辑功能,并且具有较高的速度和较好的性能。

不同点:

PROM:(1)与阵列固定,或阵列可编程

(2)当输入的数目太大时,器件功耗增加,巨大阵列开关时间也会导

致其速度缓慢,但其价格低,易于编程,没有布局、布线问题,性能

完全可以预测。

PLA:(1)与阵列和或阵列都可编程

(2)由于与阵列可编程,使得PROM中由于输入增加而导致规模增加的问题不复存在,从而有效地提高芯片的利用率,其用于含有复杂的随

机逻辑值换的场合是较为理想,但其慢速特性和相对高的价格妨碍了

它被广泛使用。

PAL:(1)或阵列固定,与阵列可编程

(2)与阵列可编程特性使输入项可以增多,而固定的或阵列又使器件得以简化。

在这种结构中,每个输出是若干乘积项之和,乘积项数目有

时固定的。

其结构对于大多数逻辑函数是有效的,同时此结构也提供

了较高的性能和速度,一度成为PLD发展史的主流。

GAL:其吸收先进的浮栅技术,并与CMOS的静态RAM结合,成了E2PROM 技术,从而使GAL具有了可电擦写、可重复编程、可设置加密功能。

GAL的输出可由用户来定义,他的每个输出端都集成着一个可编程的

输出逻辑宏单元。

2.Altera公司MAX7000系列CPLD有什么特点?

MAX7000系列是高密度、高性能的CMOS CPLD,采用先进的0.8umCMOS EEPROM技术制造,它提供600~5000可用门,引线端子到引线端子的延时为6ns,计数器频率可达151.5MHz,它主要有逻辑阵列块、宏单元、扩展乘积项、可编程连线阵列和I/O控制模块组成。