三位二进制减法计数器课程设计综述

三位二进制减法计数器设计审批稿

三位二进制减法计数器设计YKK standardization office【 YKK5AB- YKK08- YKK2C- YKK18】目录1课程设计的目的与作用1.了解同步计数器,序列信号发生器和N进制计数器工作原理;2.掌握计数器电路的分析,设计方法及应用;3.掌握序列信号发生器的分析,设计方法及应用;4.掌握N进制计数器的分析,设计方法及应用;5.学会正确使用JK触发器。

2 设计任务、及所用multisim软件环境介绍设计任务减法计数器1. 设计一个循环型3位2进制减法计数器,其中无效状态为(001,110)。

2. 根据同步计数器原理设计减法器的电路图。

3. 根据电路原理图使用Multisim进行仿真。

4. 将电路图进行实际接线操作。

5. 检查无误后,测试其功能。

1.2.2串行序列信号发生器1.设计一个序列信号发生器,其中信号序列为(101100)。

2.根据序列发生器原理设计发生器的原理图。

3.根据电路原理图使用Multisim进行仿真。

24进制计数器1. 用集成芯片设计一个24进制计数器2. 根据设计原理设计计数器原理图3. 根据电路原理图使用Mltisim仿真multisim软件环境介绍第一节 Multisim概貌软件以图形界面为主,采用菜单、工具栏和热键相结合的方式,具有一般Windows应用软件的界面风格,用户可以根据自己的习惯和熟悉程度自如使用。

一、Multisim的主窗口界面。

启动Multisim 12后,将出现如图所示的界面。

图 multism 12启动后所示界面界面由多个区域构成:菜单栏,各种工具栏,电路输入窗口,状态条,列表框等。

通过对各部分的操作可以实现电路图的输入、编辑,并根据需要对电路进行相应的观测和分析。

用户可以通过菜单或工具栏改变主窗口的视图内容。

二、菜单栏菜单栏位于界面的上方,通过菜单可以对Multisim的所有功能进行操作。

不难看出菜单中有一些与大多数Windows平台上的应用软件一致的功能选项,如File,Edit,View,Options,Help。

三位二进制减法计数器与芯片仿真进制减法计数器

目录1 课程设计的目的与作用 01.1课程设计目的 02 所用multisim软件环境介绍 02.1 Multisim软件环境介绍 02.2 Multisim软件界面介绍 (1)3设计任务 (2)3.1设计的总体框图 (2)3.1.1三位二进制减法计数器的总体框图 (2)3.1.2 串行序列信号检测器的总体框图 (2)3.1.3 74193芯片仿真63进制减法计数器原理 (2)3.2设计过程 (2)3.2.1 三位二进制同步减法计数器 (2)3.2.2串行序列信号检测器 (4)3.2.3 74193芯片仿真63进制减法计数器 (5)4实验仪器 (6)4.1三位二进制减法器 (6)4.2串行序列检测器 (6)4.3 74193芯片仿真63进制减法器计数 (6)5仿真结果分析 (6)5.1三位二进制同步减法计数器的电路原理图及结果 (6)5.2串行序列信号检测器电路原理图及结果 (7)5.3 74193芯片仿真63进制减法计数器的电路原理图及结果 (7)6设计总结和体会 (8)7参考文献 (8)1 课程设计的目的与作用1.1课程设计目的1.通过Multisim的仿真设计,掌握Multisim软件的基本使用方法;2.学会在multisim环境下建立电路模型,能进行正确的仿真;3.通过Multisim的仿真,熟练掌握三位二进制同步加法计数器和串行序列检测器电路,10000串行序列检测器电路设计;4.学会分析仿真结果的正确性,与理论计算值进行比较;5.通过课程设计,加强动手,动脑的能力。

2 所用multisim软件环境介绍2.1 Multisim软件环境介绍Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,适用于板级的模拟/数字电路板的设计工作。

它包含了电路原理图的图形输入、电路硬件描述语言输入方式,具有丰富的仿真分析能力。

Multisim 10 启动画面图工程师们可以使用Multisim交互式地搭建电路原理图,并对电路进行仿真。

三位二进制减法计数器的设计

目录1设计目的与作用设计目的及设计要求按要求设计三位二进制减法计数器(无效状态001,011)及用 74161 组成 227 进制同步计数器并显示,增强对数字电子技术的认识,稳固讲堂上学到的知识,认识计数器,并且增强对软件 multisim 的认识。

设计作用multisim 仿真软件的使用,能够使我们对计数器及串行检测器有更深的理解,并且学会剖析仿真结果,与理论结果作比较。

增强了自我着手动脑的能力。

2设计任务1.三位二进制减法计数器(无效状态001, 011)组成 227 进制同步计数器并显示3三位二进制减法计数器的设计设计原理设计一个三位二进制减法计数器(无效状态001,011)000/0010/0100/0101/0110/0111/1摆列 Q2n Q1n Q0n图状态图设计过程a.选择触发器因为 JK触发器的功能齐备,使用灵巧,在这里采纳 3 个 CP上涨沿触发的边缘JK触发器。

b.求时钟方程采纳同步方案,故取CP CP CP CP01 2c.求状态方程由所示状态图可直接画出电路次态Q2n+1Q1n+1Q0n+1卡诺图。

再分解开便能够获得如图各触发器的卡诺图。

n nQ1 Q0Q n2000111100111xxx xxx0001010*********图次态 Q2n+1 Q1n+1Q0n+1卡诺图n nQ1 Q0Q2n0001111001x x0 1011 1图 Q2n+1的卡诺图Q 0 1Qn nQ1 Q0n2000111101x x01010图 Q1n+1的卡诺图n nQ1 Q0n00 01 11 1020 1 x x 01 0 0 0 1图 Q0n+1的卡诺图状态方程:Q2n 1 Q2n Q1n Q2n Q1n Q0n(1)Q n 1 Q n Q n Q n Q n( 2)1 1 0 1 0Q0n 1 Q2n Q1n Q 2n Q1n Q0n( 3)( 2)求驱动方程JK 触发器的特征方程为Q n 1J Q n KQ nJ0Q2Q1 , K 0Q2n Q1nJ1K 1Q0nJ 2Q1n Q0n, K 2Q1n Q0n( 3)画逻辑电路图采纳触发器,写出时钟方程,输出方程,驱动方程,便能够画出以下图的逻辑电路图。

32进制同步减法计数器设计解析

目录一、设计目的 (1)二、设计原理 (1)三、设计 (1)3.1设计思路 (1)3.2设计步骤 (1)四、QuartusⅡ9.0操作步骤 (3)五、程序 (4)5.1完整程序 (4)5.2仿真程序 (8)六、仿真 (12)6.1仿真结果 (12)6.2仿真结果分析 (12)七、引脚分配 (13)八、课程设计总结 (14)参考文献 (15)一、设计目的1)巩固和加深对“EDA技术””的基本知识的理解,提高综合运用本课程所学知识的能力。

2)培养学生根据课题需要选学参考书籍、查阅手册、图表和文献资料的自学能力。

通过独立思考,深入钻研相关问题,学会自己分析解决问题的方法。

3)培养硬件设计、软件设计及系统软、硬件调试的基本思路、方法和技巧,并能熟练使用当前较流行的一些有关电路设计与分析的软件和硬件。

二、设计原理计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

按照计数器中的触发器是否同时翻转分类,可将计数器分为同步计数器和异步计数器两种。

本次设计是32进制同步减法计数器。

32进制的二进制范围为“00000”到“11111”,即十进制0~31。

当显示的数小于31时,数字将自减,减至0时又跳会预先输入的数,如此循环。

系统提供50MHZ频率的时钟源,输入的数字信号由实验装置上的开关给定,输出由LED完成,同时数码管显示输入和输出的数字信号。

设置2个按钮,一个作“开始”,即使能端en,一个作系统“复位”res。

三、设计3.1设计思路本次程序设计的思路主要是分模块进行。

32进制同步减法计数器的基本工作原理是循环自减,因此得需要一个自减VHDL的程序。

系统提供50MHZ频率的时钟源,频率太大,肉眼无法观察,得需要一个分频的程序。

三位二进制减法计数器(无效态:000,011)数电课程设计.

让我在以后的学习中,一定会继续坚持不懈地学习新兴的专业知识及相关的非专业知识. 由于我的知识浅薄,经验不足及阅历颇浅,因此还有一些细节存在不足在这里希望老师谅解,我一定会再接再厉根据学习的具体要求不断的修改,完善,争取使该以后的课设慢慢趋向完美通过这次课程设计,我们充分体会到了自己设计东西的乐趣和学习交流的重要性,在动手的过程中,不但增强了实践能力,而且在理论上有了更深的认识;懂得了实践与知识结合的重要性,并在以后的学习中不段的提高自己,通过不断的摸索和实践来弥补自己在硬件方面的差距。

我相信,这次实习将使我受益匪浅,我更相信,我会以更热忱的态度去学习并研究这门重要的实践性课程。

7 参考文献 [1] 作者:余孟尝书名:《数字电子技术基础简明教程》出版社:高等教育出版社出版年:2007 年 12 月 [2] 作者:吴翔,苏建峰书名:《Multisim10&Ultiboard 原理图仿真与 PCB 设计》出版社:电子工业出版社出版年:2008 年 1 月 11。

三位二进制减法计数器的设计

三位二进制减法计数器的设计-CAL-FENGHAI.-(YICAI)-Company One1目录1设计目的与作用 (1)设计目的及设计要求 (1)设计作用 (1)2设计任务 (1)3三位二进制减法计数器的设计 (1)设计原理 (1)设计过程 (2)4 74161构成227进制同步计数器并显示 (4)设计原理 (4)设计过程 (4)5仿真结果分析 (5)三位二进制减法计数器仿真结果 (5)74161构成227进制同步计数器的仿真结果 (8)6设计总结 (8)7参考文献 (9)1设计目的与作用设计目的及设计要求按要求设计三位二进制减法计数器(无效状态001,011)及用74161构成227进制同步计数器并显示,加强对数字电子技术的了解,巩固课堂上学到的知识,了解计数器,并且加强对软件multisim的了解。

设计作用multisim仿真软件的使用,可以使我们对计数器及串行检测器有更深的理解,并且学会分析仿真结果,与理论结果作比较。

加强了自我动手动脑的能力。

2设计任务1.三位二进制减法计数器(无效状态001,011)构成227进制同步计数器并显示3三位二进制减法计数器的设计设计原理设计一个三位二进制减法计数器(无效状态001,011)000 /0 010 /0 100 /0 101 /0 110 /0 111Q Q Q排列210图状态图设计过程a.选择触发器由于JK触发器的功能齐全,使用灵活,在这里选用3个CP上升沿触发的边沿JK触发器。

b .求时钟方程采用同步方案,故取012CP CP CP CP ===c .求状态方程由所示状态图可直接画出电路次态n+1n+1n+1210Q Q Q 卡诺图。

再分解开便可以得到如图各触发器的卡诺图。

Q 1n Q 0nQ 2n1图次态n+1n+1n+1210Q Q Q 卡诺图Q 1n Q 0nQ 1图n+12Q 的卡诺图Q 1n Q 0nQ 2n 0 1图 n+11Q 的卡诺图Q 1n Q 0nQ 2n 图 n+10Q 的卡诺图状态方程:nn Q Q Q Q Q Q 01n 2n 1n 21n 2++=+ (1)nn n n n Q Q Q Q Q 010111+=+ (2)n0n1n 2n 1n 21n 0Q Q Q Q Q Q +=+ (3)(2)求驱动方程JK 触发器的特性方程为n n 1n Q K Q J Q +=+120Q Q J ⊕=,n Q Q K 1n 20+=n 011Q K J ==n 0n 12Q Q J +=,n 0n 12Q Q K =(3)画逻辑电路图选用触发器,写出时钟方程,输出方程,驱动方程,便可以画出如图所示的逻辑电路图。

三位二进制减法计数器(无效态:000,011)数电课程设计

成绩评定表课程设计任务书目录1课程设计的目的及作用 (4)2设计任务 (4)3设计过程 (4)3.1三位二进制减法计数器(无效态:000,011) (4)3.2串行序列检测器(检测序列:1010) (6)3.3基于74191芯片仿真设计23进制减法计数器并显示计数过程 (8)4设计仿电路图 (8)4.1三位二进制减法计数器仿真电路图 (8)4.2串行序列检测器仿真电路图 (9)4.3基于74191芯片仿真设计23进制减法计数器仿真电路图 (9)5仿真结果分析 (10)5.1三位二进制减法计数器仿真结果分析 (10)5.2串行序列检测器仿真结果分析 (10)5.3基于74191芯片仿真设计23进制减法计数器仿真结果分析 (10)6设计总结 (10)7参考文献 (11)1课程设计的目的及作用1、了解同步减法计数器工作原理和逻辑功能。

2、掌握串行序列检测器的分析,设计方法及应用。

3、掌握计数器电路的分析,设计方法及应用。

4、学会正确使用JK 触发器。

2设计任务1、三位二进制减法计数器(无效态:000,011)2、串行序列检测器(检测序列:1010)3、基于74191芯片仿真设计23进制减法计数器并显示计数过程3设计过程3.1三位二进制减法计数器(无效态:000,011)1、状态图001 010 100 101 110 1112、选择的触发器名称:选用三个CP 下降沿触发的边沿JK 触发器3、状态方程三位二进制同步减法计数器次态卡诺图如图1.3.1.1所示:n nQ图3.1.1 三位二进制同步减法计数器次态卡诺图Q 2n+1的卡诺图:nnQ图3.1.2 Q 2n+1 的卡诺图Q 1n+1的卡诺图:n nQ 2图3.1.3 Q 1n+1的卡诺图Q 0n+1的卡诺图:n nQ图3.1.4 Q 0n+1的卡诺图 由卡诺图得出状态方程为:Q 0n+1=Q 1n Q 0n ̅̅̅̅+Q 2n ̅̅̅̅ Q 0n Q 1n+1=(Q 0n ̅̅̅̅+Q 2n ̅̅̅̅)Q 1n ̅̅̅̅+Q 0n Q 1nQ 2n+1=Q 0n +Q 2n Q 1n4、驱动方程J 0=Q 1n J 1=Q 2n Q 0n ̅̅̅̅̅̅̅̅ J 2=Q 0n K 0=Q 2n K 1=Q 0n ̅̅̅̅ K 2=Q 0n ̅̅̅̅ Q 1n ̅̅̅̅5、时钟方程 CP =CP 0=CP 1=CP 26、检查能否自启动/0 /0001 000 111(有效状态)可以自启动7、实验结果:111(灯:亮亮亮) 110(灯:亮亮灭) 101(灯:亮灭亮)100(灯:亮灭灭) 010(灯:灭亮灭) 001(灯:灭灭亮)3.2串行序列检测器(检测序列:1010)1、最简状态图图3.2.1最简状态图2、选择的触发器名称:选用两个CP 下降沿触发的边沿JK 触发器3、输出方程: Y =X ̅ Q 1n Q 0n ̅̅̅̅4、状态方程三位二进制同次态卡诺图:n nQ 2图3.2.2 三位二进制同步减法计数器次态卡诺图Y 的卡诺图:n n图 3.2.3 Y 的卡诺图Q 1n+1的卡诺图:Q 1n Q 0n图3.2.4 Q 1n+1的卡诺图Q 0n+1的卡诺图:Q nQ n图3.2.5 Q 0n+1的卡诺图由卡诺图得出状态方程为:Y =X ̅Q 1n Q 2n ̅̅̅̅ Q 1n+1=X ̅Q 1n ̅̅̅̅Q 0n +XQ 1n Q 0n Q 0n+1=Q 1n ̅̅̅̅Q 0n +XQ 1n ̅̅̅̅ Q 0n ̅̅̅̅+XQ 1n Q 0n ̅̅̅̅5、驱动方程J 0=X J 1=X ̅Q 0nK 0=Q 1n K 1=Q 0n X̅̅̅̅̅̅6、时钟方程 CP =CP 0=CP 17、实验结果 :按1010顺序输入信号,并在每个输入信号来时都给一个脉冲,实验结果分别为: 000(灯:灭灭灭)010(灯:灭亮灭)110(灯:亮亮灭)101(灯:亮灭亮)(按Q 1n Q 0nY 顺序)3.3基于74191芯片仿真设计23进制减法计数器并显示计数过程1、写出S N 的二进制代码S N =S 23=101112、求归零逻辑P N =P 12=Q 4n Q 2n Q 1n Q 0nCR ̅̅̅̅=CT/LD ̅̅̅̅̅̅̅̅̅̅̅̅=P N ̅̅̅̅=P 23̅̅̅̅=Q 4n Q 2n Q 1n Q 0n ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅4、异步置数的值23−1=22 (22)10=(10110)24设计仿电路图4.1三位二进制减法计数器仿真电路图图4.1.1三位二进制减法计数器电路图DCD_HEX_BLUE4.2串行序列检测器仿真电路图图4.2.1串行序列检测器电路图4.3基于74191芯片仿真设计23进制减法计数器仿真电路图图4.3.1基于74191芯片仿真设计23进制减法计数器5 VX2X3U95仿真结果分析5.1三位二进制减法计数器仿真结果分析111(灯:亮亮亮) 110(灯:亮亮灭) 101(灯:亮灭亮)100(灯:亮灭灭) 010(灯:灭亮灭) 001(灯:灭灭亮)显示屏:7 6 5 4 2 15.2串行序列检测器仿真结果分析按1010顺序输入信号,并在每个输入信号来时都给一个脉冲,实验结果分别为:000(灯:灭灭灭)010(灯:灭亮灭)110(灯:亮亮灭)101(灯:亮灭亮)(按Q1n Q0n Y顺序)5.3基于74191芯片仿真设计23进制减法计数器仿真结果分析显示屏:16 15 14 13 12 11 10 0F 0E 0D 0C 0B 0A 09 08 0706 05 04 03 02 01 006设计总结通过本次设计,我系统的学习了multisim软件。

数电课设三位同步二进制减法器串行序列检测电路设计

目录1 .数字电子课程设计的目的与作用 (1)2 .课程设计的任务 (1)3. 三位同步二进制减法器 (1)3.1. 三位同步二进制减法器设计电路的理论分析 (1)3.1.1原始状态图的建立: (1)3.1.2卡诺图 (2)3.1.3时钟方程、输出方程和状态方程: (3)3.1.4无效状态的判断 (4)3.2. 三位同步二进制减法器设计电路 (4)3.3.三位同步二进制减法器的仿真结果 (5)4.串行序列检测电路设计 (8)4.1.串行序列检测电路设计电路的理论分析 (8)4.1.1原始状态图的建立: (8)4.1.2卡诺图 (9)4.1.3时钟方程、输出方程和状态方程: (10)4.2.串行序列检测设计电路 (10)4.3串行序列检测器的仿真结果 (11)5.用数据选择器实现函数F=AB+BC+CA (13)5.1用数据选择器实现函数F=AB+BC+CA的电路设计 (13)5.1.1选择数据译码器 (13)5.1.2写标准与非—与非表达式 (13)5.1.3确定数据选择器输入变量的表达式 (13)5.2用数据选择器实现函数F=AB+BC+CA的设计电路 (14)5.3实验结论 (14)6.设计总结和体会 (14)7.参考文献 (15)1 .数字电子课程设计的目的与作用随着科技的进步和社会的发展,数字电路在各种电器中的应用越来越广泛。

0、1代码的简易变换能够实现复杂的逻辑功能使得数字电路的实现效率很高。

课程设计的目的是通过实际设计并搭建一些简易但典型的数字电路来加深对各逻辑器件逻辑功能的理解。

课程设计能够使我们更进一步理解课堂上所学的理论知识,同时又能锻炼我们的动手能力和分析问题解决问题的能力。

2 .课程设计的任务利用所学的数字电路的理论知识,用JK触发器、74LS00、74LS08等逻辑门在数字电路系统上设计并搭建000、010为无效状态的三位同步二进制减法器以及串行序列1001的检测电路,注意检查其中的无效状态能否自行启动,若不能自启进行相应的逻辑修改,直至符合设计要求。

三位二进制同步减法计数器

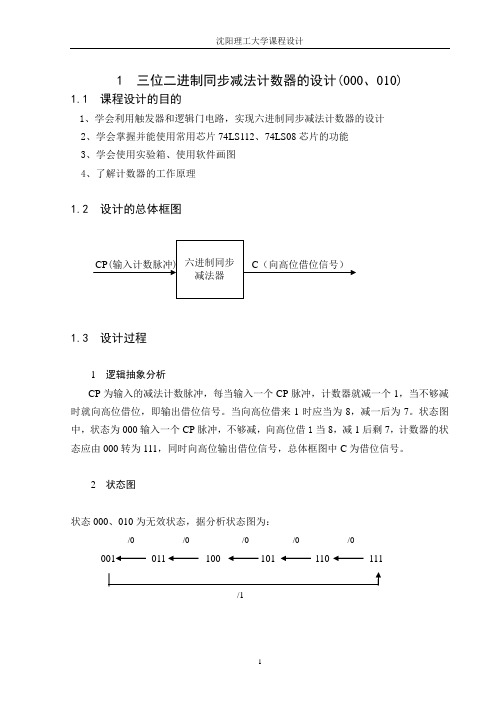

1 三位二进制同步减法计数器的设计(000、010)1.1 课程设计的目的1、学会利用触发器和逻辑门电路,实现六进制同步减法计数器的设计2、学会掌握并能使用常用芯片74LS112、74LS08芯片的功能3、学会使用实验箱、使用软件画图4、了解计数器的工作原理1.2 设计的总体框图1.3 设计过程1逻辑抽象分析CP为输入的减法计数脉冲,每当输入一个CP脉冲,计数器就减一个1,当不够减时就向高位借位,即输出借位信号。

当向高位借来1时应当为8,减一后为7。

状态图中,状态为000输入一个CP脉冲,不够减,向高位借1当8,减1后剩7,计数器的状态应由000转为111,同时向高位输出借位信号,总体框图中C为借位信号。

2状态图状态000、010为无效状态,据分析状态图为:/0 /0 /0 /0 /0001011100101110111/13 选择触发器,求时钟方程、输出方程和状态方程● 选择触发器由于状态数M=6,触发器的个数n 满足122n n M -≤≤,故n 的取值为3。

选用3个下降沿触发的JK 触发器。

● 求时钟方程因为是同步,故012CP CP CP CP ===● 求输出方程1.3.1 输出C 的卡诺图根据输出C 的卡诺图可得输出方程为C=Q 2n Q 1n● 求状态方程计数器的次态的卡诺图为1.3.2 次态210n n nQ Q Q 的卡诺图各个触发器的次态卡诺图如下:1.3.3 2nQ 次态卡诺图1.3.4 1n Q 的次态卡诺图1.3.5 0nQ 的次态卡诺图根据次态卡诺图可得次态方程为:Q 2n+1=Q 1n Q 0n +Q 2n Q 1nQ 1n+1= Q 1n Q 0n + Q 2n Q 1n + Q 2n Q 1n Q 0n Q 0n+1 =Q 2n +Q 0n4 求驱动方程Q 2n+1 =Q 1n Q 2n + Q 0n Q 1n Q 2n Q 1n+1=Q 0n Q 2n Q 1n +Q 0n Q 2n Q 1n Q 0n+1=Q 2n Q 0n +Q 2n Q 0n驱动方程是:J 0 = Q 2n K 0 =Q 2n J 1 =Q 0n Q 2n K 1= Q 0n Q 2J 2 = Q 1n K 2=Q 0n Q 1n5 检查是否能自启动将无效状态100、101分别代入输出方程、状态方程进行计算,结果如下:/0 /0000 111 010 001而000、010都是有效状态,故设计的电路能够自启动。

进制计数器课程设计

进制计数器课程设计一、课程目标知识目标:1. 让学生掌握进制计数器的基本概念,包括二进制、八进制、十进制和十六进制的转换方法;2. 使学生理解进制计数器在实际应用中的重要性,如计算机科学、电子技术等领域;3. 帮助学生了解不同进制之间的相互转换规律,提高学生的数学思维能力。

技能目标:1. 培养学生熟练运用进制计数器进行不同进制间转换的能力;2. 提高学生分析问题、解决问题的能力,尤其在电子技术、计算机编程等领域的问题;3. 培养学生团队协作和沟通能力,通过小组讨论和实践,共同完成任务。

情感态度价值观目标:1. 激发学生对进制计数器的学习兴趣,培养其探索精神和创新意识;2. 培养学生严谨的学习态度,对待科学知识具有敬畏之心;3. 增强学生的国家荣誉感和民族自豪感,认识到我国在进制计数器领域的发展成就。

课程性质:本课程为信息技术与数学相结合的实践课程,强调理论与实践相结合,注重培养学生的动手能力和实际应用能力。

学生特点:本课程针对初中生,学生具有一定的数学基础和逻辑思维能力,但需加强实际操作能力和团队协作能力的培养。

教学要求:教师应结合学生实际情况,采用启发式教学,引导学生主动探究,注重培养学生的实践能力和创新能力。

在教学过程中,关注学生的个体差异,因材施教,确保每位学生都能达到课程目标。

通过课程学习,使学生具备进制计数器相关知识和技能,为后续相关课程的学习打下坚实基础。

二、教学内容1. 导入:通过日常生活中的计数实例,引出进制计数器的概念及其重要性。

- 简介进制计数器的基本概念和应用领域。

- 激发学生对进制计数器的学习兴趣。

2. 基本知识学习:- 二进制、八进制、十进制和十六进制的定义及特点;- 不同进制之间的转换方法,如二进制与十进制的转换、八进制与十六进制的转换等。

3. 实践操作:- 安排学生进行进制计数器操作练习,巩固所学知识;- 设计实际案例,让学生动手解决进制计数器相关问题。

4. 拓展与应用:- 介绍进制计数器在计算机科学、电子技术等领域的应用;- 引导学生探讨进制计数器的未来发展及其对人类生活的影响。

三位二进制减法计数器

成绩评定表课程设计任务书目录1 课程设计的目的与作用 (1)2 设计任务 (1)2.1 三位二进制同步减法计数器 (1)2.2串行序列发生器的设计 (1)2.3基于74191芯片仿真设计54进制减法计数器并显示计数过程 (1)3设计原理 (2)3.1三位二进制减法计数器 (2)3.2串行序列发生器的设计 (2)3.374191芯片仿真设计54进制减法计数器并显示计数过程 (2)4实验步骤 (3)4.1三位二进制减法计数器(无效状态000,110) (3)4.2串行序列发生器的设计 (9)串行序列信号发生器的总体框图: (9)4.3 74191芯片仿真设计54进制减法计数器并显示计数过程 . 135 仿真结果分析 (16)6 设计总结 (16)7 参考文献 (16)1 课程设计的目的与作用1.了解同步计数器及序列信号发生器工作原理;2.掌握计数器电路的分析,设计方法及应用;3.掌握序列信号发生器的分析,设计方法及应用2 设计任务2.1 三位二进制同步减法计数器1.设计一个循环型三位二进制减法计数器,其中无效状态为(000,110),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

2.2串行序列发生器的设计1.设计一个能循环产生给定序列的串行序列信号发生器,其中发生序列(1101),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

2.3基于74191芯片仿真设计54进制减法计数器并显示计数过程1.设计一个基于74191芯片仿真设计54进制减法计数器并显示计数过程,组合电路部分选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

3设计原理3.1 三位二进制减法计数器1.计数器是用来统计输入脉冲个数电路,是组成数字电路和计算机电路的基本时序逻辑部件。

计数器按长度可分为:二进制,十进制和任意进制计数器。

计数器不仅有加法计数器,也有减法计数器。

三位二进制减法计数器(无效态:000,100)课程设计综述

成绩评定表学生姓名’班级学号专业课程设计题目数字电子课程设计评语组长签字:成绩日期20 年月日课程设计任务书学院信息科学与工程专业学生姓名班级学号课程设计题目 1.三位二进制减法计数器(无效态:000,100)2、串行序列检测器(检测序列:1011)3.基于74191芯片仿真设计243进制减法计数器并显示计数过程实践教学要求与任务:1)采用实验箱设计、连接、调试无效态为000、100的三位二进制计数器。

2)采用multisim 仿真软件设计、连接、调试检测序列1011的串行序列检测器。

3)采用multisim 仿真软件设计、连接、调试基于74191芯片的243进制减法计数器。

4)采用multisim 仿真软件建立复杂的计数器电路模型;5)对电路进行理论分析;6)在multisim环境下分析仿真结果,给出仿真时序图;7)撰写课程设计报告。

工作计划与进度安排:第1天:1. 布置课程设计题目及任务。

2. 查找文献、资料,确立设计方案。

第2-3天:在实验室中设计、连接、调试三位二进制计数器、串行序列检测器及23进制减法计数器电路。

第4天:1. 安装multisim软件,熟悉multisim软件仿真环境。

在multisim环境下建立电路模型,学会建立元件库。

2. 对设计电路进行理论分析、计算。

3. 在multisim环境下仿真电路功能,修改相应参数,分析结果的变化情况。

第5天:1. 课程设计结果验收。

2. 针对课程设计题目进行答辩。

3. 完成课程设计报告。

指导教师:2013年6月日专业负责人:2013 年月日学院教学副院长:2013 年月日目录1 Multisim软件环境介绍: (4)2 课程设计的目的与作用 (5)3 课程设计的任务 (6)4 三位二进制减法计数器的设计(无效态:000,100) (6)4.1 三位二进制减法计数器的设计原理 (6)4.2 三位二进制减法计数器的设计过程 (6)5 串行序列检测器设计过程(检测序列:1011) (10)5.1 检测器的原理: (10)5.2 检测器的设计过程: (11)6 基于74191芯片仿真设计243进制减法计数器并显示计数过程 (17)6.1 设计原理: (17)6.2 设计过程: (17)7 设计总结和体会 (19)8 参考献文 (20)1 Multisim软件环境介绍:Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,适用于板级的模拟/数字电路板的设计工作。

课程设计的目的与作用

④求驱动方程

n n n J0 =Qn 2 Q1 + Q2 Q1

K 0 =1 K1 =Qn 0

J1 = Qn 0

J2 =Qn 1 ⑤画逻辑电路图

n K 2 =Qn 0 + Q1

图 3.2.2 逻辑电路图

⑥检查电路能否自启动 将无效状态 001、110 带入状态方程进行计算,结果如下: 001 够自启动。 100(有效状态) 011 010(有效状态)可见,所设计是的时序电路能

1) 采用实验箱设计、连接、调试三位二进制计数器; 2) 采用实验箱设计、连接、调试中规模芯片构成的任意进制计数器; 3) 采用 multisim 仿真软件建立复杂的计数器电路模型; 4) 对电路进行理论分析; 5) 在 multisim 环境下分析仿真结果,给出仿真时序图; 6) 撰写课程设计报告。Fra bibliotek指导教师:

专业负责人:

学院教学副院长:

2016 年 月 日

2016 年 月

日

2016 年

月

日

3.三位二进制减法计数器的设计

1.状态图

000 010 100 101 110 111

3.1 状态图 2.选择触发器,求时钟方程、状态方程

①选择触发器 由于 JK 触发器功能齐全、使用灵活,在这里选用 3 个 CP 下降沿触发的边沿 JK 触发器。 ②求时钟方程 采用同步方案,故取 CP0=CP1=CP2=CP CP 是整个要设计的时序电路的输入时钟脉冲。 ③求状态方程 确定约束项 从图 3.1 给出的状态图可以看出,还有 001、011 两个代码状态没有出现,显然他们是没

1 课程设计的目的与作用

1.1 课程设计的目的

学习了数字电子技术的理论知识,重点在于达到理论实际相结合的学习目标,切实要 求学生的实际运用能力。考虑到电子电路设计自动化也是目前电子技术发展的一个重要趋 势,针对课程的要求对学生进行综合训练的一个实践教学环节。从应用的要求出发,除了 扼要介绍它们的电路图原理外,着重介绍器件的主要技术性能,典型应用或者连接方法。

三位二进制同步减法计数器[1]

![三位二进制同步减法计数器[1]](https://img.taocdn.com/s3/m/42749d5b02768e9951e738a7.png)

目录1、设计任务与要求 (3)2、方案设计与论证 (3)2.1 基本原理 (3)2.2 设计过程 (3)3、总原理图及元器件清单 (6)3.1 原理图 (6)3.2 原件清单 (7)4、实验结果 (8)5、结论与心得 (11)6、参考文献 (12)成绩评定表 (12)课程设计任务书 (14)3位二进制同步减法计数器1、设计任务与要求设计一个3位二进制同步减法计数器(无效状态为001 100)2、方案设计与论证2.1 基本原理计数器是用来统计脉冲个数的电路,是组成数字电路和计算机电路的基本时序部件,计数器按进制分可分为:二进制,十进制和N进制。

计数器不仅有加法计数器,也有减法计数器。

一个计数器如果既能完成加法计数,又能完成减法计数,则其称为可逆计数器。

同步计数器:当输入计数脉冲到来时,要更新状态的触发器都是同时翻转的图(1)2.2 设计过程2.2.1 状态图000 111 110 101 011 010图(2)2.2.2 卡诺图00 01 11 10111 xxx 010 000 xxx011110101图(3)00 01 11 10 1 x 0 0 x11图(4)00 01 11 101 x 1 1 x110 1Q 1nQ 0n Q 2nQ 1nQ 0n Q 2n0 1Q 1n+1的卡诺图Q 1nQ 0nQ 2n 0 1图(5)00 01 11 101 x 0 0 x11图(6)2.2.3 状态方程与驱动方程状态方程:12n Q +=1n Q2n Q+1n Q2n Q11n Q +=1nQ +0n Q1nQ10n Q +=2n Q 0n Q +0nQ 1nQ +1nQ 0n Q驱动方程:J 2=1nQ K 2=1nQJ 1=1 K 1=0nQ J 0=2n Q1n Q K 0=1nQ2.2.4 电路图Q 1nQ 0nQ 2n0 1图(7)实验结果可通过数字显示器的数字变化检验,较直观易懂,容易验证电路是否正确。

三位二进制减法计数器

成绩评定表课程设计任务书目录1 课程设计的目的与作用1.了解同步计数器及序列信号发生器工作原理;2.掌握计数器电路的分析,设计方法及应用;3.掌握序列信号发生器的分析,设计方法及应用2 设计任务三位二进制同步减法计数器1.设计一个循环型三位二进制减法计数器,其中无效状态为(000,110),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

串行序列发生器的设计1.设计一个能循环产生给定序列的串行序列信号发生器,其中发生序列(1101),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

基于74191芯片仿真设计54进制减法计数器并显示计数过程1.设计一个基于74191芯片仿真设计54进制减法计数器并显示计数过程,组合电路部分选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

3设计原理三位二进制减法计数器1.计数器是用来统计输入脉冲个数电路,是组成数字电路和计算机电路的基本时序逻辑部件。

计数器按长度可分为:二进制,十进制和任意进制计数器。

计数器不仅有加法计数器,也有减法计数器。

如果一个计数器既能完成累加技术功能,也能完成递减功能,则称其为可逆计数器。

在同步计数器中,个触发器共用同一个时钟信号。

2.时序电路的分析过程:根据给定的时序电路,写出各触发器的驱动方程,输出方程,根据驱动方程带入触发器特征方程,得到每个触发器的次态方程;再根据给定初态,一次迭代得到特征转换表,分析特征转换表画出状态图。

是输入计数脉冲,所谓计数,就是记CP脉冲个数,每来一个CP脉冲,计数器就加一个1,随着输入计数脉冲个数的增加,计数器中的数值也增大,当计数器记满时再来CP脉冲,计数器归零的同时给高位进位,即要给高位进位信号。

串行序列发生器的设计1.序列是把一组0,1数码按一定规则顺序排列的串行信号,可以做同步信号地址码,数据等,也可以做控制信号。

三位二进制减法计数器

成绩评定表课程设计任务书目录1 课程设计的目的与作用 (1)2 设计任务 (1)2.1 三位二进制同步减法计数器 (1)2.2串行序列发生器的设计 (1)2.3基于74191芯片仿真设计54进制减法计数器并显示计数过程 (1)3设计原理 (2)3.1三位二进制减法计数器 (2)3.2串行序列发生器的设计 (2)3.374191芯片仿真设计54进制减法计数器并显示计数过程 (2)4实验步骤 (3)4.1三位二进制减法计数器(无效状态000,110) (3)4.2串行序列发生器的设计 (7)串行序列信号发生器的总体框图: (7)4.3 74191芯片仿真设计54进制减法计数器并显示计数过程 (11)5 仿真结果分析 (13)6 设计总结 (13)7 参考文献 (13)1 课程设计的目的与作用1.了解同步计数器及序列信号发生器工作原理;2.掌握计数器电路的分析,设计方法及应用;3.掌握序列信号发生器的分析,设计方法及应用2 设计任务2.1 三位二进制同步减法计数器1.设计一个循环型三位二进制减法计数器,其中无效状态为(000,110),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

2.2串行序列发生器的设计1.设计一个能循环产生给定序列的串行序列信号发生器,其中发生序列(1101),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

2.3基于74191芯片仿真设计54进制减法计数器并显示计数过程1.设计一个基于74191芯片仿真设计54进制减法计数器并显示计数过程,组合电路部分选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

3设计原理3.1 三位二进制减法计数器1.计数器是用来统计输入脉冲个数电路,是组成数字电路和计算机电路的基本时序逻辑部件。

计数器按长度可分为:二进制,十进制和任意进制计数器。

计数器不仅有加法计数器,也有减法计数器。

三位二进制减法计数器精选文档

三位二进制减法计数器精选文档TTMS system office room 【TTMS16H-TTMS2A-TTMS8Q8-成绩评定表课程设计任务书目录1 课程设计的目的与作用1.了解同步计数器及序列信号发生器工作原理;2.掌握计数器电路的分析,设计方法及应用;3.掌握序列信号发生器的分析,设计方法及应用2 设计任务三位二进制同步减法计数器1.设计一个循环型三位二进制减法计数器,其中无效状态为(000,110),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

串行序列发生器的设计1.设计一个能循环产生给定序列的串行序列信号发生器,其中发生序列(1101),组合电路选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

基于74191芯片仿真设计54进制减法计数器并显示计数过程1.设计一个基于74191芯片仿真设计54进制减法计数器并显示计数过程,组合电路部分选用与门和与非门等。

2.根据自己的设计接线。

3.检查无误后,测试其功能。

3设计原理三位二进制减法计数器1.计数器是用来统计输入脉冲个数电路,是组成数字电路和计算机电路的基本时序逻辑部件。

计数器按长度可分为:二进制,十进制和任意进制计数器。

计数器不仅有加法计数器,也有减法计数器。

如果一个计数器既能完成累加技术功能,也能完成递减功能,则称其为可逆计数器。

在同步计数器中,个触发器共用同一个时钟信号。

2.时序电路的分析过程:根据给定的时序电路,写出各触发器的驱动方程,输出方程,根据驱动方程带入触发器特征方程,得到每个触发器的次态方程;再根据给定初态,一次迭代得到特征转换表,分析特征转换表画出状态图。

是输入计数脉冲,所谓计数,就是记CP脉冲个数,每来一个CP脉冲,计数器就加一个1,随着输入计数脉冲个数的增加,计数器中的数值也增大,当计数器记满时再来CP脉冲,计数器归零的同时给高位进位,即要给高位进位信号。

异步三位二进制减法计数器

异步三位二进制减法计数器

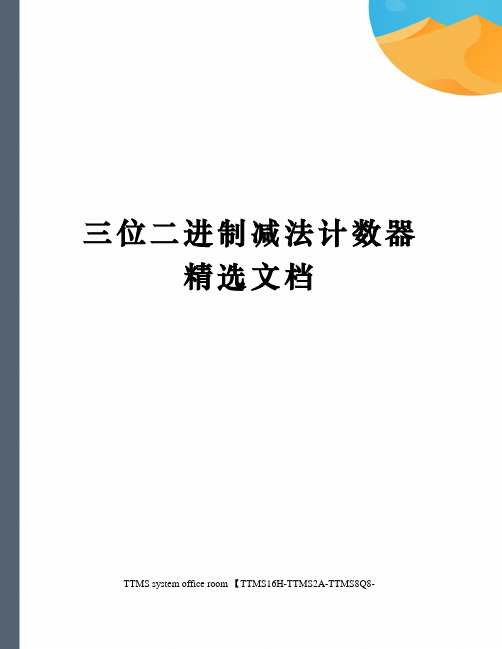

若计数脉冲只加到部分触发器的时钟输入端上,而部分触发器的触发信号由其他触发器的输出用作时钟脉冲,各触发器的翻转有先有后的二进制计数器称为异步二进制计数器。

每输入一个脉冲,就进行减1运算的计数器称为减法计数器,也称为递减计数器。

异步二进制计数器结构简单,但速度较慢(只能逐级翻转)。

异步三位二进制减法计数器的电路组成,见图示

逻辑关系表

时序图

工作过程

(1)计数器工作前应先清零,初始状态为000。

(2)当第1个CP脉冲到来后,FF0的状态由0变1。

FF2 、FF1的状态翻转,由0变1。

计数器状态为111。

(3)当第2个CP脉冲到来后,只有FF0的状态由1变0。

FF2、FF1保持原态不变。

计数器状态为110。

(4)当第3个CP脉冲到来后,FF0的状态由0变1。

FF1状态由1翻转为0,FF2保持原态不变。

计数器状态为101。

(5)当第4个CP脉冲到来后,则FF0的状态由1变0。

FF1、FF2保持原态不变。

计数器状态为100。

(6)当第5个CP脉冲到来后,三个触发器均翻转,计数器状态为011。

(7)当第6个CP脉冲到来后,则FF0的状态由1变0。

FF2、FF1保持原态不变。

计数器状态为010。

(8)当第7个CP脉冲到来后,FF0的状态由0变1。

FF1状态由1翻转为0,FF2保持原态不变。

计数器状态为001。

如再送入一个CP脉冲,计数恢复为000。

状态表。

32进制同步减法计数器设计详解

目录一、设计目的 (1)二、设计原理 (1)三、设计 (1)3.1设计思路 (1)3.2设计步骤 (1)四、QuartusⅡ9.0操作步骤 (3)五、程序 (4)5.1完整程序 (4)5.2仿真程序 (8)六、仿真 (12)6.1仿真结果 (12)6.2仿真结果分析 (12)七、引脚分配 (13)八、课程设计总结 (14)参考文献 (15)一、设计目的1)巩固和加深对“EDA技术””的基本知识的理解,提高综合运用本课程所学知识的能力。

2)培养学生根据课题需要选学参考书籍、查阅手册、图表和文献资料的自学能力。

通过独立思考,深入钻研相关问题,学会自己分析解决问题的方法。

3)培养硬件设计、软件设计及系统软、硬件调试的基本思路、方法和技巧,并能熟练使用当前较流行的一些有关电路设计与分析的软件和硬件。

二、设计原理计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

按照计数器中的触发器是否同时翻转分类,可将计数器分为同步计数器和异步计数器两种。

本次设计是32进制同步减法计数器。

32进制的二进制范围为“00000”到“11111”,即十进制0~31。

当显示的数小于31时,数字将自减,减至0时又跳会预先输入的数,如此循环。

系统提供50MHZ频率的时钟源,输入的数字信号由实验装置上的开关给定,输出由LED完成,同时数码管显示输入和输出的数字信号。

设置2个按钮,一个作“开始”,即使能端en,一个作系统“复位”res。

三、设计3.1设计思路本次程序设计的思路主要是分模块进行。

32进制同步减法计数器的基本工作原理是循环自减,因此得需要一个自减VHDL的程序。

系统提供50MHZ频率的时钟源,频率太大,肉眼无法观察,得需要一个分频的程序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

成绩评定表课程设计任务书目录1 Multisim软件环境介绍:............................................... 4. 2课程设计的目的与作用..................................................... 5. 3课程设计的任务........................................................... 6.4 三位二进制减法计数器的设计(无效态: 000, 100) (6)4.1三位二进制减法计数器的设计原理 (6)4.2三位二进制减法计数器的设计过程 (6)5串行序列检测器设计过程(检测序列:1011)................................. 1 0 5.1检测器的原理: .. (10)5.2检测器的设计过程:.................................................... .1.1 6基于74191芯片仿真设计243进制减法计数器并显示计数过程. (17)6.1设计原理: .......................................................... 1.7 6.2设计过程: .......................................................... 1.7 7设计总结和体会........................................................... 1.9 8 参考献文 (20)1 Multisim 软件环境介绍:Multisim 是美国国家仪器(NI )有限公司推出的以 Win dows 为基础的仿真工具,适用于板级的模拟/数 字电路板的设计工作。

它包含了电路原理图的图形输 入、电路硬件描述语言输入方式,具有丰富的仿真分 析能力。

工程师们可以使用 Multisim 交互式地搭建电路原理图,并对电路进行 仿真。

Multisim 提炼了 SPICE 仿真的复杂内容,这样工程师无需懂得深入 的SPICE 技术就可以很快地进行捕获、仿真和分析新的设计,这也使其更 适合电子学教育。

通过 Multisim 和虚拟仪器技术,PCB 设计工程师和电子 学教育工作者可以完成从理论到原理图捕获与仿真再到原型设计和测试这 样一个完整的综合设计流程。

NI Multisim 软件结合了直观的捕捉和功能强大的仿真,能够快速、轻松、 高效地对电路进行设计和验证。

凭借 NI Multisim ,您可以立即创建具有完整组 件库的电路图,并利用工业标准 SPICE 模拟器模仿电路行为。

借助专业的高级 SPICE 分析和虚拟仪器,您能在设计流程中提早对电路设计进行的迅速验证,从 而缩短建模循环。

与NI LabVIEW 和SignalExpress 软件的集成,完善了具有强 大技术的设计流程,从而能够比较具有模拟数据的实现建模测量。

一、 Multisim 的主窗口界面。

启动Multisim 10 后,将出现如图所示的界面。

jFMTlUWNTI窃 Nl Multisim' 10Multisim 10 启动画面醪g Mu -」1^pi _,鼻4 dAMCp. k<IV4H |*85 J^rriti 'wrtiLi mlf«ji::(*B■:ES停口EULJU WPIJM丄IS EJD i*ftiH:4¥fia; ■n;b:j ^IKIHI0甲#丘1 母厲& ^■■■毗亠少-CI ICIL J* ■ NifWk^^ ~l P H Qi. ■<! 4k. €LII » w 4 i> t TT 43 m El ra r- H r * 吞T. J- ■OP R^-E-K - El - ■!- KJ-BE-B-HJ-菜单栏菜单栏位于界面的上方,通过菜单可以对Multisim的所有功能进行操作。

不难看出菜单中有一些与大多数Windows平台上的应用软件一致的功能选项,女口 File , Edit ,View, Options ,Help。

此外,还有一些EDA软件专用的选项,如 Place, Simulation ,Transfer 以及 Tool 等。

三、工具栏Multisim 2001提供了多种工具栏,并以层次化的模式加以管理,用户可以通过View菜单中的选项方便地将顶层的工具栏打开或关闭,再通过顶层工具栏中的按钮来管理和控制下层的工具栏。

通过工具栏,用户可以方便直接地使用软件的各项功能。

顶层的工具栏有:Standard 工具栏、 Design 工具栏、Zoom 工具栏,Simulatio n 工具栏。

2课程设计的目的与作用一•课程设计的目的1)掌握数字电子技术在实际生活中的应用;2)更加深刻了解数字电子知识体系;3)通过本次设计熟悉软件平台、图形和文本输入、编辑、及仿真4)掌握计数器电路的分析,设计方法及应用;5 )学会正确使用JK触发器;二.课程设计的作用1 )学会了分析仿真结果的正确性,与理论计算值进行比较; 2)通过课程设计,加强了动手,动脑的能力;3课程设计的任务1) 三位二进制减法计数器(无效态:000,100) 2) 串行序列检测器(检测序列:1011) 3) 基于74191芯片仿真设计243进制减法计数器4三位二进制减法计数器的设计(无效态:000, 100)4.1三位二进制减法计数器的设计原理计数器是利用统计脉冲个数的电路,是组成数字电路和计算机电路的基本时 序部件,计数器按长短可分为:二进制,十进制和 N 进制计数器。

计数器不仅有 加法计数器,也有减法计数器。

如果一个计数器既能完成累加计数的功能,又能完成递减的功能,则称其为 可逆计数器。

同步计数器:当输入计数脉冲到来时,要更新状态的触发器都是同 时翻转的计数器,叫做同步计数器。

4.2三位二进制减法计数器的设计过程1)总体设计过程图4.2( a )设计流程图2)减法器的状态图如下 4.2 (b )(无效态:000,100)斗/O /0 /O /O /o111 ----- 10 ------ 01 ------ 11 ------ 101 ---- 001排列顺序:Q2Q :Q 0/Y图 4.2(b)3) 选择触发器、求时钟方程、输出方程、状态方程及驱动方程 a 选择触发器:由于JK 触发器功能齐全、使用灵活,故选用 3个下降沿JK 触发器, 本实验中选用74LS112D 芯片。

b 求时钟方程:本实验中采用同步计数故CP o =CP=CP=CP c 求输出方程:本实验给的无效态为000、100 对应最小项为Q 0 Q 1Q 2和Q; Q: Q ;由图4.2 (b)所示状态图所规定的输出与现态之间的逻辑关系,可以直 接画出输出信号丫的方程d 求状态方程:根据输出信号的卡诺图可得到上述三触发器的卡诺图图4.2 (b)状态图可直接写出Q;1Q ;1Q;1的卡诺图由如图4.2(c)XXX111 010 001 XXX01111010101 11 10@0图4.2( c)次态Q n+1Q n+1Q n+1卡诺图00根据三个次态的卡诺图可得触发器的状态方程:」広迈乜0;H e;1 =谊E IIe求驱动方程:Q 1 = JQ ' kQ变换状态方程,并比较特性方程求驱动方程: 2 /司K运L上=歹W图4.2 (g)逻辑连线图图4.2 (h)仿真1114)画逻辑电路图:2.5 V5)仿真结果6 V 1 VlOOmsec 200mXI X32 5 V图4.2 (i)仿真1106)检查能否自启动:000 --------- 100 -*111无效态没有形成循环,所以能自启动。

7)实验结论:经过实验可知,满足时序图的变化,且可以进行自启动。

现态Q n为0,次态Q n+1与j有关与k无关,即当Q n+1由0变0时,j=0 ; Q n+1由0 变 1 时,j=1。

现态Q n为1,次态Q n+1与k有关与j无关,即当Q n+1由1变0时,k=1; Q n+1由1 变 1 时,k=0。

5串行序列检测器设计过程(检测序列:1011)5.1 检测器的原理:序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出1,否则输出0。

由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。

在检测过程中,任何一位不相等都将回到初始状态重新开始检测。

5.2 检测器的设计过程:串行序列信号发生器的总体框图Y串行序列输出图5.2(a)串行序列信号发生器的总体框图1) 进行逻辑抽象建立原始状态图2) 进行状态分配,画出用二进制数编码后的状态表 3) 画出串行数据检测的状态图:图5.2 (b)串行检测器状态图4) 选择触发器、求时钟方程、输出方程、状态方程和驱动方程 a 选用两个CP 下降沿触发的边沿JK 触发器;b 采用同步故cp 0=CP 1=CP 2=CPc 求输出方程: 由状态图可见b 求状态方程:按图5.2 (b)所示状态图得规定,可画出如图 5.2(c)所示的电路次态的卡诺 图CP 输入脉冲串行序列信号发生器000010000000000XXX XXX XXX001XXX XXX XXX001000100011 10图 5.2 (c)触发器的次态卡诺图可根据上图分解得图5.2 (d) Q;的次态卡诺图图5.2 (f)Q;的次态卡诺图e 求状态方程由图5.2 (d)、5.2 (e)、5.2 (f)得状态方程为f 求驱动方程:CT 1二JQ1kQ ;变换状态方程,并比较特性方程求驱动方程:e ;1XXX0 X X0 0101 11 10n图5.2 (e ) Q 1的次态卡诺图D J=^Q:矿亍e:H0:K N;5)画逻辑电路图如下图5.2 (g)6)仿真结果:图 5.2 (g)图 5.2 (h)001(输入1)图 5.2 (i) 010 (输入 0)图 5.2 (j) 011输入 1)VW100(输入1)图 5.2 (k)图5.2 (l) 111输入1,序列被检测,输出1)图 5.2 (m) 输入、脉冲、输出时序图7 )所设计的检测器均为有效态。

有上图可见,设计的电路能够良好的运行。

6基于74191芯片仿真设计243进制减法计数器并显示计数过程6.1 设计原理:1)74191功能表2)获得N进制计数器常用的方法有两种:一是用时钟触发器和门电路进行设计;二是用集成计数器构成。