位同步的FPGA实现

π/4-DQPSK调制解调位同步算法及其FPGA的实现

Kew rs q4DQ S y od :, 一 P K;s b l y crnzt n P m y o n ho i i ;F GA s ao

0 引

言

1 调 制解 调 的 原 理

74D P K信号 星座 图和原理框 图分别 图 1 图 2 c ~Q S / 和 所

n e wo smp igp it y b 1S h lo ih i smpea dt eo eain i as i l n h a et e t e d t a l o n si as n n m o. o teag rtm s i l n h p rto s losmpea dt esm i si m i b te o i lme tt e aldgtlrc ie.M e n i m pe e tn hst e r k s u eo GA s e trt mp e n h l iia e ev r a whl i lm n ig t i h y ma e s fFP .Th eu t e o e r s l s o hs h ws t i me h d s rfr t DLL n co t o i p ee o i a cmm o aig aa tr a d d p a i t.I as a he e s c es n d t p rmee n a a tb l y t lo c iv s u c s i n i

a g r t m nd m pl m e a i n n FPGA l o ih a i e nt to i

Fe gJ a Li n n u n nBi

( p rme fEn nern c n lg De a t nto g e igTe h o o y,Sc a om a nv r iyCa tn mp s ihu nN r lU iest oa g Ca u ,Che g u 6 0 7 ) n d 1 0 2

基于FPGA的锁相环位同步提取电路设计

基于FPGA的锁相环位同步提取电路设计锁相环(Phase-Locked Loop,PLL)是一种广泛应用于通信、控制及信号处理等领域的电路,能够实现频率同步和相位同步。

在本文中,我们将讨论基于FPGA的锁相环位同步提取电路设计。

首先,我们将介绍锁相环的基本原理。

锁相环由相位比较器、低通滤波器、VCO(Voltage-Controlled Oscillator)和分频器组成。

相位比较器用于比较参考信号和反馈信号的相位差,将相位差转换为电压差。

低通滤波器将电压差平滑处理,得到控制电压,用于控制VCO的频率。

VCO产生与输入信号频率相同的输出信号,通过分频器将输出信号分频后与参考信号进行比较,实现频率同步。

在基于FPGA的锁相环位同步提取电路设计中,我们的目标是实现一个能够提取输入信号的位同步信息的电路,其中输入信号可能包含多个周期不同的位同步序列。

首先,我们需要设计一个相位比较器,用于比较参考信号和输入信号的相位差。

可以使用FPGA中的数字时钟管理模块来实现相位比较器,将输入信号与参考信号都映射到固定的时钟边沿上,并通过计数器测量输入信号和参考信号之间的相位差。

然后,我们需要设计一个低通滤波器,用于平滑处理相位差。

可以使用FPGA中的滑动平均滤波器来实现低通滤波器,通过对相位差进行滑动平均运算,得到平滑的控制电压。

接下来,我们需要设计一个VCO,用于产生与输入信号频率相同的输出信号。

可以使用FPGA中的数字控制模块来实现VCO,通过调节VCO的控制电压来控制输出频率。

最后,我们需要设计一个分频器,将VCO的输出信号分频后与参考信号进行比较。

可以使用FPGA中的计数器来实现分频器,通过设置分频器的计数值来实现对VCO输出信号的分频。

在整个电路设计过程中,我们需要注意以下几点:1.选择合适的时钟频率和分辨率。

时钟频率要足够高,以满足输入信号的高速采样需求。

分辨率要足够高,以保证位同步信息的精确提取。

2.选择合适的滤波器参数。

基于FPGA的改进积分型位同步环设计

0 引 言

位 同步也 称 定 时 同步 的提取。近年来 , 围绕提高

锁定速 度及 抗干 扰性 能 , 很 多 文献 提 出 了一 些 改 进

是数字通信系统特有的一种同步 , 不论是基带传输

还是频带传输都需要位 同步 。由于信道传输延时以 及 收发两 端时钟 频 率及 相 位 的 偏 移 , 接 收端 为 了准 确恢 复发 送端所 发 送 的数 据 , 接 收 时 钟必 须 与 所 收

s y n c h r o n i z a i t o n l o o p ,t h e s i mu l a t i o n r e s u l t s i n d i c a t e he t i m p r o v e me n t s y s t e m c a n r e d u c e he t p h a s e j i t t e r

了仿真测试 ,仿真结果表 明,改进的位 同步环可有效减少相位抖动 ,满足性能要求。 关键词 :位同步 ;F P G A ;V H D L 语言

De s i g n o f i mp r o v e me nt i n t e g r a l b i t s y nc h r o n i z a t i o n l o o p b a s e d o n FPGA

e f e c t i v e l y a n d me e t t he p e fo r r ma nc e r e q ui r e me n t s . ’

一种基于FPGA的位同步时钟提取方法及装置[发明专利]

![一种基于FPGA的位同步时钟提取方法及装置[发明专利]](https://img.taocdn.com/s3/m/077e0be290c69ec3d4bb75ae.png)

专利名称:一种基于FPGA的位同步时钟提取方法及装置专利类型:发明专利

发明人:丰泳翔,韩卓定,陈紫业,郑旎杉,陈小桥

申请号:CN201610994547.7

申请日:20161111

公开号:CN106533432A

公开日:

20170322

专利内容由知识产权出版社提供

摘要:本发明涉及通信技术领域,具体涉及一种基于FPGA的位同步时钟提取方法及装置,包括外部CK信号,包括信号发生模块、模拟信号传输模块、待测信号调理模块、信号处理模块、显示屏模块和键盘控制模块;外部CK信号输入信号发生模块,信号发生模块依次连接模拟信号传输模块、待测信号调理模块、信号处理模块、显示屏模块和键盘模块;信号发生模块用于产生测试m序列;模拟信号传输模块用于m序列滤波、衰减;待测信号调理模块用于m序列放大、整形;信号处理模块用于从m 序列提取位同步时钟信号;显示屏模块用于频率显示;键盘控制模块用于控制键盘。

该方法及装置利用m序列的自相关性质和新型锁相环方法,实现100kHz‑350kHz信号的位同步时钟提取,系统工作稳定。

申请人:武汉大学

地址:430072 湖北省武汉市武昌区珞珈山武汉大学

国籍:CN

代理机构:武汉科皓知识产权代理事务所(特殊普通合伙)

代理人:彭艳君

更多信息请下载全文后查看。

基于FPGA位同步时钟提取方案的设计

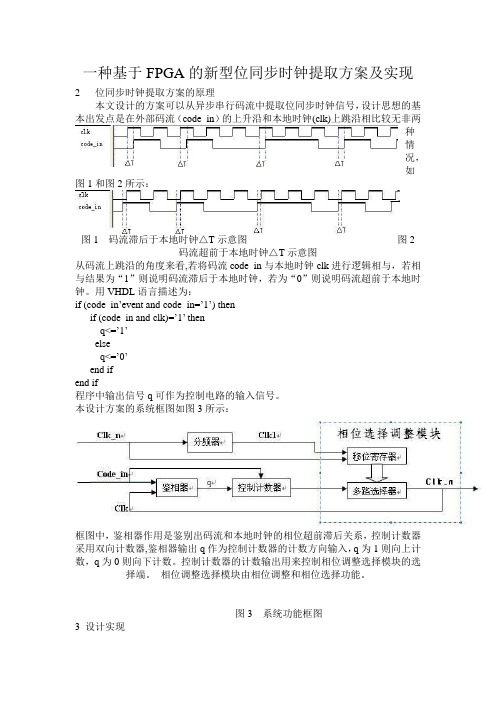

一种基于FPGA的新型位同步时钟提取方案及实现2 位同步时钟提取方案的原理本文设计的方案可以从异步串行码流中提取位同步时钟信号,设计思想的基本出发点是在外部码流(code_in)的上升沿和本地时钟(clk)上跳沿相比较无非两种情况,如图1和图2所示:图1 码流滞后于本地时钟△T示意图图2码流超前于本地时钟△T示意图从码流上跳沿的角度来看,若将码流code_in与本地时钟clk进行逻辑相与,若相与结果为“1”则说明码流滞后于本地时钟,若为“0”则说明码流超前于本地时钟。

用VHDL语言描述为:if (code_in’event and code_in=’1’) thenif (code_in and clk)=’1’ thenq<=’1’elseq<=’0’end ifend if程序中输出信号q可作为控制电路的输入信号。

本设计方案的系统框图如图3所示:框图中,鉴相器作用是鉴别出码流和本地时钟的相位超前滞后关系,控制计数器采用双向计数器,鉴相器输出q作为控制计数器的计数方向输入,q为1则向上计数,q为0则向下计数。

控制计数器的计数输出用来控制相位调整选择模块的选择端。

相位调整选择模块由相位调整和相位选择功能。

图3 系统功能框图3 设计实现依据图3系统功能框图,利用Altera 公司的Quartus II 设计软件,采用自顶向下的模块化设计方法,用VHDL 语言和电路原理图混合输入设计对位同步时钟提取电路的各个部件分别进行设计。

本设计方案的鉴相器原理相对简单,不需要用VHDL语言设计,仅用两个与门和一个D触发器就可以实现,如图4 所示。

图中的的第二个与门(inst23)是为了实现D触发器的时钟输入端与数据输入端同步。

控制计数器设计使用QuartusII的MegaWizard Plug_InManager工具来实现一个简单的双向数器,计数方向由鉴相器输出q控制,q为1则计数器向上计数,q为0则计数器向下计数,计数系数由Count Modulus设定,设定的数值要求等于分频器的分频系数N。

fpga行同步信号场同步信号

FPGA(现场可编程门阵列)中的行同步信号和场同步信号是用于控制图像数据传输的信号。

行同步信号表示一行像素数据的起始和结束,而场同步信号表示一幅完整图像的开始和结束。

这些同步信号通常由图像采集设备生成,并作为输入信号传输到FPGA中。

在FPGA中,行同步信号和场同步信号可用于控制图像数据的读取和处理,以确保数据传输的正确性和完整性。

通过使用这些同步信号,FPGA可以准确地识别图像数据的起始和结束位置,以及处理每一行和整个图像的像素数据。

此外,FPGA还可以生成行场同步信号,以控制图像的显示或输出。

例如,VGA(视频图形阵列)接口中的行同步信号、场同步信号和像素时钟信号就是由FPGA生成的,用于控制VGA显示器的显示。

总而言之,行同步信号和场同步信号在FPGA图像处理中发挥着至关重要的作用,它们是确保图像数据正确传输和处理的关键因素。

基于FPGA的基带信号的位同步信号提取(附程序)【毕业设计论文】

xxxx学院毕业设计论文题目:基于单片机和FPGA的位同步信号提取专业班级:电子信息工程学生姓名:学号:完成日期:指导教师:评阅教师:2006 年6月湖南工程学院应用技术学院毕业设计(论文)诚信承诺书本人慎重承诺和声明:所撰写的《基于单片机和FPGA的位同步信号提取》是在指导老师的指导下自主完成,文中所有引文或引用数据、图表均已注解说明来源,本人愿意为由此引起的后果承担责任。

设计(论文)的研究成果归属学校所有。

学生(签名)年月日湖南工程学院应用技术学院毕业设计(论文)任务书设计(论文)题目:基于单片机和FPGA的位同步信号提取姓名专业电子信息工程班级 0281 学号 16指导老师刘正青职称实验师教研室主任刘望军一、基本任务及要求:本课题是设计一具有通用性的输入信号的位同步提取系统,系统可以实现10HZ~1MHZ的信号同步。

使用单片机进行实时控制现场可编程逻辑门阵列FPGA完成位同步信号提取,通过理论和实验研究,完成硬件电路和软件设计并试制样机,要求完成:1、单片机实时控制FPGA,完成实时频率跟踪测量和自动锁相;2、在FPGA 内部,设计完成以下部分:A、全数字锁相环DPLL,主要包含:数控振荡器、鉴相器、可控模分频器B、LED动态扫描电路、FPGA和单片机的数字接口,以完成两者之间的数字传递3、设计辅助电路:键盘、LED;二、进度安排及完成时间:(1)第二周至第四周:查阅资料、撰写文献综述和开题报告;(2)第五周至第六周:毕业实习;(3)第六周至第七周:项目设计的总体框架:各个模块以及各个模块之间的关系确定,各个模块的方案选择与各个模块的所用主要器件的确定;(4)第八周至第十三周:各个模块的主要器件熟悉及相关知识的熟悉;各个模块的具体任务实现:硬件电路、软件编程;(5)第十四周至第十五周:系统的总体仿真与调试(6)第十六周至第十七周:撰写设计说明书;(7)第十八周:毕业设计答辩;目录摘要........................................................................................................ 错误!未定义书签。

fpga位同步信号提取

FPGA位同步信号提取1. 简介FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,能够根据用户的需求进行重新配置,实现各种不同的数字电路功能。

在FPGA设计中,位同步信号提取是一个重要的任务,它能够从输入信号中提取出同步信息,用于控制和协调各个模块之间的操作。

本文将介绍FPGA位同步信号提取的原理、方法和实现步骤,并且详细说明如何使用FPGA设计工具进行开发。

2. 原理在FPGA设计中,通常会涉及到多个时钟域(clock domain),每个时钟域都有自己的时钟信号。

由于不同时钟域的时钟频率可能不同,因此需要一种机制来确保数据在不同时钟域之间正确地传输和处理。

这就是位同步(bit-level synchronization)的概念。

位同步信号提取就是从输入信号中提取出用于位同步的控制信息。

这些控制信息通常包括数据有效性标志(valid flag)和数据使能标志(enable flag)。

通过这些标志,可以确定数据何时有效以及何时可以被处理。

3. 方法3.1 插入寄存器为了实现位同步信号提取,通常需要在输入信号路径上插入寄存器。

寄存器能够将输入信号同步到目标时钟域的时钟边沿,确保数据在时序上的正确性。

具体方法是,在输入信号路径上插入一个寄存器,并将寄存器的时钟与目标时钟域的时钟相连接。

这样,输入信号就会在目标时钟边沿被锁存,从而达到位同步的效果。

3.2 控制逻辑设计除了插入寄存器外,还需要设计控制逻辑来提取位同步信号。

控制逻辑通常包括状态机(state machine)和组合逻辑电路。

状态机用于控制数据有效性标志和数据使能标志的生成和更新。

它根据输入信号的状态和当前状态来确定下一状态,并输出相应的控制信号。

组合逻辑电路用于根据输入信号和当前状态来生成数据使能标志。

它可以根据需要进行逻辑运算、比较操作等,以判断数据是否有效并生成相应的使能标志。

3.3 时序约束设置为了确保FPGA设计满足时序要求,需要设置正确的时序约束。

基于FPGA的人体通信中位同步提取电路的设计

De i n o ta tn r u tf r Bi y c r n z to sg fEx r ci g Cic i o tS n h o ia in

A sr c : c odn ot e c a a tr t s o u n c a n l l e ta t n c c i o l dgtlp a e~lc e i s n h o i t n b s d b t a t A c r ig t h h r cei c fh ma h n e ,al xr c o i ut f l i i h s s i i r a a o k d bt y c r nz i a e ao

o n r — o y Co m un c t n b s n FPGA fI t a— b d m i ai a eo o

W ANG e , W n1 GAO Yue dn  ̄ , n g CHEN d n  ̄, N ha h ng Yi o g PA S o e

p ro ma c Al Di a h s e r n e; l tlP a e— L c e o p;Bi S n h o iain f o k dL o t y c rn z t o

1 引 言

人体 通 信 (n a oycm ui tn B ) 一 it —bd o m nc i ,IC 是 r ao 种新 兴 的短距 离 通 信方 式 , 1 在穿 戴 式 医疗 监 护 领 ] 域 中具 有广 阔的应用 前 景 。IC将 人 体 作 为 电信 号 B

cruti u tbe o h s i i s i al c s fr p a e— t c i g n a p as q ik a n hn , s H IO S n ih p e i o . A d t s g aa te r te r k n a d p e r uc lu c ig ma eT F a a d hg r cs n i n i u r ne i d f h o

DSSS接收机中PN码同步的FPGA实现

PN Synchronization in DSSS Receiver Based on FPGA

X U Fang, M EI Xiao , L I Si

( Mo dern Co mmunicat ion Research Inst it ut e, B eijing Jiaot ong Univ ersit y, B eijing, 100044, C hina)

微电子技术

徐

芳等 : DSSS 接收机中 PN 码同步的 F PGA 实现

DSSS 接收机中 PN 码同步的 FPGA 实现

徐 芳, 梅 晓, 李 司

北京 100044) ( 北京交通大学 现代通信研究所

摘 要 : P N 码同步是直接序列扩频通信系统实现正确解调的首要条件 , 由于发送端和接收端的时钟不同所造成的码片相 位偏移将影响到传输数据的正确接收 , 因此根据 PN 码良好的自相关特性 , 提出了一种在基带数字信号处理中基于 FPGA 的能 有效锁定发送端和接收端时钟, 实现 PN 码同步的方案。 并结合系统框图具体分析了同步 捕获和跟踪中各个模 块的功能和实 现方法 , 跟踪模块中涉及到模拟电路部分的也给出了具体的电路设计 , 最后说明了调试过程中的一些问题及解决技巧 。 关键词 : 同步捕获 ; 跟踪 ; 模拟 PL L; FP GA 中图分类号 : T N919. 3 + 4 文献标识码 : B 文章编号 : 1004 373X( 2006) 06 114 03

图1

同步捕获和跟踪框图

由于在同步捕获中对捕获时间的要求不是 很严格, 而 且所用的正交 m 序列的周期是 2 048, 属于短 PN 码, 所以 采用了串行滑动 相关捕 获方式。 现假设 发送端 和接 收端 都是 32. 768 M H z。如图 1 中发送端是由一个二分频模块 和一个 2 048 位的 正交 m 序列。采 用二分 频模块的 原因 是, 根据奈奎斯特准则, 接收端的 A/ D 采 样频率至 少是发 送信号速率的 2 倍, 因此, 发 送端数 据的 速率至 少应 是系

一种抗衰落的位同步设计和FPGA实现

Ab t a t I te to o c te o sr c n h r p s at rc mm u c to tlw ae o du r t , tsn h o iain u e y mo e i s al xr ce rm niain a o r t rme im a a bi y c r nz t sd b d m s u u ly e ta t fo e o d te e v l p a o ti ss c r nz t n ifr to Tog a a te teSNR fs c rnz to in l i e sag e tlto PGA e o re fr h n eo e t tc nan y h o ia o no ma n. u rne h n i i h o y ho ia nsg a ,tn e ra o fF n i d rs n c o a o t g te pe iu to F rti rbe , m p  ̄s a d a ay s a t fd n y c rnz to do n me Sfy d pi r vo smeh d, o hs po lm we p o n n l ̄ a i a i g s h o ia n me d, a d a whe l whih i n h n n - n i i l e , c s smpe a mpe ne a f Ths p p rn to l k sa d ti d s rpin o e aih t h o y o h sme o b tas e ie h i i l nd i lme td e l S y. i a o ny ma e ea e c it ft rtme c te r fti d d, u lo ra z st e bt e l o h i i l

一种基于FPGA的位同步时钟提取电路

方 案一 : 采 用 通 用 的 M CU 。 采 用 微 处 理 器 作

厂 .

为 核 心 处 理 器 可 以 缩 小 系 统 规 模 且 灵 活 性 较 高 。但

是 考虑 到 对输 出 同步 信 号 的稳 定性 的要 求 , 微 处 理 器 的计 算 能力 并不 能达 到要 求 。 方 案二 : 采 用 FP GA 。 采 用 现 场 可 编 程 门 阵 列 ( FP GA ) 作 为 核心处 理 器 。 FP GA 目 前 广 泛 应 用 于 通 信 系 统 之 中 , 可 以 同 时 提 供 强 大 的 计 算 能 力 和 足 够 的 灵 活 性 。 因 此 选 用 此方 案 是一 个 比较好 的选 择 。

率为 n F( Hz ) , 整形 之后 输 出频率 为 n F( Hz ) 的 窄 带

脉 冲 , 如 果 接 收 端 晶 振 输 出 n次 分 频 之 后 不 能 准 确

位 时 钟 自同 步 的 实 现 方 法 分 为 测 周 法 , 滤 波 法

( 波形 变换 法 ) , 开 环 同步法 和 闭环 同步 法 ( 锁 相 环 ) 。

晶振经过整形之后再送入分频器输出位同步脉冲序设码元的速率为fhz晶振的频率为nfhz整形之后输出频率为nfhz的窄带脉冲如果接收端晶振输出n次分频之后不能准确地和码元同步相位比较器就会输出误差信号通过控制器进行调整直到同步为止

2 0 1 7年 4月 第 7期 总 第 3 7 7期

内 蒙 古 科 技 与 经 济

地和码 元 同步 , 相 位 比较 器 就 会 输 出 误 差 信 号 , 通 过

控制 器进 行调 整 , 直到 同步 为止 。

方 案一 : 测 周 法 。 测 周 法 是 根 据 输 入 的 码 元 的 周期来 计 算 发送 信 号 的频 率 , 然 后 提 取 信 号 的 上 升 沿实现 与 发送 的码 元 同步 。 从 而实现 位 同步 。

fpga位同步信号提取

FPGA位同步信号提取1. 引言FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以通过编程实现不同的电路功能。

在许多应用中,需要对FPGA进行位同步信号提取,以确保各个模块之间的数据传输和处理的准确性和一致性。

本文将详细介绍FPGA位同步信号提取的原理、方法和实现过程。

2. 原理在FPGA中,位同步信号提取是指从输入数据中提取一个用于同步各个模块的时钟信号。

这个时钟信号通常由一个稳定的时钟源产生,并被分配给FPGA内部的各个模块。

位同步信号提取有两个主要任务:检测输入数据中的时钟边沿,以及生成一个与输入数据频率相匹配的稳定时钟。

2.1 时钟边沿检测在FPGA中,通常使用触发器来检测输入数据中的时钟边沿。

触发器是一种存储元件,在时钟上升沿或下降沿触发时将输入数据存储到输出端口。

通过检测触发器输出端口的变化,可以确定输入数据中是否存在时钟边沿。

常见的触发器类型包括D触发器、JK触发器和T触发器。

这些触发器可以根据需要进行级联,以实现更复杂的时钟边沿检测功能。

在FPGA中,可以使用硬件描述语言(如Verilog或VHDL)来描述和实现这些触发器电路。

2.2 稳定时钟生成一旦检测到输入数据中的时钟边沿,需要生成一个稳定的时钟信号,并将其分配给FPGA内部的各个模块。

稳定的时钟信号通常由一个PLL(Phase-Locked Loop)电路来生成。

PLL是一种反馈控制系统,可以根据输入参考时钟的相位和频率来生成一个稳定的输出时钟。

PLL通常由相位比较器、环形振荡器和反馈回路组成。

相位比较器用于比较输入参考时钟和反馈时钟之间的相位差,并产生一个控制信号。

环形振荡器根据控制信号调整自身的振荡频率,使得反馈时钟与输入参考时钟保持同步。

通过不断调整振荡频率,PLL能够自动消除相位差,并生成稳定的输出时钟。

3. 方法在FPGA中实现位同步信号提取有多种方法,下面将介绍两种常用的方法:基于触发器的位同步信号提取和基于PLL的位同步信号提取。

基于ofdm技术的plc通信系统中同步算法的研究及其fpga实现

东南大学硕士学位论文基于OFDM技术的PLC通信系统中同步算法的研究及其FPGA实现姓名:***申请学位级别:硕士专业:信号与信息处理指导教师:***20060601东南人学颀I‘学位论文图3.6M(玎)的形状曲线在接收端,当接收机发现M(门)的输山值在一段时间内保持大于某个门限时,则认为有信号到达,于是在随后的一段时间内搜索膨(撑)的最大值,认为最大值处为帧头起始点。

其实。

这个晟大值只要落入上图所示的平坦区域,则认为帧头被正确捕获。

虽然从某种角度来说,这个帧头捕获函数具有一定的模糊性,但是它实现简单,可以最快得捕捉帧头,并且并不影响后面频偏估计等子同步算法。

而随后还有精细同步模块来给出精确的定时位置。

存在频偏和高斯噪声时的包头捕获前面提到在设计合理的同步方案时需要考虑到时偏和频偏的相互影响,如定时的准确是以频率偏移己纠正为前提条件,频率偏移的估计算法又是以定时准确为前提等;帧头捕获是实现同步功能的第一块,因此不希望它的性能是以其他同步子模块为前提的。

本文中所使用帧头捕获方式确实可以做剑。

设接收到的信号,(厅)受频偏△厂=p+D);和高斯噪卢V∽)影响,。

是离号争最近的整数,s为纯小数,且川≤0.5。

,(以):(s(一)+v(玎))P埘勺nT:(J(一)+v(行))P肺寻(式3—2)州=芝Ⅺ+向,o+t+加“(式3-3)=丑I《H+七)12协+置矿(H+t+肋+'伽+宣心("+t+^D+’伽+七)v+(H+t+加】,“R(”):N-I∑lr(n+k)lz:篁I(so+Ji})+,伽+七))e’2”警IzR(”)=2=∑㈨月+Ji})+V(月+七))e”8可r…k=O(式3—4)=∑IJ(月+t)+v(n+女)12东南人学颀I学位论文胄。

(”)=∑I,("+女+Ⅳ)J2=∑㈨Ⅳ+t+Ⅳ)+v如+k+N))eS2'w!ff-一“‘。

(式3-5)=∑lJ(Ⅳ+女)+v(n+☆)12由上面二个式张明,帧头捕获函数肘(玎)2丽IP砰(n)洄[2不含与频偏有关的囚子,所以其函数形状主要受-姨头训练符号自身的统计特性和噪卢影响,而与频偏无关。

pi_4_DQPSK调制解调位同步算法及其FPGA的实现_冯娟

1 调制解调的原理

π/4-DQPSK 信号星座图和原理框图分别图 1 和图 2 所 示 。可看出 π/4-DQPSK 的最大相移为 3π/4 ;带限的 π/4DQPSK 的包络波动较小 ;非线性信道频谱扩散不严重 ;当 有多径衰落存在时 , 它的工作敏感性小 ,有利于信号传输 。

图 1 π/ 4-DQ PSK 信号星座图

-0 .707

-3π/ 4

0

0

-0 .707

0 .707

3π/ 4

0

1

0 .707

-0 .707

-π/ 4

1

0

0 .707

0 .707

π/ 4

1

1

2 Gardner 算法计算定时误差

Gardner 算法计算式如下所示 :

time

error(t)= y I(t

-

1 2

T c)×[

yI(t)-yI(t -Tc)]

yI(t) = cos[ θ(t)+ Δθ] = cosθ(t)cosΔθ- sinθ(t)

sin Δθ=yI (t)cos Δθ-yI (t)sin Δθ

(3)

yQ(t)=sin[ θ(t)+Δθ] =y I(t)sin Δθ+yQ(t)cosΔθ

(4)

将

式(3)和式(4)代入

式(2)得到

:u(t)

(n Ts

-1 2

Tc ) ·

y1 (n Ts)-y1 (nTs -Tc)

+y

Q(n

T

s

-1 2

T c)·

yQ(n Ts)-yQ(n Ts -Tc)

归一化后得到 :

(6)

基于FPGA同步电路的实现

为所 有 的触 发器 的时钟端都 接在 同一 个主时钟 上。 相 比异 步设 计 来说 ,同步设 计 有许 多 的优 点 , 同步 是通 信系统 中一 个重要 的问题 。在 数字通信 中 ,

性 ,以及 提 高 硬件 开 发 的速 度 和 降 低 系统 的成 本 。

eF G w P A的同有优点使 其得 到越来越 广泛 的应用 。 对于 FG P A设 计 ,同步 设 计 将 优 于异 步 设 计 。

rd c h ur n ierr ae (E ). e u eteb r a dbt r t B R or

K e r s F GA; i s n h o iain P L y wo d : P bt y c rn zt ; L o

1 引 言

近年 来 ,随着 超大 规 模 集成 电路 的发展 ,F — P G / P D等可 编程逻 辑器 件 的资源也 有 了极大 的发 AC L 展 ,F G P A在开 发 阶段 具 有安 全 、方 便 、可 随 时修 改 设 计 等不 可替 代 的优 点 ,在 电子 系统 中采 用 F — P G A可 以极 大 地 提升 硬件 系统设 计 的灵 活性 、可 靠

LU R -i I uj n (E R I u n zo 6 0 hn) C P E ,G a gh u5 0 1 ,C ia 1

Ab ta t S n ho i t n s i o h mao at n o mu iai s B s e cr e sr c : y crnz i i l f e ao oe t jr r i p s cm nct n . ei s ar r o d i

一种基于FPGA精确位同步的设计与实现

Q , = ( )o( 坤 D+ ( )i( 坤 D+ 2 (1 6 , cs ) 1 ) 口, 8 1 n )n

() 2

() 3

为了消除剩余频率 偏移 , 以通过坐标旋转 , 可 则有 :

,(1_(1cs + ( )i( ) , J, o( Q n s t ) ) ) np

式可表示为 :

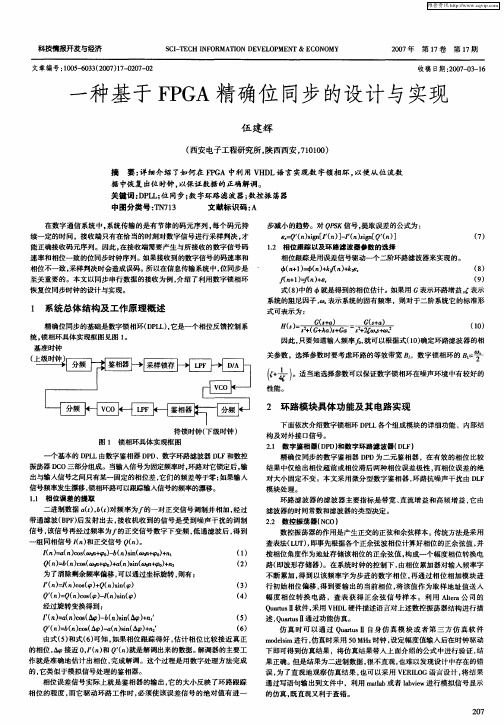

1 系统总体 结构 及 工作原 理概 述

精确位同步的基础是数字锁相环( P L , 一个相位反馈控制系 D L )它是 统, 锁相环具体实现框图见图 l 。

基准时钟

肌) = 器 =

() - 0

因此 , 知道输入频率 , 只要 就可 以根据式( 0 确定 环路滤 波器的相 1)

维普资讯

科技情报开发与经济

文章编号:0 5 6 3 (0 7 1- 27 0 10 — 0 3 2 0 )7- 0 - 2 0

S IT C F R A IND V L P E T&E O O Y C-E HI O M TO E E O M N N CN M

20 年 第 l 卷 第 l 期 07 7 7

收稿 日期:0 7 0 —1 20- 3 6

一

种基 于 F G P A精确位 同步 的设计 与实现

伍 建辉

( 西安 电子工程研究所 , 陕西西安 ,1 10 700 )

摘 要 : 细介 绍 了如何 在 F G 中利 用 V L语 言实现 数字锁相环 , 详 PA HD 以便从位流数

() 7

1 相位跟踪以及环路滤波器参数的选择 . 2

相位跟踪是用误差信 号驱动一个二阶环路滤波器来实现 的。

6 n 1= ( ) ,1 (+ ) , “l, 1 ()

FPGA_ASIC-基于FPGA的快速位同步系统设计

基于FPGA的快速位同步系统设计管立新(赣南师范学院电子信息学院 江西赣州, 341000)摘 要:从时分复接系统对位同步系统的性能要求出发,提出了一种基于FPGA的快速位同步系统的设计方案,给出了位同步系统的实验仿真,结果表明该系统有较快的位同步建立时间,节省了FPGA的耗用资源,系统工作稳定、可靠。

关键词:位同步;同步建立时间;现场可编程门阵列;仿真中图分类号:TP311;TN919 文献标识码:AFast Bit Synchronization System Design Based on FPGAGUAN Li-XinElectronic Information Science Department Of Gannan Teacher’s College,GanZhou JiangXi, 341000,china Abstract: According to the performance requirement of bit synchronization in Time Division Multiplexer system, the paper proposed a method to design fast bit synchronization system based on FPGA. The imitation and experiment of bit synchronization system were given, experiment result shows, the system can build synchronization quickly, the circuit work stably and reliable.Keywords: Bit synchronization;Synchronization Build Time;FPGA;Imitation1 引言在时分复接通信系统中,位同步是收、发两端的时钟频率必须同频、同相,这样在接收端才能正确地判决发送端送来的每一个码元。

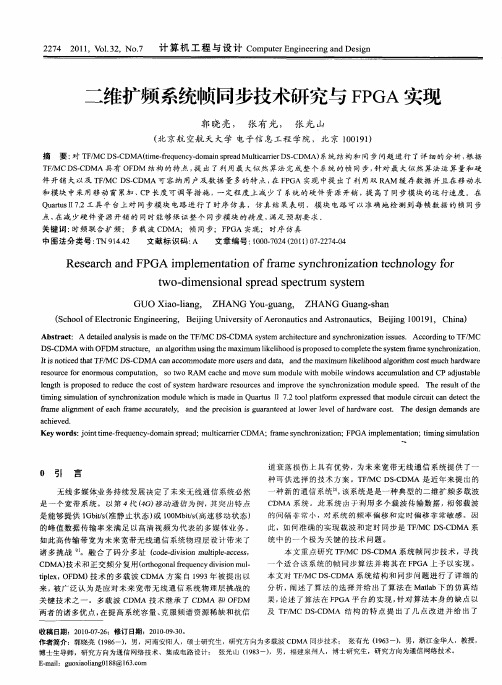

二维扩频系统帧同步技术研究与FPGA实现

关 系 着 整 个通 信 系 统 的 性 能 。 没 有 准 确 的 同 步 算 法 , 不 能 就

1 T / SC M A 系 统 分 析 FMC D — D

T / —D FMCDSC MA 的 结 构 如 图 1 示 。 显 然 ,FMC D - 所 T / S

进 行 可 靠 的数 据 传 输 , 是 信 息 可 靠 传 输 的 前 提 。 F CDS 它 T/ M —

一

种 新 的通 信 系 统 , 系 统 是 是 一 种 典 型 的 二 维 扩 频 多 统 由 于利 用 多 含 载 波 传 输 数 据 , 邻 载 波 榴

的 间 隔 非 常 小 ,对 系 统 的 频 率 偏 移 和 定 时 偏 移 非 常 敏 感 。 因

a he e . c iv d

Ke rs ji mef qe c-o i sra ; lcre D y wo d:ont —e un yd ma ed mut ar r MA; a n ho i t n F G pe nai ;i n muao ti - r - np i iC r f me y c nz i ; P Ai l s r ao m me t o t g i l in t n mi s t

rsuc r n r u o p tt n S M ah dmo e u mo ue t bl wn o cu l inadC dut l eoref omo s m uai , Ot R oe c o woA ccea v m d lwi mo i id ws cmua o n Pajs be n s h e a t a

Ab t a t A ea lda ay i d n t eT / C DS CDM A y tm r h t cu ea d s n h o i ai nis e . Ac o d n F M C sr c : d t i n l ss s e i ma eo F M — h s se a c i tr n y c r n z t u s e o s c r i gt T / o

基于三角函数内插法的Gardner位定时同步环的FPGA实现

d l

r n l 1 O l , d - , ' 3钠

¨ m

o

州 女 q

・ ' 1 q n . 41 1硼

| I 口

■

哪

.

o 住 o l

di n ( 1  ̄铷

” O l

● 1 1 q m | 1 O I

而使信号尽可能地接近 最佳采样点

∥ )

图 1 位 定 时环 路 结 构

样得到, 从而影响后续 觯调判决结果。 这就需要对采样信号 2 F P GA 实现 及 其Mo d e l s i m仿 真 进行处理, 获得最佳 采样点。 G a r d n e r 等通过分析异步采样对 F P G A 实现 的顶层 框 图如 罔2 所 示, 由三 角函数 插值 滤 波 全数: 接收机带来的影响, 提出了 基于内插的同步算法。 器、 定时 误差检测、 环路滤 波、 插值控制等部分组成。本文 本 文针 对 实 际 系 统 的 需求 , 搭 建了 一科 , 适 用十 P S K 的 通 仿真采用了B P S K调制方式, 升 余弦滤波器的滚降系数为1 , 用的Ga r d n e r 位 定时 同步 电路 。 其 中的插 值滤波 器采用 了 采样数 据经过 与发端一致 的平方根升 余弦匹配滤波器, 采 实现结 构简单, 内插精度高, 适 合于F P GA 实现的三角函数 样速率为每 个符号4 个采样点, 设置本端采样周期与 1 / 4 个符 内插算 法。 在Mo d e l s i m上 对该 电路进 行了仿真, 并进 行了 号周期相比较偏小的T / 5 1 2 。 具体模块描述如下。 F P G A实现 。 该力‘ 案已经 应 用于实

的值 。

图2 F P G A实 现顶 层

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要同步是通信系统中很重要的一个过程,它可以使通信系统更稳定、更可靠、更准确,它是数字通信系统有顺序进行的技术支撑。

同步分为位同步、帧同步和载波同步,我们对数字通信信号的同步除了载波同步和帧同步之外,还要进行位同步。

位同步也就是保证接收端准确有效抽样判决数字基带信号序列的基础,一般位同步信号从解调后的基带信号中提取出来,同时也可以从已调频带信号当中直接提取位同步信号,一般可以进行一元中央位置采样的决定,最好是在接收元素结束时间采样的决定。

位同步有插入导频法(一种外同步法)和直接法(一种自同步法),本文运用了数字锁相法提取位同步电路的方案,以大规模可编程逻辑器件FPGA为主控制器,以VHDL硬件描述语言为主要语言对其进行在线编程,在QuartusⅡ软件工具中进行仿真和调试,以达到功耗低、成本低、效率高的技术要求。

关键词:位同步;数字锁相电路;FPGA;VHDL;QuartusⅡABSTRACTSynchronization is a very important process in communication system, it can make the system more stable, more reliable, more accurate, it is the digital communication system has the technical support of the order. Synchronization is divided into bit synchronization, frame synchronization and carrier synchronization, we on the digital communication signal in addition to frame and carrier synchronization and bit synchronization. Bit synchronization is the basis to ensure the correct and effective decision receiver sampling digital baseband signal sequence,general synchronization signal is extracted from the baseband demodulated signals, but also can directly extract bit synchronization signal from the frequency band signal has, in general can be a central position sampling decisions, preferably in the receiving elements in the end time sampling decision. Bit synchronization is the pilot insertion method (a kind of external synchronization method) and direct method (a self synchronizing method), this paper uses digital PLL method of bit synchronization circuit extraction, with the large-scale programmable logic device FPGA as the main controller, using the VHDL hardware description language is the main language of the online programming, simulation and debugging in QuartusⅡsoftware tools, to meet the requirements of low power consumption, low cost, high efficiency technologyKeywords: Bit synchronization (symbol extraction process); digital phase locked loop circuit (bit synchronization circuit); FPGA; VHDL; QuartusⅡ目录摘要 (I)ABSTRACT (II)第1章绪论 (1)第2章同步技术 (3)2.1 同步技术 (3)2.2 同步的分类 (3)2.3 位同步 (3)2.3.1 位同步方法 (4)2.3.2 位同步系统性能指标 (5)第3章基于FPGA设计流程的介绍 (7)3.1 FPGA器件概述 (7)3.2 FPGA设计操作流程 (7)第4章微分型位同步的FPGA实现 (11)4.1 微分型位同步原理 (11)4.2 微分鉴相模块的VHDL实现 (12)4.3 双相时钟信号的VHDL实现 (16)4.4 单稳触发器的VHDL实现 (17)4.5 控制及分频模块的VHDL实现 (19)第5章系统仿真与结果分析 (21)5.1 顶层模块的VHDL实现 (21)5.2 系统的整体仿真与结果分析 (24)结论 (25)参考文献 (26)致谢 (27)第1章绪论在数字通信系统中,要准确的恢复信号,接收端和发送端就必须保持严格同步。

在数字通信系统中,同步又称为定时,是指收发双方在时间上保持步调一致。

同步系统性能的优劣将直接影响数字通信的质量,甚至会影响数字通信能否正常运行。

可以说同步系统是保证数字通信系统正常工作的前提。

早在1970那一年,胎膜早破(可编程只读存储器)是最古老的PLD的出现,它是可编程的只读存储器,它不能被擦除和重写,只能写一次,而在20世纪70年代中期,又出现了PLA(Programmable Logic Array),也就是可编程逻辑阵列。

可编程阵列逻辑PAL(可编程逻辑阵列)1977美国AMD装置第一,这是一个熔丝编程。

大约在1985年,Lattice公司率先发明GAL(Generic Array Logic),也就是通用阵列逻辑器件,该装置可电擦除,可编程,设置加密位PLD等,然而Altera 公司推出最晚的却是可擦除可编程逻辑器件—EPLD(Erasable PLD),它是在20世纪80年代中期推出的。

880年底,格是在系统可编程技术提出了ISP(在系统编程),它还推出了一系列的在系统可编程逻辑器件(EPLD器件)。

1985现场可编程的概念被首次提出,赛灵思公司,在同一时间,世界上第一个生产的FPGA (现场可编程门阵列,现场可编程门阵列)装置。

而在1995年,Xilinx公司又推出了XC4025,它的可用门数达到了25000门。

PLD的分类:(1)PROM 即可编程只读存储器(Programmable Read Only Memory)(2)可编程逻辑阵列PLA(Programmable logic array PLA)(3)可编程逻辑阵列PAL(Programmable logic array PAL)(4)通用逻辑阵列GAL(Generic array logic GAL)(5)即可擦除可编程器件EPLD (Erasable Programmable Logic Device)(6)复杂可编程逻辑器件CPLD (Complex PLD)(7)即现场可编程门阵列FPGA(Field Programmable Gates Array)现场可编程门阵(FPGA)是PAL、GAL、EPLD等可编程器件的进一步发展的产物。

它是作为ASIC领域中的一种半定制电路而出现的,不仅克服了原本可编程器件门电路门数量有限等缺点,还解决了定制电路的不足。

在第二十世纪中叶80年代,FPGA是一种高密度可编程逻辑器件,数组类型,它和我们以前所介绍的可编程逻辑器件是有所不同的。

FPGA由逻辑功能块排成阵列组成,还有可编程的互连资源连接等这些逻辑功能块以及还有相应的输入\输出单元来共同实现不同的设计。

这其中,FPGA的功能是由逻辑结构的配置数据而决定。

同时,存储在片上SRAM 或熔断器的配置数据。

基于SRAM 的FPGA 器件,同时,存储在片上SRAM 或熔断器的配置数据。

用户可以控制加载过程,在现场修改器件的逻辑功能,即所谓的现场可编程。

Quartus Ⅱ8.0是Altera 公司新近推出的EDA 软件工具,其设计工具完全支持VHDL 、Verilog 的设计流程,其内部嵌有VHDL 、Verilog 逻辑综合器。

第三方的综合工具,如Leonardo Spectrum 、Synplify Pro 、FPGA Compiler Ⅱ有着更好的综合效果,因此通常建议使用这些工具来完成VHDL/Verilog 源程序的综合。

Quartus Ⅱ可以直接调用这些第三方工具。

同样,Quartus Ⅱ具备仿真功能,也支持第三方工具,如Modelsim 。

此外,Quartus Ⅱ为Altera DSP 开发包进行系统模型设计提供了集成综合环境,它与MATLAB 和DSP Builder 结合可以进行基于FPGA的DSP 系统开发,是DSP 硬件系统实现的关键EDA 工具。

Quartus Ⅱ还可以与SOPCBuilder 结合,实现SOPC 系统开发本文主要研究一种位同步电路的FPGA 实现,其研究的主要内容是:理解位同步的概念及实现方法,建立位同步控制器模型,以FPGA 为主控器,设计一个位同步控制器,并完成各模块电路测试激励程序的设计。

任务:(1)掌握常用的位同步方法及实现原理;(2)完成微分型位同步的设计与仿真;(3)完成积分型位同步的设计与仿真;(4)建立数字锁相环法仿真模型并完成功能仿真;(5)完成数字锁相环法位同步的设计与仿真;技术要求:(1)完成测试激励信号源的设计;(2)相位误差 C ︒≤1e θ;(3)同步带宽KHz f 1≥∆;第2章同步技术2.1 同步技术在数字通信系统中,要准确的恢复信号,接收端和发送端就必须保持严格同步。

在数字通信系统中,同步又称为定时,是指收发双方在时间上保持步调一致。

同步系统性能的优劣将直接影响数字通信的质量,甚至会影响数字通信能否正常运行。

可以说同步系统是保证数字通信系统正常工作的前提。

2.2 同步的分类同步是通信系统中很重要的一个过程,它可以使通信系统更稳定、更可靠、更准确,它是数字通信系统有顺序进行的技术支撑。