CRC校验码的原理

crc的基本工作原理

crc的基本工作原理CRC(Cyclic Redundancy Check)是一种常用的差错检测技术,其基本工作原理是通过对数据进行多项式除法运算来生成冗余校验码,并将该校验码附加在数据后面,以便在数据传输过程中检测出可能存在的错误。

CRC的基本原理是将数据视为一个二进制数,并选择一个固定的生成多项式,通常称为CRC多项式。

生成多项式的选择是非常重要的,不同的生成多项式会导致不同的检错能力。

常用的CRC多项式有CRC-8、CRC-16和CRC-32等。

在进行CRC校验前,发送方和接收方首先要约定好使用的生成多项式。

发送方在发送数据时,会先对待发送的数据进行一系列的处理,具体步骤如下:1. 将待发送的数据表示为二进制形式,以比特位为单位进行处理。

2. 在待发送的数据后面添加一定数量的0,具体数量由生成多项式的位数决定。

这些0是为了计算冗余校验码所需的。

3. 用生成多项式对上一步得到的数据进行除法运算,求得的余数即为冗余校验码。

4. 将冗余校验码附加在原始数据的末尾,形成最终的发送数据。

接收方在接收到数据后,会进行CRC校验,具体步骤如下:1. 将接收到的数据表示为二进制形式。

2. 用生成多项式对接收到的数据进行除法运算,得到的余数。

3. 如果余数为0,则说明数据没有发生错误;如果余数不为0,则说明数据中存在错误。

CRC的优点是简单、快速和高效。

通过在数据传输过程中附加冗余校验码,可以有效地检测出数据传输过程中可能出现的错误,如位翻转、插入和删除等。

而且,CRC所需的计算量相对较小,适用于各种不同的数据传输场景。

然而,CRC也有一些局限性。

首先,CRC只能检测错误,而无法纠正错误。

其次,CRC的检错能力有限,无法检测到一些特定类型的错误。

此外,CRC对于数据长度较短的情况下,可能会出现误判的情况。

为了提高CRC的检错能力,可以采用一些增强型的CRC算法,如CRC-CCITT、CRC-16-CCITT和CRC-32-CCITT等。

CRC校验码原理

CRC校验码原理CRC(Cyclic Redundancy Check)校验码是一种常用的差错检测方法,广泛应用于数据通信领域,用于检测数据传输中是否发生了错误。

CRC校验码是通过对数据进行一系列计算产生的,可以有效地检测多种常见的差错。

本文将详细介绍CRC校验码的原理。

CRC校验码的原理是通过多项式的除法运算来生成校验码。

在CRC校验中,发送方和接收方都需要约定一个生成多项式G,通常用一个二进制数表示。

发送方在发送数据前,先通过对数据进行一系列的运算,得出一个校验码,然后将数据和校验码一起发送给接收方。

接收方在接收到数据后,也进行一系列的运算,得到一个校验码,然后与接收到的校验码进行比较。

如果两个校验码一致,说明数据没有发生错误;如果两个校验码不一致,说明数据可能发生了错误。

CRC校验码的生成和校验过程中使用到了多项式的除法运算。

在多项式的除法中,被除数表示为数据和补齐的0的序列,除数表示为生成多项式G。

除法运算的规则是,从数据的最高位开始,依次与生成多项式进行异或运算,将结果作为商,然后将商左移一个比特位,与下一位进行异或运算,得到一个新的商,如此循环,直到数据的所有位都进行了异或运算。

最后,将最后的余数作为校验码。

具体的过程可以用以下步骤来描述:1.约定生成多项式G,得到一个二进制数表示。

2.补齐数据:在数据的最高位之后添加与生成多项式的位数相同的个数的0,得到一个补齐的数据。

3.从补齐数据的最高位开始,依次与生成多项式进行异或运算。

4.将结果作为商,左移一个比特位,与下一位进行异或运算,得到一个新的商。

5.如此循环,直到补齐数据的所有位都进行了异或运算。

6.得到最后的余数,即为校验码。

7.将校验码与原数据一起发送给接收方。

8.接收方在接收到数据后,进行相同的除法运算,得到一个新的校验码。

9.将新的校验码与接收到的校验码进行比较。

10.如果两个校验码一致,说明数据没有发生错误;如果两个校验码不一致,说明数据可能发生了错误。

crc校验原理

校验原理1、循环校验码(CRC码):是数据通信领域中最常用的一种差错校验码,其特征是信息字段和校验字段的长度可以任意选定。

2、生成CRC码的基本原理:任意一个由二进制位串组成的代码都可以和一个系数仅为‘0’和‘1’取值的多项式一一对应。

例如:代码1010111对应的多项式为x6+x4+x2+x+1,而多项式为x5+x3+x2+x+1对应的代码101111。

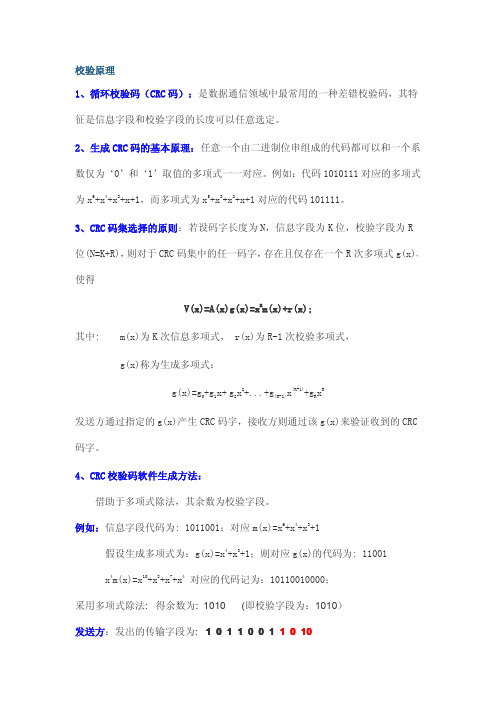

3、CRC码集选择的原则:若设码字长度为N,信息字段为K位,校验字段为R位(N=K+R),则对于CRC码集中的任一码字,存在且仅存在一个R次多项式g(x),使得V(x)=A(x)g(x)=x R m(x)+r(x);其中: m(x)为K次信息多项式, r(x)为R-1次校验多项式,g(x)称为生成多项式:g(x)=g0+g1x+g2x2+...+g(R-1)x(R-1)+g R x R发送方通过指定的g(x)产生CRC码字,接收方则通过该g(x)来验证收到的CRC 码字。

4、CRC校验码软件生成方法:借助于多项式除法,其余数为校验字段。

例如:信息字段代码为: 1011001;对应m(x)=x6+x4+x3+1假设生成多项式为:g(x)=x4+x3+1;则对应g(x)的代码为: 11001x4m(x)=x10+x8+x7+x4对应的代码记为:10110010000;采用多项式除法: 得余数为: 1010 (即校验字段为:1010)发送方:发出的传输字段为: 1 0 1 1 0 0 1 1 0 10信息字段校验字段接收方:使用相同的生成码进行校验:接收到的字段/生成码(二进制除法)如果能够除尽,则正确,CRC校验源码分析这两天做项目,需要用到CRC 校验。

以前没搞过这东东,以为挺简单的。

结果看看别人提供的汇编源程序,居然看不懂。

花了两天时间研究了一下CRC 校验,希望我写的这点东西能够帮助和我有同样困惑的朋友节省点时间。

先是在网上下了一堆乱七八遭的资料下来,感觉都是一个模样,全都是从CRC 的数学原理开始,一长串的表达式看的我头晕。

crc校验码计算电路

crc校验码计算电路CRC校验码计算电路引言:在现代通信系统中,数据的传输无法避免出现误码的情况。

为了保证数据的可靠性,校验码的使用变得至关重要。

CRC(Cyclic Redundancy Check)校验码是一种常用的错误检测码,它通过计算数据的校验值来检测数据在传输过程中是否发生错误。

本文将介绍CRC校验码的原理以及如何实现CRC校验码计算电路。

一、CRC校验码原理CRC校验码是通过将数据按照特定的方式进行计算,得到一个校验值。

发送方在发送数据前,将数据帧与生成多项式进行除法运算,得到余数,然后将余数附加到数据帧的末尾。

接收方在接收到数据后,再次进行除法运算,如果余数为0,则认为数据传输无误。

二、CRC校验码计算电路的实现1. 数据输入与位拆分CRC校验码计算电路首先需要将输入的数据进行位拆分,将数据位拆分为每一位进行处理。

这可以通过移位寄存器实现,每次将输入的数据左移一位,并将最高位取出。

2. 生成多项式的选择生成多项式是CRC校验码计算电路的关键部分,不同的生成多项式会影响校验的可靠性和效率。

常用的生成多项式有CRC-8、CRC-16和CRC-32等。

选择适合实际应用场景的生成多项式很重要。

3. 除法运算CRC校验码计算电路使用的是循环除法运算。

将数据位和生成多项式进行异或运算,然后将结果除以生成多项式,得到余数。

再将余数与下一位数据位进行异或运算,重复上述步骤直到处理完所有数据位。

4. 余数的附加除法运算结束后,将最后得到的余数附加到数据帧的末尾,形成带有校验码的数据帧。

5. 数据传输与接收发送方将带有校验码的数据帧发送给接收方。

接收方将接收到的数据帧与生成多项式进行除法运算,如果余数为0,则认为数据传输无误。

否则,认为数据传输发生错误。

三、CRC校验码计算电路的应用CRC校验码广泛应用于各种通信系统中,如以太网、无线通信、存储系统等。

在以太网中,CRC校验码用于检测数据在链路层传输过程中是否发生错误。

CRC校验原理及步骤

什么是CRC校验?

CRC即循环冗余校验码:是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以任意选定。

循环冗余检查(CRC)是一种数据传输检错功能,对数据进行多项式计算,并将得到的结果附在帧的后面,接收设备也执行类似的算法,以保证数据传输的正确性和完整性。

CRC校验原理:

种称之为

模2

CRC

2. 看选定除数的二进制位数,然后再要发送的数据帧上面加上这个位数-1位的0,然后用新生成的帧以模2除法的方式除上面的除数,得到的余数就是该帧的CRC校验码。

注意,余数的位数一定只比除数位数少一位,也就是CRC校验码位数比除数位数少一位,如果前面位是0也不能省略。

3. 将计算出来的CRC校验码附加在原数据帧后面,构建成一个新的数据帧进行发送;最后接收端在以模

2除法方式除以前面选择的除数,如果没有余数,则说明数据帧在传输的过程中没有出错。

CRC校验码计算示例:

现假设选择的CRC生成多项式为G(X)?= X4?+ X3?+ 1,要求出二进制序列的CRC校验码。

下面是具

体的计算过程:

①将多项式转化为二进制序列,由G(X)?= X4?+ X3?+ 1可知二进制一种有五位,第4位、第三位和第零位分

别为1,则序列为11001

②多项式的位数位5,则在数据帧的后面加上5-1位0,数据帧变为0000,然后使用模2除法除以除数1

1001,得到余数。

【补几位0与x的最高次幂相同,模除就是进行异或】

③将计算出来的CRC校验码添加在原始帧的后面,真正的数据帧为0100,再把这个数据帧发送到接收端。

④。

crc校验 -循环冗余校验 原理和方法 -回复

crc校验-循环冗余校验原理和方法-回复CRC校验(Cyclic Redundancy Check)是一种在数据传输过程中常用的错误检测技术。

它通过对数据进行计算并生成一组校验码,用于检测数据是否在传输过程中发生了错误。

CRC校验算法广泛应用于计算机网络、通信系统以及存储设备等领域。

一、原理:CRC校验是基于二进制的模2除法实现的。

它可以用来检测数据传输过程中是否出现了错误,但不能纠正错误。

CRC校验使用一个固定的生成多项式(通常是16位或32位),该多项式作为校验算法的一部分。

生成多项式被称为“生成多项式”或“CRC多项式”。

在进行CRC校验时,发送方和接收方都需要使用相同的生成多项式。

CRC校验的基本原理是在发送数据之前,发送方计算数据和生成多项式的除法,并将得到的余数(或称为校验码)追加到待发送的数据之后。

接收方在接收到数据后,同样计算数据和生成多项式的除法,并将得到的余数与接收到的校验码进行比较。

如果余数为0,说明数据传输过程中没有发生错误;如果余数不为0,说明数据传输过程中出现了错误。

二、方法:1. 选择生成多项式:在进行CRC校验时,首先需要选择一个适当的生成多项式。

常用的生成多项式有CRC-16、CRC-32等。

这些多项式都是经过严格计算和测试的,可以提供较高的校验能力。

2. 划定消息的边界:在进行CRC校验之前,需要将待发送的数据划分为消息和一些冗余位。

通常,消息包括需要传输的原始数据,而冗余位则由生成多项式的系数决定。

3. 数据和生成多项式的除法:使用生成多项式对消息和冗余位进行除法。

具体操作可以采用多种方法实现,例如位操作、字节操作以及表格查找等。

根据除法运算的性质,进行进位运算、模2求和等,最终得到一个余数。

4. 拼接校验码:将得到的余数追加到消息的末尾,得到一个完整的数据帧。

这个余数被称为校验码,它包含了数据中可能出现的错误的信息。

5. 数据传输:将带有校验码的数据帧发送给接收方。

crc校验码的计算方法

crc校验码的计算方法

校验码也称和校验、检验码,是一称错误检测技术。

其目的是确定在

传输、存储过程中,由于种种原因出现的数据错误,检测出这一类错误,能够快速进行数据信息的纠正和恢复,以便保证最大限度的信息

准确性。

一、CRC校验码

1、CRC算法原理

CRC(Cyclic Redundancy Check)校验码是一种数据错误检测技术,它

通过运算数据和已知校验码(参考值),来检验数据的准确性,它的

原理是用减法校验。

2、CRC校验过程

(1)选择一个固定的计算系数k。

(2)根据传输的数据K位为校验码,计算结果称为校验码。

(3)用已计算出的校验码和未知校验码作比较,若结果相同则数据正确,反之数据则有误。

3、CRC校验码的优缺点

(1)优点:比较有效,且校验码可变;

(2)缺点:计算过程复杂,计算量大,校验时间久,并且容易受干扰。

二、校验码的种类

(1)LRC(Longitudinal Redundancy Check)校验码

LRC校验码是一种用于错误检测的技术,采用垂直纵向校验来检查每

一列数据,用不同位数求取出LRC位,传输可靠性比CRC校验要高。

(2)ALSC(Advanced Longitudinal Signature Character)校验码

通过字符间的比较,不仅可以检测出一个字符的错乱,还可以检测出

多个字符的错顺、重复、错码等多种情况。

(3)奇偶校验码

奇偶校验码是一种简单的校验技术,只能检查出一位或多位数据错误,相对CRC校验,它的可靠性较低。

crc校验的原理

crc校验的原理

CRC(Cyclic Redundancy Check)校验是一种常用的数据传输错误检测方法,它通过计算数据的循环冗余校验码来检测数据传输过程中是否发生了错误。

其原理如下:

1. 将要传输的数据看成一个多项式,例如:D(x) = d7x^7 + d6x^6 + d5x^5 + d4x^4 + d3x^3 + d2x^2 + d1x + d0。

2. 选择一个固定的生成多项式G(x),例如:G(x) = g3x^3 + g2x^2 + g1x + g0。

3. 将D(x)左移G(x)的次数,将D(x)除以G(x),得到商Q(x)和余数R(x)。

4. 将余数R(x)作为校验码,将其添加到数据末尾,形成一个新的多项式T(x) = D(x) + R(x)。

5. 接收方收到数据后,再次进行CRC校验,如果计算出的余数为0,则说明数据传输没有发生错误。

CRC校验的优点是计算速度快,检测效率高,能够检测出大部分数据传输错误。

同时,CRC校验也有一些缺点,例如无法纠正错误,只能检测出错误,而且如果生成多项式选择不当,可能会出现误判的情况。

在实际应用中,CRC校验被广泛应用于网络通信、存储设备、无线通信等领域,保障了数据传输的准确性和可靠性。

crc 原理

CRC原理详解1. 引言循环冗余检验(Cyclic Redundancy Check,CRC)是一种常用的错误检测技术,广泛应用于通信、存储等领域。

CRC通过对数据进行多项式计算,生成冗余校验码,并将其附加到数据中。

接收方在接收到数据后,使用相同的多项式计算方法对数据进行校验,如果校验结果与接收到的冗余校验码一致,说明数据未被错误修改;否则,说明数据可能存在错误。

本文将详细介绍CRC的基本原理,包括生成多项式、计算过程、校验方法等。

2. 多项式生成CRC通过多项式生成冗余校验码。

生成多项式是一个固定的二进制数,通常用一个二进制数表示,如110101。

生成多项式的选择对CRC的性能有很大影响,不同的生成多项式可以检测到不同数量的错误,并具有不同的误检率。

生成多项式的选取方法有很多种,常用的有标准CRC多项式、反射CRC多项式和非反射CRC多项式。

标准CRC多项式的最高次项为1,如100000111;反射CRC多项式的最高次项为0,如110101;非反射CRC多项式的最高次项为1,如100000111。

3. 计算过程CRC的计算过程可以简单描述为:将数据按照二进制形式进行处理,除以生成多项式并取余数,将余数作为冗余校验码附加到数据中。

具体计算过程如下: 1. 将要发送的数据转换为二进制形式。

2. 在数据的末尾添加n个0,其中n为生成多项式的位数减1。

3. 将数据除以生成多项式,并取余数。

4. 将余数作为冗余校验码附加到数据末尾。

例如,要发送的数据为101010,生成多项式为110101,则计算过程如下: 1. 将数据转换为二进制形式:101010。

2. 在数据末尾添加5个0:10101000000。

3. 将数据除以生成多项式并取余数:10101000000除以110101,余数为01110。

4. 将余数作为冗余校验码附加到数据末尾:10101001110。

最终发送的数据为10101001110。

循环冗余校验码(crc)的基本原理

A:①水平垂直奇偶校验②循环求和

③循环冗余④正比率

B:①模2除法②定点二进制除法

③二-十进制除法④循环移位法

C:①1100101010111②110010101010011

③110010101011100④110010101010101

D:①可纠正一位差错②可检测所有偶数位错

③可检测所有小于校验位长度的突发错

5、通信与网络中常用的CRC

在数据通信与网络中,通常k相当大,由一千甚至数千数据位构成一帧,而后采用CRC码产生r位的校验位。它只能检测出错误,而不能纠正错误。一般取r=16,标准的16位生成多项式有CRC-16=x16+x15+x2+1和CRC-CCITT=x16+x15+x2+1。

【例1】某循环冗余码(CRC)的生成多项式G(x)=x3+x2+1,用此生成多项式产生的冗余位,加在信息位后形成CRC码。若发送信息位1111和1100则它的CRC码分别为_A_和_B_。由于某种原因,使接收端收到了按某种规律可判断为出错的CRC码,例如码字_C_、_D_、和_E_。(1998年试题11)

1011

------------

11-------余数(校验位)

(4)编码后的报文(CRC码):

1010000

+ 11

------------------

1010011

CRC码为1010011(和纠错)。

在接收端收到了CRC码后用生成多项式为G(x)去做模2除,若得到余数为0,则码字无误。若得到余数不为0,则接收的数据有错。

(2)此题生成多项式有4位(R+1),要把原始报文F(x)左移3(R)位变成1010000

CRC校验原理

CRC校验原理CRC校验码的基本思想是利用线性编码理论,在发送端根据要传送的k位二进制码序列,以一定的规则产生一个校验用的监督码(既CRC码)r位,并附在信息后边,构成一个新的二进制码序列数共(k+ r)位,最后发送出去。

在接收端,则根据信息码和CRC码之间所遵循的规则进行检验,以确定传送中是否出错。

在数据存储和数据通讯领域,CRC无处不在:著名的通讯协议X.25的FCS(帧检错序列)采用的是CRC. CCITT,ARJ、LHA等压缩工具软件采用的是CRC32,磁盘驱动器的读写采用了CRC16,通用的图像存储格式GIF、TIFF等也都用CRC作为检错手段。

CRC的本质是模-2除法的余数,采用的除数不同,CRC的类型也就不一样。

通常,CRC的除数用生成多项式来表示。

最常用的CRC码的生成多项式有CRC16,CRC32.以CRC16为例,16位的CRC码产生的规则是先将要发送的二进制序列数左移16位(既乘以2^16)后,再除以一个多项式,最后所得到的余数既是 CRC码,如下式所示,其中K(X)表示n位的二进制序列数,G(X)为多项式,Q(X)为整数,R(X)是余数(既CRC码)。

K(X)>>16=G(x)Q(x)+R(x)求CRC码所采用模2加减运算法则,既是不带进位和借位的按位加减,这种加减运算实际上就是逻辑上的异或运算,加法和减法等价,乘法和除法运算与普通代数式的乘除法运算是一样,符合同样的规律。

生成CRC码的多项式如下,其中CRC-16和CRC-CCITT产生16位的CRC码,而CRC-32则产生的是32位的CRC码接收方将接收到的二进制序列数(包括信息码和CRC码)除以多项式,如果余数为0,则说明传输中无错误发生,否则说明传输有误,关于其原理这里不再多述。

用软件计算CRC码时,接收方可以将接收到的信息码求CRC码,比较结果和接收到的CRC码是否相同。

CCITT推荐的高级数据链路控制规程HDLC的帧校验序列FCS中,使用CCITT-16即CRC16,其生成多项式为 G(x)=x16+x12+x5 +1, CRC-32的生成多项式为G(x)=x32+x26+x23+x22+x16+x11+x10+x16+x8+x7+x5+x4+x2+x+1以上是摘录的一段介绍,是不是觉得很玄?我第一次看也是觉得很晕,后来查询了一些规约和协议的实现资料以后,才恍然大悟。

循环冗余校验码(CRC)的基本原理

循环冗余校验码(CRC)的基本原理是:在K位信息码后再拼接R位的校验码,整个编码长度为N位,因此,这种编码又叫(N,K)码。

对于一个给定的(N,K)码,可以证明存在一个最高次幂为N-K=R的多项式G(x)。

根据G(x)可以生成K位信息的校验码,而G(x)叫做这个CRC码的生成多项式。

校验码的具体生成过程为:假设发送信息用信息多项式C(X)表示,将C(x)左移R位,则可表示成C(x)*2R,这样C(x)的右边就会空出R位,这就是校验码的位置。

通过C(x)*2R除以生成多项式G(x)得到的余数就是校验码。

几个基本概念1、多项式与二进制数码多项式和二进制数有直接对应关系:x的最高幂次对应二进制数的最高位,以下各位对应多项式的各幂次,有此幂次项对应1,无此幂次项对应0。

可以看出:x的最高幂次为R,转换成对应的二进制数有R+1位。

多项式包括生成多项式G(x)和信息多项式C(x)。

如生成多项式为G(x)=X^4+X^3+X+1,可转换为二进制数码11011。

而发送信息位1111,可转换为数据多项式为C(x)=X^3+X^2+X+1。

2、生成多项式是接受方和发送方的一个约定,也就是一个二进制数,在整个传输过程中,这个数始终保持不变。

在发送方,利用生成多项式对信息多项式做模2除生成校验码。

在接受方利用生成多项式对收到的编码多项式做模2除检测和确定错误位置。

应满足以下条件:a、生成多项式的最高位和最低位必须为1。

b、当被传送信息(CRC码)任何一位发生错误时,被生成多项式做模2除后应该使余数不为0。

c、不同位发生错误时,应该使余数不同。

d、对余数继续做模2除,应使余数循环。

将这些要求反映为数学关系是比较复杂的。

但可以从有关资料查到常用的对应于不同码制的生成多项式如图9所示:N K 码距d G(x)多项式G(x)7 4 3 x3+x+1 10117 4 3 x3+x2+1 11017 3 4 x4+x3+x2+1 111017 3 4 x4+x2+x+1 1011115 11 3 x4+x+1 1001115 7 5 x8+x7+x6+x4+1 11101000131 26 3 x5+x2+1 10010131 21 5 x10+x9+x8+x6+x5+x3+1 1110110100163 57 3 x6+x+1 100001163 51 5 x12+x10+x5+x4+x2+1 10100001101011041 1024 x16+x15+x2+1 11000000000000101图9 常用的生成多项式3、模2除(按位除)模2除做法与算术除法类似,但每一位除(减)的结果不影响其它位,即不向上一位借位。

crc校验码的基本原理

crc校验码的基本原理宝子!今天咱们来唠唠这个CRC校验码的基本原理,可有趣啦。

你想啊,在数据的世界里,就像咱们生活中有各种各样的东西要运输一样。

数据在各个设备之间传来传去,就像货物在各地之间运输。

可是这过程中呀,很可能会出岔子,就像货物可能会受损一样。

这时候CRC校验码就像一个超级厉害的安检员。

CRC呢,全名叫循环冗余校验(Cyclic Redundancy Check)。

简单来说,它是一种根据数据产生一个固定长度的校验值的方法。

比如说,你有一堆数据,这就好比是你要寄出去的一堆宝贝包裹。

CRC校验码呢,就会根据这些包裹的内容算出一个小小的标签(校验值)。

那这个校验值是怎么算出来的呢?它是通过一个多项式除法得到的。

这听起来是不是有点头疼?别担心,咱打个比方。

就好比你有一些彩色的珠子(代表数据),然后你按照一定的规则(多项式)把这些珠子串起来,然后做一个除法的操作。

这个除法不是咱们平常的数字除法哦,是一种特殊的按照位来做的除法。

最后得到的余数就是那个校验值啦。

这就像你把包裹按照一种奇特的方式整理了一下,最后得出一个小标记。

当数据要发送的时候,发送方就会算出这个CRC校验码,然后把数据和校验码一起发出去。

接收方收到数据后呢,就会用同样的规则重新计算一遍校验码。

如果接收方算出来的校验码和发送方发过来的校验码一样,那就说明数据在传输过程中大概率没有出错,就像货物经过运输后,检查发现和发货的时候一样完好无损。

如果不一样呢,那就说明数据可能在传输的时候被篡改了或者出了什么差错,就像货物在运输途中被磕了碰了。

你可能会想,这有啥特别的呀?它的特别之处可多着呢。

CRC校验码有不同的标准,就像不同的安检标准一样。

有的标准对数据的检测更严格,有的可能稍微宽松一点。

而且这个校验码的长度也有讲究。

短的校验码计算起来可能快一点,但是检测错误的能力可能就相对弱一些;长的校验码呢,检测错误的能力强,可是计算起来就会花费更多的时间和资源。

循环冗余校验码(crc)的基本原理

几个基本概念

1、多项式与二进制数码

多项式和二进制数有直接对应关系:x的最高幂次对应二进制数的最高位,以下各位对应多项式的各幂次,有此幂次项对应1,无此幂次项对应0。可以看出:x的最高幂次为R,转换成对应的二进制数有R+1位。

(3)用生成多项式(二进制数)对f(x)*XR做模2除,得到余数(即校验码)。

(4)将余数多项式加到f(x)*XR中,得到完整的CRC码。

【例】假设使用的生成多项式是G(x)=x3+x+1。4位的原始报文为1010,求编码后的报文。

解:

(1)将生成多项式G(x)=x3+x+1转换成对应的二进制除数1011。

31 215 x10+x9+x8+x6+x5+x3+111101101001

63 57 3x6+x+11000011

63 51 5 x12+x10+x5+x4+x2+1 1010000110101

10411024x16+x15+x2+1 11000000000000101

图9常用的生成多项式

3、模2除(按位除)

④可检测所有小于、等于校验位长度的突发错

解:从前面有关CRC的论述中可得出:

A:③循环冗余B:①模2除法

C:G(x)=11011,f(x)=11001010101,F(x)*24÷G(x)=110010101010000÷11011余0011

crc原理详解

crc原理详解CRC(Cyclic Redundancy Check)是一种校验码算法,用于检测数据传输过程中是否发生了错误。

CRC通过对数据进行多项式除法运算生成校验码,接收方在接收到数据后再次进行相同的计算,并与发送方提供的校验码进行比对,以验证数据的完整性。

CRC的原理如下:1. 选择生成多项式:首先需要选择一个生成多项式,通常是一个固定长度的二进制数,例如16位或32位。

这个生成多项式会用于计算校验码。

CRC(循环冗余校验)是一种数据通信中的差错控制方法,主要用于检测数据传输或保存后可能出现的错误。

CRC的原理基于除法及余数的概念,通过特定的算法对数据进行处理,生成一个固定位数的校验码,附加到原数据后面,形成循环校验码。

2. 具体来说,CRC算法将传输的数据(M(X))当作一个位数很长的数,并选择一个生成多项式(G(X))进行除法运算。

得到的余数(R(X))作为校验数据,附加到原数据后面,组成循环校验码。

这个校验码在数据传输过程中起到关键的作用,接收方在接收到数据后,会重新计算CRC值,并与发送方附加的CRC值进行比较,以判断数据在传输过程中是否发生错误。

数据处理:发送方将要传输的数据按照位的方式进行多项式除法运算,将生成的余数添加到数据后面形成带校验码的数据包。

3. 接收端校验:接收方收到数据后,也进行相同的多项式除法运算,得到余数并与接收到的校验码进行比对。

如果两者一致,则认为数据传输正确,否则判定数据出现错误。

4. 纠错能力:CRC算法可以检测出大多数的常见错误,如单比特错误、双比特错误等。

而且,具体的CRC算法实现可以根据选取的生成多项式来决定其校验能力和纠错能力的强度。

值得注意的是,CRC校验虽然具有较高的可靠性和安全性,但并不能完全保证数据的完整性。

在某些情况下,如遇到特定的错误模式,CRC校验可能会失效。

因此,在实际应用中,还需要结合其他差错控制方法,如校验和等,以提高数据传输的可靠性。

CRC校验码的原理

CRC校验码的原理CRC(Cyclic Redundancy Check)校验码是一种常用的错误检测码,用于检测数据传输中的错误。

它通过在数据传输过程中附加一定长度的校验码,并在接收端重新计算校验码来判断数据是否传输正确。

CRC校验码的原理基于多项式除法。

具体来说,CRC校验码通过将原始数据与一个预定的生成多项式进行除法运算得到校验码。

生成多项式的系数决定了CRC校验码的长度,通常用于CRC校验的生成多项式是众多经典多项式中的一种,比如CRC-8、CRC-16、CRC-32等。

1.生成:a.选择一个生成多项式,该多项式的位数决定了校验码的位数,比如CRC-16使用的是16位多项式;b.将要传输的数据按照一定的规则与生成多项式进行除法运算;c.得到的余数就是CRC校验码;d.将CRC校验码附加到要传输的数据后面,传输整个数据包。

2.校验:a.接收端接收到数据包后,按照与生成端相同的生成多项式和除法规则对接收到的数据进行除法运算;b.若得到的余数为0,说明数据传输正确,否则数据传输错误。

以CRC-16为例,它使用的生成多项式是x^16+x^15+x^2+1,表示为0x8005、在传输端,将要传输的数据和该生成多项式进行除法运算,得到的余数作为CRC校验码附加到传输数据后面。

在接收端,接收到数据后使用相同的生成多项式进行除法运算,若余数为0则说明传输正确,否则传输错误。

1.强大的错误检测能力:CRC校验码在有限的代码位数下能够捕捉到很多常见的传输错误,包括单比特错误、双比特错误、任意奇数个比特错误等。

2.算法简单:CRC校验码的生成和校验算法相对简单,可以通过硬件和软件实现,不占用过多的计算资源。

3.高效性能:CRC校验码生成和校验的时间复杂度都为O(n),其中n 是数据位数,因此具有较高的效率。

总的来说,CRC校验码是一种广泛应用于数据传输中的错误检测码,通过通过生成和校验过程,能够有效地检测传输中产生的错误,保证数据的可靠性。

crc16校验原理

不难看出,余式有 256 种可能的值,实际上就是 0~255 以 X16+X12+X5+1 为权得到的 CRC 码,可以通过函数 crc16l 来计算。以 1 为例。

code test[]={0x01}; crc = 0; ptr = test; crc = crc16l(ptr,1);

执行结果 crc = 1021,这就是 1 对应的余式。

图中进行 XOR 运算的位与多项式的表达相对应。 X5 代表 Bit5,X12 代表 Bit12,1 自然是代表 Bit0,X16 比较特别,是指移 位寄存器移出的数据,即图中的 DATA OUT。可以这样理解,与数据位做 XOR 运算的是上次 CRC 值的 Bit15。 根据以上说明,可以依葫芦画瓢的写出以下程序。(程序都是在 keil C 7.10 下调 试的)

typedef unsigned char uchar; typedef unsigned int uint;

code uchar crcbuff [] = { 0x00,0x00,0x00,0x00,0x06,0x0d,0xd2,0xe3};

uint crc;

// CRC 码

void main(void)

图 1,图 2 说明了 CRC 校验中 CRC 值是如何计算出来的,体现的多项式正 是 X16+X12+X5+1。 Serial Data 即是需要校验的数据。从把数据移位开始计 算,将数据位(从最低的数据位开始)逐位移入反向耦合移位寄存器(这个名词 我也不懂,觉得蛮酷的,就这样写了,嘿)。当所有数据位都这样操作后,计算 结束。此时,16 位移位寄存器中的内容就是 CRC 码。

很多资料上都写了查表法来计算,当时是怎么也没想通。其实蛮简单的。假设通 过移位处理了 8 个 bit 的数据,相当于把之前的 CRC 码的高字节(8bit)全部移 出,与一个 byte 的数据做 XOR 运算,根据运算结果来选择一个值(称为余式), 与原来的 CRC 码再做一次 XOR 运算,就可以得到新的 CRC 码。

crc校验码的原理

CRC(Cyclic Redundancy Check)校验码是一种广泛用于通信和数据存储中的错误检测技术。

它通过对数据进行一系列二进制位运算,生成一个固定长度的校验码,并将其附加到数据后面传输或存储。

接收方可以使用相同的算法来重新计算校验码并与接收到的数据比较,以确定数据是否发生了错误。

CRC校验码的原理可以简要概括如下:

1. 基本概念:

- 生成多项式:一个固定的二进制多项式,通常用一个数值表示。

- 信息位:需要进行校验的数据,每个信息位只能取0或1。

- 校验码:一串固定长度的二进制数字,由生成多项式和信息位计算而来。

2. 计算过程:

- 将信息位和一定长度的0填充在一起形成一个二进制数。

- 用生成多项式除以上述二进制数,得到商和余数。

余数就是CRC校验码。

- 将CRC校验码附加在信息位后面进行传输或存储。

3. 检验过程:

- 接收方收到数据后,将其中的校验码截取出来。

- 将接收到的信息位和一定长度的0填充在一起形成一个二进制数。

- 用相同的生成多项式除以上述二进制数,得到商和余数。

- 如果余数为0,则说明数据未发生错误;否则,说明数据发生了错误。

需要注意的是,CRC校验码可以检测出大部分单比特错误和多比特错误,但并不能保证检测所有错误,因此在实际应用中应根据具体情况选择合适的校验码和纠错技术。

希望对你有所帮助!如果还有其他问题,请随时提问。

crc校验原理

crc校验原理

CRC校验是一种通过计算数据的循环冗余校验值来验证数据

完整性的方法。

它基于多项式除法的原理,在发送端使用生成多项式对数据进行处理,生成校验值,并将该校验值附加在数据后面一并发送到接收端。

接收端使用相同的生成多项式进行计算,得到一个校验值,然后将接收到的校验值与计算得到的校验值进行比较,从而判断数据是否在传输过程中发生了错误。

具体的计算过程如下:

1. 选择一个生成多项式,也称为校验多项式。

生成多项式的位数取决于要检测的错误数量和类型。

常见的生成多项式有

CRC-8、CRC-16、CRC-32等。

2. 将数据进行整理,使其长度与生成多项式相等,并在数据末尾补充若干个0。

3. 将补充后的数据与生成多项式进行模2除法,即进行多项式的异或操作。

4. 将除法得到的余数作为校验值,将其附加在数据后面,并一同发送。

5. 接收端同样对接收到的数据进行整理,并使用相同的生成多项式进行模2除法运算,得到一个余数。

6. 将接收到的校验值与计算得到的余数比较,如果相等,则认为数据传输没有发生错误;如果不相等,则认为数据传输发生了错误。

CRC校验具有较高的检测能力和较低的冲突率,常用于数据

通信中对数据完整性进行验证。

CRC校验原理及步骤

CRC校验原理及步骤什么是CRC校验?CRC即循环冗余校验码:是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以任意选定。

循环冗余检查(CRC)是一种数据传输检错功能,对数据进行多项式计算,并将得到的结果附在帧的后面,接收设备也执行类似的算法,以保证数据传输的正确性和完整性。

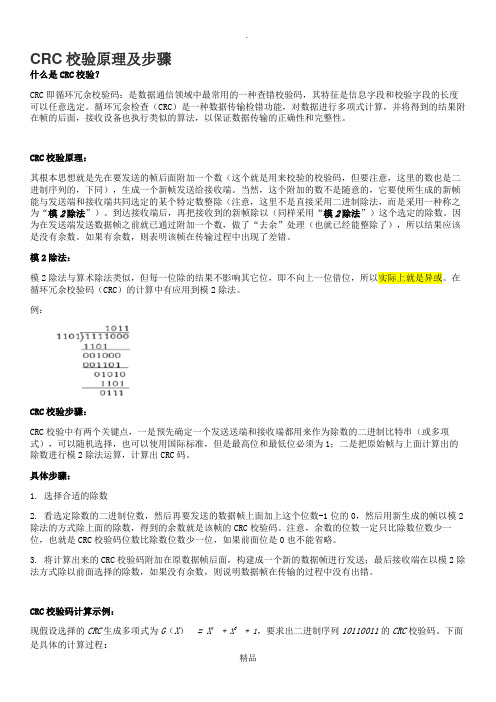

CRC校验原理:其根本思想就是先在要发送的帧后面附加一个数(这个就是用来校验的校验码,但要注意,这里的数也是二进制序列的,下同),生成一个新帧发送给接收端。

当然,这个附加的数不是随意的,它要使所生成的新帧能与发送端和接收端共同选定的某个特定数整除(注意,这里不是直接采用二进制除法,而是采用一种称之为“模2除法”)。

到达接收端后,再把接收到的新帧除以(同样采用“模2除法”)这个选定的除数。

因为在发送端发送数据帧之前就已通过附加一个数,做了“去余”处理(也就已经能整除了),所以结果应该是没有余数。

如果有余数,则表明该帧在传输过程中出现了差错。

模2除法:模2除法与算术除法类似,但每一位除的结果不影响其它位,即不向上一位借位,所以实际上就是异或。

在循环冗余校验码(CRC)的计算中有应用到模2除法。

例:CRC校验步骤:CRC校验中有两个关键点,一是预先确定一个发送送端和接收端都用来作为除数的二进制比特串(或多项式),可以随机选择,也可以使用国际标准,但是最高位和最低位必须为1;二是把原始帧与上面计算出的除数进行模2除法运算,计算出CRC码。

具体步骤:1. 选择合适的除数2. 看选定除数的二进制位数,然后再要发送的数据帧上面加上这个位数-1位的0,然后用新生成的帧以模2除法的方式除上面的除数,得到的余数就是该帧的CRC校验码。

注意,余数的位数一定只比除数位数少一位,也就是CRC校验码位数比除数位数少一位,如果前面位是0也不能省略。

3. 将计算出来的CRC校验码附加在原数据帧后面,构建成一个新的数据帧进行发送;最后接收端在以模2除法方式除以前面选择的除数,如果没有余数,则说明数据帧在传输的过程中没有出错。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CRC 校验码的原理在通信与数字信号处理等领域中循环冗余校验码(Cyclic Redundancy Check,CRC )是一种很常用的设计。

一般来说数据通信中的编码可以分为信源编码和信道编码两大类,其中,为了提高数据通信的可靠性而采取的编码称为信道编码,即抗干扰编码。

在通信系统中,要求数据传输过程中的误码率足够低,而为了降低数据传输过程中的误码率,经常采用的一种方法是差错检测控制。

在实际的通信系统中,差错检测控制的主要方法又3种:前向纠错(FEC ),自动重发(ARQ )和反馈检验法。

FEC 指接收端不仅能够在收到的信码中发现错码,而且还能够纠正错码。

一般来说,这种方法不需要反向信道,实时性很好,不过设备较复杂。

ARQ 是指接收端在收到的信码中检测出错码时,即设法通知发送端重新发送信号,直到能够正确接收为止。

通常,这种方法只用来检测误码,而且只能在双向信道中使用。

反馈检验法是指接收端将收到的信码一字不差地转发回发送端,同时与原发送信码进行比较,如果有错,则发端重发。

这种方法的原理和设备都比较简单,但需要双向信道的支持,而且传输效率低下; 通过实践检验,在这三中方法中,如果传输过程中的误码率较低,那么采用前向纠错法比较理想,但如果误码率较高时,这种方法又会出现“乱纠”的现象;在网络通信中,广泛的采用差错检测方法时自动请求重发,这种方法只要检错功能即可;反馈检验法时前向纠错法和自动请求重发的结合。

在实现差错检测控制的众多方法中,循环冗余校验就是一类重要的线性分组码。

它时一种高效的差错控制方法,它广泛应用于测控及数据通信领域,同时具有编码和解码方法简单,检错能力强,误判概率很低和具有纠错能力等优点。

循环冗余校验码实现的方法CRC 的基本原理就是在一个P 位二进制数据序列之后附加一个R 位二进制检验码序列,从而构成一个总长位N=P+R 位的二进制序列。

例如,P 位二进制数据序列D=[d 1-p d 2-p …d 1d 0],R 位二进制检验码R = [r 1-r r 2-r …r 1r 0],那么所得到的这个N 位二进制序列就是M=[d 1-p d 2-p …d 1d 0 r 1-r r 2-r …r 1r 0],这里附加在数据序列之后的CRC 码与数据序列的内容之间存在着某种特定的关系。

如果在数据传输过程中,由于噪声或传输特性不理想而使数据序列中的某一位或某些位发生错误,这种特定关系就会被破坏。

可见在数据的接收端通过检查这种特定关系,可以很容易地实现对数据传输正确性的检验。

在CRC 中,检验码R 使通过对数据序列D 进行二进制除法取余式运算得到的,他被一个称为生成多项式的(r+1)位二进制序列G=[g r g 1-r …g 1g 0]来除,具体的多项式除法形式如下:)()(x G x D x r=Q(x)+)()(x G x R其中,)(x D x r表示将数据序列D 左移r 位,即在D 的末尾再增加r 个0位;Q (x )代表这一除法所得的商,R (x )就是所需的余式。

此外,这一运算关系还可以表示为⎥⎦⎤⎢⎣⎡=)()(Re )(x G x D x x R r⎥⎦⎤⎢⎣⎡=)()(Re )(x G x M x R通过上面CRC 基本原理的介绍,可以发现生成多项式使一个非常重要的概念,它决定了CRC 的具体算法。

目前,生成多项式具有一下一些通用标准,其中CRC -12,CRC -16,CRC -ITU 和CRC -32是国际标准。

CRC -4 14++x xCRC -12 131112++++x x x x CRC -16 121216+++x x x CRC -ITU 151216+++x x xCRC -32 +++232632x x x …12+++x x CRC -32c +++272832x x x …168+++x xCRC -ITU 的硬件实现方法该图反映了CRC -ITU 用硬件实现的原理,从左至右分别代表16个移位寄存器,左边代表高位右边代表低位,可以分析得知,在生成多项式的非零项指数对应的寄存器前有一个异或门,这种电路能够实现相应的模二除法。

但是这种电路实现的却是串行输入,在高速场合下,这种方案势必会造成编码效率低下,误码率高的弊端,为了解决这个问题,提高编码效率和正确率,要求能够实现并行算法,在一个时钟周期内得到一个多位数据的CRC 码。

CRC 的并行算法原理与实现在上面已经给出了CRC 的硬件原理,我们可以依此得到并行算法的原理。

因为CRC 硬件的实现方法是利用反馈移位寄存器外加异或门进行运算得来(开始计算时,所有的寄存器要清零),假如说我们输入一个数据串,每输入一个比特的数据时,上一状态的所有寄存器的值,都会进行移位或进行异或运算后移位。

当前状态与前一状态有着紧密的联系,而这种关系就通过硬件电路的形式表示出来,同理,以此类推,那么若干个状态后的状态与初始状态也有很紧密的联系,不难看出,初始状态为全零,8个比特串行输入后又为一个状态,8个比特串行再输入后,此时的状态与上一个8比特后的状态又有着固定的联系。

可见,只要我们找到他们之中的这种联系,那么我们就可以得到每次运算8位数据的CRC 并行算法。

我们假设寄存器D15----D0的初始状态为A,B,C,D,E,F,G ,H,I,J,K,L,M,N,O,P ,输入的数据为C7,C6,C5,C4,C3,C2,C1,C0,当所有数据都输入完时,根据硬件电路图可以得到由初始状态D(15)=D(7)+D(11)+D(15)+C(7)+C(3)D(14)=D(6)+D(10)+D(14)+C(6)+C(2)D(13)=D(5)+D(9)+D(13)+C(5)+C(1)D(12)=D(4)+D(15)+C(7)+D(8)+D(12)+C(4)+C(0)D(11)=D(3)+D(14)+C(6)D(10)=D(2)+D(13)+C(5)D(9)=D(1)+D(12)+C(4)D(8)=D(0)+D(11)+D(15)+C(7)+C(3)D(7)=D(15)+C(7)+D(10)+D(14)+C(6)+C(2)D(6)=D(14)+C(6)+D(9)+D(13)+C(5)+C(1)D(5)=D(13)+C(5)+D(8)+D(12)+C(4)+C(0)D(4)=D(12)+C(4)D(3)=D(11)+D(15)+C(7)+C(3)D(2)=D(10)+D(14)+C(6)+C(2)D(1)=D(9)+D(13)+C(5)+C(1)D(0)=D(8)+D(12)+C(4)+C(0)CRC的VHDL语言实现LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CRC ISPORT(CLK,CLR:IN STD_LOGIC;DA TA_IN :IN STD_LOGIC_VECTOR(7 DOWNTO 0);DA TA_OUT:OUT STD_LOGIC_VECTOR(15 DOWNTO 0)); END CRC;ARCHITECTURE A OF CRC ISSIGNAL Q:STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL D:STD_LOGIC_VECTOR(15 DOWNTO 0);BEGINPROCESS(CLR,CLK)BEGINIF CLR='1'THEND<=(OTHERS=>'0');ELSIF CLK'EVENT AND CLK='1'THENQ<=DA TA_IN;D(0)<=D(8) XOR D(12) XOR Q(4) XOR Q(0);D(1)<=D(9) XOR D(13) XOR Q(5) XOR Q(1);D(2)<=D(10) XOR D(14) XOR Q(6) XOR Q(2);D(3)<=D(11) XOR D(15) XOR Q(7) XOR Q(3);D(4)<=D(12) XOR Q(4);D(5)<=D(13) XOR Q(5) XOR D(8) XOR D(12) XOR Q(4) XOR Q(0);D(6)<=D(14) XOR Q(6) XOR D(9) XOR D(13) XOR Q(5) XOR Q(1);D(7)<=D(15) XOR Q(7) XOR D(10) XOR D(14) XOR Q(6) XOR Q(2);D(8)<=D(0) XOR D(11) XOR D(15) XOR Q(7) XOR Q(3);D(9)<=D(1) XOR D(12) XOR Q(4);D(10)<=D(2) XOR D(13) XOR Q(5);D(11)<=D(3) XOR D(14) XOR Q(6);D(12)<=D(4) XOR D(15) XOR Q(7) XOR D(8) XOR D(12) XOR Q(4) XOR Q(0);D(13)<=D(5) XOR D(9) XOR D(13) XOR Q(5) XOR Q(1);D(14)<=D(6) XOR D(10) XOR D(14) XOR Q(6) XOR Q(2);D(15)<=D(7) XOR D(11) XOR D(15) XOR Q(7) XOR Q(3);END IF;DA TA_OUT<=D;END PROCESS;END;通过仿真,假设我们输入0x0102,那么相应的CRC码应为0x1373,当把0x01021373作为数据输入时,结果应为0x0000;仿真结果表明,设计正确。

下图为CRC模块的元件符号。