逻辑函数综合测试题七

电子电工类综合知识理论(测试卷)(答案)

3.解:灯管等效电阻R=150 ,镇流器的等效电阻 ,等效电感L=1.59H,

灯管及整个电路消耗的功率P=28W。

4.答:按下启动按钮 ,交流接触器 得电工作,且 自锁,时间继电器KT得电,延时时间一到KT常开触点闭合, 得电工作。

电子技术基础综合测试卷(一)

一、选择题

1.A2.B3.C4.C 5.A 6.B 7.B 8.C 9.A 10.D

三、计算题

1.解:S闭合时, (线电流);S断开时 (相电流), (线电流)。

2.解:当 单独作作时, (方向向下)

当 单独作作时, (方向向上)

∴ =1-0.5=0.5a

3.解:(1) ; ;(2)14.55 A;(3) 。

(4)向量图:

电工技术基础综合测试卷(八)

一、填空题

1.答:0V,444V,628V,400V,444V

5.三位环形寄存器,101,011

6. +=4V, -=2V,Δ =2V

电子技术基础综合测试卷(八)

一、选择题

1.A 2.C 3.B 4.B 5.B 6.A 7.B8.B 9.B 10.D

二、填空题

1.双单2.正反馈3.选频

4.空翻5.10

三、综合题

1.(1)A与D,B与C(2)413Hz(3)22K

2. =6 , = , =1.5 -6 -

3.A点时,5VB点时,4V C点时,2.5V

4.略

5.输入一致鉴别电路

6.

A3

A2

A1

A0

F

A3

A2

A1

A0

F

0

0

0

00000 Nhomakorabea0

0

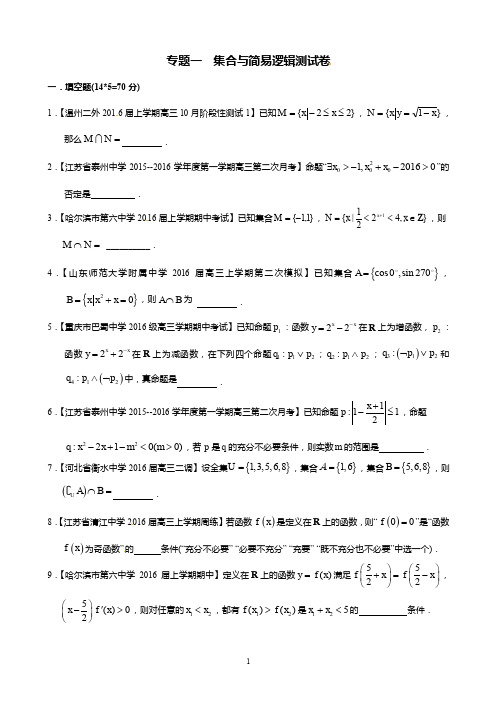

专题1.1 集合与简易逻辑(测试卷)(原卷版)

专题一 集合与简易逻辑测试卷一.填空题(14*5=70分)1.【温州二外2016届上学期高三10月阶段性测试1】已知}22{≤≤-=x x M ,}1{x y x N -==,那么=N M .2.【江苏省泰州中学2015--2016学年度第一学期高三第二次月考】命题“02016,10200>-+->∃x x x ”的否定是 .3.【哈尔滨市第六中学2016届上学期期中考试】已知集合}1,1{-=M ,},4221|{1Z ∈<<=+x x N x ,则=⋂N M __________.4.【山东师范大学附属中学2016届高三上学期第二次模拟】已知集合{}cos0,sin 270A =,{}20B x x x =+=,则A B ⋂为 .5.【重庆市巴蜀中学2016级高三学期期中考试】已知命题1p :函数22x x y -=-在R 上为增函数,2p :函数22x x y -=+在R 上为减函数,在下列四个命题112:q p p ∨;212:q p p ∧;()312:q p p ⌝∨和()412:q p p ∧⌝中,真命题是 .6.【江苏省泰州中学2015--2016学年度第一学期高三第二次月考】已知命题1211:≤+-x p ,命题)0(012:22><-+-m m x x q ,若p 是q 的充分不必要条件,则实数m 的范围是 .7.【河北省衡水中学2016届高三二调】设全集{}1,3,5,6,8U =,集合{}1,6A =,集合{}5,6,8B =,则()U A B ⋂= .8.【江苏省清江中学2016届高三上学期周练】若函数()f x 是定义在R 上的函数,则“()00f =”是“函数()f x 为奇函数”的 条件(“充分不必要” “必要不充分” “充要” “既不充分也不必要”中选一个).9.【哈尔滨市第六中学2016届上学期期中】定义在R 上的函数)(x f y =满足5522f x f x ⎛⎫⎛⎫+=- ⎪ ⎪⎝⎭⎝⎭,5()02x f x ⎛⎫'-> ⎪⎝⎭,则对任意的21x x <,都有)()(21x f x f >是521<+x x 的 条件.10.【泰州市2015届高三第三次调研测试】给出下列三个命题:①“a >b ”是“3a >3b”的充分不必要条件; ②“α>β”是“cos α<co s β”的必要不充分条件;③“0a =”是“函数()()32f x x ax x =+∈R 为奇函数”的充要条件.其中正确命题的序号为 .11.【黑龙江省牡丹江市一高2016届高三10月】已知, a b 是两个非零向量,给定命题:p ⋅=a b a b ,命题:q t ∃∈R ,使得t =a b ,则p 是q 的________条件.12.【吉林省长春外国语学校2016届上学期高三第一次质量检测】设集合}log ,3{2a P =,{}b a Q ,=,若}0{=Q P ,则=Q P ________.13.【2016届河北省邯郸市馆陶县一中高三7月调研考试】下列说法中,正确的是________.①任取x >0,均有3x >2x ;②当a >0,且a ≠1时,有a 3>a 2; ③y =(3)-x 是增函数;④y =2|x |的最小值为1; ⑤在同一坐标系中,y =2x 与y =2-x的图象关于y 轴对称. 14.【2016届湖北省部分重点中学高三上学期起点考试】以A 表示值域为R 的函数组成的集合,B 表示具有如下性质的函数()x ϕ组成的集合:对于函数()x ϕ,存在一个正数M ,使得函数()x ϕ的值域包含于区间[,]MM -.例如,当31()x x ϕ=,2()s i n x x ϕ=时,1()x A ϕ∈,2()x B ϕ∈.现有如下命题: ①设函数()f x 的定义域为D ,则“()f x A ∈”的充要条件是“b ∀∈R ,a D ∃∈,()f a b =”;②函数()f x B∈的充要条件是()f x 有最大值和最小值; ③若函数()f x ,()g x 的定义域相同,且()f x A ∈,()g x B ∈,则()()f x g x B+∉; ④若函数2()ln(2)1x f x a x x =+++(2x >-,a ∈R )有最大值,则()f x B ∈. 其中的真命题有__________________.(写出所有真命题的序号)二.解答题(6*12=72分)15.【湖北宜昌一中、龙泉中学2016届高三十月联考】已知函数()(2)()f x x x m =-+-(其中2m >-),()22x g x =-﹒(1)若命题“2log ()1g x ≤”是真命题,求x 的取值范围;(2)设命题p :(1,)x ∀∈+∞,()0f x <或()0g x <,若p ⌝是假命题,求m 的取值范围﹒16.【江西临川一中2016届上学期高三期中】已知集合{}015A x ax =∈<+≤R ,()1202B x x a ⎧⎫=∈-<≤≠⎨⎬⎩⎭R . ⑴若B A =,求出实数a 的值;⑵若命题,:A x p ∈命题B x q ∈:且p 是q 的充分不必要条件,求实数a 的取值范围.17.【山东省潍坊第一中学2016届高三10月月考16】已知集合{}2log 8A x x =<,204x B x x ⎧⎫+=<⎨⎬-⎩⎭,{}|1C x a x a =<<+.(1)求集合A B ⋂; (2)若B C B ⋃=,求实数a 的取值范围.18.【山东省潍坊第一中学2016届高三10月月考】设命题p :函数1y kx =+在R 上是增函数,命题q :x ∃∈R ,2(23)10x k x +-+=,如果p q ∧是假命题,p q ∨是真命题,求k 的取值范围.19.【辽宁省葫芦岛市一高2016届上学期期中考试】已知命题p :函数()log 21a y x =+在定义域上单调递增;命题q :不等式2(2)2(2)40a x a x -+--<对任意实数x 恒成立,若p 且q ⌝为真命题,求实数a 的取值范围.20.【江苏省阜宁中学2016届高三年级第一次调研考试】已知命题p :指数函数()()26xf x a =-在R 上是单调减函数;命题q :关于x 的方程223210x ax a -++=的两根均大于3,若p 或q 为真,p 且q 为假,求实数a 的范围.。

数理逻辑考试题

数理逻辑考试题

1. 证明:对于任意命题P和Q,如果P∧¬Q为假,则P∧Q为真。

2. 设A、B是两个命题,若A→B为真,则称A是B的充分条件。

请给出以下命题的充分条件定义:

(1) 如果一个整数是偶数,那么这个整数可以被2整除。

(2) 如果一个三角形的三条边满足勾股定理,那么这个三角形是一个直角三角形。

3. 设A、B、C是三个命题,若A∧B∧C为真,则称A、B、C互为充要条件。

请给出以下命题的充要条件定义:

(1) 如果一个整数是偶数,那么这个整数可以被2整除。

(2) 如果一个三角形的三条边满足勾股定理,那么这个三角形是一个直角三角形。

4. 设P、Q是两个命题,若¬P∧Q为真,则称P是Q的必要条件。

请给出以下命题的必要条件定义:

(1) 如果一个整数是偶数,那么这个整数可以被2整除。

(2) 如果一个三角形的三条边满足勾股定理,那么这个三角形是一个直角三角形。

5. 设A、B是两个命题,若¬A→B为真,则称A是B的逆否命题。

请给出以下命题的逆否命题定义:

(1) 如果一个整数是偶数,那么这个整数可以被2整除。

(2) 如果一个三角形的三条边满足勾股定理,那么这个三角形是一个直角三角形。

2020届人教A版_常用逻辑用语-单元测试

常用逻辑用语一、单选题 1.“1-=m”是直线01)12(=+-+y m mx 和直线033=++my x 垂直的( )条件A .充分不必要B .必要不充分C .充要D .既不充分也不必要【答案】A【解析】若直线01)12(=+-+ym mx 和直线033=++my x 垂直,则3(21)0m m m +-=,即1m =-或0m =, 所以1m =-是这两条直线垂直的充分不必要条件。

2.椭圆()2210y x m m+=>的离心率大于12的充分必要条件是( )A.14m <B.3443m <<C.34m > D.304m <<或43m > 【答案】D 【解析】试题分析:设椭圆的离心率为e ,当1m >时,焦点落在y 轴上,2114m e m -=>,解得43m >;当01m <<时,焦点落在x 轴上,则21130144m e m -=>⇒<<,综上所示,实数m 的取值范围是340,,43⎛⎫⎛⎫+∞ ⎪ ⎪⎝⎭⎝⎭,故选D. 考点:1.椭圆的离心率;2.充分必要条件3.已知命题p: “若x 2−x >0,则x >1”;命题q: “若x,y ∈R ,x 2+y 2=0,则xy =0”,则下列命题是真命题的是( )A .p ∨(¬q )B .p ∨qC .p ∧qD .(¬p )∧(¬q ) 【答案】B 【解析】【分析】先分别判定命题p,q的真假性,再根据选项判断复合命题的真假性。

【详解】求解一元二次不等式x2−x>0可得x>1或x<0,命题p是假命题;若x,y∈R,x2+y2=0,则x=y=0,此时xy=0,命题q为真命题;逐一考查所给命题的真假:A.p∨(¬q)是假命题;B.p∨q是真命题;C.p∧q是假命题;D.(¬p)∧(¬q)是假命题;故选B.【点睛】复合命题的真假性由真值表判定:4.下列命题为真命题的是().A.若x>y>0,则lnx+lny>0”是“函数y=sin(2x+φ)为偶函数”的充要条件B.“φ=π2C.∃x0∈(−∞,0),使3x0<4x0成立D.已知两个平面α,β,若两条异面直线m,n满足m⊂α,n⊂β且m//β,n//α,则α//β【答案】D【解析】对于A:令x=1,y=1,则lnx+lny=−1>0不成立,故排除A;e”是“函数y=sin(2x+φ)为偶函数”的充分不必要条件,故排除B;对于B:“φ=π2对于C:根据幂函数y=xα,当α<0时,函数单调递减,故不存在x0∈(−∞,0),使3x0< 4x0成立,故排除C;对于D:已知两个平面α,β,若两条异面直线m,n满足m⊂α,n⊂β且m//β,n//α,可过n作一个平面与平面α相交于n′,由线面平行的性质定理可得n′//n,再由线面平行的判断定理可得,n′//β,由面面平行的判断定理可得α//β,所以D正确;故选D. 5.已知下列命题中:(1)若k R ∈,且0kb =,则0k =或0b =,(2)若0a b ⋅=,则0a =或0b =(3)若不平行的两个非零向量b a ,,满足||||b a =,则0)()(=-⋅+b a b a (4)若a 与b 平行,则||||a b a b =⋅其中真命题的个数是( ) A .0 B .1 C .2 D .3 【答案】C 【解析】试题分析:对于(1)若k R ∈,且0kb =,则0k =或0b =,成立。

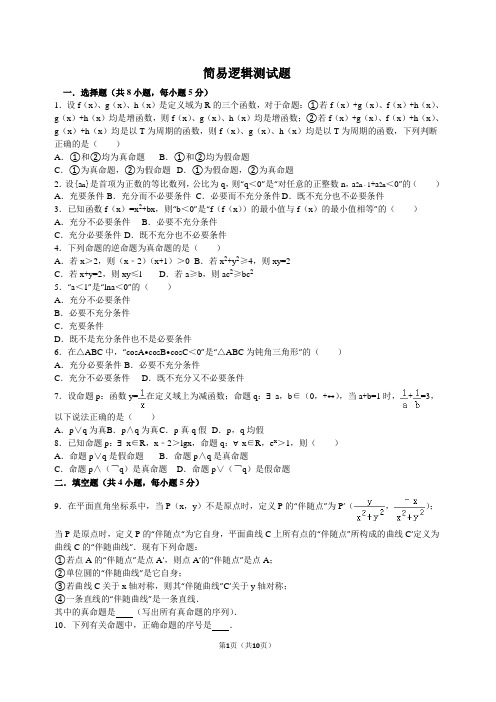

简易逻辑测试题

简易逻辑测试题一.选择题(共8小题,每小题5分)1.设f(x)、g(x)、h(x)是定义域为R的三个函数,对于命题:①若f(x)+g(x)、f(x)+h(x)、g(x)+h(x)均是增函数,则f(x)、g(x)、h(x)均是增函数;②若f(x)+g(x)、f(x)+h(x)、g(x)+h(x)均是以T为周期的函数,则f(x)、g(x)、h(x)均是以T为周期的函数,下列判断正确的是()A.①和②均为真命题B.①和②均为假命题C.①为真命题,②为假命题D.①为假命题,②为真命题2.设{a n}是首项为正数的等比数列,公比为q,则“q<0”是“对任意的正整数n,a2n﹣1+a2n<0”的()A.充要条件 B.充分而不必要条件C.必要而不充分条件 D.既不充分也不必要条件3.已知函数f(x)=x2+bx,则“b<0”是“f(f(x))的最小值与f(x)的最小值相等”的()A.充分不必要条件B.必要不充分条件C.充分必要条件 D.既不充分也不必要条件4.下列命题的逆命题为真命题的是()A.若x>2,则(x﹣2)(x+1)>0 B.若x2+y2≥4,则xy=2C.若x+y=2,则xy≤l D.若a≥b,则ac2≥bc25.“a<1”是“lna<0”的()A.充分不必要条件B.必要不充分条件C.充要条件D.既不是充分条件也不是必要条件6.在△ABC中,“cosA•cosB•cosC<0”是“△ABC为钝角三角形”的()A.充分必要条件 B.必要不充分条件C.充分不必要条件D.既不充分又不必要条件7.设命题p:函数y=在定义域上为减函数;命题q:∃a,b∈(0,+∞),当a+b=1时,+=3,以下说法正确的是()A.p∨q为真B.p∧q为真C.p真q假D.p,q均假8.已知命题p:∃x∈R,x﹣2>lgx,命题q:∀x∈R,e x>1,则()A.命题p∨q是假命题B.命题p∧q是真命题C.命题p∧(¬q)是真命题D.命题p∨(¬q)是假命题二.填空题(共4小题,每小题5分)9.在平面直角坐标系中,当P(x,y)不是原点时,定义P的“伴随点”为P′(,);当P是原点时,定义P的“伴随点“为它自身,平面曲线C上所有点的“伴随点”所构成的曲线C′定义为曲线C的“伴随曲线”.现有下列命题:①若点A的“伴随点”是点A′,则点A′的“伴随点”是点A;②单位圆的“伴随曲线”是它自身;③若曲线C关于x轴对称,则其“伴随曲线”C′关于y轴对称;④一条直线的“伴随曲线”是一条直线.其中的真命题是(写出所有真命题的序列).10.下列有关命题中,正确命题的序号是.①命题“若x2=1,则x=1”的否命题为“若x2=1,则x≠1”;②命题“∃x∈R,x2+x﹣1<0”的否定是“∀x∈R,x2+x﹣1>0”;③命题“若x=y,则sinx=siny”的逆否命题是假命题.④若“p或q为真命题,则p,q至少有一个为真命题.”11.已知函数f(x)=x2﹣2x,g(x)=ax﹣2(a>0),若∀x∈[﹣1,2],恒有(x)>g(x)成立,则a的取值范围是;若∀x1∈[﹣1,2],∃x2∈[﹣1,2],使得(x1)=g(x2),则实数a的取值范围是.12.若函数同时满足以下两个条件:①∀x∈R,f(x)<0或g(x)<0;②∃x∈(﹣1,1),f(x)g(x)<0.则实数a的取值范围为.三.解答题(共4小题,每小题10分)13.已知命题P:“函数在(﹣1,+∞)上单调递增.”命题Q:“幂函数在(0,+∞)上单调递减”.(1)若命题P和命题Q同时为真,求实数m的取值范围;(2)若命题P和命题Q有且只有一个真命题,求实数m的取值范围.14.已知p:|1﹣|<2;q:x2﹣2x+1﹣m2<0;若¬p是¬q的充分非必要条件,求实数m的取值范围.15.已知a>0设命题p:函数y=()x为增函数,命题q:当x∈[,2]时,函数f(x)=x+>恒成立.如果p∨q为真命题,p∧q为假命题,求a的取值范围.16.已知命题p:方程+=1表示焦点在y轴上的椭圆,命题q:关于x的方程x2+2mx+2m+3=0无实根,若“p∧q”为假命题,“p∨q”为真命题,求实数m的取值范围.简易逻辑测试题参考答案与试题解析一.选择题(共8小题)1.(2016•上海)设f(x)、g(x)、h(x)是定义域为R的三个函数,对于命题:①若f(x)+g(x)、f(x)+h(x)、g(x)+h(x)均是增函数,则f(x)、g(x)、h(x)均是增函数;②若f(x)+g(x)、f(x)+h(x)、g(x)+h(x)均是以T为周期的函数,则f(x)、g(x)、h(x)均是以T为周期的函数,下列判断正确的是()A.①和②均为真命题B.①和②均为假命题C.①为真命题,②为假命题D.①为假命题,②为真命题【分析】①举反例说明命题不成立;②根据定义得f(x)+g(x)=f(x+T)+g(x+T),f(x)+h(x)=f(x+T)+h(x+T),h(x)+g(x)=h(x+T)+g(x+T),由此得出:g(x)=g(x+T),h(x)=h(x+T),f(x)=f(x+T),即可判断出真假.【解答】解:对于①,举反例说明:f(x)=2x,g(x)=﹣x,h(x)=3x;f(x)+g(x)=x,f(x)+h(x)=5x,g(x)+h(x)=2x都是定义域R上的增函数,但g(x)=﹣x不是增函数,所以①是假命题;对于②,根据周期函数的定义,f(x)+g(x)=f(x+T)+g(x+T),f(x)+h(x)=f(x+T)+h(x+T),h(x)+g(x)=h(x+T)+g(x+T),前两式作差可得:g(x)﹣h(x)=g(x+T)﹣h(x+T),结合第三式可得:g(x)=g(x+T),h(x)=h(x+T),同理可得:f(x)=f(x+T),所以②是真命题.故选:D.【点评】本题考查了函数的单调性与周期性、简易逻辑的判定方法,考查了推理能力与计算能力,属于基础题目.2.(2016•天津)设{a n}是首项为正数的等比数列,公比为q,则“q<0”是“对任意的正整数n,a2n﹣1+a2n <0”的()A.充要条件 B.充分而不必要条件C.必要而不充分条件 D.既不充分也不必要条件【分析】利用必要、充分及充要条件的定义判断即可.【解答】解:{a n}是首项为正数的等比数列,公比为q,若“q<0”是“对任意的正整数n,a2n﹣1+a2n<0”不一定成立,例如:当首项为2,q=﹣时,各项为2,﹣1,,﹣,…,此时2+(﹣1)=1>0,+(﹣)=>0;而“对任意的正整数n,a2n﹣1+a2n<0”,前提是“q<0”,则“q<0”是“对任意的正整数n,a2n﹣1+a2n<0”的必要而不充分条件,故选:C.【点评】此题考查了必要条件、充分条件与充要条件的判断,熟练掌握各自的定义是解本题的关键.3.(2016•浙江)已知函数f(x)=x2+bx,则“b<0”是“f(f(x))的最小值与f(x)的最小值相等”的()A.充分不必要条件B.必要不充分条件C.充分必要条件 D.既不充分也不必要条件【分析】求出f(x)的最小值及极小值点,分别把“b<0”和“f(f(x))的最小值与f(x)的最小值相等”当做条件,看能否推出另一结论即可判断.【解答】解:f(x)的对称轴为x=﹣,f min(x)=﹣.(1)若b<0,则﹣>﹣,∴当f(x)=﹣时,f(f(x))取得最小值f(﹣)=﹣,即f(f(x))的最小值与f(x)的最小值相等.∴“b<0”是“f(f(x))的最小值与f(x)的最小值相等”的充分条件.(2)若f(f(x))的最小值与f(x)的最小值相等,则f min(x)≤﹣,即﹣≤﹣,解得b≤0或b≥2.∴“b<0”不是“f(f(x))的最小值与f(x)的最小值相等”的必要条件.故选A.【点评】本题考查了二次函数的性质,简易逻辑关系的推导,属于基础题.4.(2016•威海二模)下列命题的逆命题为真命题的是()A.若x>2,则(x﹣2)(x+1)>0 B.若x2+y2≥4,则xy=2C.若x+y=2,则xy≤l D.若a≥b,则ac2≥bc2【分析】分别写出相应的逆命题,再判断真假即可.【解答】解:选项A,“若x>2,则(x﹣2)(x+1)>0”的逆命题为“若(x﹣2)(x+1)>0,则x>2”因为(x﹣2)(x+1)>0得到x>2或x<﹣1,所以是假命题,选项B,“若x2+y2≥4,则xy=2”的逆命题为“若xy=2,则x2+y2≥2xy=4”是真命题,选项C,“若x+y=2,则xy≤l”的逆命题为“若xy≤l,则x+y=2”,因为x=2,y=,满足xy≤l,但不满足x+y=2,所以是假命题,选项D,“若a≥b,则ac2≥bc2”的逆命题为“若ac2≥bc2,则a≥b”,因为若c=0,a=1,b=2,满足ac2≥bc2,但不满足a≥b,所以是假命题.故选:B.【点评】本题考查了命题的逆命题和命题的真假判断,属于基础题.5.(2016•衡阳二模)“a<1”是“lna<0”的()A.充分不必要条件B.必要不充分条件C.充要条件D.既不是充分条件也不是必要条件【分析】当a=0时,满足a<1,但此时lna<0不成立.若lna<0,由对数函数得性质得0<a<1,满足a<1.【解答】解:a<1推不出“lna<0”,比如当a=0时.若lna<0,由对数函数得性质得0<a<1,满足a<1.故选B.【点评】本题利用对数的知识考查充要条件的知识.属于基础题.6.(2016•上海模拟)在△ABC中,“cosA•cosB•cosC<0”是“△ABC为钝角三角形”的()A.充分必要条件 B.必要不充分条件C.充分不必要条件D.既不充分又不必要条件【分析】根据三角形的几何特征,及余弦函数的符号,我们分别确定“cosA•cosB•cosC<0”⇒“△ABC 为钝角三角形”与“△ABC为钝角三角形”⇒“cosA•cosB•cosC<0”的真假,进而根据充要条件的定义,即可得到答案.【解答】解:由于△ABC中,A,B,C只少存在两个锐角故cosA,cosB,cosC中至少有两个正值则“cosA•cosB•cosC<0”⇒“△ABC为钝角三角形”为真命题;“△ABC为钝角三角形”⇒“cosA•cosB•cosC<0”为真命题;故“cosA•cosB•cosC<0”是“△ABC为钝角三角形”的充要条件故选A【点评】本题考查的知识点是充要条件的定义,余弦函数的符号,其中判断出“cosA•cosB•cosC<0”⇒“△ABC为钝角三角形”与“△ABC为钝角三角形”⇒“cosA•cosB•cosC<0”的真假,是解答本题的关键.7.(2016•河池校级一模)设命题p:函数y=在定义域上为减函数;命题q:∃a,b∈(0,+∞),当a+b=1时,+=3,以下说法正确的是()A.p∨q为真B.p∧q为真C.p真q假D.p,q均假【分析】根据反比例函数的单调性知,它在定义域上没有单调性,所以命题p是假命题;根据a+b=1得b=1﹣a,带入,看能否解出a,经计算解不出a,所以命题q是假命题,即p,q均假,所以D是正确的.【解答】解:函数y=在(﹣∞,0),(0,+∞)上是减函数,在定义域{x|x≠0}上不具有单调性,∴命题p是假命题;由a+b=1得b=1﹣a,带入并整理得:3a2﹣3a+1=0,∴△=9﹣12<0,∴该方程无解,即不存在a,b∈(0,+∞),当a+b=1时,,∴命题q是假命题;∴p,q均价,∴p∨q为假,p∧q为假;故选D.【点评】考查反比例函数的单调性,定义域,一元二次方程的解和判别式△的关系.8.(2016•大庆校级模拟)已知命题p:∃x∈R,x﹣2>lgx,命题q:∀x∈R,e x>1,则()A.命题p∨q是假命题B.命题p∧q是真命题C.命题p∧(¬q)是真命题D.命题p∨(¬q)是假命题【分析】利用函数的性质先判定命题p,q的真假,再利用复合命题真假的判定方法即可得出.【解答】解:对于命题p:例如当x=10时,8>1成立,故命题p是真命题;对于命题q:∀x∈R,e x>1,当x=0时命题不成立,故命题q是假命题;∴命题p∧¬q是真命题.故选:C.【点评】本题考查了复合命题真假的判定方法、函数的性质,属于基础题.二.填空题(共4小题)9.(2016秋•杨浦区校级月考)在平面直角坐标系中,当P(x,y)不是原点时,定义P的“伴随点”为P′(,);当P是原点时,定义P的“伴随点“为它自身,平面曲线C上所有点的“伴随点”所构成的曲线C′定义为曲线C的“伴随曲线”.现有下列命题:①若点A的“伴随点”是点A′,则点A′的“伴随点”是点A;②单位圆的“伴随曲线”是它自身;③若曲线C关于x轴对称,则其“伴随曲线”C′关于y轴对称;④一条直线的“伴随曲线”是一条直线.其中的真命题是②③(写出所有真命题的序列).【分析】利用新定义,对4个命题分别进行判断,即可得出结论.【解答】解:①若点A(x,y)的“伴随点”是点A′(,),则点A′(,)的“伴随点”是点(﹣x,﹣y),故不正确;②由①可知,单位圆的“伴随曲线”是它自身,故正确;③若曲线C关于x轴对称,点A(x,y)关于x轴的对称点为(x,﹣y),“伴随点”是点A′(﹣,),则其“伴随曲线”C′关于y轴对称,故正确;④设直线方程为y=kx+b(b≠0),点A(x,y)的“伴随点”是点A′(m,n),则∵点A(x,y)的“伴随点”是点A′(,),∴,∴x=﹣,y=∵m=,∴代入整理可得n﹣1=0表示圆,故不正确.故答案为:②③.【点评】此题考查点的坐标规律,读懂题目信息,理解“伴随点”的定义是解题的关键.10.(2016•汕头模拟)下列有关命题中,正确命题的序号是④.①命题“若x2=1,则x=1”的否命题为“若x2=1,则x≠1”;②命题“∃x∈R,x2+x﹣1<0”的否定是“∀x∈R,x2+x﹣1>0”;③命题“若x=y,则sinx=siny”的逆否命题是假命题.④若“p或q为真命题,则p,q至少有一个为真命题.”【分析】分别对①②③④进行判断,从而得到结论.【解答】解:①命题“若x2=1,则x=1”的否命题为“若x2≠1,则x≠1”;故①错误;②命题“∃x∈R,x2+x﹣1<0”的否定是“∀x∈R,x2+x﹣1≥0”;故②错误;③命题“若x=y,则sinx=siny”的逆否命题是若sinx≠siny,则x≠y,是真命题,故③错误;④若“p或q为真命题,则p,q至少有一个为真命题.”,正确;故答案为:④.【点评】本题考察了命题的否定以及命题之间的关系,是一道基础题.11.(2016•东阳市模拟)已知函数f(x)=x2﹣2x,g(x)=ax﹣2(a>0),若∀x∈[﹣1,2],恒有(x)>g(x)成立,则a的取值范围是0<a<2﹣2;若∀x1∈[﹣1,2],∃x2∈[﹣1,2],使得(x1)=g(x2),则实数a的取值范围是a≥.【分析】①∀x∈[﹣1,2],恒有f(x)>g(x)成立,化为“∀x∈[﹣1,2],h(x)=f(x)﹣g(x)>0恒成立”,由此求出实数a的取值范围;②∀x1∈[﹣1,2],∃x2∈[﹣1,2],使得f(x1)=g(x2),转化为x2∈[﹣1,2]时,g(x2)的值域A与f(x1)的值域B的关系是A⊇B,由此求出实数a的取值范围.【解答】解:①根据题意,当∀x∈[﹣1,2]时,恒有f(x)>g(x)成立,即∀x∈[﹣1,2],h(x)=f(x)﹣g(x)>0恒成立,又a>0时,h(x)=(x2﹣2x)﹣(ax﹣2)=x2﹣(2+a)x+2的对称轴是x=1+>1,所以,当1+≤2,即a≤2时,h(x)在x∈[﹣1,2]上的最小值是h(1+)=﹣(2+a)(1+)+2=﹣+2>0,解得0<a<2﹣2;当1+>2,即a>2时,h(x)在x∈[﹣1,2]上是减函数,最小值是h(2)=4﹣2(2+a)+2>0,解得a<1,不满足题意,舍去;综上,实数a的取值范围是0<a<2﹣2;②由①知,∀x1∈[﹣1,2]时,f(x1)=[﹣1,3];又∀x1∈[﹣1,2],都∃x2∈[﹣1,2],使得f(x1)=g(x2),∴当x2∈[﹣1,2]时,a>0,g(x)=ax﹣2是增函数,g(x2)的值域为[g(﹣1),g(2)],且满足[g(﹣1),g(2)]⊇[﹣1,3];即,解得a≥;∴实数a的取值范围是a≥.故答案为:0<a≤;a≥.【点评】本题考查了二次函数在闭区间上的最值问题,解题时应根据题意构造函数,求出函数的最值和值域,分类解答,是综合性题目.12.(2016•江苏模拟)若函数同时满足以下两个条件:①∀x∈R,f(x)<0或g(x)<0;②∃x∈(﹣1,1),f(x)g(x)<0.则实数a的取值范围为(2,4).【分析】由①可得当x≤﹣1时,g(x)<0,根据②可得g(1)=a(1﹣a+3)>0,由此解得实数a 的取值范围.【解答】解:∵已知函数,根据①∀x∈R,f(x)<0,或g(x)<0,即函数f(x)和函数g(x)不能同时取非负值.由f(x)≥0,求得x≤﹣1,即当x≤﹣1时,g(x)<0恒成立,故,解得:a>2;根据②∃x∈(﹣1,1),使f(x)•g(x)<0成立,∴g(1)=a(1﹣a+3)>0,解得:0<a<4,综上可得:a∈(2,4),故答案为:(2,4)【点评】本题主要考查一次函数的性质,指数函数的图象和性质,体现了转化、数形结合的数学思想,难度较大.三.解答题(共4小题)13.(2016•江西模拟)已知命题P:“函数在(﹣1,+∞)上单调递增.”命题Q:“幂函数在(0,+∞)上单调递减”.(1)若命题P和命题Q同时为真,求实数m的取值范围;(2)若命题P和命题Q有且只有一个真命题,求实数m的取值范围.【分析】(1)由题设知P:m<1,Q:﹣1<m<3,由此能求出当命题P和命题Q同时为真时,实数m的取值范围.(2)当命题P和命题Q有且仅有一个真时,P真Q假,或P假Q真,由此能求了若命题P和命题Q 有且只有一个真命题时,实数m的取值范围.【解答】解:(1)∵命题P:“函数在(﹣1,+∞)上单调递增.”命题Q:“幂函数在(0,+∞)上单调递减”.∴P:m<1,Q:﹣1<m<3,∴当命题P和命题Q同时为真时,实数m的取值范围是:﹣1<m<1.(2)当命题P和命题Q有且仅有一个真时,P真Q假,或P假Q真,当P真Q假时,,解得实数m的取值范围是:m≤﹣1.当P假Q真时时,,解得实数m的取值范围是:1≤m<3.综上所述,若命题P和命题Q有且只有一个真命题,实数m的取值范围(﹣∞,﹣1]∪[1,3).【点评】本题考查复合命题的真假,是基础题.解题时要认真审题,仔细解答.14.(2016•淮南一模)已知p:|1﹣|<2;q:x2﹣2x+1﹣m2<0;若¬p是¬q的充分非必要条件,求实数m的取值范围.【分析】¬p是¬q的充分非必要条件,所以q是p的充分非必要条件,求出p、q的范围进而求解.【解答】解:p:|1﹣|<2即为p:﹣2<x<10,q:x2﹣2x+1﹣m2<0即为(x﹣1)2<m2,即q:1﹣|m|<x<1+|m|,又¬p是¬q的充分非必要条件,所以q是p的充分非必要,∴(两式不能同时取等)得到|m|≤3,满足题意,所以m的范围为[﹣3,3].【点评】解决命题间的条件问题应该先将各个命题化简,若各个命题是由数集组成,可将条件问题转化为集合的包含关系问题.15.(2016春•福州校级期末)已知a>0设命题p:函数y=()x为增函数,命题q:当x∈[,2]时,函数f(x)=x+>恒成立.如果p∨q为真命题,p∧q为假命题,求a的取值范围.【分析】先求出命题p,q成立的等价条件,利用p∨q为真命题,p∧q为假命题,确定实数a的取值范围.【解答】解:由y=()x为增函数得,0<a<1,即p:0<a<1.∵f(x)在[,1]上为减函数,在[1,2]上为增函数.∴f(x)在x∈[,2]上最小值为f(1)=2.当x∈[,2]时,由函数f(x)=x+>恒成立得,2>,解得a>,即q:a>.若“p∨q”为真命题,且“p∧q”为假命题,则p,q一真一假.如果p真且q假,则0<a≤.如果p假且q真,则a≥1.∴a的取值范围为(0,]∪[1,+∞).【点评】本题主要考查复合命题与简单命题之间的关系,利用条件先求出命题p,q的等价条件是解决本题的关键.16.(2016春•遵义期末)已知命题p:方程+=1表示焦点在y轴上的椭圆,命题q:关于x的方程x2+2mx+2m+3=0无实根,若“p∧q”为假命题,“p∨q”为真命题,求实数m的取值范围.【分析】先将命题p,q化简,然后由“p∧q”为假命题,“p∨q”为真命题得出p,q恰有一真一假,分类讨论即可.【解答】解:∵方程+=1表示焦点在y轴上的椭圆,∴m>2;∵关于x的方程x2+2mx+2m+3=0无实根,∴4m2﹣4(2m+3)<0,解得﹣1<m<3,“p∧q”为假命题,“p∨q”为真命题⇔p,q恰有一真一假,①若“p真q假”,则,即m≥3,②若“p假q真”,则,即﹣1<m≤2,综上,实数m的取值范围是(﹣1,2]∪[3,+∞).【点评】本题的关键是在于对命题的联结词的掌握,由“p∧q”为假命题,“p∨q”为真命题得出p,q恰有一真一假.。

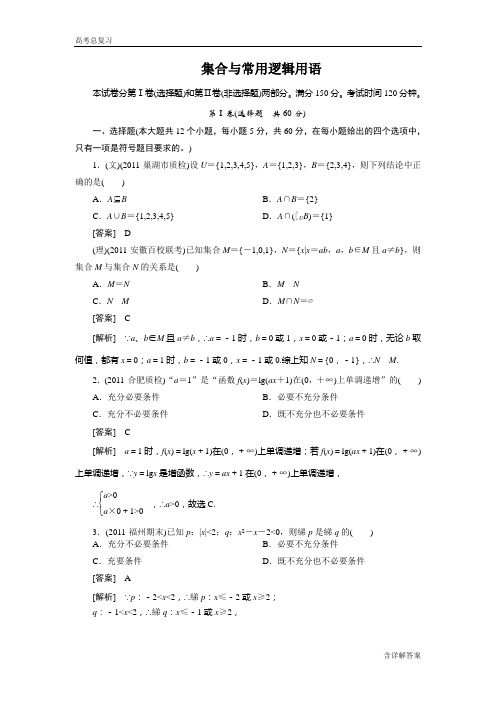

集合与常用逻辑用语测试题及详解

集合与常用逻辑用语本试卷分第Ⅰ卷(选择题)和第Ⅱ卷(非选择题)两部分。

满分150分。

考试时间120分钟。

第Ⅰ卷(选择题 共60分)一、选择题(本大题共12个小题,每小题5分,共60分,在每小题给出的四个选项中,只有一项是符号题目要求的。

)1.(文)(2011·巢湖市质检)设U ={1,2,3,4,5},A ={1,2,3},B ={2,3,4},则下列结论中正确的是( )A .A ⊆B B .A ∩B ={2}C .A ∪B ={1,2,3,4,5}D .A ∩(∁U B )={1}[答案] D(理)(2011·安徽百校联考)已知集合M ={-1,0,1},N ={x |x =ab ,a ,b ∈M 且a ≠b },则集合M 与集合N 的关系是( )A .M =NB .M NC .N MD .M ∩N =∅[答案] C[解析] ∵a 、b ∈M 且a ≠b ,∴a =-1时,b =0或1,x =0或-1;a =0时,无论b 取何值,都有x =0;a =1时,b =-1或0,x =-1或0.综上知N ={0,-1},∴N M .2.(2011·合肥质检)“a =1”是“函数f (x )=lg(ax +1)在(0,+∞)上单调递增”的( ) A .充分必要条件 B .必要不充分条件 C .充分不必要条件 D .既不充分也不必要条件[答案] C[解析] a =1时,f (x )=lg(x +1)在(0,+∞)上单调递增;若f (x )=lg(ax +1)在(0,+∞)上单调递增,∵y =lg x 是增函数,∴y =ax +1在(0,+∞)上单调递增,∴⎩⎪⎨⎪⎧a >0a ×0+1>0,∴a >0,故选C. 3.(2011·福州期末)已知p :|x |<2;q :x 2-x -2<0,则綈p 是綈q 的( ) A .充分不必要条件 B .必要不充分条件 C .充要条件 D .既不充分也不必要条件[答案] A[解析] ∵p :-2<x <2,∴綈p :x ≤-2或x ≥2; q :-1<x <2,∴綈q :x ≤-1或x ≥2, ∴綈p 是綈q 的充分不必要条件.4.(2011·福州期末)在△ABC 中,“AB →·AC →=BA →·BC →”是“|AC →|=|BC →|”的( ) A .充分不必要条件B .必要不充分条件C .充要条件D .既不充分也不必要条件[答案] C[解析] 如图,在△ABC 中,过C 作CD ⊥AB ,则|AD →|=|AC →|·cos ∠CAB ,|BD →|=|BC →|·cos ∠CBA ,AB →·AC →=BA →·BC →⇔|AB →|·|AC →|·cos ∠CAB =|BA →|·|BC →|·cos ∠CBA ⇔|AC →|·cos ∠CAB =|BC →|·cos ∠CBA ⇔|AD →|=|BD →|⇔|AC →|=|BC →|,故选C.5.(文)(2011·山东日照调研)设α、β是两个不同的平面,l 、m 为两条不同的直线,命题p :若α∥β,l ⊂α,m ⊂β则l ∥m ;命题q :l ∥α,m ⊥l ,m ⊂β,则α⊥β.则下列命题为真命题的是( )A .p 或qB .p 且qC .綈p 或qD .p 且綈q[答案] C[解析] p 为假命题,q 为假命题,故p 或q ,p 且q ,p 且綈q 均为假命题,选C. (理)(2011·辽宁省丹东四校联考)已知α、β、γ为互不重合的三个平面,命题p :若α⊥β,β⊥γ,则α∥γ;命题q :若α上不共线的三点到β的距离相等,则α∥β.对以上两个命题,下列结论中正确的是( )A .命题“p 且q ”为真B .命题“p 或綈q ”为假C .命题“p 或q ”为假D .命题“綈p 且綈q ”为假[答案] C[解析] 如图(1),正方体中,相邻三个面满足β⊥α,β⊥γ,但α⊥γ,故p 为假命题;如图(2),α∩β=l ,直线AB ,CD 是α内与l 平行且与l 距离相等的两条直线,则直线AB ,CD 上任意一点到平面β的距离都相等,三点A 、B 、C 不共线,且到平面β的距离相等,故命题q 为假命题,∴“p 或q ”为假命题.6.(2011·宁夏银川一中检测)下列结论错误的...是()A.命题“若p,则q”与命题“若綈q,则綈p”互为逆否命题B.命题p:∀x∈[0,1],e x≥1,命题q:∃x∈R,x2+x+1<0,则p∨q为真C.“若am2<bm2,则a<b”的逆命题为真命题D.若p∨q为假命题,则p、q均为假命题[答案] C[解析]根据四种命题的构成规律,选项A中的结论是正确的;选项B中的命题p是真命题,命题q是假命题,故p∨q为真命题,选项B中的结论正确;当m=0时,a<b⇒/ am2<bm2,故选项C中的结论不正确;选项D中的结论正确.7.(文)(2011·福州期末)已知集合M={y|y=x2+1,x∈R},N={y|y=x+1,x∈R},则M∩N等于()A.(0,1),(1,2) B.{(0,1),(1,2)}C.{y|y=1或y=2} D.{y|y≥1}[答案] D[解析]由集合M、N的代表元素知M、N都是数集,排除A、B;又M={y|y≥1},N =R,∴选D.(理)(2011·陕西宝鸡质检)已知集合A={x|y=1-x2,x∈Z},B={y|y=x2+1,x∈A},则A∩B为()A.∅B.{1}C.[0,+∞) D.{(0,1)}[答案] B[解析]由1-x2≥0得,-1≤x≤1,∵x∈Z,∴A={-1,0,1},当x∈A时,y=x2+1∈{2,1},即B={1,2},∴A∩B={1}.8.(2011·天津河西区质检)命题p:∀x∈[0,+∞),(log32)x≤1,则()A.p是假命题,綈p:∃x0∈[0,+∞),(log32)x0>1B.p是假命题,綈p:∀x∈[0,+∞),(log32)x≥1C.p是真命题,綈p:∃x0∈[0,+∞),(log32)x0>1D.p是真命题,綈p:∀x∈[0,+∞),(log32)x≥1[答案] C[解析] ∵0<log 32<1,∴y =(log 32)x 在[0,+∞)上单调递减,∴0<y ≤1,∴p 是真命题;∀的否定为“∃”,“≤”的否定为“>”,故选C.9.(2010·广东湛江模拟)“若x ≠a 且x ≠b ,则x 2-(a +b )x +ab ≠0”的否命题是( ) A .若x =a 且x =b ,则x 2-(a +b )x +ab =0. B .若x =a 或x =b ,则x 2-(a +b )x +ab ≠0. C .若x =a 且x =b ,则x 2-(a +b )x +ab ≠0. D .若x =a 或x =b ,则x 2-(a +b )x +ab =0. [答案] D10.(2011·四川资阳市模拟)“cos θ<0且tan θ>0”是“θ为第三角限角”的( ) A .充要条件 B .必要不充分条件 C .充分不必要条件 D .既不充分也不必要条件[答案] A[解析] ∵cos θ<0,∴θ为第二或三象限角或终边落在x 轴负半轴上,∵tan θ>0,∴θ为第一或三象限角,∴θ为第三象限角,故选A.11.(文)(2011·湖南长沙一中月考)设命题p :∀x ∈R ,|x |≥x ;q :∃x ∈R ,1x =0.则下列判断正确的是( )A .p 假q 真B .p 真q 假C .p 真q 真D .p 假q 假[答案] B[解析] ∵|x |≥x 对任意x ∈R 都成立,∴p 真,∵1x =0无解,∴不存在x ∈R ,使1x =0,∴q 假,故选B.(理)(2011·福建厦门市期末)下列命题中,假命题是( ) A .∀x ∈R,2x -1>0B .∃x ∈R ,sin x = 2C .∀x ∈R ,x 2-x +1>0D .∃x ∈N ,lg x =2[答案] B[解析] 对任意x ∈R ,总有|sin x |≤1,∴sin x =2无解,故选B.12.(2011·辽宁大连期末)已知全集U =R ,集合A ={x |x =2n ,n ∈N }与B ={x |x =2n ,n ∈N },则正确表示集合A 、B 关系的韦恩(Venn)图是( )[答案] A[解析] n =0时,20=1∈A ,但1∉B,2×0=0∈B ,但0∉A ,又当n =1时,2∈A 且2∈B ,故选A.[点评] 自然数集N 中含有元素0要特别注意,本题极易因忽视0∈N 导致错选C.第Ⅱ卷(非选择题 共90分)二、填空题(本大题共4个小题,每小题4分,共16分,把正确答案填在题中横线上) 13.已知命题甲:a +b ≠4,命题乙:a ≠1且b ≠3,则命题甲是命题乙的________条件. [答案] 既不充分也不必要[解析] 当a +b ≠4时,可选取a =1,b =5,故此时a ≠1且b ≠3不成立(∵a =1).同样,a ≠1且b ≠3时,可选取a =2,b =2,此时a +b =4,因此,甲是乙的既不充分也不必要条件.[点评] 也可通过逆否法判断非乙是非甲的什么条件. 14.方程x 24-t +y 2t -1=1表示曲线C ,给出以下命题:①曲线C 不可能为圆; ②若1<t <4,则曲线C 为椭圆; ③若曲线C 为双曲线,则t <1或t >4; ④若曲线C 为焦点在x 轴上的椭圆,则1<t <52.其中真命题的序号是______(写出所有正确命题的序号). [答案] ③④[解析] 显然当t =52时,曲线为x 2+y 2=32,方程表示一个圆;而当1<t <4,且t ≠52时,方程表示椭圆;当t <1或t >4时,方程表示双曲线,而当1<t <52时,4-t >t -1>0,方程表示焦点在x 轴上的椭圆,故选项为③④.15.(文)函数f (x )=log a x -x +2(a >0且a ≠1)有且仅有两个零点的充要条件是________. [答案] a >1[解析] 若函数f (x )=log a x -x +2(a >0,且a ≠1)有两个零点,即函数y =log a x 的图象与直线y =x -2有两个交点,结合图象易知,此时a >1;当a >1时,函数f (x )=log a x -x +2(a >0,且a ≠1)有两个零点,∴函数f (x )=log a x -x +2(a >0,且a ≠1)有两个零点的充要条件是a >1.(理)(2010·济南模拟)设p :⎩⎪⎨⎪⎧4x +3y -12≥03-x ≥0x +3y ≤12,q :x 2+y 2>r 2(x ,y ∈R ,r >0),若p 是q的充分不必要条件,则r 的取值范围是________.[答案] ⎝⎛⎭⎫0,125 [解析] 设A ={(x ,y )|⎩⎪⎨⎪⎧4x +3y -12≥03-x ≥0x +3y ≤12},B ={(x ,y )|x 2+y 2>r 2,x ,y ∈R ,r >0},则集合A 表示的区域为图中阴影部分,集合B 表示以原点为圆心,以r 为半径的圆的外部,设原点到直线4x +3y -12=0的距离为d ,则d =|4×0+3×0-12|5=125,∵p 是q 的充分不必要条件,∴A B ,则0<r <125.16.(2011·河南豫南九校联考)下列正确结论的序号是________. ①命题∀x ∈R ,x 2+x +1>0的否定是:∃x ∈R ,x 2+x +1<0.②命题“若ab =0,则a =0,或b =0”的否命题是“若ab ≠0,则a ≠0且b ≠0”. ③已知线性回归方程是y ^=3+2x ,则当自变量的值为2时,因变量的精确值为7. ④若a ,b ∈[0,1],则不等式a 2+b 2<14成立的概率是π4.[答案] ②[解析] ∀x ∈R ,x 2+x +1>0的否定应为∃x ∈R ,x 2+x +1≤0,故①错;对于线性回归方程y ^=3+2x ,当x =2时,y 的估计值为7,故③错;对于0≤a ≤1,0≤b ≤1,满足a 2+b 2<14的概率为p =14×π×⎝⎛⎭⎫1221×1=π16,故④错,只有②正确. 三、解答题(本大题共6个小题,共74分,解答应写出文字说明,证明过程或演算步骤) 17.(本小题满分12分)(文)(2011·重庆南开中学期末)已知函数f (x )=x +1x -2的定义域是集合A ,函数g (x )=lg[x 2-(2a +1)x +a 2+a ]的定义域是集合B .(1)分别求集合A 、B ;(2)若A ∪B =B ,求实数a 的取值范围. [解析] (1)A ={x |x ≤-1或x >2} B ={x |x <a 或x >a +1}.(2)由A ∪B =B 得A ⊆B ,因此⎩⎪⎨⎪⎧a >-1a +1≤2所以-1<a ≤1,所以实数a 的取值范围是(-1,1]. (理)已知函数f (x )=6x +1-1的定义域为集合A ,函数g (x )=lg(-x 2+2x +m )的定义域为集合B .(1)当m =3时,求A ∩(∁R B );(2)若A ∩B ={x |-1<x <4},求实数m 的值. [解析] 由6x +1-1≥0知,0<x +1≤6,∴-1<x ≤5,A ={x |-1<x ≤5}. (1)当m =3时,B ={x |-1<x <3} 则∁R B ={x |x ≤-1或x ≥3} ∴A ∩(∁R B )={x |3≤x ≤5}.(2)A ={x |-1<x ≤5},A ∩B ={x |-1<x <4}, ∴有-42+2·4+m =0,解得m =8. 此时B ={x |-2<x <4},符合题意.18.(本小题满分12分)(文)已知函数f (x )是R 上的增函数,a 、b ∈R ,对命题“若a +b ≥0,则f (a )+f (b )≥f (-a )+f (-b ).”(1)写出其逆命题,判断其真假,并证明你的结论; (2)写出其逆否命题,判断其真假,并证明你的结论.[解析] (1)逆命题是:若f (a )+f (b )≥f (-a )+f (-b ),则a +b ≥0,真命题. 用反证法证明:设a +b <0,则a <-b ,b <-a , ∵f (x )是R 上的增函数, ∴f (a )<f (-b ),f (b )<f (-a ),∴f (a )+f (b )<f (-a )+f (-b ),这与题设f (a )+f (b )≥f (-a )+f (-b )矛盾,所以逆命题为真. (2)逆否命题:若f (a )+f (b )<f (-a )+f (-b ), 则a +b <0,为真命题.由于互为逆否命题同真假,故只需证原命题为真. ∵a +b ≥0,∴a ≥-b ,b ≥-a ,又∵f (x )在R 上是增函数, ∴f (a )≥f (-b ),f (b )≥f (-a ).∴f (a )+f (b )≥f (-a )+f (-b ),∴原命题真,故逆否命题为真.(理)(2011·厦门双十中学月考)在平面直角坐标系xOy 中,直线l 与抛物线y 2=2x 相交于A 、B 两点.(1)求证:“如果直线l 过点(3,0),那么OA →·OB →=3”是真命题.(2)写出(1)中命题的逆命题,判断它是真命题还是假命题,并说明理由. [解析] (1)设l :x =ty +3,代入抛物线y 2=2x ,消去x 得y 2-2ty -6=0. 设A (x 1,y 1),B (x 2,y 2),∴y 1+y 2=2t ,y 1·y 2=-6, OA →·OB →=x 1x 2+y 1y 2=(ty 1+3)(ty 2+3)+y 1y 2 =t 2y 1y 2+3t (y 1+y 2)+9+y 1y 2 =-6t 2+3t ·2t +9-6=3. ∴OA →·OB →=3,故为真命题.(2)(1)中命题的逆命题是:“若OA →·OB →=3,则直线l 过点(3,0)”它是假命题. 设l :x =ty +b ,代入抛物线y 2=2x ,消去x 得y 2-2ty -2b =0. 设A (x 1,y 1),B (x 2,y 2),则y 1+y 2=2t ,y 1·y 2=-2b . ∵OA →·OB →=x 1x 2+y 1y 2=(ty 1+b )(ty 2+b )+y 1y 2=t 2y 1y 2+bt (y 1+y 2)+b 2+y 1y 2=-2bt 2+bt ·2t +b 2-2b =b 2-2b , 令b 2-2b =3,得b =3或b =-1,此时直线l 过点(3,0)或(-1,0).故逆命题为假命题.19.(本小题满分12分)(文)(2011·华安、连城、永安、漳平龙海,泉港六校联考)已知集合A ={x |x 2-2x -3≤0,x ∈R },B ={x |x 2-2mx +m 2-4≤0,x ∈R ,m ∈R }.(1)若A ∩B =[0,3],求实数m 的值; (2)若A ⊆∁R B ,求实数m 的取值范围. [解析] A ={x |-1≤x ≤3} B ={x |m -2≤x ≤m +2}. (1)∵A ∩B =[0,3],∴⎩⎪⎨⎪⎧ m -2=0m +2≥3,⎩⎪⎨⎪⎧m =2m ≥1,∴m =2. 故所求实数m 的值为2. (2)∁R B ={x |x <m -2或x >m +2} A ⊆∁R B ,∴m -2>3或m +2<-1. ∴m >5或m <-3.因此实数m 的取值范围是m >5或m <-3.(理)(2011·山东潍坊模拟)已知全集U =R ,非空集合A ={x |x -2x -(3a +1)<0},B ={x |x -a 2-2x -a<0}.(1)当a =12时,求(∁U B )∩A ;(2)命题p :x ∈A ,命题q :x ∈B ,若q 是p 的必要条件,求实数a 的取值范围. [解析] (1)当a =12时,A ={x |x -2x -52<0}={x |2<x <52},B ={x |x -94x -12<0}={x |12<x <94}.∴(∁U B )∩A ={x |x ≤12或x ≥94}∩{x |2<x <52}={x |94≤x <52}.(2)若q 是p 的必要条件,即p ⇒q ,可知A ⊆B , 由a 2+2>a ,得B ={x |a <x <a 2+2}, 当3a +1>2,即a >13时,A ={x |2<x <3a +1},⎩⎪⎨⎪⎧a ≤2a 2+2≥3a +1,解得13<a ≤3-52;当3a +1=2,即a =13时,A =∅,符合题意; 当3a +1<2,即a <13时,A ={x |3a +1<x <2}.⎩⎪⎨⎪⎧a ≤3a +1a 2+2≥2,解得-12≤a <13;综上,a ∈[-12,3-52].20.(本小题满分12分)(2010·常德模拟)已知命题p :∀x ∈[1,2],x 2-a ≥0.命题q :∃x 0∈R ,使得x 20+(a -1)x 0+1<0.若“p 或q ”为真,“p 且q ”为假,求实数a 的取值范围.[解析] 由条件知,a ≤x 2对∀x ∈[1,2]成立,∴a ≤1;∵∃x 0∈R ,使x 20+(a -1)x 0+1<0成立,∴不等式x 2+(a -1)x +1<0有解,∴Δ=(a -1)2-4>0,∴a >3或a <-1; ∵p 或q 为真,p 且q 为假,∴p与q一真一假.①p真q假时,-1≤a≤1;②p假q真时,a>3.∴实数a的取值范围是a>3或-1≤a≤1.21.(本小题满分12分)(文)已知函数f(x)=x2-2x+5,若存在一个实数x0,使不等式f(x0)-m>0成立,求实数m的取值范围.[解析]不等式f(x0)-m>0可化为m<f(x0),若存在一个实数x0使不等式m<f(x0)成立,只需m<f(x)min.又∵f(x)=x2-2x+5=(x-1)2+4,∴f(x)min=4,∴m<4.故所求实数m的取值范围是(-∞,4).(理)(2011·雅安中学期末)设函数f(x)=(x+1)ln(x+1),若对所有的x≥0,都有f(x)≥ax 成立,求实数a的取值范围.[解析]令g(x)=(x+1)ln(x+1)-ax,则g′(x)=ln(x+1)+1-a,令g′(x)=0,解得x=e a-1-1.(1)当a≤1时,对所有x>0,g′(x)>0.所以g(x)在[0,+∞)上是增函数.又g(0)=0,所以对x≥0,有g(x)≥g(0),即当a≤1时,对于所有x≥0,都有f(x)≥ax.(2)当a>1时,对于0<x<e a-1-1,g′(x)<0,所以g(x)在(0,e a-1-1)上是减函数.又g(0)=0,所以对0<x<e a-1-1,有g(x)<g(0),即f(x)<ax.所以当a>1时,不是对所有的x≥0,都有f(x)≥ax成立.综上所述a的取值范围是(-∞,1].22.(本小题满分12分)若规定E={a1,a2,…,a10}的子集{ai1,ai2,…,ai n}为E的第k个子集,其中k=2i1-1+2i2-1+…+2i n-1,则(1){a1,a3}是E的第几个子集?(2)求E的第211个子集.[解析](1)由k的定义可知k=21-1+23-1=5.因此{a1,a3}是E的第5个子集.(2)∵21-1=1,22-1=2,23-1=4,24-1=8,…k=211,且211=128+64+16+2+1,∴i1=1,i2=2,i3=5,i4=7,i5=8,故E的第211个子集是{a1,a2,a5,a7,a8}.高考总复习[点评]本题是新定义题型,构思新颖,视角独特,亮点明显,对考生在新情境下灵活运用所学知识分析,解决问题的能力要求较高,有较高的区分度.含详解答案。

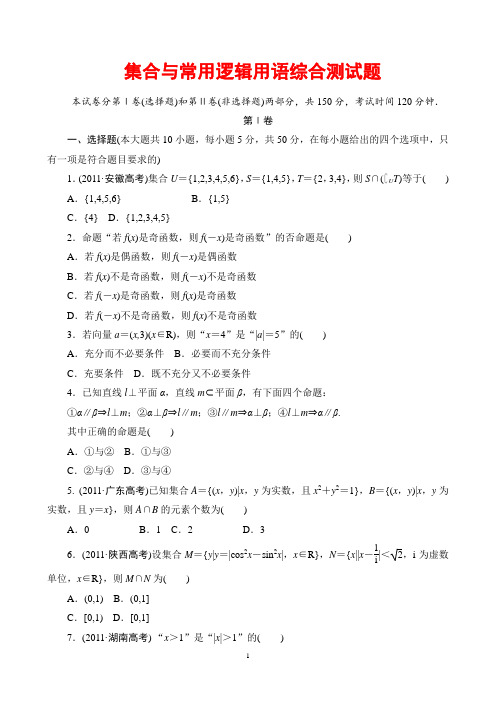

集合与常用逻辑用语综合测试题(基础、好用、含答案)

集合与常用逻辑用语综合测试题本试卷分第Ⅰ卷(选择题)和第Ⅱ卷(非选择题)两部分,共150分,考试时间120分钟.第Ⅰ卷一、选择题(本大题共10小题,每小题5分,共50分,在每小题给出的四个选项中,只有一项是符合题目要求的)1.(2011·安徽高考)集合U={1,2,3,4,5,6},S={1,4,5},T={2,3,4},则S∩(∁U T)等于() A.{1,4,5,6}B.{1,5}C.{4} D.{1,2,3,4,5}2.命题“若f(x)是奇函数,则f(-x)是奇函数”的否命题是()A.若f(x)是偶函数,则f(-x)是偶函数B.若f(x)不是奇函数,则f(-x)不是奇函数C.若f(-x)是奇函数,则f(x)是奇函数D.若f(-x)不是奇函数,则f(x)不是奇函数3.若向量a=(x,3)(x∈R),则“x=4”是“|a|=5”的()A.充分而不必要条件B.必要而不充分条件C.充要条件D.既不充分又不必要条件4.已知直线l⊥平面α,直线m⊂平面β,有下面四个命题:①α∥β⇒l⊥m;②α⊥β⇒l∥m;③l∥m⇒α⊥β;④l⊥m⇒α∥β.其中正确的命题是()A.①与②B.①与③C.②与④D.③与④5. (2011·广东高考)已知集合A={(x,y)|x,y为实数,且x2+y2=1},B={(x,y)|x,y为实数,且y=x},则A∩B的元素个数为()A.0B.1 C.2D.36.(2011·陕西高考)设集合M={y|y=|cos2x-sin2x|,x∈R},N={x||x-1i|<2,i为虚数单位,x∈R},则M∩N为()A.(0,1) B.(0,1]C.[0,1) D.[0,1]7.(2011·湖南高考) “x>1”是“|x|>1”的()A .充分不必要条件B .必要不充分条件C .充分必要条件D .既不充分又不必要条件8.有下列四个命题:①“若xy =1,则x ,y 互为倒数”的逆命题.②“面积相等的三角形全等”的否命题;③“若m ≤1,则x 2-2x +m =0有实数解”的逆否命题;④“若A ∩B =B ,则A B ”的逆否命题.其中真命题为( )A .①②B .②③C .④D .①②③9.(2012·汕尾质检)设0<x <π2,则“x sin 2x <1”是“x sin x <1”的( )A .充分而不必要条件B .必要而不充分条件C .充分必要条件D .既不充分也不必要条件10.(2012·梅州模拟)已知命题p :∃a ,b ∈(0,+∞),当a +b =1时,1a +1b =3,命题q :∀x ∈R ,x 2-x +1≥0恒成立,则下列命题是假命题的是( )A .綈p ∨綈qB .綈p ∧綈qC .綈p ∨qD .綈p ∧q第Ⅱ卷二、填空题(本大题共4小题,每小题5分,共20分.把答案填在题中横线上)11.命题“∃x ∈R ,x =sin x ”的否定是______.12.非零向量a 、b ,“a +b =0”是“a ∥b ”的________条件.13.设P 和Q 是两个集合,定义集合P -Q ={x |x ∈P ,且x ∉Q },若P ={1,2,3,4},Q ={x | x +12<2,x ∈R},则P -Q =________.14.(2012·揭阳模拟)已知函数y =lg(4-x )的定义域为A ,集合B ={x |x <a },若P :“x ∈A ”是Q :“x ∈B ”的充分不必要条件,则实数a 的取值范围________.三、解答题(本大题共6小题,共80分.解答时应写出文字说明、证明过程或演算步骤)15.(本小题满分12分)写出下列命题的否定,并判断真假.(1)p :正数的对数都是正数;(2)p :∀x ∈Z ,x 2的个位数字不等于3.16.(本小题满分13分)已知集合A={y|y2-(a2+a+1)y+a(a2+1)>0},B={y|y=12x2-x+52,0≤x≤3}.(1)若A∩B=∅,求a的取值范围;(2)当a取使不等式x2+1≥ax恒成立的最小值时,求(∁R A)∩B.17.(本小题满分13分)(2012·广州模拟)已知函数f(x)=4sin2(π4+x)-23cos 2x-1,x∈[π4,π2].(1)求f(x)的最大值及最小值;(2)若条件p:f(x)的值域,条件q:“|f(x)-m|<2”,且p是q的充分条件,求实数m的取值范围.18.(本小题满分14分)已知命题p:方程a2x2+ax-2=0在[-1,1]上有解;命题q:只有一个实数x满足不等式x2+2ax+2a≤0,若命题“p或q”是假命题,求a的取值范围.19.(本小题满分14分)命题p:实数x满足x2-4ax+3a2<0,其中a<0;命题q:实数x满足x2-x-6≤0或x2+2x-8>0.若綈p是綈q的必要不充分条件,求a的取值范围.20.(本小题满分14分)设命题甲:直线x=y与圆(x-a)2+y2=1有公共点,命题乙:函数f(x)=2-|x+1|-a的图象与x轴有交点,试判断命题甲与命题乙的条件关系,并说明理由.答案及解析1.【解析】∁U T={1,5,6},S∩(∁U T)={1,5}.【答案】 B2.【解析】“奇函数”的否定,是“不是奇函数”,因此否命题应为“若函数f(x)不是奇函数,则f(-x)不是奇函数”.【答案】 B3.【解析】a=(4,3),|a|=42+32=5;当|a|=5时,x=±4.【答案】 A4.【解析】对于②,l与m可相交、平行、异面,不正确,对于④,α与β可相交,不正确.【答案】 B5.【解析】∵直线y=x与单位圆x2+y2=1有两个交点,∴A∩B的元素有2个.【答案】 C6.【解析】由y=|cos2x-sin2x|=|cos 2x|,得M=[0,1];因为|x-1i|<2,所以|x+i|<2,即x2+1<2,所以-1<x<1,即N=(-1,1),∴M∩N=[0,1).【答案】 C7.【解析】|x|>1⇔x>1或x<-1,故x>1⇒|x|>1,但|x|>1D/⇒x>1(如x=-2),∴x>1是|x|>1的充分不必要条件.【答案】 A8.【解析】①的逆命题为:“若x,y互为倒数,则xy=1”是真命题;②的否命题为:“面积不相等的三角形不是全等三角形”是真命题;命题③是真命题,所以它的逆否命题也是真命题.命题④是假命题,所以它的逆否命题也是假命题.【答案】 D9.【解析】∵0<x<π2,∴0<sin x<1,由x·sin x<1知x sin2x<sin x<1,因此必要性成立.由x sin2x<1得x sin x<1sin x,而1sin x>1,因此充分性不成立.【答案】 B10.【解析】当a,b∈(0,+∞),且a+b=1时,1 a+1b=(a+b)(1a+1b)=2+ba+ab≥4≠3,∴p为假命题.对∀x∈R,x2-x+1=(x-12)2+34≥34≥0恒成立.∴命题q是真命题,∴綈p∧綈q是假命题.【答案】 B11.【解析】 ∵所给命题是特称命题,∴它的否定应为全称命题.【答案】 ∀x ∈R ,x ≠sin x12.【解析】 对于非零向量a ,b ,若a +b =0,则a =-b ,∴a ∥b .但a ∥b ,有a =λb (λ∈R),不一定有a +b =0,∴“a +b =0”是“a ∥b ”的充分不必要条件.【答案】 充分不必要13.【解析】 因为x ∉Q ,所以x ∈∁R Q ,∵Q ={x |-12≤x <72},∴∁R Q ={x |x <-12或x ≥72},则P -Q ={4}.【答案】 {4}14.【解析】 由4-x >0,知A =(-∞,4).又B ={x |x <a },且“x ∈A ”是“x ∈B ”的充分不必要条件.∴A B ,∴a >4.【答案】 (4,+∞)15.【解】 (1)綈p :存在一个正数,它的对数不是正数.真命题.(2)綈p :∃x ∈Z ,x 2的个位数字等于3,假命题.16.【解】 A ={y |y <a 或y >a 2+1},B ={y |2≤y ≤4}.(1)当A ∩B =∅时,⎩⎨⎧a 2+1≥4a ≤2, 所以a ≤-3或3≤a ≤2.(2)由x 2+1≥ax ,得x 2-ax +1≥0, 依题意知,Δ=a 2-4≤0,则-2≤a ≤2,即a 的最小值为-2.当a =-2时,A ={y |y <-2或y >5},所以∁R A ={y |-2≤y ≤5},故(∁R A )∩B ={y |2≤y ≤4}.17.【解】 (1)∵f (x )=2[1-cos(π2+2x )]-23cos 2x -1=2sin 2x -23cos 2x +1=4sin(2x -π3)+1.又∵π4≤x ≤π2,∴π6≤2x -π3≤2π3,即3≤4sin(2x -π3)+1≤5,∴f (x )max =5,f (x )min =3.(2)∵|f (x )-m |<2,∴m -2<f (x )<m +2.又∵p 是q 的充分条件,∴⎩⎨⎧ m -2<3m +2>5,解之得3<m <5. 因此实数m 的取值范围是(3,5).18.【解】 由题意知a ≠0,若命题p 正确,由于a 2x 2+ax -2=(ax +2)(ax -1)=0.∴x =1a 或x =-2a .若方程在[-1,1]上有解,满足-1≤1a ≤1或-1≤-2a ≤1,解之得a ≥1或a ≤-1.若q 正确,即只有一个实数x 满足x 2+2ax +2a ≤0.则有Δ=0,即a =0或2.若p 或q 是假命题.则p 和q 都是假命题,有⎩⎨⎧-1<a <1,a ≠0且a ≠2.所以a 的取值范围是(-1,0)∪(0,1).19.【解】 由x 2-4ax +3a 2<0,且a <0.得3a <x <a .∴记p :对应集合A ={x |3a <x <a ,a <0}.又记B ={x |x 2-x -6≤0或x 2+2x -8>0}={x |x <-4或x ≥-2}.∵綈p 是綈q 的必要不充分条件,∴q 是p 的必要不充分条件.因此A B .∴a ≤-4或3a ≥-2(a <0),解之得-23≤a <0或a ≤-4.20.【解】 命题甲:若直线x =y 与圆(x -a )2+y 2=1有公共点. 则|a -0|12+12≤1,-2≤a ≤ 2. 命题乙:函数f (x )=2-|x +1|-a 的图象与x 轴有交点,等价于a =2-|x +1|有解. ∵|x +1|≥0,-|x +1|≤0,∴0<2-|x +1|≤1,因此0<a ≤1.∴命题乙⇒命题甲,但命题甲D ⇒/命题乙.故命题乙是命题甲的充分不必要条件.。

集合与常用逻辑用语、一元二次函数、方程和不等式单元测试答

高一数学必修一第一、二章测试题一、单选题(每小题5分,共40分)1.若集合A ={x ∈N |x ≤ 2 020 },a =22 ,则下列结论正确的是( ) A .{a }⊆A B .a ⊆A C .{a }∈A D .a ∉A 分析选D.因为A ={x ∈N |x ≤ 2 020 },所以A 中元素全是整数,因为a =22 ,所以a ∉A .2.设全集为R ,集合A ={1,2,3},B ={x |y =x -2 },则A ∩(R B )=( ) A .{1,2} B .{1} C .{1,3} D .{1,2,3}分析选B.因为B ={x |x ≥2},所以R B ={x |x <2},且A ={1,2,3}, 所以A ∩(R B )={1}.3.已知集合A ={x |(x -1)(x +2)<0},集合B =⎩⎨⎧⎭⎬⎫x ⎪⎪x x -1>0 ,则A ∩B =( )A .{x |-2<x <0}B .{x |1<x <2}C .{x |0<x <1}D .R分析选A.因为集合A ={x |(x -1)(x +2)<0}={x |-2<x <1},集合B =⎩⎨⎧⎭⎬⎫x ⎪⎪⎪x x -1>0 ={x |x <0或x >1},所以A ∩B ={x |-2<x <0}. 4.设a =x 2+y 2-2x +2y +1,b =-4,则实数a ,b 的大小关系( ) A .a <b B .a >b C .a =b D .与x ,y 取值有关分析选B.a -b =x 2+y 2-2x +2y +5=(x -1)2+(y +1)2+3>0,所以a >b . 5.已知t >0,则函数y =2t 2-t +2t的最小值为( )A .-2B .12C .3D .2分析选C.因为t >0,则函数y =2t 2-t +2t =2t +2t-1≥22t ·2t-1=3,当且仅当t =1时取等号.所以函数y =2t 2-t +2t的最小值为3.6.若不等式kx 2-6kx +k +8≥0的解集为R ,则实数k 的取值范围是( ) A .0≤k ≤1B .0<k ≤1C .k <0或k >1D .k ≤0或k ≥1分析选A.由于不等式kx 2-6kx +k +8≥0的解集为R ,分以下两种情况讨论:①当k =0时,则有8≥0,合乎题意;②当k ≠0时,则有⎩⎪⎨⎪⎧k >0Δ=36k 2-4k (k +8)=32k (k -1)≤0 , 解得0<k ≤1.综上所述,0≤k ≤1.7.某单位计划今明两年购买某物品,现有甲、乙两种不同的购买方案,甲方案:每年购买的数量相等;乙方案:每年购买的金额相等.假设今明两年该物品的价格分别为p 1,p 2(p 1≠p 2),则这两种方案中平均价格比较低的是( ) A .甲B .乙C .甲、乙一样D .无法确定解:甲方案:每年购买的数量相等;乙方案:每年购买的金额相等. 设甲每年购买的数量x ;乙每年购买的金额y . 因为今明两年该物品的价格分别为p 1,p 2(p 1≠p 2), 则甲的平均价格甲==,①乙的平均价格乙==,②两式作商可得=>=1,故乙的平均价格比较低,故选:B .8.某公司从2018年起每人的年工资主要由三个项目组成并按下表规定实施:项目 计算方法基础工资 2018年1万元,以后每年逐增10%住房补贴 按工龄计算:400元×工龄 医疗费每年1 600元固定不变若该公司某职工在2020年将得到的住房补贴与医疗费之和超过基础工资的25%,到2020年底这位职工的工龄至少是( )A .2年B .3年C .4年D .5年分析选C.设这位职工工龄至少为x 年,则400x +1 600>10 000·(1+10%)2×25%, 即400x +1 600>3 025,即x >3.562 5,所以至少为4年.二、多选题(每小题5分,共20分,全部选对得5分,选对但不全的得2分,有选错的得0分) 9.下列命题中,正确的是( ) A .若a b >,则22ac bc > B .若a b >,则33a b >C .若0a b >>,0m >,则b m ba m a+>+ D .若15a -<<,23b <<,则43a b -<-<分析选BCD : 取0c,代入验证A,有00>,错误,故A 不正确;对于B :记()3f x x =,则()f x 为增函数,所以a b >时有()()f a f b >,故B 正确; 对于C :记()(0,0)b xf x a b x a x+=>>≥+,易证()f x 为增函数,所以0m >时有()()0f m f >,即b m ba m a+>+成立,故C 正确; 对于D :23,32b b <<∴-<-<-,又有15a -<<,利用同向不等式相加,有:43a b -<-<,故D正确.故选:BCD10.下列不等式不一定正确的是( ) A .|x +1x |≥2B .x 2+y 2xy ≥2C .x 2+y 22>xyD .|x +y |2≥|xy |分析选BCD.因为x 与1x 同号,所以⎪⎪⎪⎪⎪⎪x +1x =|x |+1|x | ≥2,A 正确; 当x ,y 异号时,B 不正确;当x =y 时,x 2+y 22=xy ,C 不正确;当x =1,y =-1时,D 不正确. 10.有以下说法,其中正确的为( )A .“x ,y 为无理数”是“xy 为无理数”的充分条件B .“若x ∈A ∩B ”则“x ∈A ”的否定是“若x ∈A ∩B ”则“x ∉∈A ”C .“x 2-2x -3=0”是“x =3”的必要条件D .“x >1”是“1x<1”的充分不必要条件分析选CD.对于A ,2 是无理数,但2 ×2 =2是有理数,故A 不正确;对于B ,“若x ∈A ∩B ”则“x ∈A ”是全称量词命题,它的否定是“∃x ∈A ∩B ”则“x ∉∈A ”,故B 不正确;对于C ,x =3⇒x 2-2x -3=0,反之不成立,因此“x 2-2x -3=0”是“x =3”的必要条件,故C 正确;对于D ,1x<1⇒x >1或x <0,因此“x >1”是“1x<1”的充分不必要条件,故D 正确.12.已知a ∈Z ,关于x 的一元二次不等式x 2-6x +a ≤0的解集中有且仅有3个整数,则a 的取值可以是( ) A .4 B .5 C .6 D .7分析选CD.设y =x 2-6x +a ,其图象为开口向上,对称轴为x =3的抛物线,如图所示.关于x 的一元二次不等式x2-6x +a ≤0的解集中有且仅有3个整数,a 需满足⎩⎪⎨⎪⎧22-6×2+a ≤012-6×1+a >0 ,解得5<a ≤8,又a ∈Z ,所以a 的取值是6,7,8. 三、填空题(每小题5分,共20分)13.命题∀x ∈R ,∃n ∈N ,2n>x 2的否定为________.分析存在量词命题的否定是全称量词命题,所以该命题的否定为 答案:∃x ∈R , ∀n ∈N ,2n≤x2 14.已知“命题p :(x -m )2>3(x -m )”是“命题q :x 2+3x -4<0”成立的必要不充分条件,则实数m 的取值范围为____________.分析:由(x -m )2>3(x -m ),得(x -m )(x -m -3)>0,解得x >m +3或x <m . 所以p :x >m +3或x <m .由x 2+3x -4<0,解得-4<x <1,即q :-4<x <1. 因为p 是q 成立的必要不充分条件,所以q ⇒p ,p ⇒q , 所以{x |-4<x <1}{x |x >m +3或x <m }.结合数轴可知m +3≤-4或m ≥1,解得m ≤-7或m ≥1.答案:m ≤-7或m ≥1 15.已知不等式axx -1<1的解集为{x |x <1或x >2},则a =______.分析由(1)101a x x -+<-,即[](1)1(1)0a x x -+-<,由不等式的解与方程的关系,(1)210a -⨯+=所以,a =1216.已知正实数a ,b 满足ab -b +1=0,则1a +4b 的最小值是________,此时b =________.分析由ab -b +1=0可得a =b -1b ,由a =b -1b>0,得b >1, 所以1a +4b =b b -1 +4b =1b -1 +4(b -1)+5,因为1b -1 +4(b -1)≥4,所以1a +4b ≥9,当且仅当a =13 ,b =32 时等号成立.答案:9 32四、解答题(共70分)17.(10分)设全集为R ,集合A ={x |x 2-2x -3>0},B ={x |a -1<x <2a +3}. (1)若a =-1,求(R A )∩B ;(2)在①A ∪B =A ,②A ∩B =B ,③(R A )∩B =∅,这三个条件中任选一个作为已知条件,求实数a 的取值范围.(注:如果选择多个条件分别解答,则按第一个解答计分)分析(1)全集为R ,集合A ={x|x 2-2x -3>0}={x|x <-1或x >3},所以R A ={x|-1≤x ≤3}; 又a =-1时,集合B ={x|a -1<x <2a +3}={x|-2<x <1},所以(R A)∩B ={x|-1≤x <1}.(2)选择①A ∪B =A 作为已知条件.(选择②,③的解法同①)因为A ∪B =A ,所以B ⊆A , 又由A ={x|x <-1或x >3}得当B =∅时a -1≥2a +3,解得a ≤-4;当B ≠∅时⎩⎪⎨⎪⎧a -1<2a +32a +3≤-1 或⎩⎪⎨⎪⎧a -1<2a +3a -1≥3 ,所以⎩⎪⎨⎪⎧a >-4a ≤-2 或⎩⎪⎨⎪⎧a >-4a ≥4,所以-4<a ≤-2或a ≥4.综上,可得a 的取值范围为a ≤-2或a ≥4. 18.(12分)解关于x 的不等式x 2-(3m +1)x +2m 2+2m <0.分析:x 2-(3m +1)x +2m 2+2m<0,即x 2-(3m +1)x +2m(m +1)=(x -2m)(x -m -1)<0, 令(x -2m)(x -m -1)=0,解得x =2m 或x =m +1, 当2m >m +1,即m >1时,解集为{x|m +1<x<2m}, 当2m <m +1,即m <1时,解集为{x|2m<x<m +1}, 当m =1时,解集为∅.综上所述,当m =1时,解集为∅;当m>1时,解集为{x|m +1<x<2m};当m<1时,解集为{x|2m<x<m +1}. 19.(12分)(1) 若x>3,求y =4x +2+13x -的最小值. (2)已知0,0a b >>,且1a b +=,4141M a b =++求M 的最大值.解(1)因为x>3,所以x -3>0.又因为y =4(x -3)+1x -3 +1414(3)14183x x ≥-⨯=- 当且仅当14(3)3x x -=-,即132x -=时,72x =等号成立,故y 的最小值是18. (2)2(4141)4()22(41)(41)4()2(41)(41)8()423M a b a b a b a b a b a b =+++=+++++≤++++++=++=,当4a+1=4b+1时取等号,此时a=b=12∴M 的最大值是3 20.(12分)已知命题p :“∃x ∈R ,x 2-2x +a =0”;命题q :“∀x ∈{x |1≤x ≤2},x 2+ax -8≤0” 若p,q 至少有一个为假命题,求实数a 的取值范围.分析命题p :“∃x ∈R ,x 2-2x +a =0”为假命题,可得方程x 2-2x +a =0无实数解,即有Δ=4-4a <0,解得a >1;命题q :“∀x ∈{x|1≤x ≤2},x 2+ax -8≤0”为真命题,可得⎩⎪⎨⎪⎧1+a -8≤04+2a -8≤0 ,解得a ≤2,命题q 为假a ≥2.综上可得,a 的取值范围是a >1. 21.(12分)()1已知x ,y 都是正数.求证:()()()2233338.x y x y x y x y +++≥()2已知a ,b ,c 为正数,且满足1a b c ++=.证明:164149a b c++≥.21.(1)证明:由基本不等式可知()()()(()(22332x y x yxy xy +++≥⋅⋅()23388xy xy x y =⋅=,(当且仅当x y =时取得等号). (2)∵1a b c ++=,∴()16411641a b c a b c a b c ⎛⎫++=++++ ⎪⎝⎭16416421b a c a c b a b a c b c ⎛⎫⎛⎫⎛⎫=++++++ ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭21≥+21168449=+++= 当且仅当47a =,27b =,17c =时,上式等号成立. 22.(12分)第一机床厂投资A 生产线500万元,每万元可创造利润1.5万元.该厂通过引进先进技术,在A 生产线的投资减少了x (x >0)万元,且每万元创造的利润变为原来的(1+0.005x )倍.现将在A 生产线少投资的x 万元全部投入B 生产线,且每万元创造的利润为1.5(a -0.013x )万元,其中a >0. (1)若技术改进后A 生产线的利润不低于原来A 生产线的利润,求x 的取值范围; (2)若B 生产线的利润始终不高于技术改进后A 生产线的利润,求a 的最大值. 分析(1)由题意得1.5(1+0.005x)(500-x)≥1.5×500,整理得x 2-300x ≤0, 解得0≤x ≤300,又x >0,故0<x ≤300.(2)由题意知,B 生产线的利润为 1.5(a -0.013x)x 万元,技术改进后,A 生产线的利润为 1.5(1+0.005x)(500-x)万元,则1.5(a -0.013x)x ≤1.5(1+0.005x)(500-x)恒成立,又x >0, 所以a ≤x 125 +500x +1.5恒成立.又x 125 +500x +1.5≥2x 125·500x+1.5=5.5, 当且仅当x 125 =500x ,即x =250时,等号成立,又a>0,所以0<a ≤5.5,所以a 的最大值为5.5.。

新教材2023年高考数学总复习考案3阶段测试一集合常用逻辑不等式及函数的概念与性质课件

11.给出下列结论,其中正确的结论是( BC )

A.函数 y=12-x2+1的最大值为12 B.若定义在R上的奇函数f(x)在(-∞,0)内有100个零点,则函数 f(x)有201个零点 C.在同一平面直角坐标系中,函数y=2x与y=log2x的图象关于直线 y=x对称 D.已知函数y=loga(2-ax)(a>0且a≠1)在(0,1)上是减函数,则实 数a的取值范围是(1,2)

二、多选题(本题共4个小题,每个小题5分,共20分.在每个小题给 出的四个选项中有多项是正确的,全部选对得5分,部分选对得2分,错 选得0分)

9.(2022·湖北华中师大一附中检测)给出以下说法,其中正确的是

( ACD ) A.“x>1”是“x>2”的必要不充分条件 B.“a>b”是“a2>b2”的充分不必要条件 C.命题“存在n∈N*,n2<2n”的否定为假命题 D.满足命题“∃x∈[0,1],x+a≤0”是假命题的a的取值范围为

[解析] 对 A,y=12-x2+1=2x2-1,故当 x=0 时,x2-1 取得最小值 -1,y=12-x2+1=2x2-1 取得最小值12,故 A 错误;对 B,若定义在 R 上的 奇函数 f(x)在(-∞,0)内有 100 个零点,则函数 f(x)在(0,+∞)内有 100 个零点,又 f(0)=0,故 f(x)有 201 个零点,故 B 正确;对 C,因为函数 y =2x 与 y=log2x 互为反函数,故图象关于直线 y=x 对称,故 C 正确;对 D,函数 y=loga(2-ax)(a>0 且 a≠1)在(0,1)上是减函数,则因为 y=2 -ax 为减函数,故 a>1.又由定义域,y=2-ax 在(0,1)上恒为正,故 2 -a≥0,解得 a≤2,故数 a 的取值范围是(1,2],故 D 错误.故选 BC.

逻辑关系测试题

逻辑关系测试题姓名班级一、填空题1、有一种物质,它的导电性介于导体和绝缘体之间,这就是。

2、基本的逻辑关系是、和。

3、逻辑是指。

4、数学集合当中的交集相当于逻辑关系当中的、并集相当于、补集相当于。

5、我们通常的正逻辑是用代表高、有,用代表低、无。

6、有0则0,全1则1是逻辑关系的规律,反之又是逻辑关系的规律。

7、同或关系的规律是。

8、异或关系的规律是。

9、请写出Y=A+B的真值表10、A⊕1= 。

二、选择题1、计算机能够识别并处理的数是()数。

A 八进制B二进制C十进制D十六进制2、二进制的基数是()。

A、0和1B、0-9C、0-7D、0-F3、同样大小的二进制数和十进制数,二进制的位数比十进制的位数。

()A、多B、少C、一样多D不知道4、一般用()位二进制表示一位八进制。

A、4B、3C、2D、15、在二进制数当中我们只需要判定()上是否为1则可以判定这个数是否为奇数。

A最高位 B百位 C个位 D十位6、条条道路通罗马是基本逻辑关系中()逻辑的表述。

A、与B、或C、非D、与非7、多个条件同时成立则命题成立缺一不可说的是()逻辑关系。

A、与B、或C、非D、与非8、当逻辑函数有n个变量时,共有()个变量取值组合。

A. nB. 2nC. n2D. 2n9.在何种输入情况下,“与非”运算的结果是逻辑0。

A.全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是110、在何种输入情况下,“或非”运算的结果是逻辑0。

A.全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为1三、判断题(正确打√,错误的打×)1.逻辑变量的取值,1比0大。

()2.异或函数与同或函数在逻辑上互为反函数。

()3、密码与账号的关系是逻辑的或关系。

()4、逻辑的变量只有两种0和1。

()5、若要表示3位十进制数代表的所有数值,则至少需用12位二进制数。

()6基数和各位数的权是进位计数制中表示数值的两个基本要素。

集合与常用逻辑用语测试题-+答案

一、选择题:本大题共10小题,每题5分,共50分,在每题给出的四个选项中,只有一项是符合题目要求的。

1.已知全集U 和集合A ,B 如下图,则(∁U A )∩B ( )A .{5,6}B .{3,5,6}C .{3}D .{0,4,5,6,7,8} 解析:选A.由题意知:A ={1,2,3},B ={3,5,6},∁U A ={0,4,7,8,5,6},∴(∁U A )∩B ={5,6},故选A.2.设集合A ={(x ,y )|x 24+y 216=1},B ={(x ,y )|y =3x },则A ∩B 的子集的个数是( )A .4B .3C .2D .1解析:A 中的元素是椭圆x 24+y 216=1上的点,集合B 中的元素是函数y =3x 的图象上的点.由数形结合,可知A ∩B 中有2个元素,因此A ∩B 的子集的个数为4.3.已知M ={x |x -a =0},N ={x |ax -1=0},假设M ∩N =N ,则实数a 的值为( )A .1B .-1C .1或-1D .0或1或-1 解析:M ∩N =N 得N ⊆M .当a =0时,N =∅,满足N ⊆M ;当a ≠0时,M ={a },N ={1a },由N ⊆M 得1a=a ,解得a =±1,故选D. 4.设集合A ={x ||x -a |<1,x ∈R },B ={x |1<x <5,x ∈R }.假设A ∩B =∅,则实数a 的取值范围是( )A .{a |0≤a ≤6}B .{a |a ≤2,或a ≥4}C .{a |a ≤0,或a ≥6}D .{a |2≤a ≤4} 解析: A 得:-1<x -a <1,即a -1<x <a +1,显然集合A ≠∅,假设A ∩B =∅,由图可知a +1≤1或a -1≥5,故a ≤0或a ≥65.定义集合运算:A ⊙B ={z |z =xy (x +y ),x ∈A ,y ∈B },设集合A ={0,1},B ={2,3},则集合A ⊙B 的所有元素之和为( )A .0B .6C .12D .18解析:x =0时,z =0;当x =1,y =2时,z =6;当x =1,y =3时,z =12. 故集合A ⊙B 中的元素有如下3个:0,6,12. 所有元素之和为18.6.以下命题中为真命题的是( )A .命题“假设x >y ,则x >|y |”的逆命题B .命题“假设x >1,则x 2>1”的否命题C .命题“假设x =1,则x 2+x -2=0”的否命题D .命题“假设x 2>0,则x >1”的逆否命题解析:“假设x >y ,则x >|y |”的逆命题是“假设x >|y |,则x >y ”,无论y 是正数、负数、0都成立,所以选A.7.设全集U={x∈N*|x≤a},集合P={1,2,3},Q={4,5,6},则“a∈[6,7)”是“∁U P=Q”的()A.充分不必要条件B.必要不充分条件C.充要条件D.既不充分也不必要条件解析:a∈[6,7),则U={1,2,3,4,5,6},则∁U P=Q;假设∁U P=Q,则U={1,2,3,4,5,6},结合数轴可得6≤a<7,故选C8.以下命题中,真命题是()A.∃m∈R,使函数f(x)=x2+mx(x∈R)是偶函数B.∃m∈R,使函数f(x)=x2+mx(x∈R)是奇函数C.∀m∈R,函数f(x)=x2+mx(x∈R)都是偶函数D.∀m∈R,函数f(x)=x2+mx(x∈R)都是奇函数解析:选A.对于选项A,∃m∈R,即当m=0时,f(x)=x2+mx=x2是偶函数.故A正确.9.已知命题p:∀x∈R,x>sin x,则p的否认形式为()A.∃x0∈R,x0<sin x0B.∀x∈R,x≤sin xC.∃x0∈R,x0≤sin x0D.∀x∈R,x<sin x解析:“∀”与“∃”相对,则¬p:∃x0∈R,x0≤sin x0,故选C.10.命题p:x=π是函数y=sin x图象的一条对称轴;q:2π是y=sin x的最小正周期,以下复合命题:①p∨q;②p∧q;③¬p;④¬q,其中真命题有()A.0个B.1个C.2个D.3个解析:p是假命题,命题q是真命题,所以p∧q为假命题,p∨q为真命题,¬p是真命题,¬q是假命题,因此①②③④中只有①③为真,故选C.11.设U={0,1,2,3},A={x∈U|x2+mx=0},假设∁U A={1,2},则实数m=________.解析:∵∁U A={1,2},∴A={0,3},∴0,3是方程x2+mx=0的两根,∴m=-3.答案:-312.设全集I={2,3,a2+2a-3},A={2,|a+1|},∁I A={5},M={x|x=log2|a|},则集合M 的所有子集是________.解析:∵A∪(∁I A)=I,∴{2,3,a2+2a-3}={2,5,|a+1|},∴|a+1|=3,且a2+2a-3=5,解得a=-4或a=2.∴M={log22,log2|-4|}={1,2}.答案:∅、{1}、{2}、{1,2}13.设U ={0,1,2,3},A ={x ∈U |x 2+mx =0},假设∁U A ={1,2},则实数m =________.解析:∵∁U A ={1,2},∴A ={0,3}, ∴0,3是方程x 2+mx =0的两根,∴m =-3. 答案:-314.已知集合A ={x |a -3<x <a +3},B ={x |x <-1或x >2},假设A ∪B =R ,则a 的取值范围为________.解析:由a -3<-1且a +3>2,解得-1<a . 答案:(-1,2)15.已知p :x ≤1,条件q :1x<1,则p 是¬q 成立的________条件.解析:¬q :0≤x ≤1. 答案:必要不充分16.假设命题“ax 2-2ax -3>0不成立”是真命题,则实数a 的取值范围是________.解析:ax 2-2ax -3≤0恒成立,当a =0时,-3≤0成立;当a ≠0时,得⎩⎪⎨⎪⎧a <0Δ=4a 2+12a ≤0,解得-3≤a <0,故-3≤a ≤0. 答案:[-3,0]17.给定以下几个命题:①“x =π6”是“sin x =12”的充分不必要条件;②假设“p ∨q ”为真,则“p ∧q ”为真; ③等底等高的三角形是全等三角形的逆命题.其中为真命题的是________.(填上所有正确命题的序号)解析:①中,假设x =π6,则sin x =12,但sin x =12时,x =π6+2k π或5π6+2k π(k ∈Z ).故“x =π6”是“sin x =12”的充分不必要条件,故①为真命题;②中,令p 为假命题,q 为真命题, 有“p ∨q ”为真命题, 而“p ∧q ”为假命题, 故②为假命题; ③为真命题.答案:①③三、解答题:本大题共5小题,共618.设全集U =R ,A ={x |2x -10≥0},B ={x |x 2-5x ≤0,且x ≠5}.求(1)∁U (A ∪B ); (2)(∁U A )∩(∁U B ).解:A ={x |x ≥5},B ={x |0≤x <5}.(1)A ∪B ={x |x ≥0},于是∁U (A ∪B )={x |x <0}.(2)∁U A ={x |x <5},∁U B ={x |x <0或x ≥5},于是(∁U A )∩(∁U B )={x |x <0}.19.已知集合A ={x |x 2-2x -3≤0,x ∈R },B ={x |x 2-2mx +m 2-4≤0,x ∈R }.(1)假设A ∩B =[1,3],求实数m 的值; (2)假设A ⊆∁R B ,求实数m 的取值范围.解:A ={x |-1≤x ≤3}, B ={x |m -2≤x ≤m +2}. (1)∵A ∩B =[1,3],∴⎩⎪⎨⎪⎧m -2=1m +2≥3,得m =3. (2)∁R B ={x |x <m -2或x >m +2}. ∵A ⊆∁R B ,∴m -2>3或m +2<-1.∴m >5或m <-3.20.已知集合A ={x |x 2-2x -3≤0,x ∈R },B ={x |x 2-2mx +m 2-4≤0,x ∈R }.(1)假设A ∩B =[1,3],求实数m 的值; (2)假设A ⊆∁R B ,求实数m 的取值范围.解:A ={x |-1≤x ≤3},B ={x |m -2≤x ≤m +2}. (1)∵A ∩B =[1,3],∴⎩⎪⎨⎪⎧m -2=1m +2≥3,得m =3. (2)∁R B ={x |x <m -2或x >m +2}. ∵A ⊆∁R B ,∴m -2>3或m +2<-1. ∴m >5或m <-3.21.已知集合A =⎩⎨⎧⎭⎬⎫y |y =x 2-32x +1,x ∈⎣⎡⎦⎤34,2,B ={x |x +m 2≥1}.命题p :x ∈A ,命题q :x ∈B ,并且命题p 是命题q 的充分条件,求实数m 的取值范围.解:化简集合A ,由y =x 2-32x +1,配方,得y =⎝⎛⎭⎫x -342+716. ∵x ∈⎣⎡⎦⎤34,2,∴y min =716,y max =2.∴y ∈⎣⎡⎦⎤716,2. ∴A =⎩⎨⎧⎭⎬⎫y |716≤y ≤2.化简集合B ,由x +m 2≥1, 得x ≥1-m 2,B ={x |x ≥1-m 2}.∵命题p 是命题q 的充分条件, ∴A ⊆B .∴1-m 2≤716,解得m ≥34,或m ≤-34.∴实数m 的取值范围是⎝⎛⎦⎤-∞,-34∪⎣⎡⎭⎫34,+∞. 22.已知a >0,设命题p :函数y =a x在R 上单调递减,q :设函数y =⎩⎪⎨⎪⎧2x -2a (x ≥2a )2a (x <2a ),函数y >1恒成立,假设p ∧q 为假,p ∨q 为真,求a 的取值范围.解:假设p 是真命题,则0<a <1, 假设q 是真命题,则函数y >1恒成立,即函数y 的最小值大于1,而函数y 的最小值大于1,最小值为2a ,只需2a >1,∴a >12,∴q 为真命题时,a >12.又∵p ∨q 为真,p ∧q 为假, ∴p 与q 一真一假,假设p 真q 假,则0<a ≤12;假设p 假q 真,则a ≥1, 故a 的取值范围为0<a ≤12或a ≥1。

时序逻辑电路习题

触发器一、单项选择题:(1)对于D触发器,欲使Q n+1=Q n,应使输入D=。

A、0B、1C、QD、(2)对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输入T=。

A、0B、1C、Q(4)请选择正确的RS触发器特性方程式。

A、B、C、 (约束条件为)D、(5)请选择正确的T触发器特性方程式。

A、B、C、D、(6)试写出图所示各触发器输出的次态函数(Q)。

n+1A、B、C、D、(7)下列触发器中没有约束条件的是。

A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器二、多项选择题:(1)描述触发器的逻辑功能的方法有。

A、状态转换真值表B、特性方程C、状态转换图D、状态转换卡诺图(2)欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A、J=K=0B、J=Q,K=C、J=,K=QD、J=Q,K=0(3)欲使JK触发器按Q n+1=0工作,可使JK触发器的输入端。

A、J=K=1B、J=0,K=0C、J=1,K=0D、J=0,K=1(4)欲使JK触发器按Q n+1=1工作,可使JK触发器的输入端。

A、J=K=1B、J=1,K=0C、J=K=0D、J=0,K=1三、判断题:(1)D触发器的特性方程为Q n+1=D,与Q无关,所以它没有记忆功能。

()n(2)同步触发器存在空翻现象,而边沿触发器和主从触发器克服了空翻。

()(3)主从JK触发器、边沿JK触发器和同步JK触发器的逻辑功能完全相同。

()(8)同步RS触发器在时钟CP=0时,触发器的状态不改变( )。

(9)D触发器的特性方程为Q n+1=D,与Q n无关,所以它没有记忆功能( )。

(10)对于边沿JK触发器,在CP为高电平期间,当J=K=1时,状态会翻转一次( )。

四、填空题:(1)触发器有()个稳态,存储8位二进制信息要()个触发器。

(2)在一个CP脉冲作用下,引起触发器两次或多次翻转的现象称为触发器的(),触发方式为()式或()式的触发器不会出现这种现象。

《数字逻辑》总复习测试题参考答案

目录

• 测试题答案概述 • 选择题答案解析 • 填空题答案解析 • 简答题答案解析 • 计算题答案解析

01

测试题答案概述

测试题答案的解析

测试题1答案解析

这道题考查了基本逻辑门的功能和特点,通 过分析题目中的逻辑表达式,可以确定使用

的逻辑门类型和输入输出关系。

测试题2答案解析

解析:此题考查了触发器的功能,C选项代表了边沿触发器的特性,即在时钟信号的上升沿或下降沿时,触发器 会进行状态更新。

03

填空题答案解析填空题一答案及解析来自答案1010解析

根据二进制数的定义,二进制数由0和1组成,逢2进1。因此,将十进制数10转换为二进制数得到1010。

填空题二答案及解析

答案:8

测试题答案的注意事项

注意单位的统一

在解题过程中,需要注意单位的一致性,避免出现单位混淆或单位 错误的情况。

考虑边界条件

在分析逻辑电路或可编程逻辑器件的应用时,需要考虑各种边界条 件和极端情况,以确保电路的可靠性和稳定性。

重视细节

在解题过程中,需要注意细节问题,如符号的规范使用、电路连接方 式的正确性等,这些细节问题可能会影响最终结果的正确性。

05

计算题答案解析

计算题一答案及解析

答案

11010010

解析

根据二进制加法规则,1010+101=1101,然后后缀一个 0,得到11010010。

计算题二答案及解析

答案:3

解析:根据逻辑或运算规则,当两个输入信 号中至少有一个为高电平时,输出信号为高 电平。因此,A、B、C中至少有一个为高电

02

选择题答案解析

选择题一答案及解析

第2-6-7章 测试题(附答案)

第2-6-7章测试题一.单选题1.下面的选项不是关系数据库基本特征的是(A )。

A. 不同的列应有不同的数据类型B. 不同的列应有不同的列名C. 与行的次序无关D. 与列的次序无关2.一个关系只有一个(D )。

A. 候选码B. 外码C. 超码D. 主码3.关系模型中,一个码是(C )。

A. 可以由多个任意属性组成B. 至多由一个属性组成C. 由一个或多个属性组成,其值能够惟一标识关系中一个元组D. 以上都不是4.现有如下关系:患者(患者编号,患者姓名,性别,出生日期,所在单位)医疗(患者编号,医生编号,医生姓名,诊断日期,诊断结果)其中,医疗关系中的外码是(A )。

A.患者编号B.患者姓名C.患者编号和患者姓名D.医生编号和患者编号5.关系代数运算是以(C )为基础的运算。

A.关系运算B.谓词演算C.集合运算D.代数运算6.关系数据库管理系统应能实现的专门关系运算包括(B )。

A.排序、索引、统计B.选择、投影、连接C.关联、更新、排序D.显示、打印、制表7.五种基本关系代数运算是(A )。

A. ∪-×σπB. ∪-σπC. ∪∩×σπD. ∪∩σπ8.规范化理论是关系数据库进行逻辑设计的理论依据,根据这个理论,关系数据库中的关系必须满足:每一个属性都是(B )。

A.长度不变的B.不可分解的C.互相关联的D.互不相关的9.已知关系模式R(A,B,C,D,E)及其上的函数依赖集合F={A→D,B→C ,E→A },该关系模式的候选码是(B )。

A.ABB.BEC.CDD.DE10.关系模式中,满足2NF的模式(B )。

A.可能是1NFB.必定是1NFC.必定是3NFD.必定是BCNF11.消除了部分函数依赖的1NF的关系模式,必定是(B )。

A.1NFB.2NFC.3NFD.BCNF12.关系模式的候选码可以有1个或多个,而主码有(C )。

A.多个B.0个C.1个D.1个或多个13.候选码的属性可以有(D )。

广工数字逻辑复习题

一、选择题(每小题2分,共20分)1. 八进制(273)8中,它的第三位数2 的位权为___B___。

A .(128)10B .(64)10C .(256)10D .(8)102. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。

A .AB F = B .C AB F +=C .C A AB F +=D .C B AB F +=3. 数字系统中,采用____C____可以将减法运算转化为加法运算。

A . 原码B .ASCII 码C . 补码D . BCD 码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A .与关系B . 异或关系C .同或关系D .无法判断 5. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误6. 与逻辑函数D C B A F +++= 功能相等的表达式为___C_____。

A . D CB A F +++=B .D C B A F +++=C .D C B A F = D .D C B A F ++=7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。

CB A F& ∇ EN ABFCB A& ∇ EN8. 如图所示电路,若输入CP 脉冲的频率为100KHZ ,则输出Q 的频率为_____D_____。

A . 500KHzB .200KHzC . 100KHzD .50KHz9.下列器件中,属于时序部件的是_____A_____。

A . 计数器B . 译码器C . 加法器D .多路选择器10.下图是共阴极七段LED 数码管显示译码器框图,若要显示字符“5”,则译码器输出a ~g 应为____C______。

A . 0100100B .1100011C . 1011011D .001101111.TTL 电路的电源是__5__V ,高电平1对应的电压范围是__2.4-5____V 。

数字电路测试题

5、是 8421BCD 码的是( A、1010 ( B、0101 ) 。 A、5 B、6 C、8 C、1100

6 、欲对全班 43 个学生以二进制代码编码表示,最少需要二进制码的位数是 D、43 ) 。 B、F(A,B,C)=∑m(1,5,6,7) D、F(A,B,C)=∑m(3,4,6,7)

7、逻辑函数 F(A,B,C) = AB+B C+ AC 的最小项标准式为( A、F(A,B,C)=∑m(0,2,4) C、F(A,B,C)=∑m (0,2,3,4)

1.一个 4 选 1 的数据选择器,应具有_____个地址输入端______个数据输入端。 2.组合电路由________________构成,它的输出只取决于 _________________而 与原状态无关。 3.一个十六选一的数据选择器,其地址(选择控制)输入端有( A、1 B、2 C、4 D、16 ) 位。 )个。

5

8. 5. 10 位双积分型 ADC,设时钟周期为 5¦ S, 则完成一次转换的时间最长需要( ¦ S A.50 B.5120 C.60 D.10240

)

综合应用题 分析下图所示的电路,其中,74161 为 4 位二进制加法计数器,计数器的初 态为 Q3Q2Q1Q0 =1111。74161 功能表如下表所示,数据选择器的逻辑表达式 为: Y [ D0 ( A1 A0 ) D1 ( A1 A0 ) D2 ( A1 A0 ) D3 ( A1 A0 )]S 要求: (1)画出计数器的状态转换表或状态转换图; (2)列出在 CP 作用下输出 Z 的状态转换表; 74161 的功能表

3.试说明单稳态触发器的工作特点和主要用途。 4. 试用图 555 定时器为核心元件构成一个鉴幅器,实现图 3.1 所示的功能。已 知电源电压为 7V,画出电路的接线图,并标明有关的参数,视需要可添加其它 元器件。

五年高职专转本数电之第一章《数字逻辑电路》测试题

第一章《数字逻辑电路》测试题一.选择题1.下列一组数中,哪一组是等值的?()①(A7)16②(10100110)2③(166)10A.①和③B.②和①C.②和③D.都不对2.下面那些数与八进制数(47.3)8等值?()A.(100111.011)2B.(27.6)16C.(27.3)16 D.(100111.11)23.在何种输入情况下,“或非”运算的结果是逻辑0?()A.全部输入是0B.全部输入是1C.任一输入为0,其他输入为1D.任一输入为14.在()输入情况下,“与非”运算的结果是逻辑0。

A.全部输入是0B.任一输入是0C.仅一输入是0D.全部输入是5.三极管工作在开关状态下,其“关态”和“开态”分别指工作在下列哪种状态?()A.饱和状态和截止状态B.截止状态和放大状态C.放大状态和饱和状态D.截止状态和饱和状态6.一位十六进制数可以用多少位二进制数来表示?()A.1B.2C.4D.167.以下表达式中符合逻辑运算法则的是()A.C·C=C2B.1+1=10C.0<1D.A+1=18.十进制数65用8421BCD码表示,可以写成()A.65 B.[1000001]BCD C.[01100101]BCD D.[1000001]29.与十进制数(53.5)10等值的数或代码为()()()()A.(01010011.0101)8421BCDB.(35.8)16C.(110101.1)2D.(65.4)810.和二进制数(1100110111.001)B等值的十六进制数是()A.(337.2)H B.(637.1)H C.(1467.1)H D.(C37.4)H11.逻辑符号如题2图所示,当输入A ""0,输入B为方波时,则输出F应为()。

A.“1”B.“0”C.方波D.三角波12.在一个8位的存储单元中,能够存储的最大无符号整数是()()()()A.(256)10B.(127)10C.(FF)16D.(255)1013.在何种输入情况下,“与非”运算的结果是逻辑0?()A.全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是114.已知A=(10.44)10(下标表示进制),下列结果正确的是()A .A=(1010.1)2B .A=(0A.8)16C .A=(12.4)8D .A=(20.21)515.8421BCD 码01100010表示十进制数为( )A .15B .98C .62D .4216.表示十进制数10个数码,需要二进制数码的位数是( )A .2位B .4位C .3位D .10位17.表示任意两位无符号十进制数需要( )二进制数。

逻辑测试题目及答案

逻辑测试题目及答案以下是一些逻辑测试题目及其答案,希望能够帮助你提高逻辑思维能力。

题目一:如果A是B的兄弟,B是C的哥哥,那么A和C的关系是?答案一:A是B的兄弟,意味着A和B是同父或者同母的子女。

B是C的哥哥,则意味着B比C年长。

根据这些信息可以判断,A和C的关系是A是C的哥哥。

题目二:某商店推出了一种买一送一的促销活动,买三件商品只需支付总价的75%。

那么如果一件商品的价格是100元,买三件需要支付多少钱?答案二:根据题意,买三件商品只需支付总价的75%。

一件商品的价格是100元,所以三件商品的总价是300元。

然后,将总价的75%计算出来,得到300 * 0.75 = 225元。

购买三件商品需要支付225元。

题目三:有五个人排队参加比赛,他们分别是A、B、C、D、E。

其中D排在A的后面,A排在B的后面,B排在C的后面,C排在E的后面。

请问,谁在队列的最前面?答案三:根据题意,D排在A的后面,A排在B的后面,B排在C的后面,C排在E的后面。

根据这些顺序可以得出,排在队列最前面的人是D。

题目四:如果所有的大象都有长鼻子,那么下面的说法哪个是正确的?A. 所有有长鼻子的都是大象。

B. 所有大象都有长鼻子。

C. 有长鼻子的就是大象。

D. 没有长鼻子的不是大象。

答案四:根据题意,所有的大象都有长鼻子,可以得出结论:所有大象都有长鼻子。

因此,选项B“所有大象都有长鼻子”是正确的。

题目五:如果"ABC"代表"XYZ","DEF"代表"UVW",那么"JKL"代表什么?答案五:根据题意,"ABC"代表"XYZ",可以得出对应关系:A对应X,B 对应Y,C对应Z。

同理,"DEF"代表"UVW",对应关系是D对应U,E对应V,F对应W。

项目七:组合逻辑门电路的安装与测试

组合逻辑门电路的安装与测试一、填空题1.按输出代码种类的不同,可将编码器分为____________和____________两种。

2.组合逻辑门电路不具有___________功能,它的输出直接由电路的___________所决定,与输入信号作用前的____________无关。

3.2位二进制编码器有____________个输人端,有___________个输出端。

4. n个输入端的二进制译码器,共有_____________个输人端,对于每一組输人代码,有____________个输出端输出有效电平。

5.常用的组合逻料门电路有____________、____________、___________和___________。

6.经常要把输人的各种信号(如十进制数、文字.符号等)转换成若干位二进制码,这种转换过程称为____________,能够完成____________功能的组合逻辑电路称为编码器。

7.组合逻辑门电路的一般分析方法和步骤为: (1)由逻辑电路图写出___________;(2)___________;(3)列出____________,然后分析____________。

8.译码是____________的逆过程,其功能是把某种二进制代码“翻译”成____________。

9.组合逻辑门电路的设计方法和步骤为: ( 1 )根据实际问题的逻辑功能,列出_______________________;(2)写出______________________;(3)化简逻辑表达式,然后根据表达式______________________。

二、选择题1.脉冲信号是( )的信号。

A.随时间连续变化B.作用时间极短、间断C.正弦被D.非正弦波2.逻辑函数ABC +C+1=( )。

A.1B. cC. ABCD. C+13.逻辑函数B+AB=( )。

A.A+BB.A c.A D. B4.组合逻辑门电路的特点是( )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

综合测试题七

一、填空题

1.在数字电路中,逻辑变量的值只有个。

2.在逻辑函数的化简中,合并最小项的个数必须是个。

3.化简逻辑函数的方法,常用的有和。

4.逻辑函数A、B的同或表达式为A⊙B= 。

5.TTL三态门的输出有三种状态:高电平、低电平和状态。

6.4线—10线译码器又叫做进制译码器,它有个输入端和个输出端, 个不用的状态。

7.组合逻辑电路的输出仅取决于该电路当前的输入信号,与电路原来的状态。

8.T触发器的特性方程Q n+1= 。

9.组成计数器的各个触发器的状态,能在时钟信号到达时同时翻转,它属于计数器。

10.四位双向移位寄存器74LS194A的功能表如表所示。

由功能表可知,要实现保持功能,应使,当R D=1;S1=1,S0=0时,电路实现功能。

74LS194A的功能表

S1

工作状态

S0

11.若要构成七进制计数器,最少用个触发器,它有个无效状态。

12.根据触发器结构的不同,边沿型触发器状态的变化发生在CP 时,其它时刻触发器保持原态不变。

13.用中规模集成计数器构成任意进制计数器的方法通常有三种,它们是级连法,和。

14.由555定时器构成的单稳态触发器,若已知电阻R=500KΩ,电容C=10μF,则该单稳态触发器的脉冲宽度tw≈。

15.在555定时器组成的施密特触发器、单稳态触发器和多谐振荡器三种电路中,电路能自动产生脉冲信号,其脉冲周期T≈。

16.随机存储器RAM的电路结构主要由、和三部分组成。

二、选择题:请将正确答案的序号填在横线上。

1.下列一组数中,是等值的。

①(A7)16②(10100110)2③(166)10

A.①和③ B. ②和① C. ②和③

2.在逻辑函数中的卡诺图化简中,若被合并的最小项数越多(画的圈越大),则说明化简后。

A.乘积项个数越少 B. 实现该功能的门电路少

C.该乘积项含因子少

3.在逻辑函数的卡诺图化简中,合并相邻项(画圈)的方法必须画成形状。

A.三角形 B. 矩形 C. 任意

4.的最小项之和的形式是。

A.

B.

C.

5. 在下列各种电路中,属于组合电路的有。

A.编码器 B. 触发器 C. 寄存器

6.74LS138是3线-8线译码器,译码输出为低电平有效,若输入A2A1A0=100时,输出

=。

A.00010000, B. 11101111 C. 11110111

7.8线—3线优先编码器74LS148的优先权顺序是I7,I6,……I1,I0,输

出Y

Y1 Y0,输入低电平有效,输出为三位二进制反码输出。

当I7I6,……

2

I1I0为11100111时,输出Y

Y1 Y0为。

2

A.011 B.100 C. 110

8.在以下各种电路中,属于时序电路的有。

A.反相器 B. 编码器

C. 寄存器

D.数据选择器

9.RS触发器当R=S=0时,Q n+1= 。

A.0 B.1 C.Q n D. Q

10.施密特触发器常用于对脉冲波形的。

A.延时和定时 B. 计数与寄存C.整形与变换

三、逻辑函数化简与变换:

1.证明等式:

2.将下列逻辑函数化简成最简与或表达式

四.试写出图 4.1电路输出z的逻辑函数式。

4选1数据选择器74LS153的功能表达式见式 4.1。

(式4.1)

图4.1

五.3线-8线译码器74LS138逻辑功能表达式为,,……,

,,正常工作时,S1 =1, S

=S3=0。

试写出Z1和Z2

2

逻辑函数式。

(图5.1)

图5.1

六.触发器练习题:见数字电子技术基础主教材P202例4.2.6。

七.触发器练习题:见数字电子技术基础主教材P219习题4.12

八.画出图8.1(a)、(b)的状态转换图,分别说明它们是几进制计数器。

74LS161功能表见数字电子技术基础主教材P245表5.3.4。

(a) (b) 图8.1

九.试用四2输入与非门74LS00实现Y=AB+CD功能。

画出实验连线图,74LS00外部引线排列见图9.1所示。

图9.1。