EDA技术与Verilog设计典型FPGACPLD的结构与配置

EDA技术简介

实体说明

图5-3 mux21a实体 实体

ARCHITECTURE one OF mux21a IS BEGIN y <= a WHEN s = '0' ELSE b ; END ARCHITECTURE one ;

EDA技术 EDA技术

2、主流器件 、

◆ FPGA 现场可编程门阵列) (Field Programmable Gate Array现场可编程门阵列) 现场可编程门阵列 ◆ CPLD 复杂可编程逻辑器件) (Complex Programmable Logic Device复杂可编程逻辑器件) 复杂可编程逻辑器件

功能仿真

逻辑综合器

FPGA/CPLD

适配

结构综合器

时序与功能 门级仿真

1、功能仿真 、 2、时序仿真 、

FPGA/CPLD 编程下载

EDA技术 EDA技术

二、 FPGA最小系统 最小系统

EDA技术 EDA技术 1、EP1K100B+ 零售价:450元(含EPC2芯片 零售价: 元 芯片) 、 芯片

EDA技术 EDA技术

技术? 一、EDA技术? 技术

EDA( Automation电子设计自动化 电子设计自动化) ● EDA(Electronic Design Automation电子设计自动化) 是指利用计算机完成电子系统的设计。 是指利用计算机完成电子系统的设计。

EDA技术是以计算机和微电子技术为先导, 技术是以计算机和微电子技术为先导 ● EDA技术是以计算机和微电子技术为先导, 汇集了计算机图 形学、 拓扑、 逻辑学、 形学、 拓扑、 逻辑学、 微电子工艺与结构学和计算数学 等多种计算机应用学科最新成果的先进技术。 等多种计算机应用学科最新成果的先进技术。 EDA技术以计算机为工具, 技术以计算机为工具 ● EDA技术以计算机为工具, 代替人完成数字系统的逻辑综 合、布局布线和设计仿真等工作。 布局布线和设计仿真等工作。 等工作

EDA技术与应用课后习题答案

EDA技术与应用课后习题答案EDA技术与应用课后习题答案第一章1-1 EDA技术与ASIC设计和FPGA开发有什么关系? P3~4答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC 的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

1-2与软件描述语言相比,VHDL有什么特点? P6答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么? P5 什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型? 答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。

(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。

2023年大学_EDA技术与VHDL第二版(潘松著)课后习题答案下载

2023年EDA技术与VHDL第二版(潘松著)课后习题答案下载EDA技术与VHDL第二版(潘松著)课后答案下载第1章 EDA技术概述1.1 EDA技术及其发展1.1.1 EDA技术的发展1.1.2 EDA技术的涵义1.1.3 EDA技术的基本特征1.2 EDA技术的主要内容及主要的EDA厂商1.2.1 EDA技术的主要内容1.2.2 主要EDA厂商概述1.3 EDA技术实现目标1.3.1 超大规模可编程逻辑器件1.3.2 半定制或全定制ASIC1.3.3 混合ASIC1.4 EDA技术应用1.4.1 EDA技术应用形式1.4.2 EDA技术应用场合1.5 EDA技术的发展趋势1.5.1 可编程器件的发展趋势1.5.2 软件开发工具的发展趋势1.5.3 输入方式的发展趋势__小结思考题和习题第2章大规模可编程逻辑器件2.1 可编程逻辑器件概述2.1.1 PLD的'发展进程2.1.2 PLD的种类及分类方法2.2 简单可编程逻辑器件2.2.1 PLD电路的表示方法及有关符号 2.2.2 PROM基本结构2.2.3 PLA基本结构2.2.4 PAL基本结构2.2.5 GAL基本结构2.3 复杂可编程逻辑器件2.3.1 CPLD基本结构2.3.2 Altera公司器件2.4 现场可编程逻辑器件2.4.1 FPGA整体结构2.4.2 Xilinx公司FPGA器件2.5 在系统可编程逻辑器件2.5.1 ispLSl/pLSl的结构2.5.2 Lattice公司ispLSI系列器件 2.6 FPGA和CPLD的开发应用2.6.1 CPLD和FPGA的编程与配置2.6.2 FPGA和CPLD的性能比较2.6.3 FPGA和CPLD的应用选择__小结思考题和习题第3章 EDA设计流程与开发3.1 EDA设计流程3.1.1 设计输入3.1.2 综合3.1.3 适配3.1.4 时序仿真与功能仿真3.1.5 编程下载3.1.6 硬件测试3.2 ASIC及其设计流程3.2.1 ASIC设计方法3.2.2 一般的ASIC设计流程3.3 可编程逻辑器件的开发环境 3.4 硬件描述语言3.5 IP核__小结思考题和习题第4章硬件描述语言VHDL4.1 VHDL概述4.1.1 VHDL的发展历程4.1.2 VHDL的特点4.2 VHDL程序基本结构4.2.1 实体4.2.2 结构体4.2.3 库4.2.4 程序包4.2.5 配置4.3 VHDL基本要素4.3.1 文字规则4.3.2 数据对象4.3.3 数据类型4.3.4 运算操作符4.3.5 VHDL结构体描述方式 4.4 VHDL顺序语句4.4.1 赋值语句4.4.2 IF语句4.4.3 等待和断言语句4.4.4 cASE语句4.4.5 LOOP语句4.4.6 RETIARN语句4.4.7 过程调用语句4.4.8 REPORT语句4.5 VHDL并行语句4.5.1 进程语句4.5.2 块语句4.5.3 并行信号代人语句4.5.4 并行过程调用语句4.5.5 并行断言语句4.5.6 参数传递语句4.5.7 元件例化语句__小结思考题和习题第5章 QuartusⅡ软件及其应用5.1 基本设计流程5.1.1 建立工作库文件夹和编辑设计文件 5.1.2 创建工程5.1.3 编译前设计5.1.4 全程编译5.1.5 时序仿真5.1.6 应用RTL电路图观察器5.2 引脚设置和下载5.2.1 引脚锁定5.2.2 配置文件下载5.2.3 AS模式编程配置器件5.2.4 JTAG间接模式编程配置器件5.2.5 USBBlaster编程配置器件使用方法 __小结思考题和习题第6章 VHDL应用实例6.1 组合逻辑电路设计6.1.1 基本门电路设计6.1.2 译码器设计6.1.3 数据选择器设计6.1.4 三态门设计6.1.5 编码器设计6.1.6 数值比较器设计6.2 时序逻辑电路设计6.2.1 时钟信号和复位信号6.2.2 触发器设计6.2.3 寄存器和移位寄存器设计6.2.4 计数器设计6.2.5 存储器设计6.3 综合实例——数字秒表的设计__小结思考题和习题第7章状态机设计7.1 一般有限状态机7.1.1 数据类型定义语句7.1.2 为什么要使用状态机 7.1.3 一般有限状态机的设计 7.2 Moore型有限状态机设计 7.2.1 多进程有限状态机7.2.2 单进程有限状态机7.3 Mealy型有限状态机7.4 状态编码7.4.1 状态位直接输出型编码 7.4.2 顺序编码7.4.3 一位热码编码7.5 状态机处理__小结思考题和习题第8章 EDlA实验开发系统8.1 GW48型实验开发系统原理与应用8.1.1 系统性能及使用注意事项8.1.2 GW48系统主板结构与使用方法8.2 实验电路结构图8.2.1 实验电路信号资源符号图说明8.2.2 各实验电路结构图特点与适用范围简述8.3 GW48CK/GK/EK/PK2系统信号名与芯片引脚对照表 __小结思考题和习题第9章 EnA技术实验实验一:全加器的设计实验二:4位加减法器的设计实验三:基本D触发器的设计实验四:同步清零计数器的设计实验五:基本移位寄存器的设计串人/串出移位寄存器实验六:同步预置数串行输出移位寄存器的设计实验七:半整数分频器的设计实验八:音乐发生器的设计实验九:交通灯控制器的设计实验十:数字时钟的设计EDA技术与VHDL第二版(潘松著):内容简介《EDA技术与VHDL》主要内容有Altera公司可编程器件及器件的选用、QuartusⅡ开发工具的使用;VHDL硬件描述语言及丰富的数字电路和电子数字系统EDA设计实例。

eda技术

2. Xilinx公司的FPGA和CPLD器件系列

Xilinx公司的CPLD以CoolRunner、XC9500系列为代表 Xilinx公司的FPGA以XC4000、Spartan、Virtex系列为 代表,从XC2000、 XC4000到Spartan和Virtex、 VirtexII pro等系列其性能不断的提高。

改和仿真,不用对印刷板进行修改;

4. 系统集成到可编程逻辑器件以后,可减少印刷板的层次和 缩小印刷板的面积。

FPGA与PAL的比较

1.FPGA有更多的I/O管脚,多达几百条,不会出现PAL逻辑没 有使用完之前,I/O已经用完; 2.有更多的触发器,可以构造许多的寄存器和计数器; 3.可以集成多个PAL; 4.减少印刷板面积,降低系统成本;降低功耗; 5. 系统有较少的元件在印刷板上,可靠性增加; 6. 可重复编程性,PAL只能一次编程,FPGA/CPLD多次编程; 7.加密能力增加。

CPLD/FPGA器件产品简介

1. Lattice 公司CPLD器件系列—ispLSI、ispMACH

系列 ispLSI1000 系列 集成度 2000-8000门 特点以及应用场合 价格便宜,适用于一般数字系统设计,例如网 卡、控制器、高速编程器、游戏机和测试仪器 仪表

ispLSI2000E /2000VL/200 0VE系列

CPLD/FPGA的编程工艺

基于熔丝和反熔丝编程单元

基于电可擦除存储单元的EEPROM或FLASH技术

基于SRAM查找表的编程单元

现场可编程门阵列FPGA的特点

SRAM结构:可以无限次编程,但它属于易失性元件,掉电后 芯片内信息丢失。通电之后,要为FPGA重新配置逻辑 内部连线结构:CPLD的信号通路固定,系统速度可以预测。 而FPGA的内连线是分布在CLB周围,而且编程的种类和编程 点很多,布线相当灵活。 芯片逻辑利用率:由于FPGA的CLB规模小,可分为两个独立 的电路,又有丰富的连线,其逻辑利用率很高。

eda技术实用教程-veriloghdl答案

eda技术实用教程-veriloghdl答案【篇一:eda技术与vhdl程序开发基础教程课后答案】eda的英文全称是electronic design automation2.eda系统设计自动化eda阶段三个发展阶段3. eda技术的应用可概括为4.目前比较流行的主流厂家的eda软件有、5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有7.逻辑综合后生成的网表文件为 edif8.布局布线主要完成9.10.常用的第三方eda工具软件有synplify/synplify pro、leonardo spectrum1.8.2选择1.eda技术发展历程的正确描述为(a)a cad-cae-edab eda-cad-caec eda-cae-cadd cae-cad-eda2.altera的第四代eda集成开发环境为(c)a modelsimb mux+plus iic quartus iid ise3.下列eda工具中,支持状态图输入方式的是(b)a quartus iib isec ispdesignexpertd syplify pro4.下列几种仿真中考虑了物理模型参数的仿真是(a)a 时序仿真b 功能仿真c 行为仿真d 逻辑仿真5.下列描述eda工程设计流程正确的是(c)a输入-综合-布线-下载-仿真b布线-仿真-下载-输入-综合c输入-综合-布线-仿真-下载d输入-仿真-综合-布线-下载6.下列编程语言中不属于硬件描述语言的是(d)a vhdlb verilogc abeld php1.8.3问答1.结合本章学习的知识,简述什么是eda技术?谈谈自己对eda技术的认识?答:eda(electronic design automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

2.简要介绍eda技术的发展历程?答:现代eda技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

1、2EDA简介与可编程逻辑器件PLD

– 是电子系统硬件行为描述、结构描述、逻辑描述的 语言 。

• HDL常用来设计规模较大、复杂的电子系统

EDA工具

用HDL描 述设计

综合、仿真

目标文件

编程下载

所谓的高层设计(High Level Design)方法

数字系统的设计描述方法

• 优点:

–能形象化、抽象地表示电路的结构和行为 –适于描述逻辑功能 –借用高级语言简化电路的描述 –具有电路仿真与验证机制 –便于文档管理 –易于理解和移植重用

电子设计自动化

——EDA 魏永涛

什么是EDA

• Electronic Design Automation电子设计自动化

–是在计算机的辅助下完成电子产品设计的一种先 进的硬件设计技术!

–是立足于计算机工作平台开发出来的一整套先进 的设计电子系统的软件工具。

信息处理

应用电子

人工智能

EDA

计算机

拓扑学

计算数学

√系统级抽象能力较强

√适合由多人合作完成的 测试激励模块容易编写 特大型项目(一百万门以

5.现场可编程门阵列FPGA

(Field Programmable Gate Array)集成度>3万门/片

EPLD和FPGA集成密度高,称为高密度PLD 以上五种PLD编程开发系统由硬件(计算机和 编程器)和软件(专用编程软件)构成。

6. 在 系 统 可 编 程 器 件 ISP(In-System Programmable)-PLD是新一代器件,不需编程 器,只要将计算机编程产生的数据直接写入 PLD 就 可 以 了 。 其 中 高 密 度 ISP-PLD 又 称 为 CPLD(Complex Programmable Logic Device)

1.EDA技术概述

内容:ቤተ መጻሕፍቲ ባይዱ

1、EDA技术综述 2、FPGA/CPLD结构原理 3、VHDL语言 4、实验:

-Quartus II软件及一位全加器设计 -交通灯信号控制器设计 参考教材:《EDA技术与应用》王紫婷编 兰州大学出版社

实习报告要求

1、理论部分:

※EDA技术概念 ※EDA技术开发流程

※FPGA/CPLD概念和结构特点

4、适配器

逻辑综合通过后必须利用适配器将综合后网表文件针对 某一具体的目标器件进行逻辑映射操作,其中包括底层器件 配臵、逻辑分割、逻辑优化、逻辑布局布线操作。适配完成 后可以利用适配所产生的仿真文件作精确的时序仿真,同时 产生可用于编程的文件。 它的功能是将由综合器产生的网表文件配臵于指定的目 标器件中,使之产生最终的下载文件,如JEDEC、Jam格式的 文件。适配所选定的目标器件(FPGA/CPLD芯片)必须属于原 综合器指定的目标器件系列。 由可编程逻辑器件的厂商提供的开发软件来完成。

1、JTAG方式下载 2、针对SRAM结构的配臵 3、配臵器件编程

FPGA/CPLD 适配

结构综合器

FPGA/CPLD 编程下载

1、设计输入

• 图形输入

– 原理图输入、状态图输入、波形图输入 – 兼容性差

• HDL文本输入

– 最基本、最有效和最通用的输入方式

2、综合

• 将软件转换为硬件电路的关键步骤 • 将电路高级语言转化成低级的,可与FPGA/CPLD的基本 结构相映射的网表文件或程序 • 映射并不是唯一的

软件程序编译器

COMPILER

(a)软件语言设计目标流程

CPU指令/数据代码: 010010 100010 1100

eda技术及应用第三版课后答案谭会生

eda技术及应用第三版课后答案谭会生【篇一:《eda技术》课程大纲】>一、课程概述1.课程描述《eda技术》是通信工程专业的一门重要的集中实践课,是通信工程专业学生所必须具备的现代电子设计技术技能知识。

eda是电子技术的发展方向,也是电子技术教学中必不可少的内容。

本课程主要介绍可编程逻辑器件在电子电路设计及实现上的应用,介绍电路原理图和pcb图的设计技术。

开设该课程,就是要让学生了解大规模专用集成电路fpga和cpld的结构,熟悉一种以上的硬件描述语言,掌握一种以上的开发工具的使用等,掌握电路原理图和pcb图的现代设计技术与方法,从而提高学生应用计算机对电子电路和高速智能化系统进行分析与设计的能力。

2.设计思路本课程坚持“以学生为中心”的原则,以项目任务驱动的方式,采取理论知识与案例相结合的方式授课,提高学生的学习主动性。

通过必要的理论知识讲授、大量的实践训练和案例分析,培养学生的动手设计和实践能力,掌握eda开发的整个流程和基本技巧。

课程采用演示讲授和实践相结合,边讲边练的方法,让学生切身体会并掌握eda开发产品的流程和方法。

本课程集中2周时间开设,注重实践性,边讲边练,让学生切身体会并掌握eda开发技术。

3.实践要求(1)纪律和安全要求①不得将食物带入实验室,每次实训后请将使用后的废弃物带走。

违反者每次扣罚平时分2分。

②实训期间不得做与实训无关的其他事情,不得大声喧哗或做其他影响实训正常进行的事宜。

违反者每次扣罚平时分2分。

③实训期间,若学生有事不能正常参加实训,须提前以书面形式请假,并按指导教师的安排补做实训。

未经指导教师许可,学生不得任意调换实训时间和实训地点。

违反者每次扣罚平时分4分。

④学生不得以任何理由替代他人进行实训,违者直接取消实训成绩。

⑤学生除操作自己所分配的计算机外,不得操作实验室内其他任何设备。

违者每次扣罚平时分2分。

(2)业务要求实训所使用的软件protel和quartus ii,所有数据均通过服务器中转以及储存在服务器上,所以重启自己所用的电脑不会造成数据丢失。

EDA技术与VHDL程序设计基础教程

二、EDA技术的发展历程和未来展望

现代EDA技术是20世纪90年代初从计算机辅助设计、辅助制造和辅 助测试等工程概念发展而来的。它的成熟主要经历了三个阶段,即:

计算机辅助设计(CAD,Computer Aided Design) 计算机辅助工程设计(CAED,Computer Aided Engineering Design) 电子设计自动化(EDA,Electronic System DesignAutomation)。

11 111 111 11111111 11

&

≥1

&

≥1

&

≥1

&

≥1

1

三、 CPLD的基本结构和工作原理

1.输出逻辑宏单元 2.控制电路

3.全局布线区

属于ispLSI中的一种专用内部 互联结构。起作用是将GLB的 输出信号或I/O单元的输入信 号与GLB的输入端连接

EDA技术主要有四个方面: 1、可编程逻辑器件,即应用EDA技术完成电子系统设计的载体; 2、硬件描述语言(VHDL 或者 Verilog)。它用来描述系统的结构和功

能,是EDA的主要表达手段; 3、配套的软件工具。它用来完成电子系统的智能化设计; 4、实验开发系统。在整个EDA设计电子系统的过程中,实验开发系统是 实现可编程器件下载和验证的工具,

第2章

重点内容:

CPLD结构和工作原理 FPGA结构和工作原理 FPGA配置方式 CPLD/FPGA应用选型

一、可编程逻辑器件概述

可编程逻辑器件 PROM、PLA和PAL的原理和特性

PROM

基于二极管和三极管 的一次可编程PROM单 字线

元

二极管

上拉电阻

数字系统设计与Verilog HDL

数字系统设计与Verilog HDL(复习)EDA(Electronic Design Automation)就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子CAD(Computer Aided Design)2.电子CAE(Computer Aided Engineering)3.EDA(Electronic Design Automation)EDA技术及其发展p2EDA技术的应用范畴1.3 数字系统设计的流程基于FPGA/CPLD的数字系统设计流程1. 原理图输入(Schematic diagrams )2、硬件描述语言 (HDL文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(Synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(RTL)◆逻辑综合:RTL级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对CPLD器件而言,产生熔丝图文件,即JEDEC文件;对FPGA器件则产生Bitstream 位流数据文件p8仿真(Simulation)功能仿真(Function Simulation)时序仿真(Timing Simulation)仿真是对所设计电路的功能的验证p9编程(Program)把适配后生成的编程文件装入到PLD器件中的过程,或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program),将基于SRAM 工艺结构的PLD器件的下载称为配置(Configure)。

CPLD及FPGA介绍

深圳双恩科技有限公司产品使用说明书一、FPGA/PLD的基本概念:PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或PLD/FPGA。

PLD是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于70年代单片机的发明和使用。

单片机在时序和延迟方面优于FPGA/PLD,但在速度、芯片容量和数字逻辑方面不及FPGA/PLD。

PLD能做什么呢?可以毫不夸张的讲,PLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用PLD来实现。

PLD如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统。

通过软件仿真,我们可以事先验证设计的正确性。

在PCB完成以后,还可以利用PLD的在线修改能力,随时修改设计而不必改动硬件电路。

使用PLD来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。

PLD的这些优点使得PLD技术在90年代以后得到飞速的发展,同时也大大推动了EDA软件和硬件描述语言(HDL)的进步。

1如何使用PLD呢?其实PLD的使用很简单,学习PLD比学习单片机要简单的多,有数字电路基础,会使用计算机,就可以进行PLD的开发。

开发PLD需要了解两个部分:1.PLD开发软件 2.PLD本身1.PLD开发软件由于PLD软件已经发展的相当完善,用户甚至可以不用详细了解PLD的内部结构,也可以用自己熟悉的方法:如原理图输入或HDL语言来完成相当优秀的PLD设计。

所以对初学者,首先应了解PLD开发软件和开发流程。

了解PLD的内部结构,将有助于提高我们设计的效率和可靠性。

如何获得PLD开发软件软件呢? 许多PLD公司都提供免费试用版或演示版(当然商业版大都是收费的),例如:可以免费从/上下载Altera公司的 Maxplus2 (Baseline版或E+MAX版),或向其代理商索取这套软件。

EDA技术与FPGA基础

EDA技术与FPGA基础3.1 EDA技术现代电子技术的核心是EDA(Electronic Design Automation电子设计自动化)技术。

EDA技术就是依赖功能强大的计算机,在EDA工具软件平台上,对以硬件描述语言HDL(Hardware Description Language)为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、逻辑化简、逻辑分割、逻辑综合、结构综合(布局布线),以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

EDA 技术使得设计者的工作仅限于利用软件的方式,即利用硬件描述语言和EDA软件来完成对系统硬件功能的实现。

EDA技术在硬件实现方面融合了大规模集成电路制造技术,IC版图设计技术、ASIC测试和封装技术、FPGA/CPLD编程下载技术、自动测试技术等;在计算机辅助工程方面融合了计算机辅助设计(CAD),计算机辅助制造(CAM)、计算机辅助测试(CAT)、计算机辅助工程(CAE)技术以及多种计算机语言的设计概念:而在现代电子学方面则容纳了更多的内容,如电子线路设计理论、数字信号处理技术、数字系统建模和优化技术及长线技术理论等等。

因此EDA技术为现代电子理论和设计的表达与实现提供了可能性。

当然,这里的所谓EDA主要是指数字系统的自动化设计,因为这一领域的软硬件方面的技术已比较成熟,应用的普及程度也比较高。

而模拟电子系统的EDA正在进入实用,其初期的EDA工具不一定需要硬件描述语言。

此外,从应用的广度和深度来说,由于电子信息领域的全面数字化,基于EDA的数字系统的设计技术具有更大的应用市场和更紧迫的需求性。

EDA技术的发展历程同大规模集成电路设计技术、计算机辅助工程、可编程逻辑器件,以及电子设计技术和工艺的发展是同步的。

20世纪80年代,集成电路设计进入了CMOS(互补场效应管)时代,复杂可编程逻辑器件已进入商用阶段,而在80年代末,出现了FPGA(Field Programmable Gate Array现场可编程门阵列)和CPLD(Complex Programmable Logic Device复杂可编程逻辑器件),其特点是直接面向用户,具有极大的灵活性和通用性,使用方便,硬件测试和实现快捷,开发效率高,电子系统设计工程师可以在实验室中设计出专用的IC, 实现系统的集成,从而大大缩短了产品上市时间,降低了开发成本。

eda技术实用教程-veriloghdl答案

eda技术实用教程-veriloghdl答案【篇一:eda技术与vhdl程序开发基础教程课后答案】eda的英文全称是electronic design automation2.eda系统设计自动化eda阶段三个发展阶段3. eda技术的应用可概括为4.目前比较流行的主流厂家的eda软件有、5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有7.逻辑综合后生成的网表文件为 edif8.布局布线主要完成9.10.常用的第三方eda工具软件有synplify/synplify pro、leonardo spectrum1.8.2选择1.eda技术发展历程的正确描述为(a)a cad-cae-edab eda-cad-caec eda-cae-cadd cae-cad-eda2.altera的第四代eda集成开发环境为(c)a modelsimb mux+plus iic quartus iid ise3.下列eda工具中,支持状态图输入方式的是(b)a quartus iib isec ispdesignexpertd syplify pro4.下列几种仿真中考虑了物理模型参数的仿真是(a)a 时序仿真b 功能仿真c 行为仿真d 逻辑仿真5.下列描述eda工程设计流程正确的是(c)a输入-综合-布线-下载-仿真b布线-仿真-下载-输入-综合c输入-综合-布线-仿真-下载d输入-仿真-综合-布线-下载6.下列编程语言中不属于硬件描述语言的是(d)a vhdlb verilogc abeld php1.8.3问答1.结合本章学习的知识,简述什么是eda技术?谈谈自己对eda技术的认识?答:eda(electronic design automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

2.简要介绍eda技术的发展历程?答:现代eda技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

第三章 FPGA/CPLD设计流程

EDA技术讲义

FPGA芯片叫板微处理器 FPGA 芯片在一定程度上正在蚕食微处理器的市场。 FPGA 芯片也开始用于消费类的电子设备中,包括手机和数码相机。 飞利浦、诺基亚、 Palm及索尼均在其消费类的电子产品中采用 了FPGA芯片。 XILINX 的首席执行官 W.Roelandts 亲眼目睹了 FPGA 如何改 变电脑构架。50多年前,匈牙利数学家纽曼(John von Neumann )提出了电脑的设计构想 ----通过中央处理器从存储器中存取数 据,并逐一处理各项任务。现在,通过采用可编程芯片FPGA取 代微处理器,电脑可并行处理多项任务。 W.Roelandts说,“由纽曼提出的电脑架构已经走到尽头” ,“可编程芯片将掀起下一轮应用高潮。

尽管FPGA芯片的主频要低于奔腾处理器,但是由于FPGA 芯片可并行处理多项任务 ,因此处理速度要比奔腾处理器 或数字信号处理器快得多!

FPGA芯片武装超级电脑

EDA技术讲义

FPGA芯片叫板微处理器 美国赢通系统公司(Wincom Systems)推出一款令人惊叹的服 务器。这款专为网站运行而设计的服务器尺寸仅有 DVD 播放机 大小,工作能力却相当于 ,甚至超过 50 台戴尔、IBM 或 SUN 公司 售价 5000 美元的服务器。赢通公司的这款服务器并未采用目前 电脑中不可或缺的微处理器。 传统的个人电脑及服务器通常采用英特尔的奔腾处理器或 SUN 计算机系统公司的 SPARC 芯片作为中央处理单元。而赢通的这 一产品却没有采用微处理器,而是由FPGA芯片驱动。 FPGA芯片的运行速度比奔腾处理器慢,但可并行处理多项任务 ,而微处理器一次仅能处理一项任务。因此,赢通公司的服务 器只需配置几个价格仅为 2000 多美元的 FPGA 芯片,便可击败 SUN 计算机系统公司的服务器或采用英特尔处理器的电脑,“ 我们的服务器处理速度要比普通服务器快50到300倍”。

EDA技术及应用—Verilog HDL版(第三版) (1)

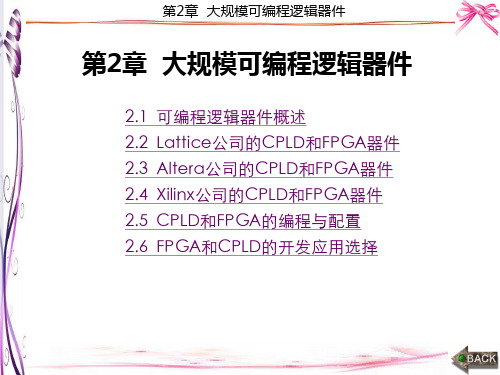

第2章 大规模可编程逻辑器件

(4) 封装代码。如Altera公司的EPM7128SLC84中的LC, 表示采用PLCC封装(Plastic Leaded Chip Carrier,塑料方形扁 平封装)。PLD封装除PLCC外,还有BGA(Ball Grid Array, 球形网状阵列)、C/JLCC(Ceramic /J-Leaded Chip Carrier,)、 C/M/P/TQFP(Ceramic/Metal/Plastic/Thin Quard Flat Package)、 PDIP/DIP(Plastic Double In line Package)、PGA(Ceramic Pin Grid Array)等,多以其缩写来描述,但要注意各公司稍有差 别,如PLCC,Altera公司用LC描述,Xilinx公司用PC描述, Lattice公司用J来描述。

第2章 大规模可编程逻辑器件

2.1.1 PLD的发展进程

最早的可编程逻辑器件出现在20世纪70年代初,主要是 可编程只读存储器(PROM)和可编程逻辑阵列(PLA)。20世 纪70年代末出现了可编程阵列逻辑(Programmable Array Logic,简称PAL)器件。20世纪80年代初期,美国Lattice公 司推出了一种新型的PLD器件,称为通用阵列逻辑(Generic Array Logic,简称GAL),一般认为它是第二代PLD器件。 随着技术进步,生产工艺不断改进,器件规模不断扩大,逻 辑功能不断增强,各种可编程逻辑器件如雨后春笋般涌现, 如PROM、EPROM、EEPROM等。

第2章 大规模可编程逻辑器件

采用ISP技术之后,硬件设计可以变得像软件设计那样灵活 而易于修改,硬件的功能也可以实时地加以更新或按预定的 程序改变配置。这不仅扩展了器件的用途,缩短了系统的设 计和调试周期,而且还省去了对器件单独编程的环节,因而 也省去了器件编程设备,简化了目标系统的现场升级和维护 工作。

集成电路中EDA技术 自上而下方法 及FPGA和CPLD

随着大规模集成电路和电子计算机的迅速发展,电子电路分析与设计方法发生了根本性变革。

以计算机辅助分析与设计为基础的电子设计自动化EDA (Electronic Design Automation)技术已经广泛应用于集成电路与系统的设计中。

电子设计自动化技术改变了以定量计算、估算和实验为基础的传统电子电路设计方法,使产品从电路设计、性能分析、参数优化到PCB(印制电路板)和专用集成电路设计,可以由计算机完成,实现了整个过程成的自动化。

因此,EDA 刚一出现,便在电子工程设计领域刮起一场狂飙,引发了一场设计方法的大革命。

所以,新一代电子设计工程师以及从事电子技术开发和研究的人员必须掌握EDA 技术。

一、EDA技术的简介EDA是电子设计自动化(Electronic Design Automation)的缩写,是从CAD (计算机辅助设计)、CAM(计算机辅助制造)、CAT(计算机辅助测试)和CAE(计算机辅助工程)的概念发展而来的。

EDA技术是以计算机为工具集数据库、图形学、图论与拓扑逻辑、计算数学、优化理论等多学科最新理论于一体,是计算机信息技术、微电子技术、电路理论、信息分析与信号处理的结晶。

它能根据硬件描述语言自动完成逻辑编译、化简、分割、综合及优化、布局布线、仿真以及对于特定目标芯片的适配编译和编程下载等工作。

20世纪90年代以来,微电子技术以惊人的速度发展,其工艺水平达到深亚微米级,在一个芯片上可继承数百万乃至上千万只晶体管,工作速度可达到GHz,这为制造出规模和信息容量更大,速度更快的芯片系统提供了条件,但同时也对EDA系统提出了更高的要求,并促进了EDA技术的发展。

此阶段出现了以高级语言描述、系统仿真和综合技术为特征的第三代EDA技术。

它不仅极大地提高了系统的设计效率,而且使设计人员摆脱了大量的辅助性及基础性工作,从而能够将精力集中于创造性的方案与概念的构思上。

EDA技术在进入21世纪后,得到了更大的发展,突出表现在以下几个方面:1)在FPGA上实现DSP应用成为可能;用纯数字逻辑进行DSP模块的设计,使得高速DSP实现成为现实,并有力地推动了软件无线电技术的实用化和发展。

EDA技术 第二章 eda设计工具及其流程

ASIC

数字 ASIC

混合 ASIC

模拟 ASIC

ASIC设计方法

按版图结构及制造方法分,有半定制(Semi-custom)和全 定制(Full-custom)两种实现方法。

全定制方法 是一种基

于晶体管级的,手工设 计版图的制造方法。

全定制法 半定制法 ASIC设计方法

半定制法 是一种

约束性设计方式,约 束的目的是简化设计 ,缩短设计周期,降 低设计成本,提高设 计正确率。 门阵列法 标准单元法

硬件测试

最后是将含有载入了设计的 FPGA或CPLD的硬件系统进行统一 测试,以便最终验证设计项目在 目标系统上的实际工作情况,以 排除错误,改进设计。

ASIC及其设计流程

ASIC(Application Specific Integrated Circuits,专用集成电路) 是相对于通用集成电路而 言的,ASIC主要指用于某 一专门用途的集成电路器 件。ASIC按功能分类大致 可分为数字ASIC、模拟 ASIC和数模混合ASIC。

综合器的使用也有两种模式: 图形模式和命令行模式(Shell模式)。

常用EDA工具

仿真器

按处理的硬件描述语言类型分,HDL仿真器可分为:

(1) VHDL仿真器。 (2) Verilog仿真器。 (3) Mixed HDL仿真器(混合HDL仿真器,同时处理Verilog与VHDL)。

Mentor的ModelSim

综合

FPGA/CPLD

器件和电路系统

1、isp方式下载 2、JTAG方式下载 3、针对SRAM结构的配置 4、OTP器件编程

功能仿真

逻辑综合器

FPGA/CPLD

适配

结构综合器 FPGA/CPLD 编程下载

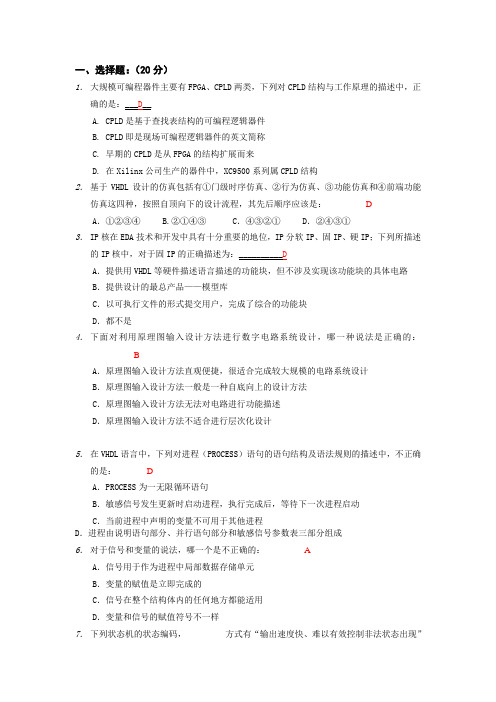

EDA选择题(含答案)

一、选择题:(20分)1.大规模可编程器件主要有FPGA、CPLD两类,下列对CPLD结构与工作原理的描述中,正确的是:___D__A. CPLD是基于查找表结构的可编程逻辑器件B. CPLD即是现场可编程逻辑器件的英文简称C. 早期的CPLD是从FPGA的结构扩展而来D. 在Xilinx公司生产的器件中,XC9500系列属CPLD结构2.基于VHDL设计的仿真包括有①门级时序仿真、②行为仿真、③功能仿真和④前端功能仿真这四种,按照自顶向下的设计流程,其先后顺序应该是:_________DA.①②③④ B.②①④③C.④③②①D.②④③①3.IP核在EDA技术和开发中具有十分重要的地位,IP分软IP、固IP、硬IP;下列所描述的IP核中,对于固IP的正确描述为:__________DA.提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路B.提供设计的最总产品——模型库C.以可执行文件的形式提交用户,完成了综合的功能块D.都不是4.下面对利用原理图输入设计方法进行数字电路系统设计,哪一种说法是正确的:__________BA.原理图输入设计方法直观便捷,很适合完成较大规模的电路系统设计B.原理图输入设计方法一般是一种自底向上的设计方法C.原理图输入设计方法无法对电路进行功能描述D.原理图输入设计方法不适合进行层次化设计5.在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,不正确的是:_______DA.PROCESS为一无限循环语句B.敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动C.当前进程中声明的变量不可用于其他进程D.进程由说明语句部分、并行语句部分和敏感信号参数表三部分组成6.对于信号和变量的说法,哪一个是不正确的:_________AA.信号用于作为进程中局部数据存储单元B.变量的赋值是立即完成的C.信号在整个结构体内的任何地方都能适用D.变量和信号的赋值符号不一样7.下列状态机的状态编码,_________方式有“输出速度快、难以有效控制非法状态出现”这个特点。

学eda技术必看的8本书_eda技术方面的书籍推荐

学eda技术必看的8本书_eda技术方面的书籍推荐随着EDA技术的发展,EDA技术的广泛应用,电子产品的更新日新月异,EDA技术已成为现代电子设计的核心。

越来越多的人加入到eda技术行业,本文小编推荐了基本学习eda技术必看的书籍,具体的跟随小编来了解一下。

1、EDA技术基础本书从EDA技术的应用角度出发,简明而系统地介绍了EDA技术的相关内容。

包括EDA技术的概念及特点,EDA技术的物质载体——可编程逻辑器件。

EDA技术的设计语言——硬件描述语言VHDL,EDA技术的开发设计流程和工具软件MAX+plusIl及Quartusll。

此外,第5章给出了大量常用VHDL设计实例,第8章详细阐述了几个典型的EDA技术综合应用设计实例,并在第9章编写了多个实验项目。

全书在取材和编排上,力求理论联系实际,由浅入深,循序渐进。

2、EDA技术与应用本书为普通高等教育“十一五”国家级规划教材,主要内容包括:EDA 技术;电路设计仿真软件PSpice、Muhisim8的使用方法;可编程逻辑器件的工作原理、分类及应用;硬件描述语言Verilog HDL的语法要点与设计实例;数字集成软件Quartus n、仿真软件ModelSim、综合软件SynplifyPro等的使用方法及设计流程;EDA技术综合设计实例。

本书内容全面,注重基础,理论联系实际,突出实用性,并使用大量图表说明问题,编写简明精炼、针对性强,设计实例都通过了编译,设计文件和参数选择都经过验证,便于读者对内容的理解和掌握。

3、CPLD/FPGA与ASIC设计实践教程《CPLD/FPGA与ASIC设计实践教程(第2版)》以大规模可编程逻辑器件为基础,详细介绍了PLD、CPLD/FPGA器件的原理和开发技术。

第1~3章介绍EDA技术和可编程逻辑器件的原理,CPLD/FPGA器件的性能指标与选型、编程方法和下载电路,以及常用EDA设计软件的使用。

第4~6章先详细介绍Verilog HDL 语言,然后按照数字电路与逻辑设计课程的顺序,通过实例说明常用数字逻辑电路的实现方法,并讨论利用Verilog HDL设计可综合的数字电路的方法与技巧。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第13页/共26页

4.可编程连线阵列(PIA)

PIA信号布线到LAB的方式

第14页/共26页

5.I/O控制块

EPM7128S器件 的I/O控制块

第15页/共26页

3.3 编程与配置

USB-Blaster下载电缆

引脚

1

2

下载接口引脚信号名称

3

4

5

6

7

8

9

10

PS模式

DCK

GND

PS模式,FLEX10K配置时序

第19页/共26页

使用PC并行口配置FPGA

多FPGA芯片第配20置页电/共路26页

FPGA专用配置器件

FPGA的配置电路原理图

第21页/共26页

FPGA专用配置器件

EPCS器件配置FPGA的电路原理图

第22页/共26页

使用单片机配置FPGA

用89C52进行配置

Cyclone LE普通模式

第2页/共26页

行、列 直连线布线

行、列 直连线布线

行、列 直连线布线

LUT链

寄存器链

Cyclone系列器件的结构与原理

LAB 进位输入 进位输入0 进位输入1

addnsub Data1 Data2

Data3

进位输入 逻辑

两个 2输入 LUT (和)

寄存器链 输入

寄存器 控制信号

两个 2输入

LUT (进位)

同步装载 清零逻辑

寄 存

器

行、列和 直连线布线

局部布线

进位输出 逻辑

进位输出0 进位输出1

寄存器链 输出

Cyclone LE动态算术模式

第3页/共26页

Cyclone系列器件的结构与原理

控制信号

LAB输入信号

局部互连

4

LE1

4

LE2

4

LE3

4

LE4

4

LE5

4

LE6

4

LE7

3.2 典型CPLD的结构

1.逻辑阵列块(LAB)

MAX7128S的结构

第10页/共26页

2.宏单元

MAX7000系列的单个宏单元结构 第11页/共26页

3.扩展乘积项

局部连线

共享扩展 项提供的 “与非” 乘积项

共享扩展乘积项结构

宏单元的 乘积项 逻辑

宏单元的 乘积项 逻辑

第12页/共26页

3.扩展乘积项

快速进位选择链

第7页/共26页

进位输出0

进位输出1

Cyclone系列器件的结构与原理

LE1

Lut

DQ

LE2

Lut

DQ

LUT链

LEs 3- 10

寄存器链

LUT链和寄存器链的使用

第8页/共26页

Cyclone系列器件的结构与原理

Cyclone器件

接收器件

外接电阻网路

外接终端电阻

LVDS连接

第9页/共26页

第25页/共26页

感谢您的欣赏!

第26页/共26页

CONF_DONE

VCC

nCONFIG

-

nSTATUS

-

DATA0

GND

JATG模

TCK

GND

TDO

VCC

TMS

-

-

式

-

TDI

GND

第16页/共26页

JTAG方式的在系统编程

CPLD编程下载连接图

第17页/共26页

JTAG方式的在系统编程

多CPLD芯片ISP编程连接方式

第18页/共26页

使用PC并行口配置FPGA

第23页/共26页

使用CPLD配置FPGA

使用单片机配置的缺点: 1、速度慢,不适用于大规模FPGA和高可靠 应用; 2、容量小,单片机引脚少,不适合接大的 ROM以存储较大的配置文件; 3、体积大,成本和功耗都不利于相关的设 计。

第24页/共26页

习题

3-1 OLMC有何功能?说明GAL是怎样实现可编程组合电 路与时序电路的。 3-2 什么是基于乘积项的可编程逻辑结构? 3-3 什么是基于查找表的可编程逻辑结构? 3-4 FLEX10K系列器件中的EAB有何作用? 3-5 与传统的测试技术相比,边界扫描技术有何优点? 3-6 解释编程与配置这两个概念。

01

LLeE11 和1 LLeE22 和2 LLeE33 和3 LLeE44 和4 LE5 和5

01

LE6 和6 LE7 和7 LE8 和8 LE9 和9 LE10 和10

LAB进位输出

LAB 进位输入 进位输入0 进位输入1

A B

0

1

2输入LUT

A+B+0

0

和

A+B+1

1

A+B+0

A+B+1

10

10

CLKENA2 SYNCLOAD

CLR2

ADDNSUB

CLK2

ASYNCLOAD /LABPRE

LAB控制信号生成

第6页/共26页

CLR1

SYNCCLR

LAB进位输入

A1 B1

A2 B2

A3 B3

A4 B4

A5 B5

A6 B6

A7 B7

A8 B8

A9 B9

A10 B10

Cyclone系列器件的结构与原理

Cyclone系列器件的结构与原理

Cyclone LE结构图

第1页/共26页

Cyclone系列器件的结构与原理

sload sclear

aload

addnsub

data1 data2 data3

cin data4

寄存器链 输入

44--iinnppuutt LLUUTT

clock ena aclr

RReegg

4

LE8

4

LE9

4

LE10

LUT链 和

寄存器链

LE反馈信号连线

Cyclone LAB结构

第4页/共26页

Cyclone系列器件的结构与原理

LAB阵列

第5页/共26页

Cyclone系列器件的结构与原理

LAB 行 Clock

6

至每个寄存器

/

局部互连

局部互连

局部互连

局部互连 局部互连

局部互连

CLKENA1