晶振和电容的匹配原理

25m晶振匹配电容

25m晶振匹配电容摘要:1.晶振与电容的基本概念2.25MHz 晶振的特点3.匹配电容的作用4.25MHz 晶振匹配电容的选择与计算5.实际应用中25MHz 晶振与匹配电容的注意事项正文:在电子电路设计中,晶振与电容的搭配是非常重要的,它们共同组成了电路中的谐振回路。

本文将详细介绍25MHz 晶振匹配电容的相关知识,包括晶振与电容的基本概念、25MHz 晶振的特点、匹配电容的作用、25MHz 晶振匹配电容的选择与计算以及实际应用中25MHz 晶振与匹配电容的注意事项。

首先,我们需要了解晶振与电容的基本概念。

晶振是一种能够产生稳定频率振荡的电子元件,它将电能转化为机械能,再将机械能转化为电能。

而电容是一种能够储存电荷的电子元件,具有筛选信号、滤波等功能。

在电路中,晶振与电容共同组成谐振回路,晶振产生的振荡信号经过电容滤波后,输出稳定的振荡信号。

接下来,我们来了解25MHz 晶振的特点。

25MHz 晶振,即频率为25MHz 的晶体振荡器,具有较高的频率稳定性。

在通信、遥控、导航等领域有着广泛的应用。

由于25MHz 晶振的谐振特性,其与匹配电容的搭配至关重要。

那么,匹配电容的作用是什么呢?匹配电容主要是为了使晶振的输出信号能够更好地传输到下一个电路元件,它的选取要与晶振的特性相匹配,以达到最佳的传输效果。

匹配电容的选择与计算需要根据晶振的谐振频率、工作电压、负载电容等参数来确定。

在实际应用中,25MHz 晶振与匹配电容的搭配需要注意以下几点:1.选择合适的匹配电容值,使晶振的输出信号能够有效地传输到下一个电路元件。

2.确保匹配电容的稳定性,避免由于电容变化导致的频率漂移。

3.在布局和安装时,注意将晶振与电容尽可能靠近,以减小传输线效应和噪声影响。

总之,25MHz 晶振匹配电容的选择与计算以及实际应用中的注意事项对于保证电路性能至关重要。

25m晶振匹配电容

25m晶振匹配电容随着电子技术的不断发展,25m晶振已经成为众多电子设备中不可或缺的元器件。

它具有良好的频率稳定性和精度,广泛应用于通信、计算机、消费电子等领域。

而在25m晶振的使用过程中,匹配电容的选择与计算至关重要,它将直接影响到整个电路的性能。

一、25m晶振概述25m晶振,即工作频率为25MHz(兆赫兹)的石英晶体振荡器。

它通过石英晶体谐振器与电子电路的结合,产生稳定的正弦波信号。

在实际应用中,25m晶振不仅能为电路提供稳定的时钟信号,还能起到滤波、振荡等作用。

二、25m晶振匹配电容的作用在25m晶振电路中,匹配电容起到调整电路阻抗、提高信号传输效率的作用。

匹配电容的大小会影响到晶振的工作稳定性、输出信号质量以及电路的功耗等。

因此,合理选择匹配电容对于保证25m晶振电路的性能至关重要。

三、匹配电容的选择与计算1.电容值的选择匹配电容的选取主要依据晶振的频率、工作电压、负载电阻等因素。

一般情况下,匹配电容的电容值可通过以下公式进行计算:C_match = √(F × R_load)其中,F为晶振的频率(单位:Hz),R_load为负载电阻(单位:Ω)。

2.电容材质的选择匹配电容的材质对电容的性能有很大影响。

常见的匹配电容材质有陶瓷、聚酯、聚苯乙烯等。

其中,陶瓷电容具有较高的容值精度、稳定性好等特点,适用于高精度、高稳定性的电路;聚酯电容和聚苯乙烯电容则具有良好的频率响应和较低的介质损耗,适用于宽带、低功耗的电路。

3.电容尺寸的选择电容尺寸的选择主要考虑电容的容值、工作电压、安装空间等因素。

电容尺寸越大,容值越大,但体积和重量也相应增加。

在实际应用中,应根据电路设计和安装空间的要求,选择合适的电容尺寸。

四、25m晶振应用场景及注意事项1.应用场景25m晶振广泛应用于通信设备、计算机、嵌入式系统、仪器仪表、消费电子等领域。

如:手机、路由器、卫星接收器、测量仪器等。

2.注意事项(1)在选择匹配电容时,应注意电容的容值、工作电压、频率响应等参数,确保与25m晶振电路相匹配。

20pf晶振匹配电容

20pf晶振匹配电容以20pf晶振匹配电容为标题,我们来探讨一下晶振匹配电容的相关内容。

晶振匹配电容是指在电子电路中,为了确保晶振的稳定工作,需要使用适当的电容与晶振进行匹配。

匹配电容的选择对于电路的性能和稳定性有着重要的影响。

我们需要了解晶振的工作原理。

晶振是一种利用晶体的谐振特性来产生稳定频率的振荡器。

在电子设备中,晶振被广泛应用于时钟电路、通信电路、计算机电路等领域。

晶振的频率由晶体的物理特性决定,通常以赫兹(Hz)为单位表示。

在晶振的工作中,它需要与外部电路相互作用,而这个作用是通过电容来实现的。

晶振匹配电容的作用是为了调节晶振的频率,使之达到设计要求。

匹配电容的选择需要根据晶振的频率和电路的要求进行合理的设计。

在选择匹配电容时,我们需要考虑以下几个因素:1. 电容值:匹配电容的电容值与晶振的频率有关。

一般来说,晶振的频率越高,所需的匹配电容的电容值越小。

对于20pf晶振,我们需要选择适当的匹配电容,以确保晶振的稳定工作。

2. 电容精度:匹配电容的精度也是一个重要的考虑因素。

晶振对电容的精度要求较高,一般在1%或更高的精度范围内。

因此,在选择匹配电容时,我们应尽量选择具有较高精度的电容,以满足晶振的要求。

3. 温度特性:晶振在工作过程中会受到温度的影响,而电容的特性也会随着温度的变化而发生变化。

因此,在选择匹配电容时,我们需要考虑其温度特性,选择具有较好温度稳定性的电容。

4. 封装形式:匹配电容的封装形式也是需要考虑的因素。

根据实际应用需求,我们可以选择贴片电容、插件电容等不同形式的电容进行匹配。

总结起来,匹配电容的选择需要综合考虑晶振的频率、电容的精度、温度特性和封装形式等因素。

合理的匹配电容设计可以确保晶振的稳定工作,提高电路的性能和可靠性。

需要注意的是,不同的应用场景可能对匹配电容的要求有所差异,因此在实际应用中,我们还需要根据具体情况进行合理的选择和调试。

同时,为了确保匹配电容的质量和可靠性,我们应选择具有良好声誉和品质保证的厂家提供的电容产品。

为何在晶振两端并上由两个小的电容串联的呢

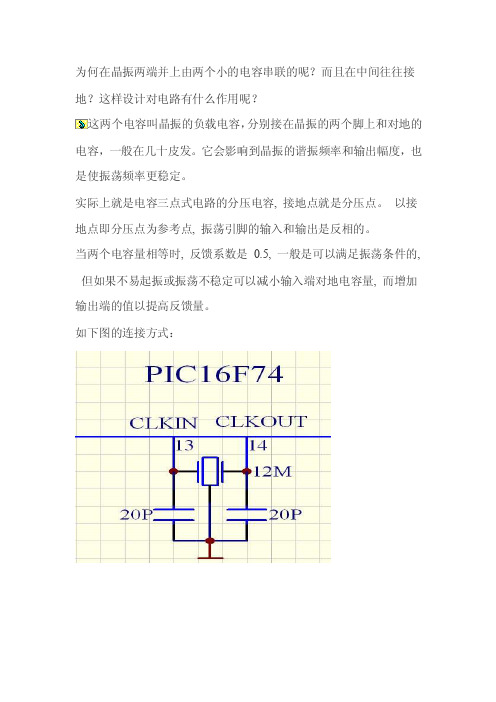

为何在晶振两端并上由两个小的电容串联的呢?而且在中间往往接地?这样设计对电路有什么作用呢?这两个电容叫晶振的负载电容,分别接在晶振的两个脚上和对地的电容,一般在几十皮发。

它会影响到晶振的谐振频率和输出幅度,也是使振荡频率更稳定。

实际上就是电容三点式电路的分压电容, 接地点就是分压点。

以接地点即分压点为参考点, 振荡引脚的输入和输出是反相的。

当两个电容量相等时, 反馈系数是0.5, 一般是可以满足振荡条件的,但如果不易起振或振荡不稳定可以减小输入端对地电容量, 而增加输出端的值以提高反馈量。

如下图的连接方式:外接时大约是数pf到数十pf,依频率和石英晶体的特性而定,需要注意的是这两个串联的值是并联在谐振回路上的,会影响振荡频率。

当两个电容量相等时,反馈系数时0.5,一般是可以满足谐振条件的,但如果不易起振或振荡不稳定可以减小输入端对地电容量, 而增加输出端的值以提高反馈量。

设计考虑事项:1.使晶振,外部电容与IC之间的信号尽可能的保持最短。

当非常低的电流流过IC晶振振荡器时,如果线路太长,会使它对EMC.ESD与串扰产生非常敏感的影响,而且长线路还会给振荡器增加寄生电容。

2.尽可能将其他时钟线路与频繁切换的信号线路布置在远离晶振连接的位置。

3.当心晶振和地的走线4.将晶振外壳接地如果实际的负载电容配置不当,第一会引起线路参考频率的误差,另外如在发射接收电路上会使晶振的震荡幅度下降(不在峰点),影响混频信号的信号强度与信噪。

当波形出现削峰,畸变时,可增加负载电阻调整。

(几十K到几百K),要稳定波形是并联一个1M左右的反馈电阻。

晶振是晶体振荡器的简称,在电气上它可以等效成一个电容和一个电阻并联再串联一个电容的二端网络,电工学上这个网络有两个谐振点,以频率的高低分其中较低的频率是串联谐振,较高的频率是并联谐振。

由于晶体自身的特性致使这两个频率的距离相当的接近,在这个极窄的频率范围内,晶振等效为一个电感,所以只要晶振的两端并联上合适的电容它就会组成并联谐振电路。

晶振与匹配电容的总结

晶振与匹配电容的总结 Document number:PBGCG-0857-BTDO-0089-PTT1998匹配电容-----负载电容是指晶振要正常震荡所需要的电容。

一般外接电容,是为了使晶振两端的等效电容等于或接近负载电容。

要求高的场合还要考虑ic输入端的对地电容。

一般晶振两端所接电容是所要求的负载电容的两倍。

这样并联起来就接近负载电容了。

2.负载电容是指在电路中跨接晶体两端的总的外界有效电容。

他是一个测试条件,也是一个使用条件。

应用时一般在给出负载电容值附近调整可以得到精确频率。

此电容的大小主要影响负载谐振频率和等效负载谐振电阻。

3.一般情况下,增大负载电容会使振荡频率下降,而减小负载电容会使振荡频率升高4.负载电容是指晶振的两条引线连接IC块内部及外部所有有效电容之和,可看作晶振片在电路中串接电容。

负载频率不同决定振荡器的振荡频率不同。

标称频率相同的晶振,负载电容不一定相同。

因为石英晶体振荡器有两个谐振频率,一个是串联揩振晶振的低负载电容晶振:另一个为并联揩振晶振的高负载电容晶振。

所以,标称频率相同的晶振互换时还必须要求负载电容一至,不能冒然互换,否则会造成电器工作不正常。

一份电路在其输出端串接了一个22K的电阻,在其输出端和输入端之间接了一个10M的电阻,这是由于连接晶振的芯片端内部是一个线性运算放大器,将输入进行反向180度输出,晶振处的负载电容电阻组成的网络提供另外180度的相移,整个环路的相移360度,满足振荡的相位条件,同时还要求闭环增益大于等于1,晶体才正常工作。

晶振输入输出连接的电阻作用是产生负反馈,保证放大器工作在高增益的线性区,一般在M欧级,输出端的电阻与负载电容组成网络,提供180度相移,同时起到限流的作用,防止反向器输出对晶振过驱动,损坏晶振。

和晶振串联的电阻常用来预防晶振被过分驱动。

晶振过分驱动的后果是将逐渐损耗减少晶振的接触电镀,这将引起频率的上升,并导致晶振的早期失效,又可以讲drive level调整用。

晶振接电容

晶振接电容

晶振接电容是一种用于滤波的重要组件,可以有效地减少电路中出现的噪音和其他不同信号之间的干扰。

它是由晶振和电容两部分组成,电容是装在晶振背后的一个外壳内,通常由四个不同大小的电容组成,每个电容之间有一个连接线将它们连接起来。

晶振接电容能够提供一个稳定的相位,从而减少射频电路中信号的失真和抖动,从而使信号传输更可靠。

此外,它还能增加电路的信号/噪声比,使其在高质量的信号传输中发挥重要作用。

晶振接电容的另一个主要应用是过滤电路中的不需要的频率,这样可以提高信号的传输质量。

它能够过滤掉特定频率外的其他频率,从而提高传输信号的质量。

这就是晶振接电容的原理,它可以将多余的频率过滤掉,使传输信号变得更加纯净,从而使信号的测量更加准确。

总之,晶振接电容是一种用于滤波的重要组件,它可以有效地抑制噪音和干扰信号,为电路的运行提供一个稳定的电场,使信号的传输质量得以提高。

此外,它也可以用于过滤不需要的频率,从而更有效地减少抖动,增加信号/噪声比,使信号变得更加纯净,从而提高测量准确度。

晶振的匹配电容

在某些情况下,也可以通过调整这两个电容的大小来微调振荡频率,当然可调范围一般在10ppm量级。

晶振的稳定性是产品的内在品质,与匹配电容无关(当然电容的稳定性不好是另一个问题)。匹配电容决定了晶振的运行精度。在晶振的产品参数中,有一项是负载电容CL,匹配电容的选择与它有关。例如你选的两个匹配电容都是20p,电路衍生电容为2.5p,则有CL=20×20/(20+20)+2.5=12.5p。你应选CL为12.5p的晶振。

晶振和普通的振荡器起振原理一样,要满足:1增益足够大;2正反馈回路;3相位2npai;

晶体的负载电容要和振荡电路匹配,只有负载电容和振荡电路的等效负载电容相等时,振荡电路输出的频率才和晶体频率一致。

如果晶体负载电容偏大,得到的振荡输出频率则会低于晶体的频率,反之则高于晶体频率。

单片机晶振旁的2个电容是晶体的匹配电容,只有在外部所接电容为匹配电容的情况下,振荡频率才能保证在标称频率附近的误差范围内。

晶振接电容

晶振接电容

晶振接电容就是把一个电容连接到一个晶体振荡器上,以调整其

频率。

一般来说,晶体振荡器有两个基本参数:谐振频率和谐振Q值。

其中谐振频率是振荡器给出的振荡频率,而谐振Q值是振荡器能量转

换的效率,即振荡器输出所受到的衰减的程度。

晶振接电容的作用是调节晶体振荡器的谐振频率和谐振Q值。

通

常情况下,当电化学电容接入晶体振荡器时,其谐振频率会发生调整。

根据所选择的电容值,分别可以调节谐振频率和谐振Q值。

如果电容

值大,则谐振频率会降低;如果电容值少,则谐振频率会升高。

此外,同一电容值接入不同的晶体振荡器,可能会影响晶体振荡

器的工作特性,因此在接电容之前,应该研究晶体振荡器的工作原理,以便选择最佳的电容值。

此外,应注意电容接入晶体振荡器后,其稳

定频率和谐振Q值也会发生变化,因此应根据实际应用确定电容值。

在安装晶振接电容时,有必要注意电容的接触方式,以免影响晶

体振荡器的谐振特性。

此外,由于电容本身会吸收一定的电量,如果

撞击过猛,电容也可能损坏,因此,安装晶振接电容时,应该尽量避

免撞击或抖动电容。

另外,施工前要先检查晶体振荡器的电流强度,

以免损坏晶体振荡器。

以上就是晶振接电容的大致内容,希望能帮助到你。

晶振 匹配电容

晶振匹配电容晶振是一种非常常见的电子元件,它在电路中起到产生稳定的时钟信号的作用。

而匹配电容则是在晶振电路中常用的元件之一,它的作用是调整晶振的频率,使其能够工作在预期的频率范围内。

本文将从晶振的工作原理、匹配电容的选择和调试等方面进行介绍,帮助读者更好地理解和应用晶振和匹配电容。

一、晶振的工作原理晶振是一种利用晶体的谐振特性产生稳定时钟信号的元件。

晶体的晶格结构具有谐振频率,当施加外加电场时,晶体会发生压电效应,从而使晶体发生机械振动。

而晶体的机械振动又会产生电场效应,使晶体产生电压信号。

当外加电场的频率等于晶体的谐振频率时,晶体会产生最大的电压信号,这就是晶振的工作原理。

二、匹配电容的选择匹配电容是用来调整晶振的频率的元件,它的值决定了晶振的谐振频率。

匹配电容的选择需要根据晶振的规格参数来确定。

通常晶振的规格参数中会标明所需的匹配电容范围。

在选择匹配电容时,应该优先选择与晶振规格参数相匹配的电容值,以确保晶振能够正常工作。

三、匹配电容的调试当晶振电路中的匹配电容选择好之后,还需要进行调试。

调试过程中,可以通过改变匹配电容的值来调整晶振的频率,以满足实际应用的需要。

调试时可以采用示波器等测量工具来观察晶振的输出信号,并根据实际需求来调整匹配电容的值。

调试时应该逐步调整,每次调整后都观察输出信号的变化,直到满足要求为止。

四、晶振和匹配电容的应用晶振广泛应用于各种电子设备中,例如计算机、手机、电视等。

在这些设备中,晶振起到产生稳定的时钟信号的作用,确保设备能够正常工作。

匹配电容则是晶振电路中的重要组成部分,它的选择和调试对于晶振的性能和稳定性至关重要。

总结:晶振是一种产生稳定时钟信号的元件,而匹配电容则是晶振电路中常用的元件之一,它的作用是调整晶振的频率。

本文从晶振的工作原理、匹配电容的选择和调试等方面进行了介绍。

希望通过本文的阐述,读者能够更好地理解和应用晶振和匹配电容,为电子设备的设计和维修提供帮助。

晶振匹配电容计算公式

晶振匹配电容计算公式

1 晶振匹配电容

晶振是电子设备中常用的外部元件,用于提供时钟信号,其安装往往需要校正环境参数,从而满足设备的要求。

晶振匹配电容是一种电容工具,通常和晶振共同使用,以确保晶振正常使用。

晶振匹配电容是一种消耗型电容,有很好的共振特性,可以帮助改善晶振产生的信号,为电子系统提供高质量的时钟信号。

2 计算公式

晶振匹配电容的计算公式为:C=1/4π²f²L ,其中,C为匹配电容值(单位:F),f为晶振振荡频率(单位:Hz),L为晶振电感(单位:H)。

一般情况下,晶振振荡频率为20MHz或以上,计算出的匹配电容值应大于10pF,且越大越好,建议电容值以50pF为最佳。

此外,为了避免发生次谐振,建议上源点和下源点电容分别采用不同的电容值,其差值则为实际值。

3 共振调谐

因为要求晶振的时钟精度必须极高,因此必须调节电路元件,较低频率晶振下需要有2个电容(上源点和下源点),用于改变电路阻抗,从而调节共振频率。

如果晶体管赋予极大的负阻抗,晶振上源点

和下源点电容分别应调节到正好可以抵消晶体管对共振频率的影响,

从而精确维护晶振的振荡频率。

4 综上

需要使用晶振匹配电容的电子系统,电容的选择和振荡频率有直

接的关系,其计算公式为:C=1/4π²f²L。

仔细调节源点电容,以避免

发生次谐振,将可以极大提高晶振的性能,从而确保系统不出现故障。

有源晶振的负载电容

有源晶振的负载电容

有源晶振的负载电容是指在使用有源晶振时,需要连接一个电容器来作为负载。

这个电容器的作用是为有源晶振提供一个稳定的负载,以确保晶振的稳定性和精度。

一、有源晶振的基本原理

有源晶振是一种基于晶体管的振荡器,它利用晶体管的放大特性和反馈电路来产生稳定的振荡信号。

有源晶振的输出信号是一个正弦波,其频率由晶振的谐振频率决定。

二、有源晶振的负载电容的作用

有源晶振的负载电容是为了提供一个稳定的负载,以确保晶振的稳定性和精度。

晶振的谐振频率与晶振的物理结构有关,而晶振的物理结构又与晶振的封装形式有关。

因此,不同封装形式的晶振需要不同的负载电容。

三、如何选择有源晶振的负载电容

选择有源晶振的负载电容需要考虑多个因素,包括晶振的封装形式、晶振的频率、负载电容的容值等。

通常,晶振的封装形式和频率可以在晶振的规格书中找到,

而负载电容的容值则可以通过试验或计算得出。

在选择负载电容时,需要注意以下几点:

1. 负载电容的容值应该与晶振的规格书中推荐的负载电容相匹配。

2. 如果没有规格书中的推荐值,可以根据晶振的频率和封装形式选择一个合适的负载电容。

3. 负载电容的容值应该尽可能接近推荐值,但不应该超过推荐值的两倍。

4. 如果负载电容的容值过小或过大,会导致晶振的频率偏移和振荡不稳定。

四、总结

有源晶振的负载电容是为了提供一个稳定的负载,以确保晶振的稳定性和精度。

选择负载电容需要考虑晶振的封装形式、频率和负载电容的容值等因素。

负载电容的容值应该尽可能接近推荐值,但不应该超过推荐值的两倍。

25m晶振匹配电容

25m晶振匹配电容摘要:一、引言二、25m 晶振简介1.什么是25m 晶振2.25m 晶振的应用领域三、25m 晶振匹配电容的作用1.电容的定义与性质2.匹配电容对25m 晶振的影响3.匹配电容的选择与计算四、25m 晶振匹配电容的类型及选择1.陶瓷电容2.钽电容3.薄膜电容4.选择匹配电容的注意事项五、25m 晶振匹配电容的故障及排查1.故障现象2.故障原因3.故障排查方法六、结论正文:【引言】25m 晶振是一种高精度、高稳定的晶体振荡器,广泛应用于通信、计算机、仪器仪表等领域。

为了确保25m 晶振的性能,匹配电容的选择与使用尤为重要。

本文将详细介绍25m 晶振匹配电容的相关知识。

【25m 晶振简介】25m 晶振,即25 兆赫兹晶体振荡器,其频率稳定度非常高,具有出色的抗干扰性能。

广泛应用于通信系统、全球定位系统(GPS)、卫星通信等领域。

【25m 晶振匹配电容的作用】在25m 晶振电路中,匹配电容起到关键作用。

电容对25m 晶振的性能影响很大,合适的匹配电容可以提高电路的稳定性和性能。

首先,电容的定义是储存电荷的能力,它的单位是法拉(F)。

电容的性质包括容量、耐压、温度系数等。

在25m 晶振电路中,匹配电容主要起到调整电路的截止频率和提高电路的稳定性作用。

【25m 晶振匹配电容的类型及选择】常见的25m 晶振匹配电容类型有陶瓷电容、钽电容和薄膜电容。

陶瓷电容具有体积小、容量精度高、稳定性好等特点,广泛应用于25m 晶振电路。

钽电容具有较高的耐压和稳定性,但体积较大,适用于对空间要求不高的场合。

薄膜电容体积小、耐压高,但容量精度相对较低。

选择匹配电容时,应根据实际应用场景和电路要求,综合考虑电容的容量、耐压、温度系数等因素。

【25m 晶振匹配电容的故障及排查】在实际应用中,25m 晶振匹配电容可能会出现故障,导致电路性能下降。

常见的故障现象包括电路工作不稳定、输出信号失真等。

针对这些故障,首先要分析故障原因,如电容损坏、电路设计不合理等。

24M晶振匹配电容计算

从模块24M 晶振(SMD3225-24MHz -7pF )电容匹配测试报告图 1.1 24M 晶振原理图 1测试PCB 板寄生电容如上图1.1,图中C1与C2为匹配电容,C3为测试使用表笔(5.6pf )。

通过频率计测试电路频率偏移,结合晶振T/S 值(T/S 值按20ppm/pf 计算),可计算出PCB 寄生电容。

使用频率计测试晶振电路频偏为-25.6ppm ,如下图1.2所示。

图 1.2 频率偏移频偏-25.6ppm 换算成电容为1.28pf 。

加入表笔后的频率影响,总电容为:pf C 14.52.8//2.86.5=+=)(总根据公式:L C C C C +=+总频偏寄生有:1.28pf 7pf 14.5+=+寄生C pf可算出寄生电容C 寄生:pf 14.3=寄生C2.根据寄生电容值进行匹配方案设计使用的晶振为24.000MHz,CL=7pf 。

根据C 寄生的取值,能够优化出以下几个备选方案:表 1不同匹配电容的备选方案可见方案B 串联后容值匹配效果较好。

已知匹配电容C1=C2=8.2pf ,表笔电容5.6pf ,晶振的T/S=20ppm/pf ,接下来可计算出实际的频率偏移。

使用表笔(5.6pf )测试出晶振电路频偏为-25.6ppm ,计算此时电路实配电容:14.52C 1C 2C 1C =++•+表笔表笔)(C C pf同时,计算不加表笔时匹配电容:pf C C 1.42//1=表笔令整个电路的匹配电容增加1.04pf ,即频偏增加了20.8ppm ,根据“电容容值越大,晶振电路频率越低”的原理,可得出电路未引入表笔时频偏为-4.8ppm 。

3. 测试方案B 的波形和特性阻抗。

图 1.3 方案B 芯片输入波形图 1.4 方案B芯片输出波形负阻抗测试,约1.5K欧姆时,不能正常抄表。

查规格书,等效电阻最大约为50欧姆,阻抗值为等效阻抗30倍,合理。

4.之前使用以下原理,未串入电阻,匹配电容10pf时输入存在明显过冲,输出波形畸变较为严重。

25m晶振匹配电容

25m晶振匹配电容

【实用版】

目录

1.25m 晶振匹配电容的概述

2.25m 晶振匹配电容的工作原理

3.25m 晶振匹配电容的应用领域

4.25m 晶振匹配电容的选型与安装

5.25m 晶振匹配电容的发展前景

正文

一、25m 晶振匹配电容的概述

25m 晶振匹配电容,顾名思义,是一种用于晶振电路中的电容,具有匹配晶振频率的作用。

晶振电路是数字电路、模拟电路、通信电路等各类电子电路中的核心部分,其稳定性和性能直接影响到整个系统的工作效果。

因此,选择合适的 25m 晶振匹配电容对于保证电路的稳定性和可靠性至

关重要。

二、25m 晶振匹配电容的工作原理

25m 晶振匹配电容的工作原理主要基于电容的频率响应特性。

晶振电路中的振荡频率会受到电路中电容、电感等元器件的影响。

通过选择合适的电容值和电容类型,可以实现对晶振频率的优化和调整,从而达到匹配电路的目的。

三、25m 晶振匹配电容的应用领域

25m 晶振匹配电容广泛应用于各类电子设备和系统中,如通信设备、计算机、智能家居、自动控制等领域。

在这些应用中,25m 晶振匹配电容主要起到稳定晶振频率、提高系统性能的作用。

四、25m 晶振匹配电容的选型与安装

在选择 25m 晶振匹配电容时,需要根据晶振电路的实际需求来确定电容的容值、额定电压、稳定性等参数。

在安装过程中,要注意电容的正确接线,以及与其他元器件之间的距离和布局,以保证电路的稳定性和可靠性。

五、25m 晶振匹配电容的发展前景

随着科技的不断发展,晶振电路在各类电子设备和系统中的应用越来越广泛,对 25m 晶振匹配电容的需求也日益增加。

8mhz晶振的匹配电容

8mhz晶振的匹配电容8MHz晶振是一种常用的时钟源,广泛应用于各种电子设备中。

为了确保晶振的稳定性和精确性,通常需要连接匹配电容。

匹配电容是指为了使晶振的谐振频率与其工作频率相匹配而添加的电容。

晶振的谐振频率与其电容值成反比关系,因此选择合适的匹配电容非常重要。

我们需要了解晶振的工作原理。

晶振是利用晶体的共振特性来产生稳定的时钟信号。

当施加外加电压时,晶体会发生机械振动,产生电荷。

当电荷积累到一定程度时,晶体会发生共振,产生稳定的振荡信号。

然而,晶振的谐振频率受到环境温度、供电电压等因素的影响,容易发生漂移。

为了解决这个问题,我们需要通过添加匹配电容来调整晶振的谐振频率,使其与工作频率相匹配。

具体来说,匹配电容通过改变晶振的等效电容值来调整谐振频率。

当晶振的谐振频率偏离工作频率时,可以通过增加或减小匹配电容的值来调整。

匹配电容的选择需要根据晶振的参数和工作条件来确定,一般可以在晶振的数据手册中找到相关的建议。

在确定匹配电容的值时,需要考虑晶振的等效电容和外部电路的等效电容之和。

晶振的等效电容包括晶体片上的电容和引脚之间的电容,而外部电路的等效电容包括PCB布线和其他连接元件的电容。

通过合理选择匹配电容的值,可以使晶振的谐振频率与工作频率相匹配,从而确保系统的稳定性和精确性。

需要注意的是,匹配电容的选择也受到其他因素的影响,如功耗、噪声等。

因此,在实际设计中,需要综合考虑这些因素,并进行合理的权衡。

匹配电容在晶振电路中起到了重要的作用,可以调整晶振的谐振频率,使其与工作频率相匹配。

通过合理选择匹配电容的值,可以提高系统的稳定性和精确性。

在实际设计中,需要综合考虑晶振的参数、工作条件以及其他因素,并进行合理的选择和调整。

晶振匹配电容快速计算

晶振匹配电容快速计算一、什么是晶振匹配电容在电子电路中,晶体振荡器(晶振)是一种能够产生稳定的高频振荡信号的元件。

为了使晶振能够正常工作,需要将其与电容器进行匹配,以达到最佳的振荡效果。

晶振匹配电容指的是与晶振共同工作的电容器。

二、晶振匹配电容的计算方法1. 确定晶振的额定频率(单位为赫兹)首先需要了解晶振的额定频率。

这通常可以在晶振的规格书或数据手册中找到。

假设晶振的额定频率为f。

2. 根据晶振的额定频率计算晶振的频率稳定度要求(单位为ppm)晶振的频率稳定度是指在一定温度范围内,晶振输出频率的变化范围。

一般情况下,晶振的频率稳定度要求在几十ppm以内。

假设晶振的频率稳定度要求为ppm。

3. 计算晶振的频率稳定度对应的频率变化范围(单位为赫兹)根据晶振的额定频率和频率稳定度要求,可以计算出晶振的频率变化范围。

计算公式为:频率变化范围 = 频率稳定度× 频率 / 10^6。

假设计算得到的频率变化范围为Δf。

4. 根据晶振的频率变化范围计算所需的匹配电容(单位为法拉)根据晶振的频率变化范围,可以计算出所需的匹配电容。

计算公式为:匹配电容= 1 / (2πf × Δf)。

假设计算得到的匹配电容为C。

5. 选择合适的标准电容值根据计算得到的匹配电容,可以选择最接近的标准电容值。

在选择标准电容值时,可以参考电容器的规格书或数据手册。

三、晶振匹配电容计算的实例假设我们有一个频率为10MHz的晶振,需要满足100ppm的频率稳定度要求。

根据计算公式,可以得到频率变化范围为10MHz × 100ppm / 10^6 = 1kHz。

根据匹配电容的计算公式,可以得到匹配电容为1 / (2π × 10MHz × 1kHz) = 7.96pF。

在实际选择标准电容值时,可以选择最接近的标准电容值,例如8pF的电容器。

四、总结晶振匹配电容的计算方法可以帮助我们选择合适的电容器,以满足晶振的频率稳定度要求。

晶振的匹配电容

12M配30P;24M配22P;大于33M的配5-15P及10K电阻。

一般的电路里晶振旁边都接了两个电容,是起什么作用的啊~~请教高手的指点啊~~~答 1:谐振组成振荡器电路谐振答 2:启振电容。

有空就翻几个老帖出来看看,里面应该有。

答 3:电容三点试振荡器的槽路电容,正反馈量由此两个电容分压决定答 4:负载电容用来纠正晶体的振荡频率用的答 5:re答 6:re 正说,是为了稳定振荡频率;俗说,就是劫持干扰。

电容与内部电路共同组成一定频率的振荡,这个电容是硬连接,固定频率能力很强,其他频率的干扰就很难进来了。

想起一个笑话,大概意思就是本飞机被我劫持了,其他劫持者等下次吧。

这个电容就是本次劫机者。

答 7:晶振电路其实是个电容三点式振荡电路,输出是正玄波晶体等效于电感,加两个槽路分压电容,输入端的电容越小,正反馈量越大。

答 8:负载电容每个晶振都会有的参数例如:稳定度是多少PPN 负载电容是多少PF 等。

当晶振接到震荡电路上在震荡电路所引入的电容不符合晶振的负载电容的容量要求时震荡电路所出的频率就会和晶振所标的频率不同例如:一个4.0000MHz +-20PPN 负载电容是16PF 的晶振当负载电容是10PF时震荡电路所出的频率就可能会是4.0003MHz当负载电容是20PF时震荡电路所出的频率就可能会是3.9997MHz晶振负载电容有2种接法 1 并联在晶振上 2 串联在晶振上第2种比较常用 2个脚都接一个电容对交流地在一些对频率精度要求高的电路上如PLL的基准等。

就是并多个可调电容来微调频率的如果对频率精度要求不高就用固定电容就行了晶振是晶体振荡器的简称,在电气上它可以等效成一个电容和一个电阻并联再串联一个电容的二端网络,电工学上这个网络有两个谐振点,以频率的高低分其中较低的频率是串联谐振,较高的频率是并联谐振。

由于晶体自身的特性致使这两个频率的距离相当的接近,在这个极窄的频率范围内,晶振等效为一个电感,所以只要晶振的两端并联上合适的电容它就会组成并联谐振电路。

晶振连接2个电容的作用

晶振连接2个电容的作用

晶振连接两个电容的作用是为了提供稳定的工作频率和稳定的输出信号。

晶振是一种电子元件,可以产生稳定的频率信号。

在晶振电路中,两个电容起到了滤波和稳定电压的作用。

具体来说,晶振电路中的两个电容分别连接在晶振的输入和输出端。

这样做的目的是通过电容的滤波作用,减小输入和输出信号中的噪声和干扰,使得晶振的工作频率更加稳定。

同时,电容还可以稳定晶振电路的电压,防止电压波动对晶振的工作产生影响。

连接两个电容可以提高晶振电路的稳定性和可靠性,确保晶振的输出频率准确无误。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

晶振和电容的匹配 /spec_pages/PNDescrpt/Load_Cap.htm 晶振 等效 于 电感/电容/内阻使用 VCXO (压控晶体振荡器)作为时钟(CLK)发生器 测量时可接出一段锡丝,锡丝上紧密缠绕十多匝线,形成天线感应,再用 counter 频率计用探头(可用示波器探头)测量。

其中 两个电容 C1、C2 通过地串联又与晶振并联,并与其他杂散电容并联。

一般选择 C1、C2 值要比其他杂散电容高 8~10 倍,来减少杂散电容影响。

一般 IC 引脚约 2~3pF,杂散电容 2~3pF Co(晶振内部电容)3~5pF 所有 Cl=C1 串 C2+IC+杂散+Co 即 Load capacitance :Cl 值fS = (Series) frequency =I2C BUS 很常用, 也常出问题, 所以我们通常要用 DIGITAL SCOPE 来观察它在出 状况前和出状况时的波形有无异样. 什么样的波形才算正确呢? 1) rise time 2) fall time 3) ack voltage 4) start condition 5) stop condition 6) 读的时候, ACK 从哪里来, 每个 BYTE 都要有? 最后一个 BYTE? 7) 写的时候, ACK 从哪里来, 每个 BYTE 都要有? 最后一个 BYTE? 8) repeated start condition 9) 9 个 CLK 的间隔必须一样吗?如何选用 Voltage Regulator? 似乎很简单, 提几个问题让大家考虑一下. 1)输出电流需要多大? 2)Dropout(压降)多大? 3)功耗多大? 4)采用哪一种 PAKAGE? 5)站立式的,要加 HEATSINK 吗? 多大的 HEATSINK 才够? 6)贴片式的, 要多大的铜片才够上热?7)PCB 所能承受的最高温度是多少? 8)如输入电压太高, REGULATOR 两端的压降太大而引起过热, 如何解决? 9) 多大的电流要求多宽的 COPPER TRACK? 10) 多大的电流要求多大的过孔?The table below gives rough guidelines of how wide to make a trace for a given amount of current. Trace Width [inches] 0.010 0.015 0.020 0.025 0.050 0.100 0.150 Trace Width [mm] 0.254 0.381 0.508 0.635 1.27 2.54 3.81 Current [A] 0.3 0.4 0.7 1.0 2.0 4.0 6.0Here is what I have used for years to calculate the current carrying capacity of a plated-thru hole. Find the circumference of the hole by multiplying the diameter x 3.141 this will give you the equivalent 1 Oz. trace width that can be used to find the current carrying capacity from the tables in IPC-D-275. Remember the copper in the hole is always 1 Oz. 1) Φ0.5 (diameter = 0.5mm) via Circumference of via = 0.5x3.14 = 1.57 mm 2) Φ0.3 (diameter = 0.3mm) via Circumference of via = 0.3x3.14 = 0.942 mm若用铜箔作为散热, 需要多大的面积? /Article/com/200511/791.html 1.系统要求: VOUT=5.0V;VIN(MAX)=9.0V;VIN(MIN)=5.6V;IOUT=700mA;运行周期=100%;T A=50℃ 根据上面的系统要求选择 750mA MIC2937A-5.0BU 稳压器,其参数为: VOUT=5V±2%(过热时的最坏情况) TJ MAX=125℃。

采用 TO-263 封装,θJC=3℃/W; θCS≈0℃/W(直接焊接在电路板上)。

2.初步计算: VOUT(MIN)=5V-5×2%=4.9V PD=(VIN(MAX)-VOUT(MIN))+IOUT+(VIN(MAX)×I)=[9V-4.9V]×700mA+(9V×15mA) =3W 温度上升的最大值, ΔT=TJ(MAX)-TA = 125℃-50℃=75℃;热阻 θJA(最坏情 况):ΔT/PD=75℃/3.0W=25℃/W。

散热器的热阻, θSA=θJA-(θJC+θCS);θSA=25-(3+0)=22℃/W(最大)。

3.决定散热器物理尺寸: 采用一个方形、单面、水平具有阻焊层的铜箔散热层与一个有黑色油性涂料覆盖 的散热铜箔,并采用 1.3 米/秒的空气散热的方案相比较,后者的散热效果最好。

采用实线方案,保守设计需要 5,000mm2 的散热铜箔,即 71mm×71mm(每边长 2. 8 英寸)的正方形。

4.采用 SO-8 和 SOT-223 封装的散热要求: 在下面的条件下计算散热面积大小:VOUT=5.0V;VIN(MAX)=14V;VIN(MIN)=5.6 V;IOUT=150mA;占空比=100%;TA=50℃。

在允许的条件下,电路板生产设备更 容易处理双列式 SO-8 封装的器件。

SO-8 能满足这个要求吗?采用 MIC2951-03B M(SO-8 封装),可以得到以下参数: TJ MAX=125℃;θJC≈100℃/W。

5.计算采用 SO-8 封装的参数: PD=[14V-5V]×150mA+(14V×8mA)=1.46W; 升高的温度=125℃-50℃=75℃; 热阻 θJA(最坏的情况):ΔT/PD=75℃/1.46W=51.3℃/W; θSA=51-100=-49℃/W(最大)。

显然,在没有致冷条件下,SO-8 不能满足设计要求。

考虑采用 SOT-223 封装的 M IC5201-5.0BS 调压器,该封装比 SO-8 小,但其三个引脚具有很好的散热效果。

选用 MIC5201-3.3BS,其相关参数如下: TJ MAX=125℃ SOT-223 的热阻 θJC=15℃/W θCS=0 ℃/W(直接焊在线路板上的) 。

6.计算采用 SOT-223 封装的结果: PD=[14V-4.9V]×150mA+(14V×1.5mA)=1.4W 上升温度=125℃-50℃=75℃; 热阻 θJA(最坏的情况): ΔT/PD=75℃/1.4W=54℃/W; θSA=54-15=39℃/W(最大)。

根据以上的数据,参考图 1,采用 1,400 mm2 的散 热铜箔(边长 1.5 英寸的正方形)可以满足设计要求。

以上的设计结果可以作为粗略的参考,实际设计中需要了解电路板的热特性,得 出更准确、满足实际设计的结果。

25. 新手应注意的问题 新手因为缺乏经验,在设计电路时考虑不周, 常常要等到装完样机之后, 才知道 电路不能工作, 要加电路, 要改板, 即浪费金钱, 又拖延时间. 每个 IC, 每个方案都有参考设计, 但我们大多时候没办法全部照抄, 而是要把 它们拼在一起, 实现我们所需要的功能, 所以 INTERFACE 的设计尤其重要. 常犯哪些错误? 要做哪些准备工作? 如何避免?1) 在参考样机里测量你所要用的那一部分电路的输入或输出信号的电平. 从而 决定你所需要的那一部分电路的输入电阻或负载. 如 CVBS 是 1V, 2V, 0.7V?2). LAYOUT, 元器件封装常犯错误. /forum/dispbbs.asp?boardID=3&ID=9682&page= 1 3) 3) 601 Interface 请注意以下几个问题: (1) Hsync 和 Vsync 的极性要求? (2) (3) Hsync 和 Vsync 的位置关系? Hsync 和 DATA 的位置关系?(4) HSYNC 和 CLOCK 的位置关系? (5) VSYNC 和 CLOCK 的位置关系? (6) DATA 和 CLOCK 的位置关系? (7) CLCOK 的特性要求? (8) 在 H-BLANKING 里是些什么 DATA? (9) HSYNC 的宽度要求? (10) 两个 HSYNC 的间隔? (11) VSYNC 的宽度要求? (12) 两个 VSYNC 的间隔?开发人员的几个常疏忽的问题点 开发人员的几个常疏忽的问题点 我的工作主要是主导新产品试产,在实际的工作中,经常出现因为 RD 人员的设计“疏忽”导致试产失败。

这个疏忽要加上引号,是因为这并不是真正的粗心造成的 ,而是对生产工艺的不熟悉而导致的。

为了避免各位做 RD 的朋友出现同样的错误, 或为了更好的完成试产我对一些常见的问题点做一些总结,希望能对大家有所帮助 。

1、IC 封装的选择。

现在电子产品都在向环保的无铅发展,欧洲 2006 年 7 月 1 日 就要实现全部无铅化,,现在正处于有铅向无铅的过渡期。

因此,元器件厂商提供 的元器件也出现无铅与有铅两种规格,有的厂商甚至已经停止了有铅元器件的生产 。

问题点就在于这有铅和无铅两种元器件的选择上,当一个产品设计完成后,RD 人员需要对具体元器件进行确认,请在确认前要做出该产品采用无铅工艺还是有铅 工艺的选择。

如果没有一个具体的确定,在选料时不注意这个问题,原料中出现有 铅元件与无铅元件同时使用,就会导致 SMT 工艺的困难。

无铅元件的回流峰值温度在 255 度,有铅元件的回流峰值温度最高不超过 235 度 ,如果混用两种材料,那么必然会导致 1、有铅元件被高温损坏。

2、无铅元件,特 别是 BGA 封装的元件,所附锡球未达到熔点,易导致虚焊或抗疲劳度下降。

所以在 确定元器件的时候一定要首先确认元器件是有铅的还是无铅的,同时如果元器件选 择无铅,那么 PCB 板也要做相应选择,一个方面配合无铅工艺,让无铅锡膏的焊接 性得到加强,另一方面应用于有铅制程的 PCB 板也无法承受过高的温度,易造成板 翘等不良现象。