verilog定点数转浮点数

上海大学verilog设计32位浮点加法器设计

32位浮点加法器设计摘要:浮点数具有数值范围大,表示格式不受限制的特点,因此浮点数的应用是非常广泛的。

浮点数加法运算比较复杂,算法很多,但是为了提高运算速度,大部分均是基于流水线的设计结构。

本文介绍了基于IEE754标准的用Verilog 语言设计的32位浮点加法器,能够实现32位浮点数的加法运算。

虽然未采用流水线的设计结构但是仍然对流水线结构做了比较详细的介绍。

关键字:浮点数,流水线,32位浮点数加法运算,Verilog 语言设计32-bit floating point adder designCao Chi,Shen Jia- qi,Zheng Yun-jia(School of Mechatronic Engineering and Automation, Shanghai University, Shanghai ,China ) Abstract://沈佳琪搞定Key words :float; Assembly line; 32-bit floating-point adder 浮点数的应用非常广泛,无论是在计算机还是微处理器中都离不开浮点数。

但是浮点数的加法运算规则比较复杂不易理解掌握,而且按照传统的运算方法,运算速度较慢。

因此,浮点加法器的设计采用了流水线的设计方法。

32位浮点数运算的摄入处理采用了IEE754标准的“0舍1入”法。

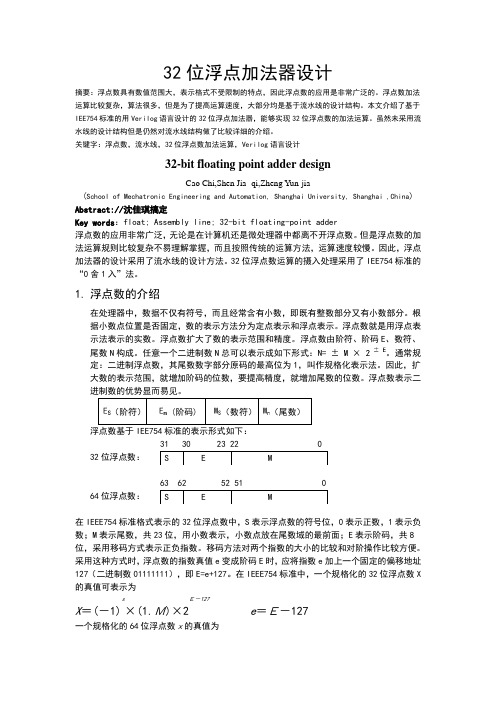

1. 浮点数的介绍在处理器中,数据不仅有符号,而且经常含有小数,即既有整数部分又有小数部分。

根据小数点位置是否固定,数的表示方法分为定点表示和浮点表示。

浮点数就是用浮点表示法表示的实数。

浮点数扩大了数的表示范围和精度。

浮点数由阶符、阶码E 、数符、尾数N 构成。

任意一个二进制数N 总可以表示成如下形式:N=。

通常规定:二进制浮点数,其尾数数字部分原码的最高位为1,叫作规格化表示法。

因此,扩大数的表示范围,就增加阶码的位数,要提高精度,就增加尾数的位数。

verilog 实数转换函数

verilog 实数转换函数Verilog实数转换函数Verilog是一种硬件描述语言,用于描述数字电路的结构和行为。

在Verilog中,对于实数的处理是非常重要的。

实数转换函数是一种在Verilog中用于将实数转换为其他数据类型的函数。

本文将介绍Verilog中常用的实数转换函数,并详细讨论它们的功能和使用方法。

一、实数转整数函数在Verilog中,实数转整数函数可以将实数转换为整数数据类型。

Verilog提供了几种不同的实数转整数函数,包括$floor、$ceil、$round、$trunc等。

这些函数的功能如下:1. $floor函数:返回小于或等于实数的最大整数。

2. $ceil函数:返回大于或等于实数的最小整数。

3. $round函数:返回四舍五入后的整数。

4. $trunc函数:返回实数的整数部分。

这些函数在实现数字电路时非常有用。

例如,当需要将实数作为地址输入到存储器中时,可以使用$floor函数将实数转换为最接近的整数,以确保地址的正确性。

二、实数转浮点数函数除了将实数转换为整数,Verilog还提供了将实数转换为浮点数的函数。

这些函数包括$bitstoreal、$itor、$rtoi等。

1. $bitstoreal函数:将二进制位转换为实数。

该函数的输入是一个包含二进制位的变量或寄存器,输出是对应的实数。

2. $itor函数:将整数转换为实数。

该函数的输入是整数类型的变量或寄存器,输出是对应的实数。

3. $rtoi函数:将实数转换为整数。

该函数的输入是实数类型的变量或寄存器,输出是对应的整数。

这些函数在进行数值计算时非常有用。

例如,在进行浮点数乘法时,可以使用$bitstoreal函数将二进制位转换为实数,进行乘法计算,然后使用$rtoi函数将结果转换为整数。

三、实数转字符串函数在某些情况下,需要将实数转换为字符串进行输出或显示。

Verilog 提供了$realtime函数来实现这一功能。

verilog 浮点数定点化

verilog 浮点数定点化

Verilog中不存在浮点数数据类型,只能通过定点数来模拟浮点数的

运算。

定点数是使用固定数量的整数位和小数位来表示实数的一种方法。

例如,在一个定点数中,如果我们规定有4个整数位和4个小数位,那么这

个数就可以表示为$0000.0000$到$1111.1111$(十进制中的0到15.9375)之间的任何一个实数。

定点数的加减法可以直接进行,而乘法和除法则需要额外的处理。

在Verilog中,我们可以使用shift、concatenate等操作符来实现定点数

的运算。

例如,下面是一个简单的定点数乘法的Verilog实现:```。

module fixed_point_multiply(input [7:0] a, input [7:0] b, output reg [15:0] result);。

result = {a, 8'b0} * {b, 8'b0};。

end。

endmodule。

```。

在这个例子中,输入的a和b都是带符号的8位整数,我们把它们扩

展为16位的定点数,然后使用乘法操作符*进行乘法运算。

这里需要注意的是,定点数的表示要考虑到数据精度的问题。

如果我们希望表示的数在小数部分有更高的精度,就需要增加小数位的数量。

但是这样会增加数据宽度,也会增加计算的复杂度。

因此,定点数的设计需要根据具体应用的需求进行权衡和调整。

verilog 浮点运算

verilog 浮点运算Verilog是一种硬件描述语言,用于设计数字电路。

在Verilog 中,浮点运算主要涉及到定点数和浮点数之间的转换。

以下是一些关于Verilog浮点运算的基本知识:1. 固定点数(Fixed Point Numbers):在Verilog中,固定点数是一种特殊的数据类型,它表示一个有固定位数的整数。

固定点数的优点是计算速度快,因为所有的算术运算都是在固定点数上进行的。

然而,固定点数的缺点是精度较低,因为每个位都有一定的误差。

2. 浮点数(Floating Point Numbers):浮点数是一种更精确的数据类型,它表示一个实数。

在Verilog中,浮点数通常使用IEEE 754标准来表示。

浮点数的优点是精度较高,但计算速度较慢,因为大多数算术运算都是在浮点数上进行的。

3. Verilog中的浮点运算:在Verilog中,可以使用内置的浮点运算函数来进行浮点数运算。

例如,可以使用`$realtobits`函数将实数转换为固定点数,然后使用`$bitstoreal`函数将固定点数转换回实数。

此外,还可以使用`$itor`和`$bitstoreal`函数进行整数到浮点数的转换。

以下是一个简单的示例,演示了如何在Verilog中进行浮点数加法:verilogmodule float_addition (input wire clk,input wire reset,input wire [31:0] a, // 输入浮点数ainput wire [31:0] b, // 输入浮点数boutput wire [31:0] result // 输出浮点数结果);reg [31:0] a_fixed; // 存储固定点数形式的areg [31:0] b_fixed; // 存储固定点数形式的breg [31:0] result_fixed; // 存储固定点数形式的结果// 将浮点数a转换为固定点数形式assign a_fixed = $realtobits(a);// 将浮点数b转换为固定点数形式assign b_fixed = $realtobits(b);// 对固定点数形式的a和b进行加法运算assign result_fixed = a_fixed + b_fixed;// 将固定点数形式的结果转换回浮点数形式assign result = $bitstoreal(result_fixed);endmodule在这个示例中,我们首先使用`$realtobits`函数将浮点数a和b转换为固定点数形式,然后对它们进行加法运算,最后使用`$bitstoreal`函数将固定点数形式的结果转换回浮点数形式。

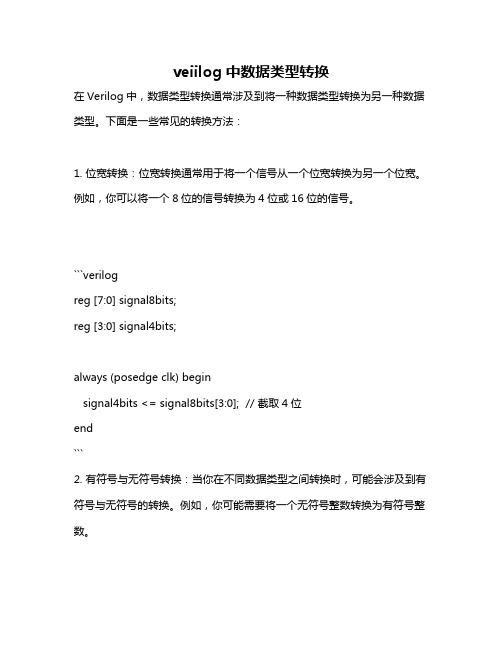

veiilog中数据类型转换

veiilog中数据类型转换在Verilog中,数据类型转换通常涉及到将一种数据类型转换为另一种数据类型。

下面是一些常见的转换方法:1. 位宽转换:位宽转换通常用于将一个信号从一个位宽转换为另一个位宽。

例如,你可以将一个8位的信号转换为4位或16位的信号。

```verilogreg [7:0] signal8bits;reg [3:0] signal4bits;always (posedge clk) beginsignal4bits <= signal8bits[3:0]; // 截取4位end```2. 有符号与无符号转换:当你在不同数据类型之间转换时,可能会涉及到有符号与无符号的转换。

例如,你可能需要将一个无符号整数转换为有符号整数。

```verilogreg [7:0] unsigned_num;reg signed_num;always (posedge clk) beginsigned_num <= signed'(unsigned_num); // 转换有符号整数end```3. 定点数与整数之间的转换:在数字信号处理和通信中,经常需要将定点数转换为整数或反之。

这通常涉及到移位和缩放操作。

4. 强制类型转换:你可以使用`<类型名称>`来强制类型转换。

例如,如果你想将一个无符号整数转换为有符号整数,你可以这样做:```verilogreg [7:0] unsigned_num;reg signed_num;always (posedge clk) beginsigned_num <= <signed> unsigned_num; // 强制类型转换end```5. 使用内置函数进行转换:Verilog也提供了一些内置函数来进行数据类型转换,如`$signed`和`$unsigned`。

这些函数可以用于将一个信号转换为有符号或无符号版本。

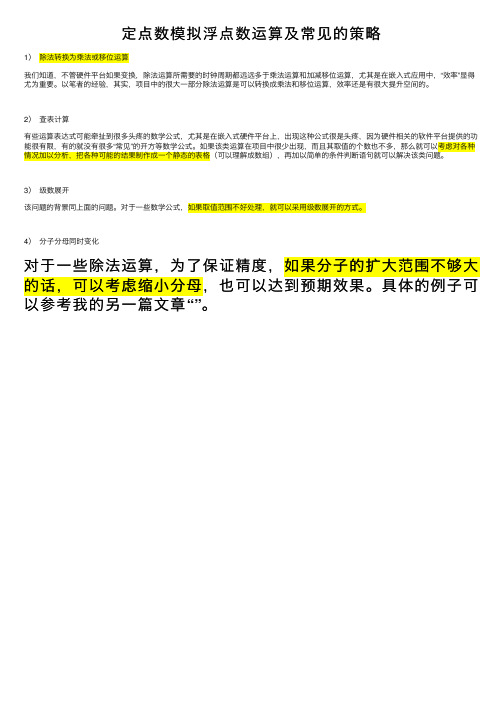

定点数模拟浮点数运算及常见的策略

定点数模拟浮点数运算及常见的策略

1)除法转换为乘法或移位运算

我们知道,不管硬件平台如果变换,除法运算所需要的时钟周期都远远多于乘法运算和加减移位运算,尤其是在嵌⼊式应⽤中,“效率”显得尤为重要。

以笔者的经验,其实,项⽬中的很⼤⼀部分除法运算是可以转换成乘法和移位运算,效率还是有很⼤提升空间的。

2)查表计算

有些运算表达式可能牵扯到很多头疼的数学公式,尤其是在嵌⼊式硬件平台上,出现这种公式很是头疼,因为硬件相关的软件平台提供的功能很有限,有的就没有很多“常见”的开⽅等数学公式。

如果该类运算在项⽬中很少出现,⽽且其取值的个数也不多,那么就可以考虑对各种情况加以分析,把各种可能的结果制作成⼀个静态的表格(可以理解成数组),再加以简单的条件判断语句就可以解决该类问题。

3)级数展开

该问题的背景同上⾯的问题。

对于⼀些数学公式,如果取值范围不好处理,就可以采⽤级数展开的⽅式。

4)分⼦分母同时变化

对于⼀些除法运算,为了保证精度,如果分⼦的扩⼤范围不够⼤

如果分⼦的扩⼤范围不够⼤对于⼀些除法运算,为了保证精度,

,也可以达到预期效果。

具体的例⼦可的话,可以考虑缩⼩分母,也可以达到预期效果。

具体的例⼦可的话,可以考虑缩⼩分母

以参考我的另⼀篇⽂章“”。

第3讲 定点运算及浮点运算汇总

结果超过16位的定点加法

例子: 设x=15000,y=20000,则浮点运算结果为z

=x+y=15000+20000=35000,显然z>32767; Qx=1,Qy=0,Qz=0,则定点加法为: x=30000;y=20000; temp=20000<<1=40000; temp=temp+x=40000+30000=70000; z=70000L>>1=35000;

除法运算的C语言定点模拟

z = x/y

zq 2Qz=

xq 2Qx yq 2Qy

zq

xq

2(Qz Qx Qy ) yq

float x,y,z; z = x/y;

int x,y,z;

long temp;

temp = (long)x;

z = (temp<<(Qz-Qx+Qy))/y;

定点除法

0010000000000000

小数点的位置

浮点数与定点数的转换关系

浮点数转换为定点数

xq int x 2Q

定点数转换为浮点数

x floatxq 2Q

浮点数 x=0.5,定标 Q=15, 则定点数=0.5*32768=16384

Q表示 Q15 Q14

. . . . . .

Q1 Q0

DSP芯片的数以2的补码形式表示 数的定标:“小数点” 的位置 Q表示法和S表示法 对定点数而言,数值范围与精度是一对矛盾,一 个变量要想能够表示比较大的数值范围,必须以 牺牲精度为代价。

Q表示法16进制数2000H

Q0表示为8192

0010000000000000

符

号 位 Q15表示为0.25

verilog中浮点数的表示以及浮点数除法IP核的使用

Verilog中的浮点数的表示以及浮点数除法IP核的用法初学FPGA,最近用到除法,刚开始想要自己写一段除法的代码来解决,和好多菜鸟一样先去网上输入“verilog除法器”去搜索,搜到了一些代码,但是这些代码都是:分子除以分母得到的结果是商和余数。

例如10除以5商2余0,这个还好,因为可以整除。

如果是11除以5商2余1,可是我想得到的结果是2.2。

继续在网上找,还是没有找到。

后来听从大神指点试试Verilog自带的除法IP核,于是就去找IP核。

马上就要切入正题了,在此先介绍一下本人的背景,主要是增强大家学习FPGA的信心。

本人本科学的是物理学,硕士学的是光学,大学期间对电脑的认识就是计算机二级的水平,本科毕业论文用了一点MATLAB,可以说对于编程完全空白,对于数电中的二极管,三极管,触发器都只停留在知道名字上。

对于二进制,十六进制,浮点,整型都没有概念。

硕士也就用过LabVIEW。

就是这样的基础来学FPGA的,介绍这么一堆,是因为以前看帖子时经常会看到发帖的人会默认读者懂数电,懂模电,懂进制,懂单片机,懂各种协议,懂一切工科的基础知识。

但是问题来了,对于我这种理科生,啥也不懂,怎么办,回答问题的人当然会说:不懂就自己去看呗,谁能把所有的东西都告诉你。

事实确实是这样的,什么问题都要自己去解决,但是我想说如果解答者能站在提问者的角度去回答,那么双方都会获益匪浅的,能知道提问者问的是什么并站在提问者的角度去回答对于解答者是一个很高的要求。

当然提问者也要懂得独立思考,不要什么都去问,先自己查做好准备再提问,这样才能够提出准确,高效的问题。

解答者也乐意解答。

下面我们切入正题:首先我们把要处理的数据分成两类:整型和浮点型,通俗的说就是整数和小数。

我们用这两种数做除法得到的结果无非两种,整除和不能整除,对应的商就是整数和小数。

在此我对除法的编程代码原理不做介绍,只介绍如何调用IP核,对于除法结果为商和余数的代码在网上可以找到,大家可以自己看。

FPGA浮点数定点数的处理

FPGA浮点数定点数的处理/justlxy/p/5100053166⼤佬博客,讲的⾮常有条理的1,基础知识(1)定点数的基础认知:⾸先例如⼀个16位的数表⽰的定点数的范围是:(MAX:16‘d32767 MIN: -32767#2^15-1#’)最⾼位符号位,三位整数位,其余的12位是⼩数位的话,那么它的精度有⼩数部分决定:1/4096=0.024*******可表⽰数的范围为:(0.024********4095)=0.999755859375,然后加上整数的最⼤表⽰值7,即极限最⼤值为7.999755859375。

(2)浮点数的认知浮点数就是指整数和⼩数位数不确定的数字的表达,实际上采⽤的就是咱们常⽤的科学计数法。

如1.23*10^2采⽤的是基数(10),指数(2),尾数(1.23)以及⼀个符号位来表⽰。

这⾥实际上是采⽤指数⽅法实现了⼩数点的浮动。

在 IEEE 标准中,浮点数是将特定长度的连续字节的所有⼆进制位分割为特定宽度的符号域,指数域和尾数域三个域,其中保存的值分别⽤于表⽰给定⼆进制浮点数中的符号,指数和尾数。

这样,通过尾数和可以调节的指数(所以称为"浮点")就可以表达给定的数值了。

具体的格式参见下⾯的图例:上图中可以看出S表⽰符号位,EXponent表⽰指数位,也就是“浮动”的指数位,指数的范围在32位的系统中(0-2^8 -1)/2 也就是0-127,在double型位2^11位浮动指数。

2.FPGA浮点数的定点化⾸先明确输⼊的浮点数是什么格式的:其次明⽩要输出的定点数⼜是怎样的,最后两者之间的转换也就明了了:输⼊的浮点数是::f[31:0]表⽰⼀个单精度32位浮点数,f[31]是符号位,其为‘0’表⽰正数、为‘1’表⽰负数;f[30:23]这8位为指数位,为了能表⽰负指数,将在实际指数的基础上加上127得到的结果存⼊f[30:23];f[22:0]表⽰⼩数位(尾数),类似科学计数法,不过采⽤了省略整数位(2进制的科学计数法整数位必定是1)1。

verilog十进制数转化为浮点数代码完整

很高兴接到您的任务要求,让我为您撰写一篇关于verilog十进制数转化为浮点数代码完整的文章。

让我们先来了解一下verilog中十进制数和浮点数的概念。

在verilog中,十进制数是一种常见的数据类型,通常用于表示整数。

而浮点数则是一种用于表示带有小数部分的数值的数据类型。

在实际应用中,很多时候我们需要将十进制数转化为浮点数,这涉及到了一定的代码实现。

要实现verilog中十进制数转化为浮点数的代码,首先需要了解浮点数的表示方法。

在IEEE 754标准中,浮点数由三个部分组成:符号位、指数和尾数。

根据这一表示方法,我们可以使用一定的算法来实现十进制数到浮点数的转化。

一般来说,将十进制数转化为浮点数的算法可以分为以下几个步骤:1. 确定符号位:根据十进制数的正负确定浮点数的符号位。

2. 将十进制数转化为二进制形式:采用适当的算法将十进制数转化为二进制形式。

3. 确定指数和尾数:根据转化得到的二进制形式,确定浮点数的指数和尾数部分。

4. 将三个部分组合成最终的浮点数。

在具体的verilog代码实现中,可以根据这一算法进行相应的逻辑设计。

通过合理的模块划分和逻辑实现,我们可以编写出完整的代码来实现十进制数到浮点数的转化。

verilog中十进制数转化为浮点数的代码实现,需要我们熟悉浮点数的表示方法和相应的转化算法,并通过适当的逻辑设计和代码编写来实现这一功能。

通过深入的研究和实践,我们可以掌握这一重要的技能,为verilog编程添加新的可能性。

个人观点和理解:在实际的verilog编程中,对于浮点数的处理往往具有重要的意义。

通过将十进制数转化为浮点数,我们可以更加灵活的处理数据,并实现更加复杂的功能。

对于这一问题的研究和实践具有重要的意义,可以帮助我们更好地应用verilog语言,实现更加丰富和高效的功能。

希望通过我的文章,您能对verilog中十进制数转化为浮点数的代码实现有更加全面、深刻和灵活的理解。

verilog浮点数运算

verilog浮点数运算

Verilog 是一种硬件描述语言 HDL),通常用于描述数字电路和硬件设计,而不是用于进行浮点数运算。

在 Verilog 中,并不直接支持浮点数运算,而是侧重于整数运算和位级操作。

如果需要进行浮点数运算,可以考虑以下几种方法:

1. 使用定点数

定点数是一种在数字电路中常用的数值表示方法,它使用整数来表示小数部分。

通过使用固定的小数点位置,可以模拟浮点数的运算。

例如,可以将小数部分的位数作为一个固定的小数点位数。

2. 使用专用的 IP 核或库

有一些专门的 IP 核或者库可以在 FPGA 或 ASIC 设计中实现浮点数运算。

这些 IP 核通常是针对特定的浮点数标准 例如 IEEE 754)设计的。

3. 使用 FPGA 高级综合工具

一些现代的FPGA 设计工具例如Vivado High-Level Synthesis)可能提供了针对 C/C++ 代码的高级综合功能,可以在高级抽象层面上进行浮点数运算,并将其综合成硬件描述语言。

4. 利用 FPGA 上的软处理器

某些 FPGA 上集成了可编程软处理器,如 ARM Cortex 系列。

在这些处理器上,可以使用软件编程语言 如 C/C++)执行浮点数运算,并与硬件设计进行交互。

需要注意的是,对于浮点数运算的实现,硬件实现通常会更复杂、

更昂贵,并且不如软件中的浮点数运算灵活和高效。

因此,在数字电路设计中,往往更倾向于使用定点数或者其他方式来近似实现浮点数运算,以满足特定的需求和性能要求。

基于FPGA的卷积神经网络的实现

基于FPGA的卷积神经网络的实现李嘉辉;蔡述庭;陈学松;熊晓明【摘要】现有基于CPU或GPU的卷积神经网络实现方案,无法兼顾实时性、功耗以及便携性的要求.基于FPGA强大的并行处理能力和超低功耗,在DE1-Soc开发板上采用Verilog HDL实现了使用MNIST数据集的阿拉伯数字手写体识别卷积神经网络.网络的每一层采用流水线和时分复用方法;单个时钟周期能完成72次乘累加操作,在100 MHz的工作频率下,加速器峰值运算速度可达7.2 GMAC/s.与PC 上运行的定点数版本的C语言程序相比,在相同错误率6.43%的情况下,速度是其5.2倍.【期刊名称】《自动化与信息工程》【年(卷),期】2018(039)001【总页数】6页(P32-37)【关键词】卷积神经网络;FPGA;性能加速【作者】李嘉辉;蔡述庭;陈学松;熊晓明【作者单位】广东工业大学自动化学院;广东工业大学自动化学院;广东工业大学自动化学院;广东工业大学自动化学院【正文语种】中文目前卷积神经网络(Convolutional Neural Network,CNN)的实现方案有基于CPU、GPU和FPGA三大类。

因CPU的结构特点以及通用计算机的架构限制,导致基于CPU的方案功耗、便携性和实时性不可兼得。

虽然GPU具有强大的浮点运算和并行处理能力,但基于GPU的方案,存在功耗过高,移动性能也不足的弱点[1-3]。

因此,基于CPU或者GPU的实现方案在追求移动性能的场景下均不可取。

FPGA具有强大的并行处理能力、灵活的可配置特性和超低功耗,可以考虑作为CNN的实现平台。

目前,FPGA开发有2种途径:一种是基于HDL的传统途径;另一种是使用高层次综合工具,如OpenCL或者Xilinx的HLS[4],虽能加快FPGA开发流程,但资源消耗大、性能低,且开发人员不能对生成的电路进行精准干预。

因此本文使用Verilog HDL语言,在DE1-Soc平台下实现一个识别阿拉伯数字手写体的CNN 网络。

verilog 中负整数转浮点

verilog 中负整数转浮点摘要:一、引言二、Verilog中的负整数转浮点1.负整数转浮点原理2.Verilog实现方法三、实例分析1.实例一2.实例二四、总结正文:一、引言在数字电子技术中,浮点运算被广泛应用于科学计算、信号处理等领域。

在Verilog中,实现负整数转浮点是一个常见的需求。

本文将详细介绍这一过程的原理及Verilog实现方法。

二、Verilog中的负整数转浮点1.负整数转浮点原理在Verilog中,负整数转浮点主要依靠符号位、阶码和尾数来表示。

其中,符号位用于表示正负,阶码表示指数,尾数表示小数部分。

通过这些位的组合,可以表示出负整数对应的浮点数。

2.Verilog实现方法(1)符号位:通过添加一个额外的位来表示负数,0表示正数,1表示负数。

(2)阶码:使用一个8位二进制数表示,用来表示指数部分。

(3)尾数:使用23位二进制数表示,用来表示小数部分。

三、实例分析1.实例一假设有一个负整数-5,我们可以通过以下步骤将其转换为浮点数:(1)符号位:因为-5是负数,所以符号位为1。

(2)阶码:将-5的绝对值转换为二进制,得到101,取反加1得到010,即阶码为6。

(3)尾数:将-5的小数部分转换为二进制,得到0.101,截断后得到0.101,即尾数为0.101。

综上,-5在Verilog中表示为:符号位1,阶码6,尾数0.101。

2.实例二再以负整数-3为例,进行浮点转换:(1)符号位:因为-3是负数,所以符号位为1。

(2)阶码:将-3的绝对值转换为二进制,得到011,取反加1得到100,即阶码为4。

(3)尾数:将-3的小数部分转换为二进制,得到0.011,截断后得到0.011,即尾数为0.011。

综上,-3在Verilog中表示为:符号位1,阶码4,尾数0.011。

四、总结本文详细介绍了Verilog中负整数转浮点的原理及实现方法,并通过实例进行了分析。

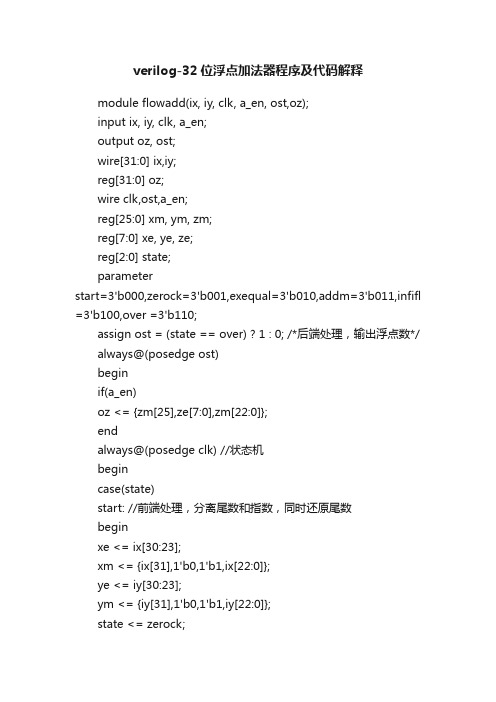

verilog-32位浮点加法器程序及代码解释

verilog-32位浮点加法器程序及代码解释module flowadd(ix, iy, clk, a_en, ost,oz);input ix, iy, clk, a_en;output oz, ost;wire[31:0] ix,iy;reg[31:0] oz;wire clk,ost,a_en;reg[25:0] xm, ym, zm;reg[7:0] xe, ye, ze;reg[2:0] state;parameterstart=3'b000,zerock=3'b001,exequal=3'b010,addm=3'b011,infifl =3'b100,over =3'b110;assign ost = (state == over) ? 1 : 0; /*后端处理,输出浮点数*/ always@(posedge ost)beginif(a_en)oz <= {zm[25],ze[7:0],zm[22:0]};endalways@(posedge clk) //状态机begincase(state)start: //前端处理,分离尾数和指数,同时还原尾数beginxe <= ix[30:23];xm <= {ix[31],1'b0,1'b1,ix[22:0]};ye <= iy[30:23];ym <= {iy[31],1'b0,1'b1,iy[22:0]};state <= zerock;endzerock:beginif(ix == 0)begin{ze, zm} <= {ye, ym};state <= over;endelseif(iy == 0)begin{ze, zm} <= {xe, xm};state <= over;endelsestate <= exequal;endexequal: //指数处理,使得指数相等beginif(xe == ye)state <= addm;elseif(xe > ye)beginye <= ye + 1;ym[24:0] <= {1'b0, ym[24:1]};if(ym == 0)beginzm <= xm;ze <= xe;state <= over;endelsestate <= exequal;endelsebeginxe <= xe + 1;xm[24:0] <= {1'b0,xm[24:1]};if(xm == 0)beginzm <= ym;ze <= ye;state <= over;endelsestate <= exequal;endendaddm: //带符号位和保留进位的尾数相加beginif ((xm[25]^ym[25])==0)beginzm[25] <= xm[25];zm[24:0] <= xm[24:0]+ym[24:0]; endelseif(xm[24:0]>ym[24:0])beginzm[25] <= xm[25];zm[24:0] <=xm[24:0]-ym[24:0]; endelsebeginzm[25] <= ym[25];zm[24:0] <=ym[24:0]-xm[24:0]; endze <= xe;state <= infifl;endinfifl: //尾数规格化处理beginif(zm[24]==1)beginzm[24:0] <= {1'b0,zm[24:1]}; ze <= ze + 1;state <= over;endelseif(zm[23]==0)beginzm[24:0] <= {zm[23:0],1'b0}; ze <= ze - 1;state <= infifl;endelsestate <= over;endover:beginstate<= st art;end default: beginstate<= start; end endcaseend endmodule。

verilog 带符号定点数加法

Verilog带符号定点数加法一、引言Verilog是一种硬件描述语言,被广泛用于数字电路的设计和仿真。

在Verilog中,定点数加法是常见的数字电路设计任务之一。

在本文中,我们将介绍Verilog中带符号定点数加法的实现方法。

二、带符号定点数1. 定点数定点数是一种表示数值的方法,它将数值表示为带有小数部分的整数。

定点数可以是带符号的,也可以是无符号的。

在Verilog中,定点数通常使用固定位宽的二进制数表示。

2. 带符号数带符号数是可以表示正负的数值。

在Verilog中,带符号数通常使用二进制补码表示。

在二进制补码表示中,最高位表示符号位,0表示正数,1表示负数。

三、带符号定点数加法的实现在Verilog中,带符号定点数加法可以通过将加数和被加数的符号位相同的情况下,对二进制数进行加法运算来实现。

具体步骤如下:1. 确定位宽需要确定带符号定点数的位宽,包括整数部分和小数部分。

位宽的选择需要考虑数值范围和精度要求。

2. 符号扩展对于两个带符号定点数,需要进行符号扩展,使它们的位宽相同。

符号扩展是将较短的带符号定点数的符号位复制到较长的带符号定点数的高位。

3. 加法运算进行带符号定点数的加法运算。

在Verilog中,可以使用"+"操作符进行加法运算。

需要注意处理进位,以及溢出情况。

4. 结果截断根据实际需求,对加法运算得到的结果进行截断,得到最终的带符号定点数结果。

四、示例代码以下是一个简单的Verilog示例代码,实现了带符号定点数加法的功能:```module signed_fixed_point_addition(input signed [7:0] a, // 带符号定点数a,8位位宽input signed [7:0] b, // 带符号定点数b,8位位宽output reg signed [7:0] result // 加法结果,8位位宽);always (*) beginresult = a + b; // 带符号定点数加法运算endendmodule```五、总结带符号定点数加法是数字电路设计中常见的任务,Verilog提供了实现这一功能的灵活和强大的工具。

verilog 定点数转浮点数

verilog 定点数转浮点数英文回答:Floating-point numbers are commonly used in many applications, such as scientific computing, computer graphics, and signal processing. Verilog, a hardware description language, is often used to design digital circuits, including those that can perform floating-point operations.There are several ways to convert a fixed-point number to a floating-point number in Verilog. One common method is to use the `ieee_float_conv` function, which is part of the IEEE Std 1364-1995 standard. This function takes a fixed-point number as input and returns a floating-point number with the same value.Another method for converting a fixed-point number to a floating-point number is to use a series of bitwise operations. This method can be more efficient than usingthe `ieee_float_conv` function, but it is also more complex.Here is an example of how to convert a fixed-point number to a floating-point number using bitwise operations:verilog.module fixed_to_float(。

Verilog浮点数的定点化

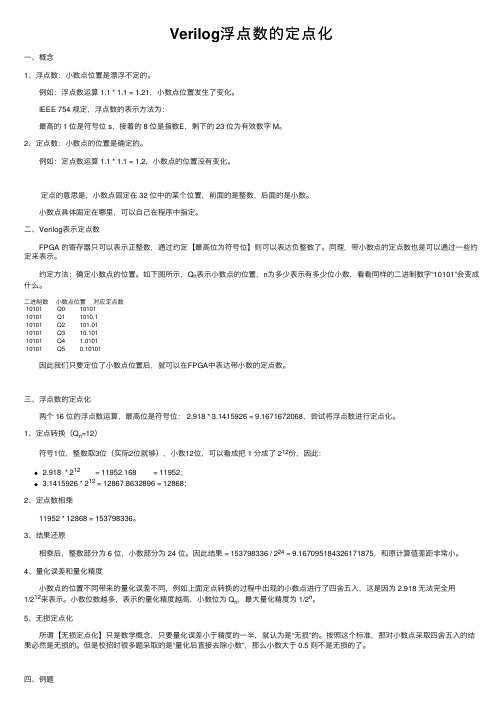

Verilog浮点数的定点化⼀、概念1、浮点数:⼩数点位置是漂浮不定的。

例如:浮点数运算 1.1 * 1.1 = 1.21,⼩数点位置发⽣了变化。

IEEE 754 规定,浮点数的表⽰⽅法为: 最⾼的 1 位是符号位 s,接着的 8 位是指数E,剩下的 23 位为有效数字 M。

2、定点数:⼩数点的位置是确定的。

例如:定点数运算 1.1 * 1.1 = 1.2,⼩数点的位置没有变化。

定点的意思是,⼩数点固定在 32 位中的某个位置,前⾯的是整数,后⾯的是⼩数。

⼩数点具体固定在哪⾥,可以⾃⼰在程序中指定。

⼆、Verilog表⽰定点数 FPGA 的寄存器只可以表⽰正整数,通过约定【最⾼位为符号位】则可以表达负整数了。

同理,带⼩数点的定点数也是可以通过⼀些约定来表⽰。

约定⽅法:确定⼩数点的位置。

如下图所⽰,Q n表⽰⼩数点的位置,n为多少表⽰有多少位⼩数,看看同样的⼆进制数字“10101”会变成什么。

⼆进制数⼩数点位置对应定点数10101 Q0 1010110101 Q1 1010.110101 Q2 101.0110101 Q3 10.10110101 Q4 1.010110101 Q5 0.10101 因此我们只要定位了⼩数点位置后,就可以在FPGA中表达带⼩数的定点数。

三、浮点数的定点化 两个 16 位的浮点数运算,最⾼位是符号位: 2.918 * 3.1415926 = 9.1671672068,尝试将浮点数进⾏定点化。

1、定点转换(Q n=12) 符号1位,整数取3位(实际2位就够),⼩数12位,可以看成把 1 分成了 212份,因此:2.918 * 212 = 11952.168 = 11952;3.1415926 * 212 = 12867.8632896 = 12868;2、定点数相乘 11952 * 12868 = 153798336。

3、结果还原 相乘后,整数部分为 6 位,⼩数部分为 24 位。

verilog 中负整数转浮点

verilog 中负整数转浮点摘要:1.负整数转浮点的背景和需求2.Verilog 中负整数转浮点的方法3.实例解析4.总结正文:【1.负整数转浮点的背景和需求】在数字电路设计和FPGA 开发中,Verilog 作为一种硬件描述语言,常常需要对数字信号进行各种操作。

其中,负整数转浮点数的操作在某些场景下是必要的。

例如,在数字信号处理、通信系统等领域,需要对负整数进行浮点数运算,以满足精度和性能的要求。

【2.Verilog 中负整数转浮点的方法】在Verilog 中,负整数转浮点数的方法主要有以下几种:(1) 使用`$float`和`$int`运算符:通过将负整数与`$int`类型的数进行运算,然后将结果赋值给`$float`类型的变量,从而实现负整数转浮点数。

(2) 使用`conv`函数:`conv`函数是Verilog 中的一个内置函数,用于将整数转换为浮点数。

通过`conv`函数,可以直接将负整数转换为浮点数。

(3) 使用`$cast`运算符:`$cast`运算符可以将一个数据类型的值转换为另一个数据类型的值。

通过`$cast`运算符,可以将负整数转换为浮点数。

【3.实例解析】下面给出一个Verilog 代码实例,演示如何实现负整数转浮点数:```verilogmodule negative_integer_to_float (input wire clk,input wire reset,input wire [7:0] negative_integer,output reg [23:0] float_number);reg [23:0] float_number_reg;always @(posedge clk or posedge reset) beginif (reset) beginfloat_number <= 0;end else beginfloat_number <= float_number_reg;endendalways @(*) beginif (negative_integer < 0) beginfloat_number_reg <= conv(negative_integer, 16, 32);end else beginfloat_number_reg <= 0;endendendmodule```在这个例子中,输入信号`negative_integer`表示一个负整数,输出信号`float_number`表示对应的浮点数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

verilog定点数转浮点数

定点数和浮点数是数字电路中常用的数据表示形式。

定点数用于表示整数,而浮点数用于表示实数。

在Verilog语言中,可以通过一些算法和技巧将定点数转换为浮点数。

一种常用的定点数转浮点数的方法是将定点数表示法转换为IEEE 754浮点数表示法。

IEEE 754浮点数表示法是一种标准的浮点数表示方法,它使用符号位、指数位和尾数位来表示实数的值和精度。

定点数通常是用有限的二进制位数来表示的,而浮点数则采用科学计数法的形式。

因此,定点数转换为浮点数的关键是如何选择适当的指数和尾数,以保持有效的精度。

首先,将定点数转换为二进制数。

定点数可以是有符号的,因此需要考虑符号位。

根据定点数的位宽,选择合适的位数表示整数部分和小数部分。

对于有符号定点数,需要将其转换为补码表示法。

接下来,确定指数位和尾数位的位宽。

指数位用于表示浮点数的指数部分,尾数位用于表示浮点数的尾数部分。

根据IEEE 754浮点数表示法的规定,指数位和尾数位的位宽可以根据所需的精度和取值范围进行选择。

然后,进行指数的偏移。

在IEEE 754浮点数表示法中,指数位使用了一个偏移值来表示浮点数的真实指数值。

偏移值的选择取决于指数部分的位宽和所需的指数范围。

进行尾数的规范化。

浮点数的尾数部分采用了规范化的表示形式,其中最高有效位为1。

将定点数的二进制表示形式转换为浮点数的二进制表示形式时,需要对尾数进行规范化操作,使其满足规范化表示的要求。

最后,将符号位、指数位和尾数位组合成浮点数的表示形式。

根据IEEE 754浮点数表示法的规定,符号位放在最高位,指数位紧接着符号位,然后是尾数位。

以上是一种常用的定点数转浮点数的方法,可以在Verilog语言中实现。

该方法的关键是选择合适的位宽和参考IEEE 754浮点数表示法的规范进行转换。

通过这种方法,可以将定点数转换为浮点数,并在数字电路设计中应用浮点数运算。

定点数转浮点数的实现并不复杂,但需要仔细设计和验证。

在Verilog语言中,可以使用各种工具和库来实现该转换,并进行仿真和验证。

通过适当的测试和验证,可以确保定点数转换为浮点数的正确性和可靠性。